#### **Features**

- Up to 4.25 Gbps per channel

- 2 to 12 independent receivers in a single package

- Each channel complies with IEEE Std. 802.3z Gigabit Ethernet 1000 Base-Sx PMD requirements

- Also suitable for Fibre Channel, Infiniband and VSR-1 requirements

- Qualified over the industrial temperature range [-40;+85°C]

- Standard electrical plug/socket interface

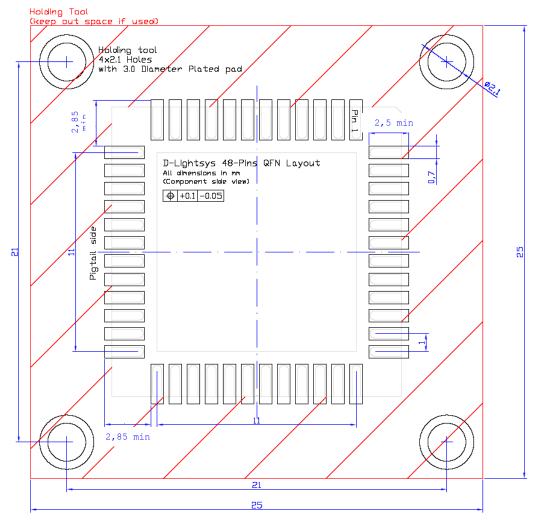

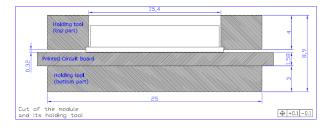

- Small package size (16x16x3mm)

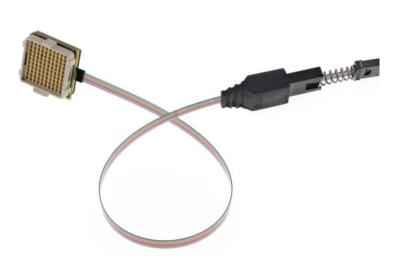

- Pigtailed optical connectics

- Low power consumption

- Single 3.3 V power supply

#### **Applications**

- Sensors interconnects

- Numerical video transmission

- Board-to-board communications

- Severe environment interconnects

- Space application

#### **Product Description**

D-Light DLR-xx-251-lw-Pyz-Lvv parallel optoelectronic modules receive high data rate signals on either 2, 4, 8 or 12 independent channels. They are optimized for short distance high data rate optical communications on multimode fiber ribbon and fully comply with ARINC804 Standard. They are protocol independent and can be applied to Gigabit Ethernet (both 1GBE and 10 GBE), Fibre Channel, Infiniband or any specific communication application in the qualified temperature range [-40;+85°C].

DLR-xx-251-lw-Pyz-Lvv modules integrate state-of-the art GaAs PIN photodiode arrays and are optimized for low power consumption (<125 mW for each receiver channel).

DLR-xx-251-lw-Pyz-Lvv are available in various package such as surface mount or pluggable ones and various multimode fiber ribbon pigtail termination are offered around the standardized MT ferrule.

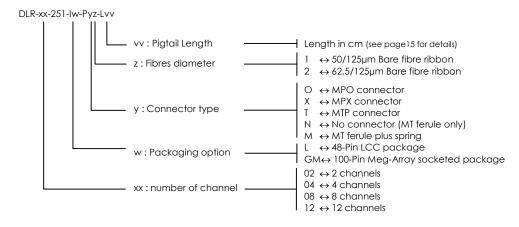

#### Ordering Information

Several versions of D-Light optoelectronic receivers are currently available. All use 50/125 or  $62.5/125\mu m$  fiber ribbon cables.

Information subject to change without further notice

#### **Absolute Maximum Ratings**

Stress beyond the values stated below may cause permanent damage to the device.

| Parameter                 | Symbol           | Min                  | Max                  | Unit | Notes |

|---------------------------|------------------|----------------------|----------------------|------|-------|

| Storage temperature       | Tst              | -55                  | +125                 | °C   | -     |

| Soldering temperature     | T <sub>sol</sub> | -                    | 230                  | °C   | -     |

| Soldering time            | † <sub>sol</sub> | -                    | 60                   | S    | -     |

| Supply voltage            | Vcc              | -0.3                 | +4.0                 | V    | -     |

| Signal pins voltage range | $V_{pin}$        | V <sub>EE</sub> -0.3 | V <sub>CC</sub> +0.3 | V    | -     |

| Junction temperature      | Tj               | -                    | 130                  | °C   | -     |

| ESD resistance voltage    | ESD              | -                    | 1                    | KV   | -     |

Notes:

1. Human Body Model (HBM) according to JESD22-A114-B.

| Module specifications – General VCC =3.3V, VEE=GND= 01 |                              |           |                      |        |        |      |       |  |  |

|--------------------------------------------------------|------------------------------|-----------|----------------------|--------|--------|------|-------|--|--|

| Parameter                                              |                              | Symbol    | Min                  | Тур    | Max    | Unit | Notes |  |  |

| Supply voltage                                         |                              | Vcc       | 3.0                  | 3.3    | 3.6    | V    | -     |  |  |

| Supply voltage noise                                   |                              | Nvcc      | -                    | -      | 100    | mV   | 1     |  |  |

| Supply current                                         |                              | Icc       | -                    | xx•35  | xx•42  | mA   | 2     |  |  |

| Power supply noise re                                  | Power supply noise rejection |           | -                    | -      | 15     | dB   | -     |  |  |

| Dower consumption                                      | 12 channels                  | Ptot      |                      | xx•125 | xx•150 | mW   | 2     |  |  |

| Power consumption                                      | Per channel                  | $P_{ch}$  | -                    | -      | 125    | mW   | 2     |  |  |

| Rx enable/disable                                      | Disabled                     | $V_{dis}$ | 0                    | -      | 0.8    | V    | 3     |  |  |

| voltage Enabled                                        |                              | Ven       | V <sub>CC</sub> -1.3 | _      | Vcc    | V    | 3     |  |  |

| Data rate per channel                                  |                              | В         | 0.01                 | 2.5    | 4.25   | Gbps | 4     |  |  |

| Qualified temperature                                  | Qualified temperature        |           |                      | -      | +85    | °C   | 5     |  |  |

Notes:

- 1. For noise frequencies < 10MHz

- 2. xx represents the number of channel. Power consumption per Rx channel operating at full speed.

- 3. The module is normally enabled (i.e. when the RxEnable control input is not connected).

- 4. Bit rate of 4.25Gbps can be achieved with an optical input sensitivity reduced to -15 dBm typ.

- 5. Module operates over [-55;+100°C] with limited degraded performances.

| Module specifications – Electrical | VCC <sub>x</sub> =3.3V, | VEEx=GNDx= 0      | V, Temp = [- | 40;+85°C] |     |      |       |

|------------------------------------|-------------------------|-------------------|--------------|-----------|-----|------|-------|

| Parameter                          |                         | Symbol            | Min          | Тур       | Max | Unit | Notes |

| Number of channels                 |                         | Nch               | 4            | -         | 12  | -    | -     |

| Differential output voltage        |                         | $V_{OUTpp}$       | 250          | 300       | 400 | mV   | -     |

| Output stage power supply rang     | е                       | Voref             | 1.8          | -         | Vcc | V    | 1     |

| Output impedance                   |                         | Zout              | 80           | 100       | 120 | Ω    | -     |

| Channel crosstalk penalty          |                         | X <sub>Popt</sub> | -            | 1         | 2   | dB   | 2     |

| Link Manitar Output                | High                    | V <sub>OH</sub>   | 2.4          | -         | Vcc | V    | 3, 4  |

| Link Monitor Output                | Link Monitor Output Low |                   | 0            | -         | 0.5 | V    | 3, 4  |

| Total jitter receiver              |                         | TJ                | -            | -         | 150 | ps   | 5     |

| Rise/Fall time                     |                         | $	au_{R},	au_{F}$ | 40           | -         | 120 | ps   | 5     |

| Rx electrical power consumption    | $P_{Rx}$                | -                 | 125          | 150       | mW  | -    |       |

Notes:

- 1. Output stage complies with CML 3.3 to 1.8V standards. See description for details.

- 2. For adjacent channels in worst case at full speed (one channel at sensitivity & adjacent channel at saturation), squelch function OFF.

- 3. Compatible with LVTTL/CMOS digital level specifications.

- The Link Monitor circuit monitors the incoming optical signal level and generates a logic LOW signal when insufficient photocurrent is produced (see detailed description below).

- 5. Measured at 1.25Gbps and with 20% / 80% levels.

Information subject to change without further notice

| Module specifications - O <sub>l</sub> | x=3.3V, VEE= 0 | )V, Temp = [-         | 40;+85°C]            |     |                      |      |       |

|----------------------------------------|----------------|-----------------------|----------------------|-----|----------------------|------|-------|

| Parameter                              |                | Symbol                | Min                  | Тур | Max                  | Unit | Notes |

| Center wavelength                      |                | λς                    | 760                  | 850 | 860                  | nm   | -     |

| Spectral width – rms                   |                | Δλ                    | -                    | -   | 1                    | nm   | -     |

| Core diameter of the Rx pigtail        | optical fiber  | Dc                    | 50                   | -   | 62.5                 | μm   | -     |

|                                        | 1.25 Gbps      |                       | -                    | -18 | -17                  | dBm  | 1     |

| Optical sensitivity                    | 2.5 Gbps       | Pin                   | -                    | -17 | -16                  | dBm  | 1     |

|                                        | 4.25 Gbps      |                       | -                    | -16 | -15                  | dBm  | 1     |

| Optical modulation amp                 | litude         | OMA                   | 50                   | -   | -                    | μW   | -     |

| Optical return loss                    |                | ORL                   | -30                  | -   | -                    | dB   | -     |

| SDy antical consitivity                | SDx = High     | PoptTh(H)             | -19.2                | -18 | -16.5                | dBm  | 2     |

| SDx optical sensitivity                | SDx = Low      | PoptTh(L)             | -22.2                | -21 | -19.2                | dBm  | 2     |

| Signal Data et valetas Normal          |                | V <sub>SD Norm</sub>  | V <sub>CC</sub> -0.5 | -   | Vcc                  | V    | 3     |

| Signal Detect volatge                  | Fault          | V <sub>SD</sub> Fault | VEE                  | -   | V <sub>EE</sub> +0.5 | V    | 3     |

#### Notes:

- 1. For BER= $10^{-12}$  measured at the specified bit rate with a  $2^7$ -1 PRBS signal

- 2. Assuming a receiver sensitivity of 0.5A/W.

- 3. Signal Detect is LVTTL. Logic "1" indicates normal operation; logic "0" indicates no signal is detected.

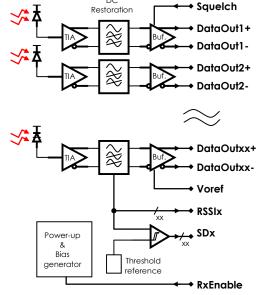

#### Functional block diagram

Figure 1 - DLR-xx-251-lw-Pyz-Lvv block schematic

#### **Description**

#### General

DLR-xx-251-lw-Pyz-Lvv modules are optimized for high speed DC-coupled serial links: the maximum bit rate is up to 4.25Gbits/s/ch. The module is 3.3 Volts single supplied for low power consumption. The module dimensions are  $16\times16\times3$  mm.

DLR-xx-251-lw-Pyz-Lvv modules are based on high speed GaAs photodiode arrays and on high performances BiCMOS transimpedance (TIA) and limiting (LA) amplifiers arrays. The signal path is AC-coupled and allows 2R (reshape and reclock) recovery.

Several features allow a large range of applications.

- LVCMOS input compatible Run/shutdown commands permit low power consumption.

- Analog inputs & outputs monitor each channel state and performance.

#### **Receiver controls**

The following input/output pins permit a complete monitoring of the module:

- RXEnable. All receiver channels can be disabled by pulling down the enable input pin.

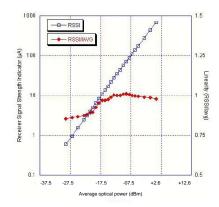

- Receiver Strengh Signal Indicator (RSSIx). Each DC/low-frequency output RSSIx sources a current proportional to the average input photocurrent of the considered photodiode.

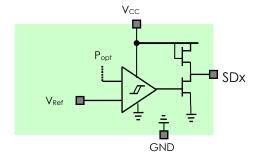

- Link Monitors or **Signal Detect** (SDx). Each Signal detect output indicates a presence or a loss-of signal. When peak to peak photocurrent is below the sensitivity limit of the circuit.

- □ **Squelch**: this digital input pin enables the squelch function.

#### **Detail description**

The receiver part of the DLR-xx-251-lw-Pyz-Lvv module is based on high speed GaAs photodiode array and high performances BiCMOS transimpedance (TIA) and limiting (LA) amplifiers array. Some input and output signals have been added to the design for complete controlling of the module (in particular a link monitor with a threshold selector has been added to comply with standard specifications SDH STM-16).

The signal path is AC-coupled and allows 2R (reshape and reclock) recovery. The minimum lower cut-off frequency is dependent on the pattern spreading but can be as low as 100KHz. This circuit is therefore compatible with data rates ranging from 10Mbps to 4.25 Gbps.

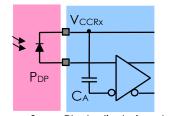

#### Photodiode input stage

The photodiode input stage is a differential transimpedance amplifier with high sensitivity that operates with input current as low as  $12\mu A_{pp}$ . Typical photodiode sensitivity at 850nm is 0.6A/W: the optical sensitivity is therefore as low as -18dBm (@1.25Gbps). The amplifier incorporates a compensation capacitor.

Figure 2 - Receiver bloc diagram (1ch)

Figure 3 - Photodiode input stage

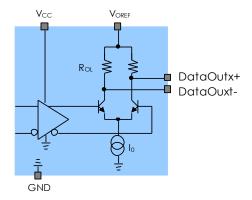

#### **Data Output stage**

The output stage is a differential current-mode-logic (CML) driver (cf. Figure 4). The pull-up resistors are tied to a separated supply pin  $V_{OREF}$  which, according to the applied voltage, allows the stage to be compatible with LVDS level. Provided the load impedances at the two outputs are matched, the switching noise can be minimized. The general characteristics of the output stage are the following (See application note for usage):

- □ Switched current I<sub>0</sub> of 9mA,

- $\square$  pull-ups Rol 2x50 $\Omega$  to Voref.

- A squelch function is implemented to turn off the output stage when no input power is detected.

- $\Box$  Free choice of V<sub>OREF</sub> and 50 $\Omega$  load resistor connection, as long as operating conditions are fulfilled.

- Only a small amount of noise is generated on VOREF and GND.

- Output swing selectable (SWS pin).

For <u>differential DC-coupled termination with negative power supply</u> (Vcc and Vores should be connected to ground and GND to the negative supply): The outputs are then connected to  $50\Omega$  tracks, terminated by two  $50\Omega$  loads to ground, or a floating  $100\Omega$  load.

For <u>single-ended AC-coupled</u>: both outputs should see equal load impedances.

For <u>LVDS-level compatibility</u>:  $V_{\text{OREF}}$  should be tied to  $VEE_{\text{Rx}}$ +2.4V. The resulting levels are then compatible with an IEEE P1596.3 LVDS input stage.

VOREF voltage range allows compatibility with CML common mode voltage from 1.8V to 3.3V.

Figure 4 - Data output stage

The output stage is equipped with a squelch function that turn off the output stage when the input optical power of the corresponding channel is below a threshold (typically -18dBm). In addition to this function a Swing Size (SWS pin) select feature is implemented to increase the size of output swing as a Pre-emphasis feature (PE[2:0] pins).

#### Receiver controls

Note that all the receiver controls are not available for all the module package option. We describe hereafter all the receiver controls available (accessible in the IGM option: 100-pin Meg-Array socket).

Receiver Signal Strength Indicator (RSSIx): the DC/low-frequency outputs source a current proportional to the average input photocurrent (internally loaded by a Resistor to provide a Voltage output) of the corresponding channel provided that V<sub>RSSIX</sub> is within the operating range specified  $(V_{RSSIx} \le 2.0 \text{ V})$  to obtain best linearity (see receiver characteristics table). This output can be used to monitor the optical power incident on the photodiode. It may be left open if not used. The upper corner frequency of the output is equal to the rollon frequency flow of the high-speed data path (Figure 5 & Receiver characteristics table).

Figure 5 - Typical average monitor current and RSSI voltage (one channel)

Information subject to change without further notice

#### Receiver incident optical power computation

The voltage at RSSI<sub>x</sub> output pin is proportional to the input optical power of the receiver thought the following equation:

$$RSSI_{x} = \frac{1}{k} \cdot \frac{R_{ext} \times 10000}{R_{ext} + 10000} \cdot P_{opt} \rightarrow Popt = k \cdot RSSI_{x} \cdot \frac{R_{ext} + 10000}{R_{ext} \times 10000} \text{ (µW)}$$

Where  $R_{\text{ext}}$  is the resistor attached to RSSI<sub>x</sub> pin, k a internal coefficient and  $P_{\text{opt}}$  the incident receiver optical power in  $\mu$ W. Note that linearity is maintained for RSSI  $\leq$  2.0V. RSSI accuracy is depending to the accuracy value of the internal k coefficient.

|                               | Symbol | Min. | Тур. | Max. |

|-------------------------------|--------|------|------|------|

| Internal coefficient for RSSI | k      | -20% | 2    | +20% |

□ Signal Detect: The signal detect circuitry is available for each channel. The circuitry compares the average current of a channel to the threshold current. If it is below the threshold, the signal detect condition is de-asserted. A hysteresis function of greater than 1dB prevents chattering of the signal detect signal. The channel level signal detect pads (SDx) are open drain outputs with weak pull-ups.

Figure 6 - Link monitor output stage

- Squelch (**SQS**): this digital input pin enables the squelch function i.e. the data outputs of the corresponding channel are set to "0" when Signal Detect signals are asserted (no sufficient P<sub>opt</sub>).

- RXEnable: the receiver side of the module can be disabled by pulling down the RXEnable input pin.

- Swing Size Select (**SWS**): This function is used to increase the size of the output swings. When SWS is high, the output voltage swing (differential, pp) is set to a min. value of 500mV with a max. value of 800mV (+400mV to -400mV). These values correspond to the single ended swings of 250 and 400mV. When SWS is low, the voltage swing is increased by approximately 50%. The output voltage swing (differential, pp) is set to min. 750mV and a max. 1100mV (+550mV to -550mV). These values correspond to the single ended voltage swings of 375mV and 550mV.

- The common mode level (VOREF) of the output is adjustable in order to interface to different kind of logic levels (LVDS for examples).

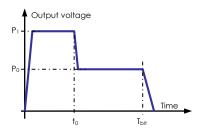

- Pre-emphasis Control (**PE[2:0]**): The Pre-emphasis technique is used to partially negate the effect of high frequency attenuation of signals traveling through PCB due to skin effect and dielectric loss. Pre-emphasis increase the high frequency component of a pulse by re-shaping it. The pre-emphasis scheme emphasizes the high frequency components to P<sub>1</sub> during the t<sub>0</sub> period of the bit transition. When there is no switching in subsequent bit period, the voltage level stays at P<sub>0</sub>. The T<sub>0</sub> value is tuned towards operation at 3.125Gbps. Lower data rate will not require pre-emphasis.

The amount of pre-emphasis that is needed is highly dependent on the characteristics of the trace. The designer will need to set the pre-emphasis based on the actual measurements from the board. There are seven different settings for pre-emphasis and one setting to turn-off the function (PE[2:0]=000).

Figure 7 - Pulse shape with pre-emphasis

| PE[2:0] | P <sub>0</sub> | <b>P</b> 1 |

|---------|----------------|------------|

| 000     | 300mV          | 0mV        |

| 001     | 280mV          | 20mV       |

| 010     | -              | -          |

| 011     | 230mV          | 100mV      |

| 100     | -              | -          |

| 101     | 200mV          | 200mV      |

| 110     | -              | -          |

| 111     | 150mV          | 250mV      |

Pre-emphasis will increase the power consumption of the module. Pre-emphasis can only be used with SWS=1. Using it with SWS=0 lowers the long term reliability of the module.

#### Power supply noise rejection

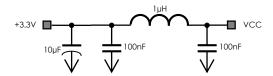

Even though bypass capacitors are integrated inside the module, additional filtering can reduce the noise penalty above 10 MHz. For a supply noise  $V_{PSN} = 100 \text{ mVpr}$  a 0.5 dB sensitivity penalty can be reached over the whole frequency range by using a first order low-pass filter with  $f_c = 10 \text{ MHz}$  on the power supply. See figure 8 for a typical power supply filter.

Figure 8 - Typical power supply filter

Module power supplies (VCC and VOREF) should be correctly filtered in order to sufficiently reject the digital noise produced by the output stage on the VOREF power supply rail from the analog power supply rail (VCC). A 15dB rejection ratio between VCC and VOREF is recommended.

The previous proposed filter could be used on both VCC and VOREF rails, assuming the decoupling caps are RF ones.

#### **Memory Mapping**

The module memory is mapped in one memory area. The memory is accessible through a common 2-wire serial interface. The following figure details the module memory organization.

| Function                   | Index | D7   | D6   | D5        | D4        | D3        | D2        | D1        | D0        |

|----------------------------|-------|------|------|-----------|-----------|-----------|-----------|-----------|-----------|

| Link Monitor 1             | 0x00  | SD8  | SD7  | SD6       | SD5       | SD4       | SD3       | SD2       | SD1       |

| Link Monitor 2             | 0x01  | Х    | Х    | Х         | Х         | SD12      | SD11      | SD10      | SD9       |

| Channel Powerdown 1        | 0x02  | DIS8 | DIS7 | DIS6      | DIS5      | DIS4      | DIS3      | DIS2      | DIS1      |

| Channel Powerdown 2        | 0x03  | Х    | Х    | Х         | Х         | DIS12     | DIS11     | DIS10     | DIS9      |

| Pre-emphasis Ch 1 and 2    | 0x04  | Х    | Х    | PECH2[2]  | PECH2[1]  | PECH2[0]  | PECH1[2]  | PECH1[1]  | PECH1[0]  |

| Pre-emphasis Ch 3 and 4    | 0x05  | Х    | Х    | PECH4[2]  | PECH4[1]  | PECH4[0]  | PECH3[2]  | PECH3[1]  | PECH3[0]  |

| Pre-emphasis Chl 5 and 6   | 0x06  | Х    | Х    | PECH6[2]  | PECH6[1]  | PECH6[0]  | PECH5[2]  | PECH5[1]  | PECH5[0]  |

| Pre-emphasis Chl 7 and 8   | 0x07  | Х    | Х    | PECH8[2]  | PECH8[1]  | PECH8[0]  | PECH7[2]  | PECH7[1]  | PECH7[0]  |

| Pre-emphasis Ch 9 and 10   | 0x08  | Х    | Х    | PECH10[2] | PECH10[1] | PECH10[0] | PECH9[2]  | PECH9[1]  | PECH9[0]  |

| Pre-emphasis Chl 11 and 12 | 0x09  | Х    | Х    | PECH12[2] | PECH12[1] | PECH12[0] | PECH11[2] | PECH11[1] | PECH11[0] |

| Vendor ID code 1           | 0x0A  | M7   | M6   | M5        | M4        | M3        | M2        | M1        | M0        |

| Vendor ID code 2           | 0x0B  | Х    | Х    | Х         | Х         | Х         | M10       | M9        | M8        |

| Global Link Monitor        | 0x0C  | Х    | Х    | Х         | Х         | Х         | Х         | Х         | SD_ALL    |

| Increment mode             | 0x0D  | Х    | Χ    | Х         | Х         | Х         | Х         | Х         | NOTINCR   |

Figure 9 - DLR-xx-251-lw-Pyz-Lvv memory organization

**Note**: the I2C interface could not be use in conjunction with the JTAG interface. Disable JTAG before using the I2C by pulling low the TRSTn pin.

#### Receiver memory description

The receiver memory is accessible only in R/W. The receiver memory responds to address (1010010) $_b$  or (52) $_h$  and (1010011) $_b$  or (53) $_h$ .

**Receiver memory**

| Memory<br>Location<br>(hex) | EEPROM/SRAM | R/W | Default<br>Setting<br>(hex) | Name of Location            | Function                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------|-------------|-----|-----------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                          | SRAM        | R   | N/A                         | Link Monitor Register<br>#1 | The bit indicates the signal detect status. When the bit is set, it indicates that the peak to peak input current is above the threshold $I_{thSD}$ . When the bit is cleared, the signal level is below the threshold. There is a hysteresis circuit to avoid chatter on this signal. These bits do not latch the outputs and are an instantaneous indication of the signal levels. |

| 01                          | SRAM        | R   | N/A                         | Link Monitor Register<br>#2 | Link Monitor register for channel 9 to 12.  7 0 Res Res Res Res SD                                                                                                                                                                                                                                                                               |

Information subject to change without further notice

| Memory<br>Location<br>(hex) | EEPROM/SRAM | R/W | Default<br>Setting<br>(hex) | Name of Location                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------|-------------|-----|-----------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02                          | SRAM        | R/W | N/A                         | Channel Power Down<br>#1                     | The Channel Disable bits are used to disable individual channels. The transimpedance amplifier stage, the limiting amplifier and the CML output stage for the specific channel are turned off to reduce power consumption. When the channel is disabled, the CML outputs are both at the VOREF level and the signal detect for the channel is high. When the bit is cleared, the channels will operate according to RUN and SEL12. When RUN is low, it overrides this register and disables all channels. When RUN is high, the channels (subject to SEL12 settings) with channel disable set are powered down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 03                          | SRAM        | R/W | N/A                         | Channel Power Down<br>#2                     | The Channel Disable bits for channel 9 to 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                             |             |     |                             |                                              | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 04                          | SRAM        | R/W | 00                          | Pre-emphasis Register<br>for channel 1 & 2   | The three bits are used to set the level of pre-emphasis used for each channel. The default value on power up has pre-emphasis off. When the value of the register is set to a high value (1111) <sub>b</sub> , the amount of high frequency component being added to the bit is the maximum value for the circuits. For each register, pre-emphasis settings for two channels can be made.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 05                          | SRAM        | R/W | 00                          | Pre-emphasis Register                        | Res Res PE2 PE2 PE1 PE1 PE1 Res: Reserved  7  0  Res PE4 PE4 PE4 PE3 PE3 PE3 PE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                             |             |     |                             | for channel 3 & 4                            | Res : Reserved   PE4   PE4   PE5   P |

| 06                          | SRAM        | R/W | 00                          | Pre-emphasis Register<br>for channel 5 & 6   | 7   O     Res   Res   PE6   PE6   PE6   PE5   PE5   PE5   PE5   Res : Reserved   (1)   (0)   (2)   (1)   (0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 07                          | SRAM        | R/W | 00                          | Pre-emphasis Register<br>for channel 7 & 8   | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 08                          | SRAM        | R/W | 00                          | Pre-emphasis Register<br>for channel 9 & 10  | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 09                          | SRAM        | R/W | 00                          | Pre-emphasis Register<br>for channel 11 & 12 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Information subject to change without further notice

| Memory<br>Location<br>(hex) | EEPROM/SRAM | R/W | Default<br>Setting<br>(hex) | Name of Location                 | Function                                                                                                                                                                                                                                                                                                                         |

|-----------------------------|-------------|-----|-----------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0A                          | SRAM        | R/W | 5F                          | ID Code 1 Register               | These bits are used for the identification code (ID Code). The 11 bits are split into two registers. These registers can be written and read.                                                                                                                                                                                    |

|                             |             |     |                             |                                  | 7 0<br>M7 M6 M5 M4 M3 M2 M1 M0                                                                                                                                                                                                                                                                                                   |

|                             |             |     |                             |                                  | The default reads (00101011111).                                                                                                                                                                                                                                                                                                 |

| OB                          | SRAM        | R/W | 01                          | ID Code 2 Register               | The ID Code 2 Register contains the most significant bits of the vendor code.                                                                                                                                                                                                                                                    |

|                             |             |     |                             |                                  | 7                                                                                                                                                                                                                                                                                                                                |

|                             |             |     |                             |                                  | The default reads (00101011111).                                                                                                                                                                                                                                                                                                 |

| 0C                          | SRAM        | R/W | N/A                         | Global Signal Detect<br>Register | Only the LSB bit is valid and corresponds to SD_All. The SD_All bit is a logical AND of the signal detect of all channels. When it is high, all channels are registering signal level above I <sub>thSD</sub> . When it is low, one or more channels have signal level below I <sub>thSD</sub> . This SD_ALL bit is not latched. |

| 0D                          | SRAM        | R/W | x0                          | Increment Mode<br>Register       | The LSB bit of this register is used to enable the auto-increment mode. When the bit is set, the auto-increment mode is disabled. All other bits are not used.                                                                                                                                                                   |

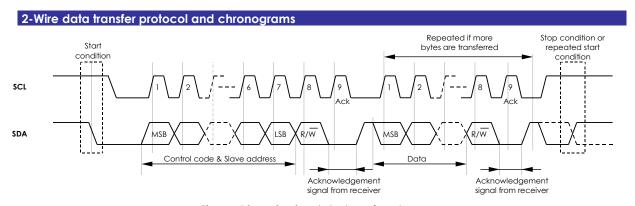

#### 2-Wire data transfer operation

The 2-wire serial port interface supports a bi-directional data transmission protocol with device addressing (Default address is  $1010010_b$ ). A device that sends data on the bus is defined as a transmitter, and a device receiving data as a receiver. The device that controls the message is called a "master." The devices that are controlled by the master are "slaves." The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The DLR-xx-251-lw-Pyz module operates as a slave on the 2-wire bus. Connections to the bus are made via the open-drain I/O lines SDA and SCLc or SCLd (when present). Timing diagrams for the 2-wire serial port can be found in Figures "2-wire data transfer protocol" and "2-wire data transfer protocol". Timing information for the 2-wire serial port is provided in the following table.

The following bus protocol has been defined:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as control signals.

Accordingly, the following bus conditions have been defined:

Bus not busy: Both data and clock lines remain HIGH.

**Start data transfer:** A change in the state of the data line from HIGH to LOW while the clock is HIGH defines a START condition.

**Stop data transfer:** A change in the state of the data line from LOW to HIGH while the clock line is HIGH defines the STOP condition.

**Data valid:** The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line can be changed during the LOW period of the clock signal. There is one clock pulse per bit of data. Figures 12 and 13 detail how data transfer is accomplished on the 2-wire bus. Depending upon the state of the R/W bit, two types of data transfer are possible.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit. Within the bus specifications a regular mode (100kHz clock rate) and a fast mode (400kHz clock rate) are defined. The SLM module works in both modes.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit. A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is a stable LOW during the HIGH period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the SLM module slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

- 1. Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the command/control byte. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte.

- 2. Data transfer from a slave transmitter to a master receiver. The master transmits the first byte (the command/control byte) to the slave. The slave then returns an acknowledge bit. Next, follows a number of data bytes transmitted by the slave to the master. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a 'not acknowledge' can be returned.

Information subject to change without further notice

The master device generates all serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus will not be released.

The DLR-xx-251-lw-Pyz-Lvv module may operate in the following two modes:

- 1. Slave receiver mode: Serial data and clock are received through SDA and SCLc or SCLd, respectively. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave (device) address (default address is 000) and direction bit. Slave transmitter mode: The first byte is received and handled as in the slave receiver mode. However, in this mode the direction bit will indicate that the transfer direction is reversed. Serial data is transmitted on SDA by the DLT module, while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer.

- 2. Slave Address: Command/control byte is the first byte received following the START condition from the master device. The command/control byte consists of a 4-bit control code. For the SLM module, this is set as 1010 binary for read/write operations. The next 3 bits of the command/control byte are the device-select bits or slave address. When reading or writing the SLM module, the device-select bits must match the device-select pins. The last bit of the command/control byte (R/W) defines the operation to be performed. When set to a 1, a read operation is selected, and when set to a 0, a write operation is selected.

Following the START condition, the DLR module monitors the SDA bus checking the device type identifier being transmitted. Upon receiving the **1010** control code, the appropriate device address bits (default address is 010), and the read/write bit, the slave device outputs an acknowledge signal on the SDA line.

#### **Module Address Presets**

The modules are delivered with two in-fab predefined device addresses selectable through the **Module Serial Interface Address Selection pin (SERADD):** The Serial Address pad selects the slave address of the serial interface that the device will respond to. When the input is low, it will respond to 7 bits address: (1010010)<sub>b</sub>. When the input is high, it will respond to 7 bits address: (1010011)<sub>b</sub>.

The SERADR can be changed only when there are no transactions on the serial interface.

Note that the I2C interface is only accessible when the JTAG interface is disabled (TRTn pin set to 0).

Figure 10 - 2-wire data transfer chronograms

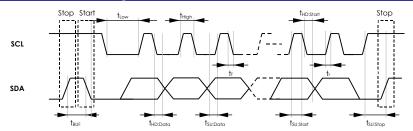

#### 2-Wire AC Characteristics and timing

Figure 11 - 2-wire data transfer chronograms

Timing table  $(-40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{V}_{CC} = 3.3\text{V})$

| Parameter              | Symbol              | Condition     | Min. | Max. | Unit | Note     |

|------------------------|---------------------|---------------|------|------|------|----------|

| Social alack fraguency | E                   | Fast mode     | 0    | 400  |      | 1        |

| Serial clock frequency | F <sub>scl</sub>    | Standard mode | 0    | 100  | kHz  | '        |

| Bus free time between  | t. <sub>BUF</sub> . | Fast mode     | 1.3  | -    | 116  | 1        |

| STOP and START         | I.BUF.              | Standard mode | 4.7  | -    | μs   | I        |

| Hold time for START    | t.,,,,,,,,          | Fast mode     | 0.6  | -    | 116  | 1,2      |

| condition              | t.HD:Start.         | Standard mode | 4.0  | -    | μs   | 1,2      |

| Low period of SCL      | +.                  | Fast mode     | 1.3  | -    | 116  | 1        |

| clock                  | t <sub>.Low</sub> . | Standard mode | 4.7  | -    | μs   | I        |

| High period of SCL     | +                   | Fast mode     | 0.6  | -    | 116  | 1        |

| clock                  | t.High.             | Standard mode | 4.0  | -    | μs   | ı        |

| Data set up time       | +                   | Fast mode     | 0    | 0.9  | 116  | 1        |

| Data set-up time       | †su:Data            | Standard mode | 0    | 0.9  | μs   | <u> </u> |

| Data hold time         | t                   | Fast mode     | 0    | 0.9  | 116  | 124      |

| Data riola firme       | †.HD:Data           | Standard mode | 0    | 0.9  | μs   | 1,3,4    |

| Set-up time for STOP   | +                   | Fast mode     | 0.6  | -    | 116  | 1        |

| and START conditions   | t.su:Stop           | Standard mode | 4.0  | -    | μs   | I        |

| Rise time              | t <sub>c</sub>      | Fast mode     | 80   | 300  | n.,  |          |

| RISE IIITIE            | l.r.                | Standard mode | 100  | 1000 | ns   | -        |

| Fall time              | +.                  | Fast mode     | 80   | 300  | n.,  |          |

| Fall time              | t.f.                | Standard mode | 100  | 1000 | ns   | -        |

| EEPROM write time      | t.w.                | -             | 5    | 20   | ms   | 5        |

#### Notes:

- A fast mode device can be used in a standard mode system, but the requirement t<sub>SU:DAT.</sub> > 250ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>RMAX</sub> + t<sub>SU:DAT.</sub> = 1000ns + 250ns = 1250ns before the SCL line is released.

- 2. After this period, the first clock pulse is generated.

- The maximum t<sub>HD:DAT</sub> has only to be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal.

- 4. A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

- 5. EEPROM write begins after a STOP condition occurs.

#### JTAG and Boundary Scan Definition

The DLR-xx-251-lw-Pyz-Lvv contains the following items, which meet the requirements, set by the IEEE-1149.1 standard Test Access Port and Boundary Scan Architecture, the IEEE 1149.6 Standard for Boundary-Scan Testing of Advanced Digital Networks as well as the AC boundary-scan Specification for IEEE from Cisco:

- Test Access Port (TAP)

- TAP Controller

- Instruction Register (3 Bit)

- Bypass Register (1 Bit)

- Boundary Scan Register (16 Bit)

- □ Device Identification Register (32 Bit)

- User Data Register (32 Bit)

- Certified 'AC Boundary Scan' as licensed from Cisco Systems, Inc.

Details on Boundary Scan Architecture and the Test Access Port can be found in IEEE 1149.1-2001, IEEE 1149.6-2003 and AC boundary-scan Specification for IEEE from Cisco (EDCS-134568 Rev B5, www.acextest.org).

#### Instruction Codes for the module Boundary Scan Architecture

| Instruction    | Selected Register     | Instruction Codes |

|----------------|-----------------------|-------------------|

| BYPASS         | Bypass                | 111               |

| EXTEST         | Boundary Scan         | 000               |

| AC_EXTEST      | AC Boundary Scan      | 100               |

| SAMPLE/PRELOAD | Boundary Scan         | 010               |

| IDCODE         | Device Identification | 001               |

| SEL_INIT_SCAN  | User Data Register    | 011               |

| EXTEST_PULSE   | AC Boundary Scan      | 101               |

| extest_train   | AC Boundary Scan      | 110               |

#### Device Identification Register (32 Bits)

| W? | В                                      |     |    |  |  |  |  |                                 |     |    |     |     |     |    |       |  |  |  |  |  |    |     |    |    |    |  |  | F2R |  |

|----|----------------------------------------|-----|----|--|--|--|--|---------------------------------|-----|----|-----|-----|-----|----|-------|--|--|--|--|--|----|-----|----|----|----|--|--|-----|--|

|    | 31                                     |     |    |  |  |  |  |                                 |     |    |     |     |     |    |       |  |  |  |  |  |    |     |    |    |    |  |  | 0   |  |

|    | Version (4 Bits) Part Number (16 Bits) |     |    |  |  |  |  | Manufacturer Identity (11 Bits) |     |    |     |     |     |    | Fixed |  |  |  |  |  |    |     |    |    |    |  |  |     |  |

|    |                                        | 000 | )1 |  |  |  |  | 00                              | 000 | 00 | 000 | 000 | 000 | 10 | 1     |  |  |  |  |  | 00 | 010 | 10 | 11 | 11 |  |  | 1   |  |

#### **Boundary Scan Register (16 Bits)**

This register contains both a shift register path and a latched parallel output for all control cells and digital I/O cells and is 16 bits in length. The table below shows all cell bit locations and definitions.

| MS | В  |       |             |             |             |             |             |             |             |             |             |             |             |             |        | LSB   |

|----|----|-------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--------|-------|

|    | 15 | 14    | 13          | 12          | 11          | 10          | 9           | 8           | 7           | 6           | 5           | 4           | 3           | 2           | 1      | 0     |

|    | -  | RUN   | A12         | A11         | A10         | A9          | A8          | A7          | A6          | A5          | A4          | A3          | A2          | A1          | SD_All | SQS   |

|    | -  | Out   | Out         | Out         | Out         | Out         | Out         | Out         | Out         | Out         | Out         | Out         | Out         | Out         | Out    | In    |

|    | -  | BC_2  | HX_BC4_DIFF | BC_2   | BC_4  |

|    |    | No AC | AC_Extest   | No AC  | No AC |

#### Notes:

BC\_4: Observe only registers

BC\_2: Control and observe registers

HEX\_BC4\_DIFF: AC Observe only registers

Information subject to change without further notice

#### User Data Register (16 Bit)

This register contains a shift register path for different control signals and is 32 bits in length. The table below shows all signals connected to the user data register.

| VIJ | D    |      |      |      |      |      |      |      |      |      |      |      |      |      |      | LJD  |

|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

|     | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|     | Res. | Res. | Res. | Res. | SD12 | SD11 | SD10 | SD9  | SD8  | SD7  | SD6  | SD5  | SD4  | SD3  | SD2  | SD1  |

|     | Read |

Notes:

Res.: Reserved bit (Logical low)

#### Channels distribution over the fiber and pigtail length

The following table shows the channel distribution over the 12 fiber ribbon configuration.

| Fiber number            | 12   | 11     | 10    | 9     | 8    | 7     | 6   | 5     | 4      | 3      | 2    | 1    |

|-------------------------|------|--------|-------|-------|------|-------|-----|-------|--------|--------|------|------|

| Color code              | Blue | Orange | Green | Brown | Grey | White | Red | Black | Yellow | Violet | Pink | Aqua |

| DLR-02- 251             |      |        |       |       |      | Rx2   | Rx1 |       |        |        |      |      |

| DLR-04-251              |      |        |       |       | Rx4  | Rx3   | Rx2 | Rx1   |        |        |      |      |

| DLR-08-251 <sup>1</sup> |      |        | Rx8   | Rx7   | Rx6  | Rx5   | Rx4 | Rx3   | Rx2    | Rx1    |      |      |

| DLR-12-251              | Rx12 | Rx11   | Rx10  | Rx9   | Rx8  | Rx7   | Rx6 | Rx5   | Rx4    | Rx3    | Rx2  | Rx1  |

lote:

1. DLR-08-251-lx-Py1-Lvv or DLR-08-251-lx-Py2-Lvv 8 channel devices based on 12 channel version with 4 channels permanently disabled.

According to the previous table, the module pin is following the same distribution (pins are for IGM package option):

- 1. For a 2 channels receiver having a fiber ribbon pigtail (DLR-02-251-lx-Py1-Lvv or DLR-02-251-lx-Py2-Lvv), the electrical input data will be distributed as stated on the table: channel #1 positive input is connected to D3+ (Pin A3) and negative input to D3- (Pin B3), channel #2 positive input is connected to D10+ (Pin B8) and negative input to D10- (Pin A8).

- 2. For a 4 channels receiver having a fiber ribbon pigtail (DLR-04-251-lx-Py1-Lvv or DLR-04-251-lx-Py2-Lvv), the electrical input data will be distributed as stated on the table: channel #1 positive input is connected to D3+ (Pin A3) and negative input to D3- (Pin B3), channel #2 positive input is connected to D8+ (Pin A5) and negative input to D8- (Pin A6), channel #3 positive input is connected to D7+ (Pin C5) and negative input to D7- (Pin C6), channel #4 positive input is connected to D10+ (Pin B8) and negative input to D10- (Pin A8).

- 3. Same for 8 channels device.

Other Optical pin-out could be proposed under customer requirements.

The following table provides the pigtail length precision per length (measure from module edge to optical end-face)

| Distail longth (one) | Standard I | Dimensions | Tight Tolerances (T option) |            |  |  |

|----------------------|------------|------------|-----------------------------|------------|--|--|

| Pigtail length (cm)  | Tolerances | Resolution | Tolerances                  | Resolution |  |  |

| 5 to 50              | +/-15mm    | 10mm       | +/-5mm                      | 1mm        |  |  |

| 50 to 100            | +/-20mm    | 15mm       | +/-10mm                     | 5mm        |  |  |

| Above 100            | +/-2%      | 15mm       | Not Available               | 10mm       |  |  |

For Tight tolerances add "T" in the part number at the end of the "-Lvv" section followed by the millimeter value: "-LvvTw" for a length of vv.w cm. For example a receiver with a pigtail of 12.3cm length will have the P/N: **DLR-12-251-lx-Pyz-L12T3**.

#### Temperature and Mechanical Qualifications

D-Lightsys modules fully complies with the following Aeronautic/harsh environment standards:

- ARINC804, extended operation range,

- MIL-STD-883e (as specified with ARINC804),

- DO-160 (as specified with ARINC804).

Refer to the ARINC804, MIL-STD-883e and DO-160 standards for further details on the qualifications.

Note that the vibrations and shocks qualification results are related to the optical termini and package selected. Selecting a non-environmental qualified optical termini and/or packaging will limit the module environmental performances. Contact sales for details or recommended package/optical termini.

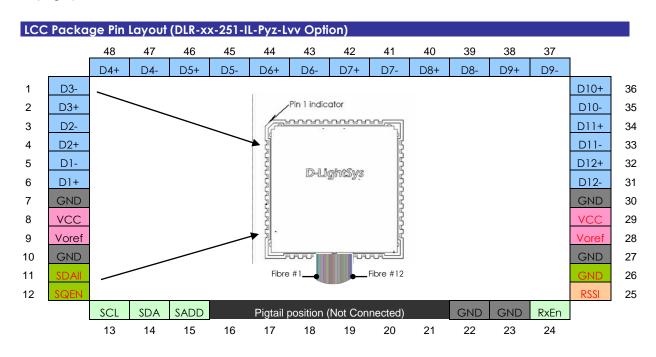

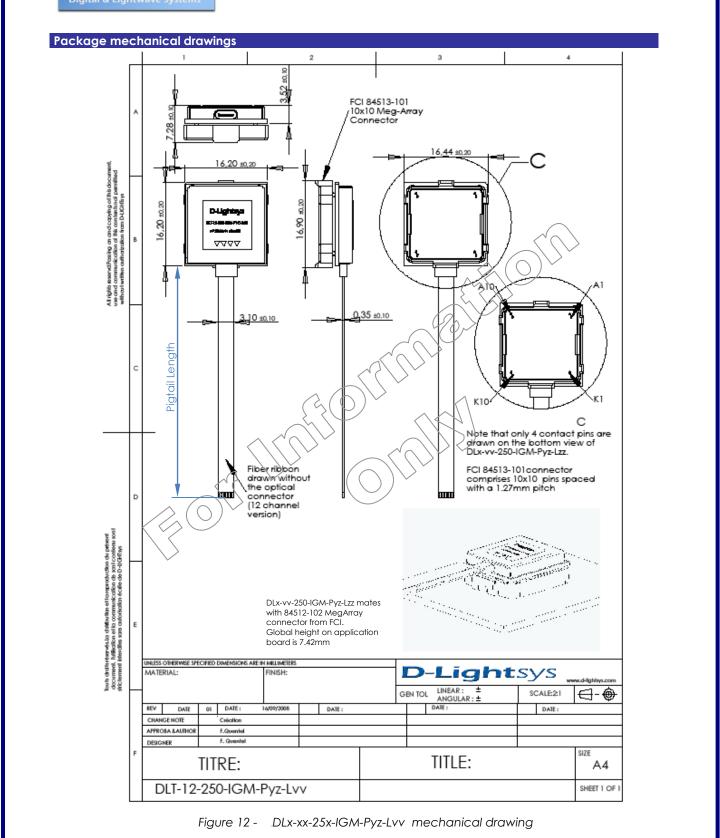

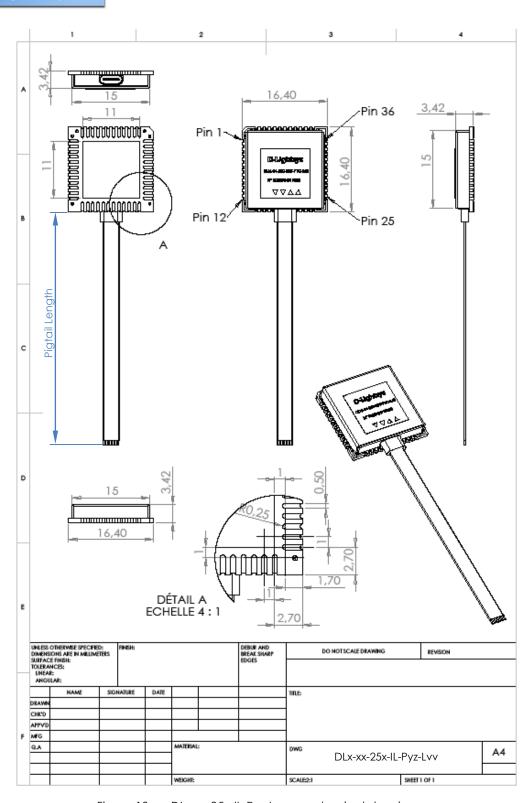

Pin out description

Information subject to change without further notice

| Signal -              | Pin nu | ımber | Туре                      |                                                                                |

|-----------------------|--------|-------|---------------------------|--------------------------------------------------------------------------------|

|                       | IGM    | IL    | Туре                      |                                                                                |

| DataOut1+ or<br>D1+   | E1     | 6     | HS. <sup>1</sup> . output | Positive Data output for channel 1: LVDS/CML positive high speed output        |

| DataOut1- or<br>D1-   | D1     | 5     | HS. <sup>1</sup> . output | Negative Data output for channel 1: LVDS/CML negative high speed output        |

| DataOut2+ or<br>D2+   | В1     | 4     | HS.1. output              | Positive Data output for channel 2: LVDS/CML positive high speed input         |

| DataOut2- or<br>D2-   | Al     | 3     | HS. <sup>1</sup> . output | Negative Data output for channel 2: LVDS/CML negative high speed output        |

| DataOut3+ or<br>D3+   | A3     | 2     | HS. <sup>1</sup> . output | Positive Data output for channel 3: LVDS/CML positive high speed output        |

| DataOut3- or<br>D3-   | В3     | 1     | HS. <sup>1</sup> . output | Negative Data output for channel 3: LVDS/CML negative high speed output        |

| DataOut4+ or<br>D4+   | D3     | 48    | HS. <sup>1</sup> . output | Positive Data output for channel 4: LVDS/CML positive high speed output        |

| DataOut4- or<br>D4-   | E3     | 47    | HS.1. output              | Negative Data output for channel 4: LVDS/CML negative high speed output        |

| DataOut5+ or<br>D5+   | G5     | 46    | HS. <sup>1</sup> . output | Positive Data output for channel 5: LVDS/CML positive high speed output        |

| DataOut5- or<br>D5-   | G6     | 45    | HS. <sup>1</sup> . output | <b>Negative Data output for channel 5:</b> LVDS/CML negative high speed output |

| DataOut6+ or<br>D6+   | E5     | 44    | HS. <sup>1</sup> . output | Positive Data output for channel 6: LVDS/CML positive high speed output        |

| Dataln6- or D6-       | E6     | 43    | HS. <sup>1</sup> . Input  | Negative Data output for channel 6: LVDS/CML negative high speed output        |

| DataOut7+ or<br>D7+   | C5     | 42    | HS. <sup>1</sup> . output | Positive Data output for channel 7: LVDS/CML positive high speed output        |

| DataOut7- or<br>D7-   | C6     | 41    | HS. <sup>1</sup> . output | <b>Negative Data output for channel 7:</b> LVDS/CML negative high speed output |

| DataOut8+ or<br>D8+   | A5     | 40    | HS. <sup>1</sup> . output | Positive Data output for channel 8: LVDS/CML positive high speed output        |

| DataOut8- or<br>D8-   | A6     | 39    | HS. <sup>1</sup> . output | Negative Data output for channel 8: LVDS/CML negative high speed output        |

| DataOut9+ or<br>D9+   | E8     | 38    | HS.1. output              | Positive Data output for channel 9: LVDS/CML positive high speed output        |

| DataOut9- or<br>D9-   | D8     | 37    | HS. <sup>1</sup> . output | Negative Data output for channel 9: LVDS/CML negative high speed output        |

| DataIn10+ or<br>D10+  | В8     | 36    | HS.1. output              | Positive Data output for channel 10: LVDS/CML positive high speed output       |

| DataOut10- or<br>D10- | A8     | 35    | HS.1. output              | Negative Data output for channel 10: LVDS/CML negative high speed output       |

| DataIn11+ or<br>D11+  | A10    | 34    | HS. <sup>1</sup> . output | Positive Data output for channel 11: LVDS/CML positive high speed output       |

| DataOut11- or<br>D11- | B10    | 33    | HS.1. output              | Negative Data output for channel 11: LVDS/CML negative high speed output       |

| DataOut12+ or<br>D12+ | D10    | 32    | HS. <sup>1</sup> . output | Positive Data output for channel 12: LVDS/CML positive high speed output       |

Information subject to change without further notice

| DataOut12- or<br>D12-     | E10 | 31 | HS. <sup>1</sup> . output    | <b>Negative Data output for channel 12:</b> LVDS/CML negative high speed output                                                                                                                                                                                                                                                                                                |

|---------------------------|-----|----|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|