# Intel<sup>®</sup> FM1010

Six-Interface SPI-4.2 Interconnect

Data Sheet

December, 2007 (Revision 2.0)

# Legal

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

The Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2011. Intel Corporation. All Rights Reserved.

# **Table of Contents**

| Product Highlights6 |            |                  |                                                                                  |      |

|---------------------|------------|------------------|----------------------------------------------------------------------------------|------|

| Applications6       |            |                  |                                                                                  |      |

| FM1                 | 010 Fe     | eatures.         |                                                                                  | 6    |

| Docu                | ument      | Revisio          | n History                                                                        | 7    |

| Prod                | luct Ai    | oplicabil        | ity                                                                              | 7    |

|                     | -          | •                | uments and Tools                                                                 |      |

| 1.0                 |            |                  | cription                                                                         |      |

|                     | 1.1        | FM1010           | ) Överview                                                                       | 9    |

|                     | 1.2<br>1.3 |                  | ) Application Example<br>ons                                                     |      |

|                     | 1.3        | 1.3.1            | Terms Defined in the OIF SPI-4.2 Implementation Agreement .                      |      |

|                     |            | 1.3.2            | Other Relevant Terms                                                             | . 13 |

| 2.0                 | Theo       | ry of Op         | peration                                                                         | 14   |

|                     | 2.1        | Operati<br>2.1.1 | ng Modes<br>Clear Mode                                                           |      |

|                     |            | 2.1.1            | Multi-Port Mode                                                                  |      |

|                     |            | 2.1.2            | Extended Multi-Port Mode                                                         |      |

|                     | 2.2        | Mixing (         | Operating Modes                                                                  |      |

| 3.0                 | Func       | tional D         | escriptions                                                                      | . 19 |

|                     | 3.1        |                  | eset and Configuration                                                           |      |

|                     |            | 3.1.1<br>3.1.2   | Chip Reset Parameters                                                            |      |

|                     |            | 3.1.2<br>3.1.3   | Reset and Configuration Procedure<br>Mode-Independent Global Start-up Parameters |      |

|                     |            | 3.1.3            | Mode-Independent SPI-4.2 Start-up Parameters                                     |      |

|                     |            | 3.1.5            | Mode-Dependent Start-up Parameters                                               |      |

|                     | 3.2        | Chip Op          | peration                                                                         |      |

|                     |            | 3.2.1            | Statistics                                                                       |      |

|                     |            | 3.2.2            | Link/Port Reset Procedure                                                        |      |

|                     | 3.3        | 3.2.3            | Interrupt Processing                                                             |      |

|                     | 3.3<br>3.4 |                  | erface                                                                           |      |

|                     | 0.1        | 3.4.1            | General Description                                                              |      |

|                     |            | 3.4.2            | Register Read/Write Operations                                                   | . 28 |

|                     |            | 3.4.3            | CPU Interface Operation                                                          |      |

|                     | <u>а г</u> | 3.4.4            | Bus Error Condition Handling                                                     |      |

|                     | 3.5<br>3.6 |                  | nterface                                                                         |      |

|                     | 5.0        | 3.6.1            | SPI-4.2 Receive and Transmit Data Path Clocks                                    |      |

|                     |            |                  | CPU Interface Clock                                                              |      |

|                     |            | 3.6.3            | JTAG Interface Clock                                                             | . 32 |

| 4.0                 |            |                  | ecifications                                                                     |      |

|                     | 4.1        |                  | e Maximum Ratings                                                                |      |

|                     | 4.2<br>4.3 |                  | nended Operating Conditions                                                      |      |

|                     | т.5        | 4.3.1            | SPI-4 Interface                                                                  |      |

|                     |            | 4.3.2            | CPU Interface, General Timing Requirements                                       |      |

|                     |            | 4.3.3            | JTAG Interface                                                                   |      |

| 5.0                 |            | ster Defi        | initions                                                                         | 39   |

|                     | 5.1        | Memory           | у Мар                                                                            | . 39 |

|     | 5.2              | FM1010  | OGlobal and CPU Interface Register Definitions | 41 |

|-----|------------------|---------|------------------------------------------------|----|

|     | 5.3              | SPI-4.2 | Interface Register Descriptions                | 43 |

|     |                  | 5.3.1   | RX_RESET                                       | 43 |

|     |                  | 5.3.2   | RX_CAL_LM                                      | 43 |

|     |                  | 5.3.3   | RX_SYNC                                        | 44 |

|     |                  | 5.3.4   | RX_DESKEW1                                     | 44 |

|     |                  | 5.3.5   | RX_DESKEW2                                     | 44 |

|     |                  | 5.3.6   | RX_DESKEW3                                     |    |

|     |                  | 5.3.7   | RX_CALS                                        |    |

|     |                  | 5.3.8   | RX_FS                                          | 46 |

|     |                  | 5.3.9   | RX_OP_MODE                                     | 46 |

|     |                  | 5.3.10  | RX_WATERMARK                                   |    |

|     |                  |         | RX_PORT2FIFO[031]                              |    |

|     |                  |         | RX_PORT_VALID[07]                              |    |

|     |                  |         | RX_STATUS_OVERRIDE                             |    |

|     |                  |         | RX_OS                                          |    |

|     |                  |         | RX_LINKCFG1[015]                               |    |

|     |                  |         | RX_LINKCFG2[015]                               |    |

|     |                  |         | RX_LINK_RESET                                  |    |

|     |                  |         | RX_PKTCNT                                      |    |

|     |                  |         | RX_PKTERRCNT                                   |    |

|     |                  |         | RX_DATACNT                                     |    |

|     |                  |         |                                                |    |

|     |                  |         | RX_IP                                          |    |

|     |                  |         | RX_IM                                          |    |

|     |                  |         | RX_DEBUG_STATUS                                |    |

|     |                  |         | TX_RESET                                       |    |

|     |                  |         | TX_CAL_LM                                      |    |

|     |                  |         | TX_SYNC0                                       |    |

|     |                  |         | TX_SYNC1                                       |    |

|     |                  |         | TX_CORE_WATERMARK                              |    |

|     |                  |         | TX_CALS                                        |    |

|     |                  |         | TX_FS                                          |    |

|     |                  |         | TX_OP_MODE                                     |    |

|     |                  |         | TX_SERVICE_LIMIT                               |    |

|     |                  |         | TX_MAX_BURST[015]                              |    |

|     |                  |         | TX_FIFO2PORT[015]                              |    |

|     |                  | 5.3.35  | TX_FIFO_VALID                                  | 59 |

|     |                  | 5.3.36  | TX_OS                                          | 60 |

|     |                  | 5.3.37  | TX_LINKCFG[015]                                | 60 |

|     |                  | 5.3.38  | TX_PKTCNT                                      | 61 |

|     |                  | 5.3.39  | TX_PKTERRCNT                                   | 61 |

|     |                  | 5.3.40  | TX_DATACNT                                     | 61 |

|     |                  |         | TX_IP                                          |    |

|     |                  | 5.3.42  | ТХ_ІМ                                          | 62 |

|     |                  |         | TX_PLL_CTRL                                    |    |

|     |                  |         | TX_PLL_STAT                                    |    |

|     | 5.4              |         | nark Recommendation                            |    |

|     | 5.5              |         | y Parity Errors                                |    |

| 4.0 |                  | -       | -                                              |    |

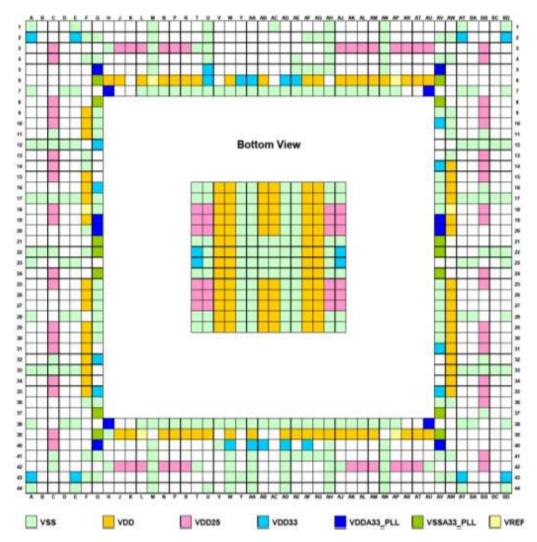

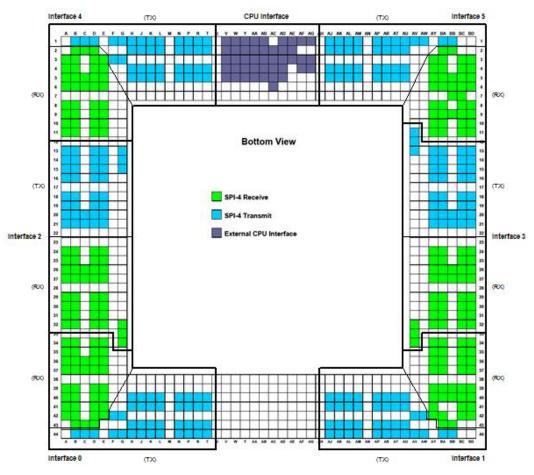

| 6.0 | <b>Signa</b> 6.1 |         | and Package Descriptions                       |    |

|     | 6.2              | 0       | apping                                         |    |

|     | 6.3              |         | ce Mapping                                     |    |

|     | 6.4              |         | Descriptions                                   |    |

|     | 0.4              | 0       |                                                |    |

|     |                  | 6.4.1   | FM1010 Signals                                 | 0/ |

|     |                  | 6.4.2   | Power Supply Pins and Recommendations          | 10 |

|     |            | 6.4.3 Ball Assignment                            | 73  |

|-----|------------|--------------------------------------------------|-----|

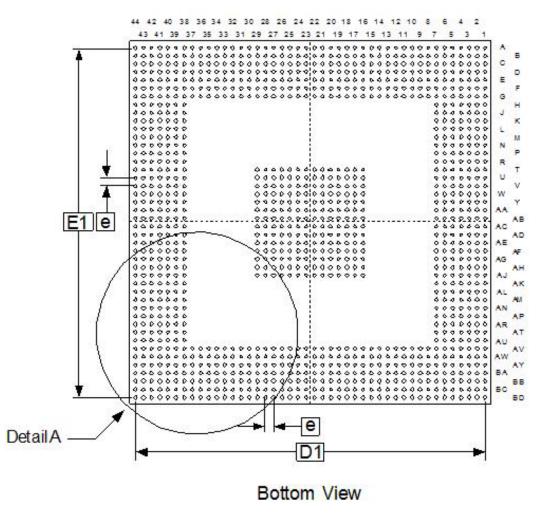

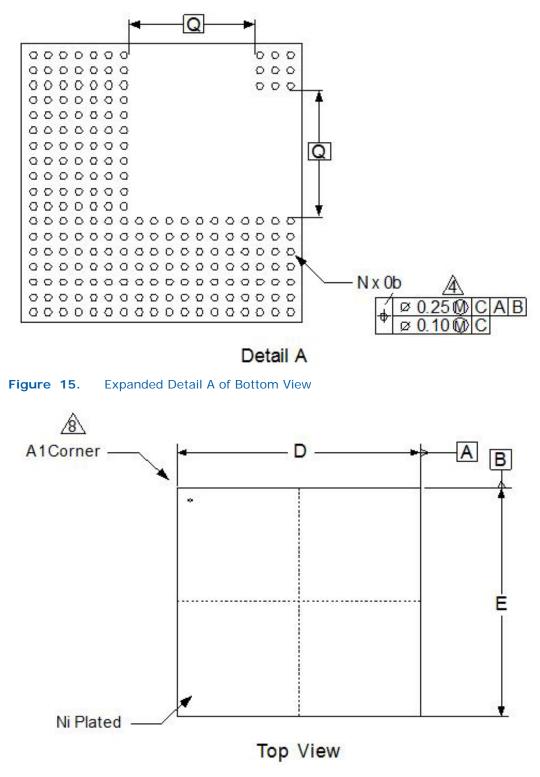

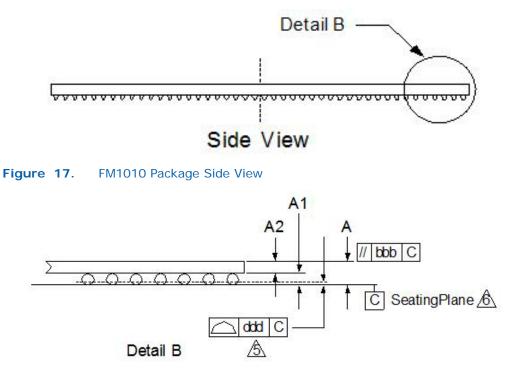

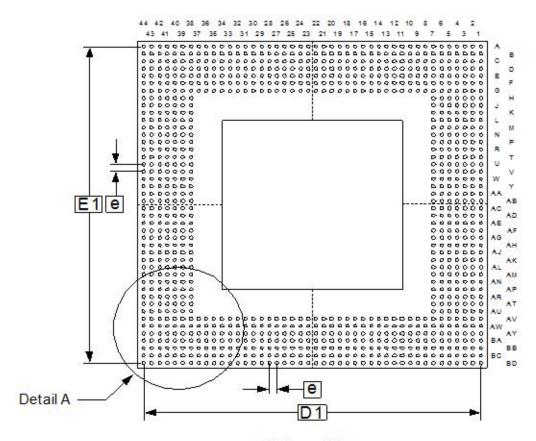

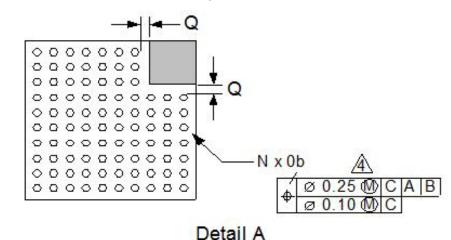

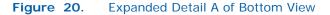

|     | 6.5        | Package Dimensions                               | 100 |

|     |            | 6.5.1 1232-Ball Version (FM1010-F1232)           | 100 |

|     |            | 6.5.2 1036-Ball Version (FM1010-F1036)           | 103 |

|     | 6.6        | Recommended Heat Sink Vendors                    | 106 |

| 7.0 | Docu       | ment Revision Information                        |     |

|     |            |                                                  |     |

|     | 7.1        | Nomenclature                                     | 107 |

|     | 7.1<br>7.2 | Nomenclature<br>Rev 1.1 to 1.2 Changes           |     |

|     |            |                                                  | 107 |

|     | 7.2        | Rev 1.1 to 1.2 Changes                           |     |

|     | 7.2<br>7.3 | Rev 1.1 to 1.2 Changes<br>Rev 1.2 to 1.3 Changes |     |

# **Product Highlights**

The FM1010 six-interface System Packet Interface Level 4 Phase 2 (SPI-4.2) interconnect is a high-performance switch-based solution for seamlessly and intelligently interconnecting multiple chips containing the SPI-4.2 interface, enabling designers to deliver sophisticated systems while significantly reducing costs, increasing system flexibility, and reducing time to market. A member of Intel's PivotPoint product family, the FM1010 converts a fixed-configuration half-duplex daisy-chain of devices with SPI-4.2 interfaces (such as NPUs, traffic managers, co-processors, search engines, custom ASICs, and FPGAs) into a dynamically-reconfigurable full-duplex resource pool, enabling more efficient use of the silicon resources, and eliminating the custom glue logic that often accompanies complex system designs.

# **Applications**

The FM1010 can be used at the blade level and for small modular systems (appliances and "pizza boxes") in high-speed communications and computing applications where the SPI-4.2 interface is used to interconnect the silicon resources in the system, for:

- Ethernet Switches and Routers

- Enterprise Compute Servers

- Enterprise Firewalls and Gateways

# FM1010 Features

#### General

- Fully connected non-blocking switch

(soft-configurable interfaces and ports)

- Six independent SPI-4.2 interfaces

- 3x internal switch fabric overspeed

- Built-in fine-grained flow control

- 1.2V core, 2.5 V LVDS and 3.3 V LVTTL operation

#### **Test and Control Features**

- 16-bit standard CPU interface

- JTAG and boundary scan support

- Support for loopback on each interface

#### Physical

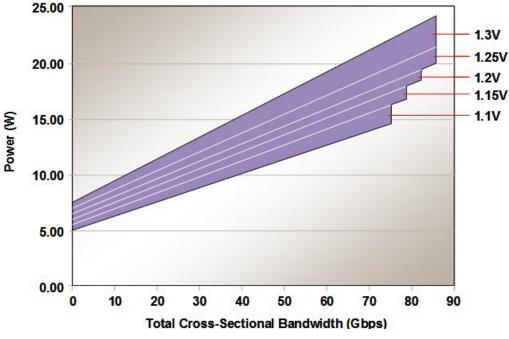

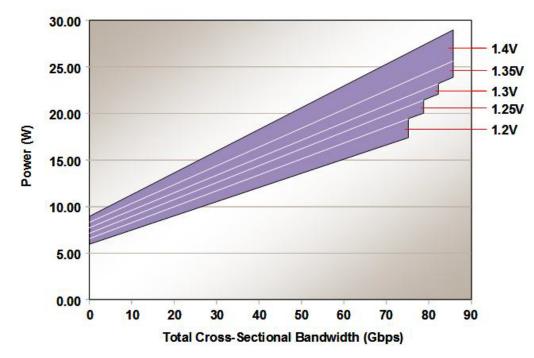

- Modest and flexible power profile

- 2 W (avg.) per active interface

#### • SAN Switches and Gateways

- Multi-Service Platforms

- Enterprise Services Appliances

#### Interface Features

- Each interface consists of a simplex RX and TX path, each of which is independently clocked

- Each interface can support data rates up to 14.4 Gb/s

- Support for dynamic and static phase alignment

- LVTTL status channel

- Configurable packet buffer (16KB ingress; 16KB egress) per interface

Up to 256 flow controlled ports

- Independent enable/disable control for each interface

- Statistics and error reporting

- •

- Power scales linearly on activity

- 130 nm CMOS process technology

- 1232-ball (and 1036-ball) BGA package

# **Document Revision History**

| Revision | Date           | Notes                                                                                                                                                                         |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0      | Dec 19, 2007   | Details in Section 7.6                                                                                                                                                        |

| 1.41     | Jan 13, 2006   | Details in Section 7.5                                                                                                                                                        |

| 1.4      | Dec 19, 2005   | Details in Section 7.4                                                                                                                                                        |

| 1.3      | May 20, 2005   | Many changes. See Section 7 for details.                                                                                                                                      |

| 1.2      | April 28, 2005 | IGNORE_DS_N pin changed sense. Made power supply names consistent.                                                                                                            |

| 1.1      | Feb 11, 2005   | Part numbers updated, and new package information added.<br>Several register descriptions updated. Specification updates<br>described in document FM1010-SU-001 incorporated. |

| 1.0      | Sept 28, 2004  | Characterization and qualification data incorporated. All features and operations have been verified.                                                                         |

| 0.9      | Feb 10, 2004   | Advance information datasheet.                                                                                                                                                |

| 0.2      | July 7, 2003   | Preliminary datasheet. Limited distribution.                                                                                                                                  |

# **Product Applicability**

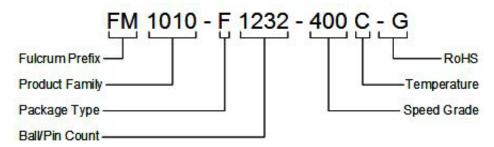

This data sheet documents the features and functionality of all generally-available versions of the PivotPoint FM1010 product family. The PivotPoint FM1010 part number is structured as follows:

Unless specifically noted, the contents of this data sheet apply to all product variants, which include all versions of FM1010-F1036 and FM1010-F1232.

For documentation on the original FM1010 package based on wire-bond package technology (labeled as "FM1010"), refer to the following documents:

| FM1010-DS-1.0: | FM1010 Data Sheet, version 1.0 |

|----------------|--------------------------------|

|----------------|--------------------------------|

FM1010-SU-001: FM1010 Specification Update, version 001

• FM10x0-DG-1.0: FM1010 and FM1020 Design Guide, version 1.0

# **Other Related Documents and Tools**

Other documents that may be useful for evaluating and using the FM1010 include:

- FM1010 Specification Update, which contains errata and other specification and documentation changes (document: FM1010-SU)

- FM1010 and FM1020 Design and Layout Guide (document: FM10x0-DG)

- FM1010 and FM1020 Evaluation Platform Data Sheet (document: FM10x0-EP-DS)

- FM1010 Hardware Development Kit CD (order number: FM1010-HDK)

# 1.0 General Description

# 1.1 FM1010 Overview

The PivotPoint FM1010 is a configurable six-interface System Packet Interface Level 4 Phase 2 (SPI-4.2) switch chip, which provides configurable connectivity between a variety of chips in a system at full line rate and with minimal additional latency. The switching is accomplished on an interface or port / interface pair basis based on a software-configurable port mapping. No inspection or interpretation of the payload within the SPI-4.2 packet is required, except to the extent required to determine the SPI-4.2 port identification.

Each SPI-4.2 electrical interface operates up to 450 MHz (approximately 14.4 Gb/s throughput). Each SPI-4.2 interface is composed of two simplex interfaces (a transmit and a receive), each of which may operate at an independent frequency from all other interfaces. The calendar status channel for each SPI-4.2 interface is a 1/4 frequency LVTTL implementation. The calendar length, multiplicity, and entries are configured when the SPI-4.2 interface is initialized or reset.

Each SPI-4.2 interface on the FM1010 supports three modes of operation: Clear (where a single port is active on the interface), and multi-port mode (where multiple ports are active, up to 16 ports per interface), and extended multi-port mode (where multiple ports are active, up to 256 ports per interface).

**Clear Mode:** In Clear mode, the entire SPI-4.2 interface is mapped to a single port and the port ID field in the SPI-4.2 packet is ignored.

**Multi-port Mode:** Multi-port mode routes all packets with different SPI-4.2 port IDs independently of the others as if the packets were sent over unrelated interfaces. There is no ordering relationship, and thus no blocking between SPI-4.2 packets with different port IDs. All of the flow control information is maintained for each active port, and thus, to be effective, the external SPI-4.2 devices must support multiport operation. The FM1010 contains up to 16 FIFOs per interface and thus supports up to 16 ports per interface, each of which can be any available port of the 256 total port IDs specified in the OIF SPI-4.2 Implementation Agreement.

**Extended Multi-port Mode:** Extended Multi-port Mode operates identically to Multi-port mode, with the extended ability to support up to 256 ports per interface, mapped as appropriate to the 16 available FIFOs per interface.

Additionally, the FM1010 can be configured to reassign port IDs as packets flow through the system.

The FM1010 also contains a standard 16-bit address/data processor bus interface that is used to read and write all Control Status Registers that control the chip configuration and operation, and also to obtain status and to debug the chip. This CPU interface can be configured to support a variety of commercial processors including the Motorola MPC8260, and MPC860, IBM PowerPCs with an EBC bus, and various I/ O bridge chips (such as the PLX 9030 PCI bridge chip from PLX Technologies). The different modes are supported through pin strapping options. This CPU interface operates up to 100 MHz.

Lastly, the FM1010 implements an industry-standard JTAG controller for test and design debug. The JTAG controller can access boundary scan registers and all internal registers.

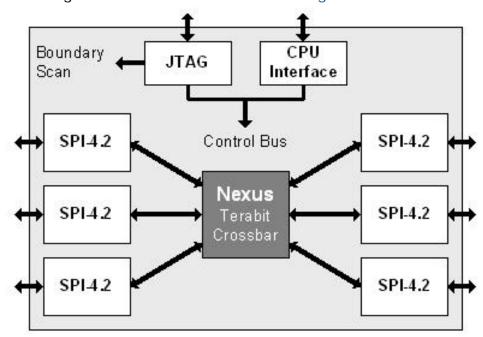

A block diagram of the FM1010 is shown in Figure 1.

Figure 1. FM1010 Block Diagram

The FM1010 contains six independent SPI-4.2 interfaces connected together through Nexus (Intel's terabit crossbar). An integrated JTAG interface provides standards-based test and debug, and a generic CPU interface provides access to the FM1010 Configuration and Status Registers via a variety of standard processors.

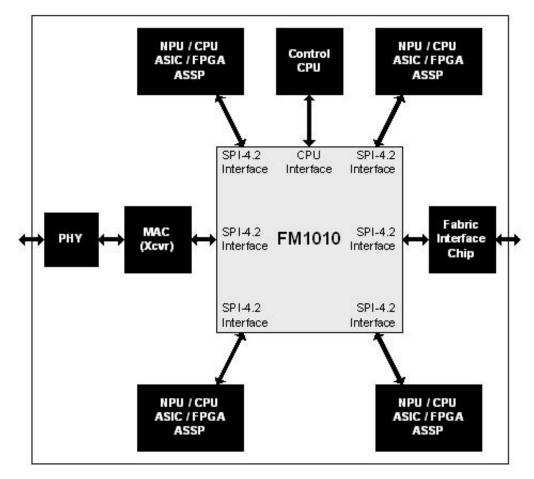

# 1.2 FM1010 Application Example

The FM1010 enables as many as six SPI-4.2-compliant devices to be interconnected at rates up to 14.4 Gb/s per interface. The FM1010 transparently handles rate mismatch between the different interfaces

with a combination of low-latency buffers and end-to-end flow control. Simple interface and port assignment through a standard CPU interface allows the system to be reconfigured for different applications, allowing the hardware to optimally match the application.

The FM1010 is configured by the Control CPU by writing its control registers through the CPU interface. Each SPI-4.2 interface may operate in clear or multi-port mode independently. Links are established between attached SPI-4.2 devices through port assignment. Multiple ports may be used to support QoS differentiated links between the same two external SPI-4.2 devices provided that the external devices have an ability to assign and support multiple ports within a SPI-4.2 interface. The FM1010 interface and port assignment may be soft reconfigured during device operation.

An FM1010 system-level block diagram of a sample generic "blade" is shown in Figure 2.

The FM1010 can be integrated into a blade or "pizza box" application and convert a fixed hardware configuration into a soft-configurable pool of silicon resources. Low latency, high throughput, and independent interfaces with independent clock rates make the FM1010 a versatile platform for rapidly delivering configurable hardware platforms.

# 1.3 Definitions

The following are terms that are relevant for the FM1010, and which are used throughout this document to describe the features, functions, configuration, and use of the FM1010.

## 1.3.1 Terms Defined in the OIF SPI-4.2 Implementation Agreement

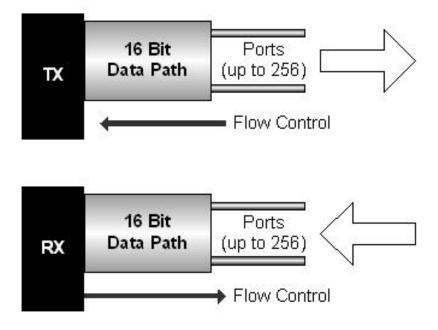

Figure 3 depicts the components defined in the Optical Internetworking Forum (OIF) System Packet Interface Level 4 Phase 2 (SPI-4.2) Implementation Agreement. The terminology defined by the OIF is used throughout this document, including the term "port" which refers to a logical partition (or allocated portion) of a physical interface.

The Optical Internetworking Forum defined the SPI-4.2 interface originally for interconnecting physical layer devices with link layer devices. Due to the versatility defined into the interface (including multiple ports, each with independent flow control) designers have extended their use of SPI-4.2 to the entire data path in a variety of high-speed streaming data applications.

| Interface        | A single SPI-4.2 physical implementation containing a transmit<br>and receive data path and a separate status interface for flow<br>control for each direction.                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port             | A logical partition (or allocated portion) of a physical interface.<br>A physical SPI-4.2 interface can contain up to 256 logical ports.<br>Generally, status control is supported on a per-port basis so that<br>each interface can support multiple flows without ports blocking<br>each other. |

| Channel          | A commonly used synonym for "Port". Not defined in the OIF SPI-4.2 Implementation Agreement.                                                                                                                                                                                                      |

| Status Interface | A separate path between sending and receiving SPI-4.2 interfaces used to provide flow control and to report the status of FIFOs in the connected interfaces.                                                                                                                                      |

| Flow Control     | Supported through the Status Interface, as described above.                                                                                                                                                                                                                                       |

|                  |                                                                                                                                                                                                                                                                                                   |

# 1.3.2 Other Relevant Terms

| CSR (Register) | Control Status Register used for configuration, status reporting, and debug.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nexus          | Intel's Terabit fully-connected non-blocking crossbar; Nexus is the core of PivotPoint.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EOP            | End of Packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SOP            | Start of Packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Queue          | A temporary packet storage element in the SPI-4.2 interface (a.k.a., FIFO). In the FM1010, queues are located on the transmit and receive data paths of each SPI-4.2 interface.                                                                                                                                                                                                                                                                                                                           |

| Clear          | A mode of operation on the SPI-4.2 interface where the Port ID is ignored and all of the data on an interface is transported as a single stream to either a single egress port or an egress interface.                                                                                                                                                                                                                                                                                                    |

| Multi-Port     | A mode of operation on the SPI-4.2 interface where each<br>interface can contain multiple active ports which can be mapped<br>independently of each other to any available port on any other<br>interface. In this mode, the Port IDs are used to route data from<br>ingress queue to egress queue through the FM1010, and flow<br>control is enforced on a port-by-port basis. (Extended multi-port<br>mode leverages the 16 FIFOs available per interface to support<br>up to 256 ports per interface.) |

| Cut Through    | A switching mode or architecture where the packet can be<br>delivered to the destination port without being stored, as soon<br>as the destination address can be determined from the packet<br>header.                                                                                                                                                                                                                                                                                                    |

# 2.0 Theory of Operation

SPI-4.2 is a point-to-point streaming interface standard defined by the Optical Internetworking Forum for efficiently connecting together high-speed data path devices. The interface operates from 9.9 Gb/s to 16 Gb/s, having a 16-bit LVDS data path and a separate out-of-band LVTTL status channel. Since the data path is dual data rate, the interface operates from 311 to 500 MHz. The protocol supports up to 256 ports per interface, each of which can optionally be independently flow-controlled.

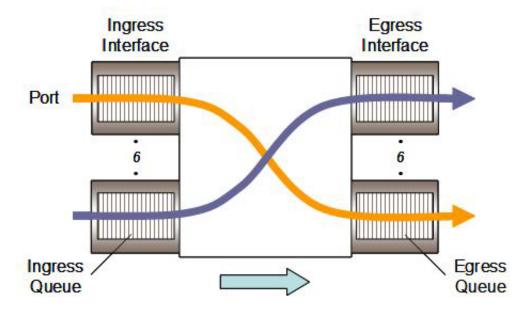

The FM1010 is a transparent SPI-4.2 interconnect. When inserted between two neighboring SPI-4.2 devices, it can switch each port on each interface independently and completely transparent to the neighboring devices. The FM1010 bridges between the flow control domains on its ingress and egress paths using Intel's high-capacity non-blocking crossbar circuit, Nexus.

Each SPI-4.2 interface of the FM1010 implements a transmit interface and a receive interface that operate independently as two simplex interfaces, each with full buffering (ingress and egress queues) and flow control. Packet data is transported efficiently from any interface (and port) to any other interface (and port) through Intel's fullyconnected, non-blocking crossbar - Nexus - using an efficient and lowoverhead message-passing system. The internal protocol and switching system is transparent to the application. Its operation is described in this document only to the extent that is required for the designer to use the FM1010 in application.

Each SPI-4.2 queue must have the routing configuration -- the pairing of ingress queues to egress queues -- pre-configured. There must be a unique pairing for each active egress queue to an appropriate ingress queue. Each queue has a producer and consumer pointer, which is passed across the Nexus as needed. For each ingress queue, the destination interface and egress queue are configured. Similarly the destination egress queue must be configured to identify where the consumer pointer updates shall be sent. All packet switching within the FM1010 is based on the user-defined queue-to-queue port map, which begins switching once the ingress burst has been placed in an ingress queue.

# 2.1 Operating Modes

The SPI-4.2 interface supports three modes of operation:

- Clear mode (where an entire interface is connected to a second interface or a single port on an interface with no port relevance)

- Multi-port mode (where packets are routed between multiple SPI-4.2 interfaces based on Port ID, where each interface can support up to 16 active and independent ports)

- Extended Multi-port mode (where packets are routed between multiple SPI-4.2 interfaces based on Port ID, where each interface can support up to 256 active and somewhat independent ports)

- *Note:* The mode of operation can be configured per SPI-4.2 interface, and per transmit and receive block. The FM1010 can support mixing modes among different interfaces, given certain operating constraints described later in this section.

#### 2.1.1 Clear Mode

In Clear mode, static routing is used (configured on a per-ingressinterface basis) to determine to which egress SPI-4.2 interface (and optionally to which port) the packet is to be delivered, as shown in Figure 4. This mode is constrained to a one-to-one correspondence between an egress interface and an ingress interface (that is no more than one ingress interface may be mapped to a given egress interface). The Port ID information is transported with the packet, but is not used for any routing decisions.

The egress SPI-4.2 interface will send out the packet in configurablesized SPI-4.2 bursts as credits are available from the SPI-4.2 status channel. The FM1010 is cut-through in its operation. The only restriction is that the complete packet must be transmitted before switching ports, a restriction which is inherently met because the ingress interface receives (and enforces via packet termination if necessary) complete packets per Port ID, and because there is only a one-to-one configured relationship between an egress interface and a single ingress interface.

All incoming SPI-4.2 bursts are stored in a single incoming RX queue in the SPI-4.2 interface. The ingress sends out status for a single queue (FIFO) on the SPI-4.2 status channel. The ingress queue may be configured as a single 1K, 2K, 4K, 8K or 16K Byte queue.

In this mode all port information is ignored.

Figure 4. Clear Mode Supported within the FM1010

In this example, all of the interfaces are configured in Clear mode, where a single queue is defined for each interface. In Clear mode, the queue of an ingress interface is mapped to the queue of an egress interface. This mode is the most efficient method for transporting all of the traffic from one chip to another, where both chips are configured with link-level flow control.

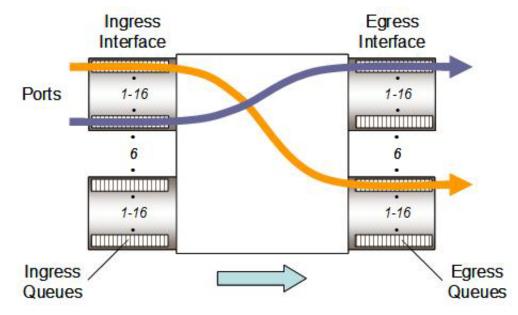

## 2.1.2 Multi-Port Mode

Multi-port mode offers the most flexibility in operation, and is the default mode of the FM1010. In Multi-port mode, each SPI-4.2 transmit and receive interface can support up to 16 fully-flow-controlled SPI-4.2 ports, as shown in Figure 5. The ports can be any 16 of the Port IDs from 0 to 255; they don't need to be contiguous, nor defined in any particular order. Each configured port has a dedicated ingress and egress queue. The size of each queue depends on the number of active ports defined per interface.

The SPI-4.2 status calendar length, multiplicity and entry organization can be set to accommodate ports operating at different rates. A calendar length of up to 255 is supported. SPI-4.2 credit status is distributed on a per-port basis according to the calendar. Packets being sent over the SPI-4.2 interface can be sent as interleaved SPI-4.2 bursts of different ports per the OIF SPI-4.2 specification.

In Multi-port mode, the size of the ingress and egress queues must be set, generally according to the number of active ports being supported per interface. Each SPI-4.2 ingress and egress interface can be configured differently; the interfaces need not be symmetrically

configured. The size may be set to 1K, 2K, 4K, 8K, or 16K Bytes per queue, which corresponds to a maximum of 16, 8, 4, 2, or 1 active ports, respectively. Note the word maximum, as fewer ports may be configured and in use than the maximum. Refer to **RX\_FS** (page 46) for correspondence between number of FIFOs and the FIFO size.

Figure 5. Multi-port Mode Supported Within the FM1010

In this example, all of the interfaces are configured in Multi-port mode, where each ingress interface is configured to support 1, 2, 4, 8, or 16 ports, each egress interface is also configured independently to support 1, 2, 4, 8, or 16 ports, and the queues for each ingress interface are mapped to the appropriate queues for each egress interface. This mode can be used to support source routing between connected chips, where each chip can assign a Port ID to transmitted packets which get switched by the FM1010 and delivered to the appropriate egress interface and port.

## 2.1.3 Extended Multi-Port Mode

Extended multi-port mode operates identically to multi-port mode, with the additional ability to map multiple ports to a single FIFO, allowing an interface to support up to 256 active ports that are mapped to up to 16 active FIFOs per interface. This mode can be used in applications where a relatively large number of moderately-active ports are supported.

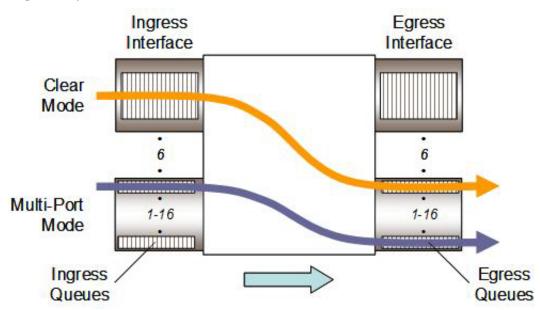

# 2.2 Mixing Operating Modes

The FM1010 supports mixing modes of operation within certain constraints, as follows:

- An ingress interface configured in Clear mode may be mapped to a single port on an egress interface configured in Multi-port mode.

- A single port on an ingress interface configured in Multi-port mode may be mapped to an egress interface configured in Clear mode.

#### Figure 6 provides further clarification.

Figure 6. Mapping Between Clear and Multi-port Interfaces

In this example, an ingress interface in Clear mode is connected to an egress interface in Multi-port mode, and vice versa. In the first example, the single queue of the ingress interface in Clear mode is mapped to a single available queue on the egress interface in Multi-port mode. In the second example, a single available queue on the ingress interface in Multi-port mode is mapped to the single queue of the egress interface in Clear mode. This configuration flexibility enables designers to support special applications such as multiplexing streams from multiple devices onto a single interface for delivery to a single connected device. Once a clear interface is mapped to a port of a Multiport interface, the Port IDs of the stream from the clear interface to the multi-port interface are overwritten with the Port ID of the mapped port of the Multi-port interface. In the other direction, the Port IDs on the clear interface is set to 0.

# 3.0 Functional Descriptions

This section describes the high-level functionality, including basic configuration guidelines, for the FM1010.

There are four main tasks associated with configuring the device:

- 1. Reset the Chip

- 2. Configure the SPI-4.2 interfaces

- 3. Map SPI-4.2 ports to FIFOs

- 4. Map FIFOs to FIFOs

The following sections describe these tasks in detail and in the context of global, mode-independent, and mode-dependent start-up parameters.

Additionally, there are registers used for statistics and interrupts. And finally there is a procedure for link reconfiguration, a feature that allows channel remapping during device operation.

Table 1 shows a list of registers and the basic description of their role in the FM1010. Refer to Chapter 5 for more detailed register information.

| Table 1. | FM1010 Register Summary |

|----------|-------------------------|

|          | Global Registers        |

| Global Registers |           |                                 |  |  |

|------------------|-----------|---------------------------------|--|--|

| Name             | Table Ref | Description                     |  |  |

| VPD              | Table 19  | Vital Product Data              |  |  |

| INTR_DETECT      | Table 18  | Interrupt Detect                |  |  |

| CPU_INTERFACE_IM | Table 16  | CPU Interface Interrupt Mask    |  |  |

| CPU_INTERFACE_IP | Table 17  | CPU Interface Interrupt Pending |  |  |

| SPI4_WATCHDOG    | Table 15  | SPI.4-2 Watchdog configuration  |  |  |

| SPI-4.2 Receive Interface Registers (one set per SPI-4.2 interface) |          |                                          |  |  |

|---------------------------------------------------------------------|----------|------------------------------------------|--|--|

| Name                                                                | Page Ref | Description                              |  |  |

| RX_RESET                                                            | 43       | Receive Interface Reset                  |  |  |

| RX_CAL_LM                                                           | 43       | Receive Calendar Length and Multiplicity |  |  |

| RX_SYNC                                                             | 44       | Receive Interface synchronization status |  |  |

| RX_DESKEW1                                                          | 44       | Static Deskew Configuration #1           |  |  |

| RX_DESKEW2                                                          | 44       | Static Deskew Configuration #2           |  |  |

| RX_DESKEW3                                                          | 45       | Static Deskew Configuration #3           |  |  |

| RX_CALS[j] {031}                                                    | 45       | Receive Interface Calendar               |  |  |

| RX_FS                                                               | 46       | Receive FIFO Size                        |  |  |

| RX_OP_MODE                                                          | 46       | Receive Interface Operational Mode       |  |  |

| RX_WATERMARK                                                        | 46       | Receive FIFO Watermark                   |  |  |

| RX_PORT2FIFO[j] {031}                                               | 47       | Receive Port to FIFO Mapping             |  |  |

| SPI-4.2 Receive Interface Registers (one set per SPI-4.2 interface) |          |                                       |  |  |  |

|---------------------------------------------------------------------|----------|---------------------------------------|--|--|--|

| Name                                                                | Page Ref | Description                           |  |  |  |

| RX_PORT_VALID[j] {07}                                               | 47       | Receive Port Usage                    |  |  |  |

| RX_STATUS_OVERRIDE                                                  | 48       | Receive FIFO Flow Control Override    |  |  |  |

| RX_OS                                                               | 49       | Receive Interface Status              |  |  |  |

| RX_LINKCFG1[j] {015}                                                | 49       | Mapping from RX FIFO to TX FIFO       |  |  |  |

| RX_LINKCFG2[j] {015}                                                | 50       | Additional Information in FIFO Map    |  |  |  |

| RX_LINKRESET                                                        | 50       | Receive Link Reset                    |  |  |  |

| RX_PKTCNT                                                           | 51       | Receive Packet Count Statistics       |  |  |  |

| RX_PKTERRCNT                                                        | 51       | Receive Error Packet Count Statistics |  |  |  |

| RX_DATACNT                                                          | 52       | Receive Byte Count Statistics         |  |  |  |

| RX_IP                                                               | 52       | Receive Interrupt Pending             |  |  |  |

| RX_IM                                                               | 53       | Receive Interrupt Mask                |  |  |  |

| RX_DEBUG_STATUS                                                     | 53       | Receive Interrupt Status              |  |  |  |

| SPI-4.2 Transmit Interface Registers (one set per SPI-4.2 interface) |          |                                           |  |  |  |

|----------------------------------------------------------------------|----------|-------------------------------------------|--|--|--|

| Name                                                                 | Page Ref | Description                               |  |  |  |

| TX_RESET                                                             | 55       | Transmit Interface Reset                  |  |  |  |

| TX_CAL_LM                                                            | 55       | Transmit Calendar Length and Multiplicity |  |  |  |

| TX_SYNC0                                                             | 55       | Transmit Synchronization Configuration    |  |  |  |

| TX_SYNC1                                                             | 56       | Transmit Interface's Training Interval    |  |  |  |

| TX_CORE_WATERMARK                                                    | 56       | Reserved                                  |  |  |  |

| TX_CALS[j] {031}                                                     | 57       | Transmit Calendar                         |  |  |  |

| TX_FS                                                                | 57       | Transmit FIFO Size                        |  |  |  |

| TX_OP_MODE                                                           | 58       | Transmit Operational Mode                 |  |  |  |

| TX_SERVICE_LIMIT                                                     | 58       | Transmit Service Limit per FIFO           |  |  |  |

| TX_MAX_BURST[j] {015}                                                | 59       | Transmit Credit Refill per Status         |  |  |  |

| TX_FIFO2PORT[j] {015}                                                | 59       | Transmit FIFO to SPI-4.2 Port Map         |  |  |  |

| TX_FIFO_VALID                                                        | 59       | Transmit FIFO Usage                       |  |  |  |

| TX_OS                                                                | 60       | Transmit Interface Operational Status     |  |  |  |

| TX_LINKCFG[j] {015}                                                  | 60       | Transmit FIFO to Receive FIFO Map         |  |  |  |

| TX_PKTCNT                                                            | 61       | Transmit Packet Count Statistics          |  |  |  |

| TX_PKTERRCNT                                                         | 61       | Transmit Error Packet Count Statistics    |  |  |  |

| TX_DATACNT                                                           | 61       | Transmit Byte Count Statistics            |  |  |  |

| TX_IP                                                                | 62       | Transmit Interface Interrupt Pending      |  |  |  |

| TX_IM                                                                | 62       | Transmit Interface Interrupt Mask         |  |  |  |

| TX_PLL_CTRL                                                          | 62       | Transmit PLL Control                      |  |  |  |

| TX_PLL_STAT                                                          | 63       | Transmit PLL Statistics                   |  |  |  |

# 3.1 Chip Reset and Configuration

This section provides details on how to reset and configure the FM1010 globally, and for various modes of operation.

## 3.1.1 Chip Reset Parameters

Table 2 lists a summary of all reset signals associated with the FM1010. Please see the appropriate sections for a detailed description of the functionality of each.

Table 2. FM1010 Reset Signals

| Name            | Туре                   | Description/ Comments                                                                                                                                            |

|-----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHIP_RESET_N    | Chip Input             | Chip reset that resets all logic. Active low.                                                                                                                    |

| CPU_BUS_RESET_N | Chip input             | Electrical Reset for the CPU bus interface only.<br>Active low. This is a subset of CHIP_RESET_N.<br>Asserting CHIP_RESET_N automatically resets the<br>CPU bus. |

| TX_PLL_CTRL     | Register (1 per SPI-4) | Control register for PLL in the TX SPI-4.2 interface.                                                                                                            |

| TX_PLL_STAT     | Register (1 per SPI-4) | Status register for PLL in the TX SPI-4.2 interface.                                                                                                             |

| RX_RESET        | Register (1 per SPI-4) | Resets a RX SPI-4.2 interface. Active high. This register defaults to asserted on chip reset.                                                                    |

| TX_RESET        | Register (1 per SPI-4) | Resets a TX SPI-4.2 interface. Active high. This register defaults to asserted on chip reset.                                                                    |

# 3.1.2 Reset and Configuration Procedure

The following is the recommended procedure for resetting and configuring the FM1010. The procedure is generally accomplished in three phases: (1) Reset; (2) Mode-independent configuration; and (3) Mode-dependent configuration, as follows:

- 1. Apply power to the FM1010 and IO pins keeping CHIP\_RESET\_N asserted.

- 2. Wait a minimum of 100 ns before de-asserting **CHIP\_RESET\_N**, and then wait at least 4 full CPU Bus clock cycles before activating the CPU Bus functional signals.

*Note:* If using JTAG, also wait 4 JTAG clock cycles after CHIP\_RESET before operating the JTAG interface.

- 3. Per active SPI-4.2 interface, configure the PLL controls in **TX\_PLL\_CTRL** (page 62).

- 4. Check the operation of the PLL by polling the **TX\_PLL\_STAT** (page 63) to determine whether the lock bit has been set. The lock bit signifies that the PLL has properly locked on the requested frequency.

- *Notes:* (1) One must wait at least 100ms after configuring the PLL control registers before polling the signal **TX\_PLL\_STAT** to allow it to stabilize.

(2) The Lock Pins can be used instead of polling TX\_PLL\_STAT to determine whether the PLL has properly locked on the requested frequency. The pins can also be used to drive status LEDs.

- 5. Configure the desired SPI-4.2 physical layer and SPI-4.2 mode-dependent switching layer registers (page 21), while leaving **TX\_RESET** and **RX\_RESET** asserted.

- 6. After the set-up configuration, enable the corresponding SPI-4.2 interfaces by deasserting the **RX\_RESET**s and **TX\_RESET**s. This will start training on the SPI-4.2 physical interfaces to gain synchronization.

- *Notes:* (1) There is no order dependency between RX\_RESET and TX\_RESET; they are independent interfaces, and can be de-asserted in either order.

(2) It is recommended that the TDCLK on the TX interfaces of the devices connected to PivotPoint be present prior to de-asserting the RX\_RESET on PivotPoint to ensure that the RDCLK is active. If the RDCLK on an interface is inactive, the watchdog must be disabled when de-asserting RX\_RESET. Otherwise, if the RDCLK is active, the watchdog state doesn't matter.

(3) The FM1010 is operational once the training sequences are complete and synchronization has been obtained on the SPI-4.2 interfaces. This can be determined by reading the status registers, **RX\_OS** (page 49) and **TX\_OS** (page 60).

#### 3.1.3 Mode-Independent Global Start-up Parameters

Note that all interrupt mask registers, including **CPU\_INTERFACE\_IM** (page 41), **RX\_IM** (page 53), and **TX\_IM** (page 62) default to masks on, and should only be set to masks off during device operation to avoid spurious interrupts that would occur during start-up.

Set the **SPI4\_WATCHDOG** register (page 41) to activate the watchdog on all active SPI-4.2 ports. Some control and status register operations require the SPI-4.2 watchdog to be active if the link is not yet in operation. Activating the watchdog will have no undesirable effects on interrupts during setup as long as the interrupt mask registers have not yet been set to the active interrupt state.

*Note:* The SPI4\_WATCHDOG uses the least significant 6 bits, where bit 0 enables the watchdog for interface 0, bit 1 enables the watchdog for interface 1, and so forth.

#### 3.1.4 Mode-Independent SPI-4.2 Start-up Parameters

The SPI-4.2 interface defaults to dynamic deskew. If it is desired to operate the FM1010 with static deskew on any receive interface, then for that RX SPI-4.2 interface set the registers **RX\_DESKEW1** (page 44), **RX\_DESKEW2** (page 44), and **RX\_DESKEW3** (page 44). The first register configures the manual deskew mode, and all three registers together determine the tap points for data lanes.

SPI-4.2 synchronization is based on correctly receiving DIP4 and DIP2 frames. **MIN\_GOOD\_PARITY** (MGP) is the number of correct DIP4 frames received before declaring synchronization, and **MAX\_BAD\_PARITY** (MBP) is the number of incorrect DIP4 frames received before declaring loss of synchronization. The register **RX\_SYNC** (page 44) has fields for MGP and MBP on the RX side. The register **TX\_SYNCO** (page 55) has MGP and MBP for the TX side as well

as the data training multiplicity. The **TX\_SYNC1** (page 56) register contains the **MAX\_DATA\_T** parameter, which is the number of SPI-4.2 clock cycles between training sequences. Both synchronization registers have reasonable default values. These registers only need to be configured in the event that it is desired to operate the FM1010 outside of the synchronization defaults.

*Note:* It is not necessary to set any registers on unused SPI-4.2 interfaces.

#### 3.1.5 Mode-Dependent Start-up Parameters

SPI-4.2 is a dual simplex interface. The FM1010 provides six full-duplex SPI-4.2 interfaces, which means there are 12 totally independent simplex interfaces, six of which are TX, and six of which are RX. The FM1010 allows each of its 12 simplex interfaces to be configured independently, including configuring the number of active ports per interface. The FM1010 can have a mixture of Clear and Multi-port modes communicating with each other.

#### 3.1.5.1 Multi-port

There are many ways to configure multi-port mode. The following procedure is a guide to programming multi-port mode in typical configurations.

1. Leave the (M) field **RX\_OP\_MODE** (page 46) and **TX\_OP\_MODE** (page 58) unmodified.

Rationale: The mode fields (M) of **RX\_OP\_MODE** and **TX\_OP\_MODE** default to Multi-port after chip reset, and do not need to be set on start-up.

Set the calendar length field and optionally set the multiplicity field of RX\_CAL\_LM (page 43) and TX\_CAL\_LM (page 55) and set the calendar in RX\_CALS[0..31] (page 45) and TX\_CALS[0..31] (page 57) to reflect the desired SPI-4.2 port configuration.

Rationale: The default parameter for length is a 16-port interface. The appropriate calendar is system dependent; so it is likely that this parameter needs to be set. The default multiplicity is 4, and should only be changed if the system needs tuning. **RX\_CALS[0..31]** and **TX\_CALS[0..31]** default to linear 16 ports.

Background: Flow control status is sent from the RX to the TX side of the SPI-4.2 link on the status channel. The flow control mechanism uses a calendar that must be configured the same on both the RX and TX devices. The RX interface steps through the fields in the calendar, and sends Starving, Hungry, or Satisfied flow control updates per port. The TX receives those credits and adjusts its transmission accordingly. The length of the calendar is defined in the length field of RX\_CAL\_LM and TX\_CAL\_LM. The length is the number of entries in the calendar. As the interfaces step through the calendar, the FIFO IDs in the calendar registers determine which port is currently under status update. In a linear calendar, the length is equal to the number of ports configured on the interface, and the calendar entries appear in ascending order. Sometimes it is desirable to update status on particular ports more frequently or in a different order. This is achieved by adjusting the length field and the calendar entries. The multiplicity field determines how many times the calendar is repeated between DIP2 parity and training pattern frames. The purpose of this is to optimize the efficiency of the status channel bandwidth versus the

status channel overhead. The calendar entries themselves are FIFO numbers from 0-255 in the register **RX\_CALS[0..31]** and **TX\_CALS[0..31]**.

3. If 8 or fewer FIFOs are to be used, Set the FIFO size value in **RX\_FS** (page 46) and **TX\_FS** (page 57).

Rationale: The default is 16 1KB FIFOs. 1KB FIFOs should be enough to cover link partner latency. However, it is often desirable to use all available buffering. Background: The FM1010 has 16KB of configurable FIFOs per simplex interface.

4. Set the LOW and HIGH watermarks in **RX\_WATERMARK** (page 46) to tune system performance.

Rationale: These watermarks should be set during start-up because the default values are conservative and have not been optimized for performance. See Table 29 for the recommended values for the watermarks for each FIFO size. Background: SPI-4.2 employs a two-watermark credit system for flow control. Below the LOW watermark field in **RX\_WATERMARK** (page 46) the status channel update is "Starving," between the LOW and HIGH watermark, the status update is "Hungry," and above the HIGH watermark, the status update is "Satisfied."

Leave the registers TX\_MAX\_BURST[0..15] (page 59) and TX\_SERVICE\_LIMIT (page 58) unmodified unless it is required to tune per channel service limits. Rationale: The default values in the max burst and service limit registers are typical for a wide range of applications.

Background: **TX\_MAX\_BURST[0..15]** specifies the values of **MAXBURST1** and **MAXBURST2** for each transmit port. A status report of "Starving" will reset the transmit port credits to **MAXBURST1** and a status report of "Hungry" will reset the transmit port credits to **MAXBURST2**, provided the credits had fallen below the level of **MAXBURST2**. The register **TX\_SERVICE\_LIMIT** offers a certain level of traffic shaping. It determines how much data is sent out of an eligible FIFO at a time (an eligible FIFO is one where the FIFO has data and the port has credits).

Set RX\_PORT\_VALID[0..7] (page 47, note the encoding) and TX\_FIFO\_VALID (page 59, note the encoding) to indicate the valid ports of the Rx interface and the valid FIFO's of the Tx interface.

Rationale: All ports default to invalid, so at least one valid port must be set at start-up.

Background: One error handling feature of the FM1010 is to drop packets with invalid Port IDs and report an error packet. There is a maximum of 16 active ports, which may have any port number, on any interface in multi-port mode.

7. Set RX\_PORT2FIFO[0..31] (page 47, note encoding) and

TX\_FIFO2PORT[0..15] (page 59) to establish the mapping of ports to FIFOs. Rationale: The default values will not likely be appropriate for the target system.

Background: The default settings map the first 16 SPI-4.2 ports to the 16 perinterface FIFOs, and all other ports to FIFO 0. This register does not determine port validity. On the receive side, the port valid and the port-to-FIFO map registers together establish valid ports and link them to the RX queues. On transmit side, **TX\_FIFO\_VALID** (page 59) and **TX\_FIFO2PORT[0..15]** determine the validity of the queue and map it to an outgoing SPI-4.2 port. There is no filtering function on the transmit side, so **TX\_FIFO\_VALID** is a check for proper device configuration.

Set RX\_LINKCFG1[0..15] (page 49), RX\_LINKCFG2[0..15] (page 50), and TX\_LINKCFG[0..15] (page 60) to configure the binding between ingress FIFOs and egress FIFOs.

Rationale: It is necessary to define the routing configuration in the FM1010 to reflect the system topology.

Background: **RX\_LINKCFG1[0..15]** and **RX\_LINKCFG2[0..15]** establish the mapping of ingress queues to egress queues across the internal switch element in the FM1010. **TX\_LINKCFG[0..15]** is the reverse mapping of this same information. The register has dependent information, but is set independently for internal hardware efficiency reasons. Consult the detailed sections for register entry equations.

#### 3.1.5.2 Clear Mode

In Clear mode, the flow control of SPI-4.2 applies to the entire interface as if there were only one active port, however any port number may appear in the Port ID of the SPI-4.2 segment control word. This mode enables devices with more than 16 active ports to pass traffic through the FM1010 without error, but sacrifices flow control on a per-port basis, and instead has flow control on a per-interface basis. If a connected device were natively single ported, but an extra tag per SPI-4.2 burst was desired in the system, this mechanism provides that feature.

For the background descriptions on the register-setting instructions for the following procedure in clear mode, please refer to the previous section on configuring multi-port mode.

- *Note:* Clear mode has the restriction that packets must be sent in their entirety before the Port ID can be changed.

- 1. Set the (M) field **RX\_OP\_MODE** (page 46) and **TX\_OP\_MODE** (page 58) to clear mode.

Rationale: The mode fields (M) of **RX\_OP\_MODE** and **TX\_OP\_MODE** default to multi-port mode after chip reset, and thus needs to be changed.

Set the calendar length field to 1 and set the multiplicity field according to tuning considerations and to match the partner device in RX\_CAL\_LM (page 43) and TX\_CAL\_LM (page 55). Set the calendar in *RX\_CALS[0..31]* (page 45) and TX\_CALS[0..31] (page 57) to FIFO 0.

Rationale: The default parameter for length is a 16-port interface. n The calendar refers to the FIFOs of which one is in use.

- Set RX\_FS (page 46) and TX\_FS (page 57). to 1 FIFO, 16KB. Rationale: The default is 16 1KB FIFOs. 1KB FIFOs should be enough to cover link partner latency. However, it is often desirable to use all available buffering, and this setting allows for 16KB of buffering per interface.

- 4. Set the LOW and HIGH watermarks in **RX\_WATERMARK** (page 46) to tune system performance.

Rationale: These watermarks should be set during start-up because the default values are conservative and have not been optimized for performance. See Table 29 for the recommended values for the watermarks for each FIFO size.

- Set the register TX\_MAX\_BURST[0..15] (page 59) to avoid overflow in the partner device buffer and leave TX\_SERVICE\_LIMIT (page 58) unmodified.

Rationale: TX\_MAX\_BURST[0..15] is only meaningful for multi-port mode.

- There is no need to overwrite the default values in RX\_PORT\_VALID[0..7] (page 47, note encoding) as they are ignored in clear-port mode. Set TX\_FIFO\_VALID (page 59, note encoding) to valid FIFO 0 only.

- Rationale: In clear mode, **RX\_PORT\_VALID[0..7]** is ignored. However, **TX\_FIFO\_VALID** determines the validity of the output queues. All queues

default to off since the SPI-4.2 link defaults to off. Queue 0 must be set to valid.

- 7. There is no need to set **RX\_PORT2FIFO[0..31]** or **TX\_FIFO2PORT[0..15]** as these two registers are ignored in clear-port mode..

- Set RX\_LINKCFG1[0..15] (page 49), RX\_LINKCFG2[0..15] (page 50), and TX\_LINKCFG[0..15] (page 60) to configure the binding between ingress FIFOs and egress FIFOs.

Rationale: It is necessary to define the routing configuration in the FM1010 to reflect the system topology.

# 3.2 Chip Operation

#### 3.2.1 Statistics

Basic statistics are available on each transmit and receive SPI-4.2 interface. These statistics are read-only registers.

- **RX\_PKTCNT** (page 51) is a 32-bit count of the received packets. It wraps to zero after reaching its maximum value.

- **RX\_PKTERRCNT** (page 51) is a 16-bit count of the packets received with errors.

- **RX\_DATACNT** (page 52) is the top 32-bits of a 34-bit count of all bytes of data received by the SPI-4.2 interface. It wraps to zero after reaching its maximum value.

- **TX\_PKTCNT** (page 61) is a 32-bit count of the transmitted packets. It wraps to zero after reaching its maximum value.

- **TX\_PKTERRCNT** (page 61) is a 16-bit count of the packets transmitted with errors.

- **TX\_DATACNT** (page 61) is the top 32-bits of a 34-bit count of all bytes of data transmitted by the SPI-4.2 interface. It wraps to zero after reaching its maximum value.

#### 3.2.2 Link/Port Reset Procedure

This procedure can be used to reset a link (queue pairing) within the FM1010. This procedure can only be used after a valid link has been established within the device, and not directly after chip reset. The feature allows the administrator to remap a port during run time if so desired.

To reset one or more ports:

- 1. Set the corresponding FIFO bit in **RX\_STATUS\_OVERRIDE** (page 48). This will cause the SPI-4.2 interface to send out satisfied status for the port to be reset.

- 2. Clear the corresponding bit in **RX\_PORT\_VALID** (page 47). This will cause any future data that arrives for that port to be discarded at the input.

- 3. After clearing the **RX\_PORT\_VALID** bit, wait until the port FIFO's are no longer draining (either empty or, if stalled, no longer draining) before proceeding to step 4. Not doing so will result in unpredictable behavior.

- 4. Set the corresponding bit in **RX\_LINK\_RESET** (page 50). This will initiate the reset of the queue pair link (several bits may be set at once to reset several links). This will flush the data from the input and output queue of that link.

- 5. Poll for the bit in **RX\_LINK\_RESET** to clear. This indicates that the reset has been successfully completed.

- 6. Optionally make any link configuration changes.

- 7. Set the correct bit in **RX\_PORT\_VALID** to enable the port.

- 8. Clear the bit in RX\_STATUS\_OVERRIDE to resume sending valid status.

During step 6 of the link reset procedure, it is valid to change the following configuration registers:

- RX\_LINKCFG1

- RX\_LINKCFG2

- RX\_PORT2FIFO

- TX\_LINKCFG

- TX\_FIFO\_VALID

- TX\_FIF02PORT

*Note:* It is only valid to change the information related to either the link that is being reset and torn down or any replacement link being established.

## 3.2.3 Interrupt Processing

The FM1010 has 13 possible interrupt sources:

- The CPU bus interface

- Six SPI-4.2 transmit interfaces

- Six SPI-4.2 receive interfaces

Upon detection of an interrupt from the FM1010, the host processor software shall proceed as follow:

- 1. Read the **INTR\_DETECT** register to determine the sources of the interruption. The register contains one bit per possible source.

- 2. If an interrupt from the CPU interface is detected, read the CPU\_INTERFACE\_IP to determine the exact cause of the interruption. This register is self clearing (this register and the corresponding bit for this source in the INTR\_DETECT are automatically cleared after being read). The interrupts from the CPU interface may be masked using the CPU\_INTERFACE\_IM register.

- 3. If an interrupt from the SPI-4.2 transmit or receive interface is detected, read the corresponding **RX\_IP** or **TX\_IP** register to determine the exact cause of the interruption. These registers are self clearing (these registers and the corresponding bits in the **INTR\_DETECT** are automatically cleared after being read). The interrupts from the SPI-4.2 interfaces may be masked using the **RX\_IM** and **TX\_IM** registers.

# 3.3 SPI-4.2 Interface

For a general overview of the SPI-4.2 interface specification, please refer to the SPI-4.2 implementation agreement:

Optical Internetworking Forum System Packet Interface Level 4 (SPI-4) Phase 2: OC-192 System Interface for Link Layer Devices, January 2001

This document is available at <u>http://www.oiforum.com</u>.

# 3.4 CPU Interface

The CPU Interface in the FM1010 is a 17-bit address, 16-bit data bus used to access the internal FM1010 registers. This bus is the primary access point for configuration and control. The interface is a slave device that uses a handshaking protocol to allow a variable amount of delay to respond to requests. Requests of 32-bit length are accomplished using two sequential 16-bit accesses.

## 3.4.1 General Description

- Slave-terminated protocol that allows a variable amount of delay to respond to requests

- 16-bit data interface only, supporting single, Big Endian, read/write transactions

- Interrupt generation

- No support for parity and other bus error detection and correction mechanisms

- Reconfiguration of the FM1010 10 us max

- Maximum frequency range of 50MHz

## 3.4.2 Register Read/Write Operations

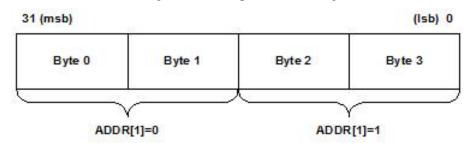

Reads and writes always act on a word (of 32-bit length) internally. The FM1010 assumed that the processor creates an atomic 32-bit read or write operation that is segmented by the bus protocol into two 16-bit read or write accesses.

*Note:* It is required that all writes and reads access the upper 16-bit aligned half-word before accessing the lower half-word (big-endian half-word ordering). The High Half Word shall be transferred when ADDR[1] is 0 while the Low Half Word shall be transferred when ADDR[1] is 1.

Figure 7 illustrates the byte ordering assumed by the FM1010.

Figure 7. Register Byte Format

#### 3.4.2.1 Read Operation

A read operation must always request the entire 32 bits of an internal register. The host bus controller shall break the 32-bit access into two successive 16-bit accesses:

- 1. First Access: Read Word Address at address X (Addr[1] not set). The FM1010 performs an internal 32-bit read and returns the most significant 16 bits on the bus while the least significant 16 bits are temporarily cached in the interface logic.

- 2. Second Access: Read Word Address at address X+2 (Addr[1] is set), the locally stored 16 bits are returned.

- *Note:* If the second read is not to the same word address or Addr[1] is not set, then the first step is repeated for this new word access. In a register read request, it is required that the high Half-Word is read first. A failure to follow this protocol may result in undefined behavior.

#### 3.4.2.2 Write Operation

A write operation must write an entire 32-bit register for the device to work properly. The host bus controller must break the 32-bit access into two successive 16-bit accesses:

- 1. First Access: Write Word Address X (Addr[1] is not set). The 16 bits of data are stored temporarily in a 16-bit register in the interface logic.

- 2. Second Access: Write Word Address X+2 (Addr[1] is set). The temporarily stored 16 bits and the new 16 bits of data are combined and written to the appropriate register. Only the second write triggers the register state change.

- *Note:* The FM1010 internal bus interface logic will generate CPU interrupt faults if this protocol is not respected. An overwrite error is generated if Addr[1] is not set and the temporary write register has been initialized with data by a previous transaction. The FM1010 will overwrite the temporary register and set the Overwrite Status bit to indicate the event. A maskable interrupt is automatically generated If this bit is not masked. An underwrite error is generated if Addr[1] is set on a new address (different from previously-accepted address). The FM1010 will use the current content of the 16-bit temporary register, combined with the new data, and proceed with the write, and then set the Underwrite Status bit to indicate the event. A maskable interrupt is automatically generated if this bit is not masked.

#### 3.4.3 CPU Interface Operation

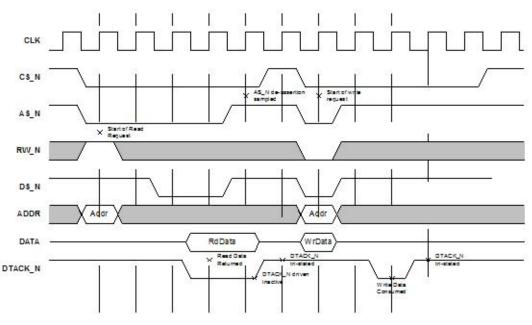

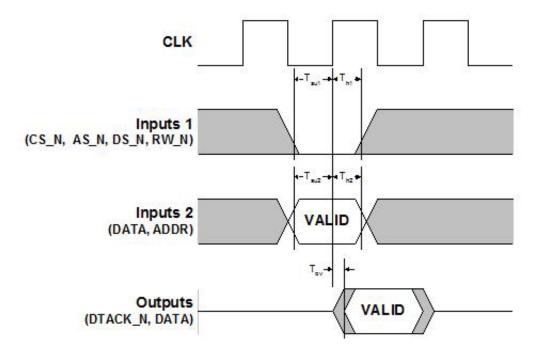

The CPU Bus Interface timing diagram is shown in Figure 8. All input signals are sampled at the rising edge of CLK and all output signals are driven (or tri-stated) at the rising edge of CLK as well.

**Figure 8.** CPU Bus Interface Timing Diagram

*Note:* Two consecutive 16b read (write) operations are required for a complete 32b read (write) transaction. The diagram of Figure 8 does not represent a complete transaction of either type and is only for illustrative purposes. See Paragraph 3.4.2 for a complete description.

The FM1010 Bus Interface operates under the following rules:

- The assertion of AS\_N, ADDR, RW\_N can occur at an arbitrary number of cycles after CS\_N is asserted. ADDR and RW\_N are only sampled after the first clock edge in which AS\_N is asserted.

- 2. The assertion of AS\_N can be as small as 1 cycle. This will allow DTACK\_N and DATA to be asserted as soon as possible (for the minimum of 1 clock period). This is shown in the Write request example. Otherwise a handshake occurs between AS\_N and DTACK\_N which forces DTACK\_N and DATA to be driven for a minimum of 2 clock cycles. This is shown in the Read request example.

- 3. CS\_N can be de-asserted 1 clock earlier on the read request but the DTACK\_N will not drive itself inactive and will instead be tri-stated on the clock edge after CS\_N is de-asserted.

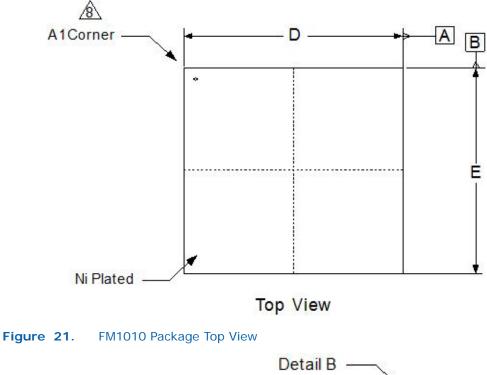

- 4. CS\_N must be de-asserted for at least 1 cycle between transactions.