# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

### **General Description**

**Features**

The MAX19792 dual general-purpose analog voltage variable attenuator (VVA) is designed to interface with  $50\Omega$  systems operating in the 500MHz to 4000MHz frequency range. The device includes a patented control circuit that provides 23.2dB of attenuation range (per attenuator) with a typical linear control slope of 8.5dB/V.

Both attenuators share a common analog control and can be cascaded together to yield 46.4dB of total attenuation range with a typical combined linear control slope of 17dB/V (5V operation).

Alternatively, the on-chip 4-wire SPI-controlled 10-bit DAC can be used to control both attenuators. In addition, a step-up/down feature allows user-programmable attenuator stepping through command pulses without reprogramming the SPI interface.

The MAX19792 is a monolithic device designed using one of Maxim's proprietary SiGe BiCMOS processes. The part operates from a single +5V supply or alternatively from a single +3.3V supply. It is available in a compact 36-pin TQFN package (6mm x 6mm x 0.8mm) with an exposed pad. Electrical performance is guaranteed over the -40°C to +100°C extended temperature range.

### **Applications**

Broadband System Applications, Including Wireless Infrastructure Digital and Spread-Spectrum Communication Systems

WCDMA/LTE, TD-SCDMA/TD-LTE, WiMAX®, cdma2000®, GSM/EDGE, and MMDS Base Stations

VSAT/Satellite Modems

Military Systems

Microwave Point-to-Point Systems

Lineup Gain Trim

Temperature-Compensation Circuits

Automatic Level Control (ALC)

Transmitter Gain Control

Receiver Gain Control

General Test Equipment

**♦ Wideband Coverage**

♦ 500MHz to 4000MHz RF Frequency Range

**♦** High Linearity

- ♦ Greater Than +37.9dBm IIP3 Over the Full Attenuation Range

- ♦ Integrates Two Analog Attenuators in One Monolithic Device

- **♦ Two Convenient Control Options**

- **♦ Single Analog Voltage**

- ♦ On-Chip SPI-Controlled 10-Bit DAC

- ♦ Step-Up/Down Pulse Command Inputs

- **♦ Flexible Attenuation Control Ranges**

- ♦ 46.4dB (Both Attenuators Cascaded)

- Linear dB/V Analog Control Response Curve Simplifies Automatic Leveling Control and Gain-Trim Algorithms

- ♦ Excellent Attenuation Flatness Over Wide Frequency Ranges and Attenuation Settings

- ♦ On-Chip Comparator (for Successive Approximation Measurement of Attenuator Control Voltage)

- ♦ Low 13mA Supply Current

- ♦ Single 5V or 3.3V Supply Voltage

- ♦ Pin-Compatible with the MAX19791 and MAX19793

- ♦ Pin-Compatible with the MAX19794 with Addition of Two Shunt Capacitors

- **♦ PCB-Compatible with the MAX19790**

- ♦ Lead(Pb)-Free Package

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to www.maximintegrated.com/MAX19792.related.

WiMAX® is a registered certification mark and registered service mark of WiMAX Forum. cdma2000 is a registered trademark of Telecommunications Industry Association.

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> 0.3V to +5.5V<br>REF_IN0.3V to Minimum (V <sub>CC</sub> + 0.3V, 3.6V) | RF Input Power at IN_A, IN_B, OUT_A, OUT_B+20dBm Continuous Power Dissipation (Note 1)2.8W |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| REF_SEL, DAC_LOGIC, MODE, DWN, UP,                                                    | Operating Case Temperature Range (Note 2)40°C to +100°C                                    |

| DIN, CLK, $\overline{\text{CS}}$                                                      | Maximum Junction Temperature+150°C                                                         |

| COMP_OUT, DOUT0.3V to +3.6V                                                           | Storage Temperature Range65°C to +150°C                                                    |

| IN_A, OUT_A, IN_B, OUT_B0.3V to V <sub>CC</sub> + 0.3V                                | Lead Temperature (soldering, 10s)+300°C                                                    |

| CTRL (except for test mode)0.3V to V <sub>CC</sub> + 0.3V                             | Soldering Temperature (reflow)+260°C                                                       |

| Maximum CTRL Pin Load Current                                                         |                                                                                            |

| (CTRL configured as an output)0.3mA                                                   |                                                                                            |

- Note 1: Based on junction temperature  $T_J = T_C + (\theta_{JC} \times V_{CC} \times I_{CC})$ . This formula can be used when the temperature of the exposed pad is known while the device is soldered down to a PCB. See the *Applications Information* section for details. The junction temperature must not exceed +150°C.

- Note 2: T<sub>C</sub> is the temperature on the exposed pad of the package. T<sub>A</sub> is the ambient temperature of the device and PCB.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS

**TOFN**

| Junction-to-Ambient Thermal Resistance $(\theta_{JA})$ | Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) |

|--------------------------------------------------------|-------------------------------------------------------|

| (Notes 3, 4)+36°C/W                                    | (Notes 1, 4)+10°C/W                                   |

- Note 3: Junction temperature  $T_J = T_A + (\theta_{JA} \times V_{CC} \times I_{CC})$ . This formula can be used when the ambient temperature of the PCB is known. The junction temperature must not exceed +150°C.

- **Note 4:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### 3.3V DC ELECTRICAL CHARACTERISTICS

$(V_{CC}=3.15V\ to\ 3.45V,\ V_{CTRL}=1V,\ V_{DAC\_LOGIC}=0V,\ RDBK\_EN(D9,\ REG3)=logic\ 0,\ no\ RF\ signals\ applied,\ all\ input\ and\ output\ ports\ terminated\ with\ 50\Omega\ through\ DC\ blocks,\ T_{C}=-40^{\circ}C\ to\ +100^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $V_{CC}=3.3V,\ V_{CTRL}=1V,\ V_{DAC\ LOGIC}=0V,\ RDBK\_EN(D9,\ REG3)=logic\ 0,\ T_{C}=+25^{\circ}C,\ unless\ otherwise\ noted.)$  (Note 5)

| PARAMETER                | SYMBOL            | CONDITIONS                                             | MIN  | TYP | MAX  | UNITS |

|--------------------------|-------------------|--------------------------------------------------------|------|-----|------|-------|

| Supply Voltage           | V <sub>CC</sub>   |                                                        | 3.15 | 3.3 | 3.45 | V     |

| Supply Current           | Icc               |                                                        |      | 9.5 | 14   | mA    |

| Control Voltage Range    | V <sub>CTRL</sub> |                                                        | 1    |     | 2.5  | V     |

| CTRL Input Resistance    | R <sub>CTRL</sub> |                                                        |      | 1.0 |      | ΜΩ    |

| Input Current Logic-High | I <sub>IH</sub>   |                                                        | -1   |     | +1   | μΑ    |

| Input Current Logic-Low  | I <sub>IL</sub>   |                                                        | -1   |     | +1   | μΑ    |

| REF_IN Voltage           |                   |                                                        |      | 1.4 |      | V     |

| REF_IN Input Resistance  |                   |                                                        |      | 1.0 |      | MΩ    |

| DAC Number of Bits       |                   | Monotonic                                              |      |     | 10   | Bits  |

| Input Voltage Logic-High | V <sub>IH</sub>   |                                                        | 2    |     |      | V     |

| Input Voltage Logic-Low  | V <sub>IL</sub>   |                                                        |      |     | 0.8  | V     |

| COMP_OUT Logic-High      |                   | RDBK_EN(D9, REG3) = logic 1,<br>$R_{LOAD} = 47k\Omega$ |      | 3.3 |      | V     |

| COMP_OUT Logic-Low       |                   | RDBK_EN(D9, REG3) = logic 1,<br>RLOAD = $47k\Omega$    |      | 0   |      | V     |

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

### **5V DC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 4.75 \text{V to } 5.25 \text{V}, V_{CTRL} = 1 \text{V}, V_{DAC\_LOGIC} = 0 \text{V}, RDBK\_EN(D9, REG3) = logic 0, no RF signals applied, all input and output ports terminated with 50<math>\Omega$  through DC blocks,  $T_{C} = -40^{\circ}\text{C}$  to +100°C, unless otherwise noted. Typical values are at  $V_{CC} = 5 \text{V}, V_{CTRL} = 1 \text{V}, V_{DAC\_LOGIC} = 0 \text{V}, RDBK\_EN(D9, REG3) = logic 0, T_{C} = +25^{\circ}\text{C}, unless otherwise noted.)$  (Note 5)

| PARAMETER                | SYMBOL            | CONDITIONS                                             | MIN  | TYP | MAX  | UNITS |

|--------------------------|-------------------|--------------------------------------------------------|------|-----|------|-------|

| Supply Voltage           | V <sub>CC</sub>   |                                                        | 4.75 | 5.0 | 5.25 | V     |

| Supply Current           | Icc               |                                                        |      | 13  | 20   | mA    |

| CTRL Voltage Range       | V <sub>CTRL</sub> |                                                        | 1    |     | 4    | V     |

| CTRL Input Resistance    | R <sub>CTRL</sub> |                                                        |      | 124 |      | kΩ    |

| Input Current Logic-High | lін               |                                                        | -1   |     | +1   | μΑ    |

| Input Current Logic-Low  | I <sub>IL</sub>   |                                                        | -1   |     | +1   | μΑ    |

| REF_IN Voltage Range     |                   |                                                        |      | 1.4 |      | V     |

| REF_IN Input Resistance  |                   |                                                        |      | 1.0 |      | MΩ    |

| DAC Number of Bits       |                   | Monotonic                                              |      | 10  |      | Bits  |

| Input Voltage Logic-High | VIH               |                                                        | 2    |     |      | V     |

| Input Voltage Logic-Low  | V <sub>IL</sub>   |                                                        |      |     | 0.8  | V     |

| COMP_OUT Logic-High      |                   | RDBK_EN(D9, REG3) = logic 1,<br>$R_{LOAD} = 47k\Omega$ |      | 3.3 |      | V     |

| COMP_OUT Logic-Low       |                   | RDBK_EN(D9, REG3) = logic 1,<br>$R_{LOAD} = 47k\Omega$ |      | 0   |      | V     |

### RECOMMENDED AC OPERATING CONDITIONS

| PARAMETER           | SYMBOL          | CONDITIONS           | MIN | TYP | MAX  | UNITS |

|---------------------|-----------------|----------------------|-----|-----|------|-------|

| RF Frequency Range  | f <sub>RF</sub> | (Note 6)             | 500 |     | 4000 | MHz   |

| RF Port Input Power | P <sub>RF</sub> | Continuous operation |     |     | 15   | dBm   |

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

### 3.3V AC ELECTRICAL CHARACTERISTICS

$(Typical\ Application\ Circuit)$ , one attenuator,  $V_{CC}=3.15V$  to 3.45V, RF ports are driven from  $50\Omega$  sources and loaded into  $50\Omega$ , input  $P_{RF}=0$ dBm,  $f_{RF}=950$ MHz to 2150MHz,  $V_{CTRL}=1V$  to 2.5V,  $V_{DAC\_LOGIC}=0V$ , RDBK\_EN(D9, REG3) = logic 0,  $T_{C}=-40^{\circ}$ C to  $+100^{\circ}$ C. Typical values are for  $T_{C}=+25^{\circ}$ C,  $V_{CC}=3.3V$ , input  $P_{RF}=0$ dBm,  $f_{RF}=1500$ MHz,  $V_{CTRL}=1V$ ,  $V_{DAC\_LOGIC}=0V$ , RDBK\_EN (D9, REG3) = logic 0, unless otherwise noted.) (Notes 5, 7)

| PARAMETER                                                                             | SYMBOL            | CONDITIONS                                                                                                                                                                                              | MIN  | TYP  | MAX | UNITS  |  |

|---------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|--------|--|

| Insertion Loss                                                                        | IL                | One attenuator                                                                                                                                                                                          |      | 2.8  |     | ٩D     |  |

| insertion Loss                                                                        | IL.               | Two attenuators                                                                                                                                                                                         |      | 5.3  |     | dB     |  |

| Loss Variation Over<br>Temperature                                                    |                   | $T_{C} = -40^{\circ}\text{C to } +100^{\circ}\text{C}$                                                                                                                                                  |      | 0.21 |     | dB     |  |

| Input P <sub>1dB</sub>                                                                | IP <sub>1dB</sub> |                                                                                                                                                                                                         |      | 17.3 |     | dBm    |  |

| Minimum Input Second-Order<br>Intercept Point Over Full<br>Attenuation Range (Note 8) | IIP2              | One attenuator, f <sub>RF1</sub> +f <sub>RF2</sub> term,<br>f <sub>RF1</sub> -f <sub>RF2</sub> = 1MHz, V <sub>CTRL</sub> = 1V to 2.5V,<br>P <sub>RF</sub> = 0dBm/tone applied to attenuator<br>input    |      | 55   |     | dPm    |  |

|                                                                                       | IIFZ              | Two attenuators, f <sub>RF1</sub> + f <sub>RF2</sub> term,<br>f <sub>RF1</sub> - f <sub>RF2</sub> = 1MHz, V <sub>CTRL</sub> = 1V to 2.5V,<br>P <sub>RF</sub> = 0dBm/tone applied to attenuator<br>input |      | 52   |     | dBm    |  |

| Minimum Input Third-Order<br>Intercept Point Over Full<br>Attenuation Range (Note 8)  | IIP3              | One attenuator, V <sub>CTRL</sub> = 1V to 2.5V,<br>f <sub>RF1</sub> - f <sub>RF2</sub> = 1MHz, P <sub>RF</sub> = 0dBm/tone<br>applied to attenuator input                                               |      | 34.8 |     | alD as |  |

|                                                                                       |                   | Two attenuators, V <sub>CTRL</sub> = 1V to 2.0V, f <sub>RF1</sub> - f <sub>RF2</sub> = 1MHz, P <sub>RF</sub> = 0dBm/tone applied to attenuator input                                                    |      | 34.1 |     | dBm    |  |

| Second Harmonic                                                                       |                   |                                                                                                                                                                                                         |      | 62.7 |     | dBc    |  |

| Third Harmonic                                                                        |                   |                                                                                                                                                                                                         |      | 90.6 |     | dBc    |  |

| Attanuation Control Dange                                                             |                   | One attenuator, V <sub>CTRL</sub> = 1V to 2.5V                                                                                                                                                          |      | 23.4 |     | dB     |  |

| Attenuation Control Range                                                             |                   | Two attenuators, V <sub>CTRL</sub> = 1V to 2.5V                                                                                                                                                         |      | 46.8 |     | иБ     |  |

| Average Attenuation-Control Slope                                                     |                   | V <sub>CTRL</sub> = 1.4V to 2.3V                                                                                                                                                                        |      | 22   |     | dB/V   |  |

| Maximum Attenuation-Control Slope                                                     |                   | V <sub>CTRL</sub> = 1V to 2.5V                                                                                                                                                                          |      | 40   |     | dB/V   |  |

| S21 Attenuation Deviation from a Straight Line                                        |                   | V <sub>CTRL</sub> = 1.4V to 2.1V                                                                                                                                                                        | ±0.4 |      |     | dB     |  |

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

### **5V AC ELECTRICAL CHARACTERISTICS**

(*Typical Application Circuit*, one attenuator,  $V_{CC} = 4.75V$  to 5.25V, RF ports are driven from  $50\Omega$  sources and loaded into  $50\Omega$ , input  $P_{RF} = 0$ dBm,  $f_{RF} = 950$ MHz to 2150MHz,  $V_{CTRL} = 1V$  to 4V,  $V_{DAC\_LOGIC} = 0V$ , RDBK\_EN(D9, REG3) = logic 0,  $T_{C} = -40^{\circ}$ C to +100°C. Typical values are for  $T_{C} = +25^{\circ}$ C,  $V_{CC} = 5V$ , input  $P_{RF} = 0$ dBm,  $f_{RF} = 1500$ MHz,  $V_{CTRL} = 1V$ ,  $V_{DAC\_LOGIC} = 0V$ , RDBK\_EN (D9, REG3) = logic 0, unless otherwise noted.) (Notes 5, 7)

| PARAMETER                                                                             | SYMBOL            | CONDITIONS                                                                                                                                                                                            | MIN | TYP   | MAX | UNIT  |  |

|---------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|--|

| Insertion Loss                                                                        | IL                | One attenuator                                                                                                                                                                                        |     | 2.64  |     | dB    |  |

| Insertion Loss                                                                        | IL                | Two attenuators                                                                                                                                                                                       |     | 5.2   |     | uв    |  |

| Loss Variation Over<br>Temperature                                                    |                   | $T_{C} = -40^{\circ}\text{C to } +100^{\circ}\text{C}$                                                                                                                                                |     | 0.22  |     | dB    |  |

| Input P <sub>1dB</sub>                                                                | IP <sub>1dB</sub> |                                                                                                                                                                                                       |     | 22.7  |     | dBm   |  |

| Minimum Input Second-Order<br>Intercept Point Over Full<br>Attenuation Range (Note 8) | IIP2              | One attenuator, f <sub>RF1</sub> + f <sub>RF2</sub> term,<br>f <sub>RF1</sub> - f <sub>RF2</sub> = 1MHz, V <sub>CTRL</sub> = 1V to 4V,<br>P <sub>RF</sub> = 0dBm/tone applied to attenuator<br>input  |     | 63.4  |     | dBm   |  |

|                                                                                       | IIFZ              | Two attenuators, f <sub>RF1</sub> + f <sub>RF2</sub> term,<br>f <sub>RF1</sub> - f <sub>RF2</sub> = 1MHz, V <sub>CTRL</sub> = 1V to 4V,<br>P <sub>RF</sub> = 0dBm/tone applied to attenuator<br>input |     | 59.4  |     | asm   |  |

| Minimum Input Third-Order                                                             | UD0               | One attenuator, V <sub>CTRL</sub> from 1V to 4V, f <sub>RF1</sub> - f <sub>RF2</sub> = 1MHz, P <sub>RF</sub> = 0dBm/tone applied to attenuator input                                                  |     | 37.9  |     | 10    |  |

| Intercept Point Over Full IIP3 Attenuation Range (Note 8)                             |                   | Two attenuators, $V_{CTRL}$ from 1V to 3.5V, $f_{RF1}$ - $f_{RF2}$ = 1MHz, $P_{RF}$ = 0dBm/tone applied to attenuator input                                                                           |     | 34.6  |     | - dBm |  |

| Second Harmonic                                                                       |                   |                                                                                                                                                                                                       |     | 73.4  |     | dBc   |  |

| Third Harmonic                                                                        |                   |                                                                                                                                                                                                       |     | 101.7 |     | dBc   |  |

| Attenuation Control Range                                                             |                   | One attenuator, V <sub>CTRL</sub> = 1V to 4V                                                                                                                                                          |     | 23.2  |     | dB    |  |

| Attendation Control Hange                                                             |                   | Two attenuators, V <sub>CTRL</sub> = 1V to 4V                                                                                                                                                         |     | 46.4  |     | dB    |  |

| Average Attenuation-Control Slope                                                     |                   | V <sub>CTRL</sub> = 1.4V to 3.1V                                                                                                                                                                      |     | 8.5   |     | dB/V  |  |

| Maximum Attenuation-Control Slope                                                     |                   | V <sub>CTRL</sub> = 1V to 3.5V                                                                                                                                                                        |     | 35    |     | dB/V  |  |

| Attenuation Flatness Over any 125MHz Band                                             |                   | V <sub>CTRL</sub> = 1V to 3.1V                                                                                                                                                                        |     | 0.2   |     | dB    |  |

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

### **5V AC ELECTRICAL CHARACTERISTICS (continued)**

(*Typical Application Circuit*, one attenuator,  $V_{CC} = 4.75V$  to 5.25V, RF ports are driven from  $50\Omega$  sources and loaded into  $50\Omega$ , input  $P_{RF} = 0$ dBm,  $f_{RF} = 950$ MHz to 2150MHz,  $V_{CTRL} = 1V$  to 4V,  $V_{DAC\_LOGIC} = 0V$ , RDBK\_EN(D9, REG3) = logic 0,  $T_{C} = -40^{\circ}$ C to  $+100^{\circ}$ C. Typical values are for  $T_{C} = +25^{\circ}$ C,  $V_{CC} = 5V$ , input  $P_{RF} = 0$ dBm,  $f_{RF} = 1500$ MHz,  $V_{CTRL} = 1V$ ,  $V_{DAC\_LOGIC} = 0V$ , RDBK\_EN (D9, REG3) = logic 0, unless otherwise noted.) (Notes 5, 7)

| PARAMETER                                         | SYMBOL           | CONDITIONS                        | MIN | TYP  | MAX | UNIT    |

|---------------------------------------------------|------------------|-----------------------------------|-----|------|-----|---------|

| CTRL Switching Time (Note 9)                      |                  | 15dB to 0dB range                 |     | 360  |     | ns      |

| CTAL Switching Time (Note 9)                      |                  | 0dB to 15dB range                 |     | 780  |     | 115     |

| CS Switching Time (Note 10)                       |                  | 15dB to 0dB range                 |     | 700  |     | ns      |

| C3 Switching Time (Note 10)                       |                  | 0dB to 15dB range                 |     | 2200 |     | 113     |

| MODE Switching Time (Note                         |                  | 15dB to 0dB range (MODE 1 to 0)   |     | 700  |     | ns      |

| 11)                                               |                  | 0dB to 15dB range (MODE 0 to 1)   |     | 2200 |     | 113     |

| Input Return Loss                                 |                  |                                   |     | 21   |     | dB      |

| Output Return Loss                                |                  |                                   |     | 31   |     | dB      |

| Group Delay                                       |                  | Input/output 50Ω lines deembedded |     | 190  |     | ps      |

| Group Delay Flatness Over Any<br>125MHz Band      |                  | Peak to peak                      |     | 25   |     | ps      |

| Group Delay Change                                |                  | V <sub>CTRL</sub> = 1V to 4V      |     | -85  |     | ps      |

| Insertion Phase Change vs.<br>Attenuation Control |                  | V <sub>CTRL</sub> = 1V to 4V      |     | 17.8 |     | Degrees |

| S21 Attenuation Deviation from a Straight Line    |                  | V <sub>CTRL</sub> = 1.4V to 3.1V  |     | ±0.4 |     | dB      |

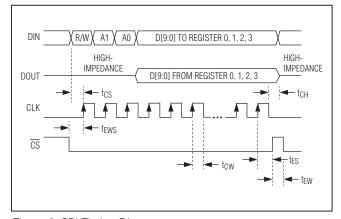

| SERIAL PERIPHERAL INTERFA                         | CE (SPI)         |                                   |     |      |     |         |

| Maximum Clock Speed                               |                  |                                   |     | 20   |     | MHz     |

| Data-to-Clock Setup Time                          | t <sub>CS</sub>  | (Note 12)                         |     | 2    |     | ns      |

| Data-to-Clock Hold Time                           | t <sub>CH</sub>  | (Note 12)                         |     | 2.5  |     | ns      |

| CS-to-CLK Setup Time                              | t <sub>EWS</sub> | (Note 12)                         |     | 3    |     | ns      |

| CS Positive Pulse Width                           | t <sub>EW</sub>  | (Note 12)                         |     | 7    |     | ns      |

| Clock Pulse Width                                 | t <sub>CW</sub>  | (Note 12)                         |     | 5    |     | ns      |

- **Note 5:** Production tested at  $T_C = +100^{\circ}C$ . All other temperatures are guaranteed by design and characterization.

- **Note 6:** Recommended functional range. Not production tested. Operation outside this range is possible, but with degraded performance of some parameters.

- **Note 7:** All limits include external component losses, connectors and PCB traces. Output measurements taken at the RF port of the *Typical Application Circuit*.

- **Note 8:**  $f_{RE1} = 1501 \text{MHz}$ ,  $f_{RE2} = 1500 \text{MHz}$ ,  $P_{RE} = 0 \text{dBm/tone}$  applied to attenuator input.

- **Note 9:** Switching time measured from 50% of the CTRL signal to when the RF output settles to  $\pm 1$ dB (R3 = 0 $\Omega$ ).

- Note 10: Switching time measured from when  $\overline{CS}$  is asserted to when the RF output settles to ±1dB.

- Note 11: Switching time measured from when MODE is asserted to when the RF output settles to ±1dB.

- Note 12: Typical minimum time for proper SPI operation.

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

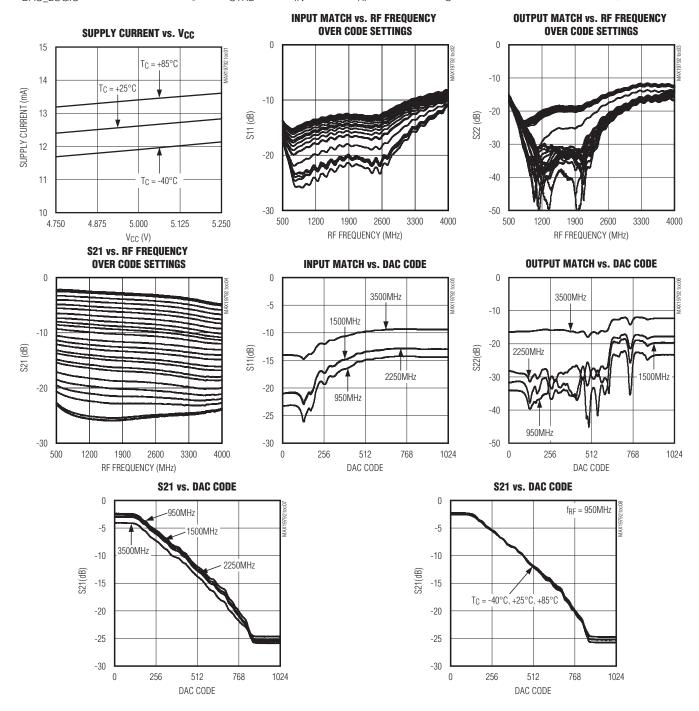

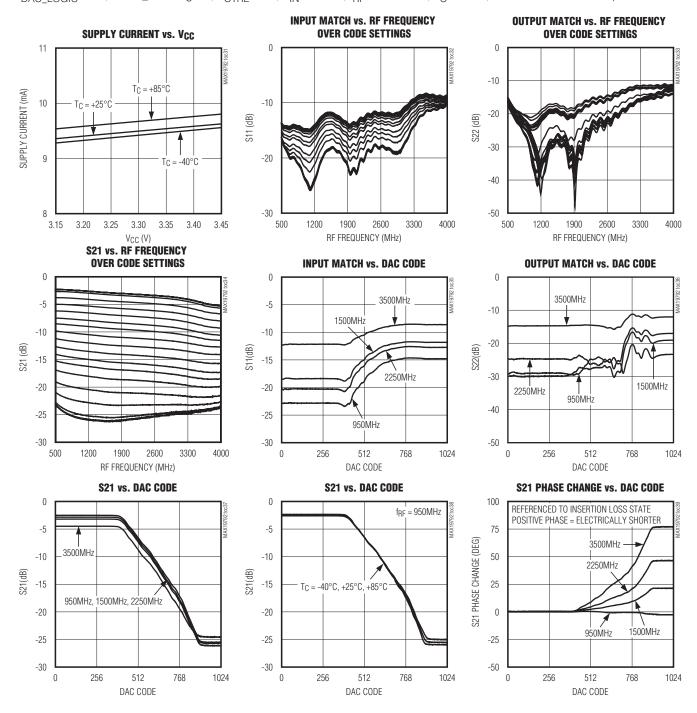

## **Typical Operating Characteristics**

$( \underline{\textit{Typical Application Circuit}}, \textbf{V}_{\textbf{CC}} = \textbf{5V}, \text{ configured for single attenuator, RF ports are driven from } 50\Omega \text{ sources and loaded into } 50\Omega, \\ \textbf{V}_{DAC\_LOGIC} = \textbf{0V}, \textbf{RDBK\_EN} = \textbf{Logic 0}, \textbf{V}_{CTRL} = \textbf{1V}, \textbf{P}_{IN} = \textbf{0dBm}, \textbf{f}_{RF} = \textbf{1500MHz}, \textbf{T}_{C} = \textbf{25}^{\circ}\text{C}, \text{ unless otherwise noted.} ).$

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

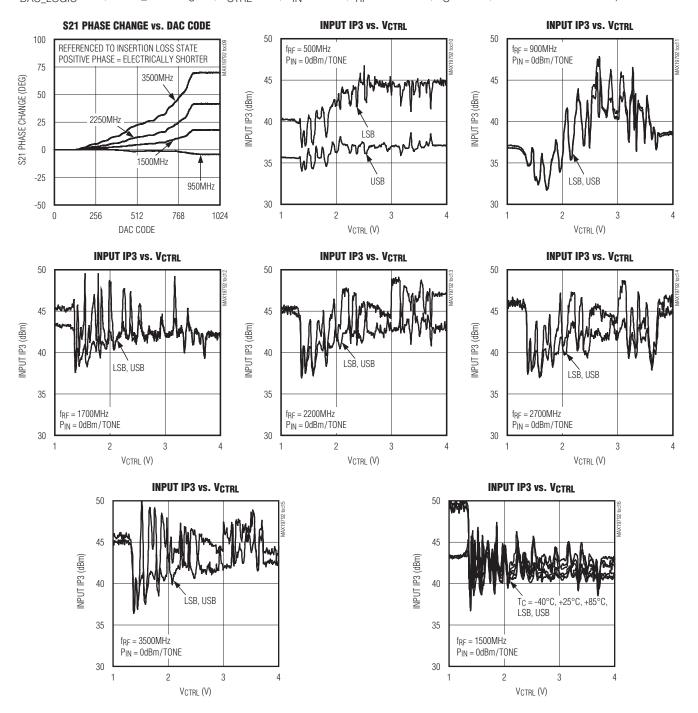

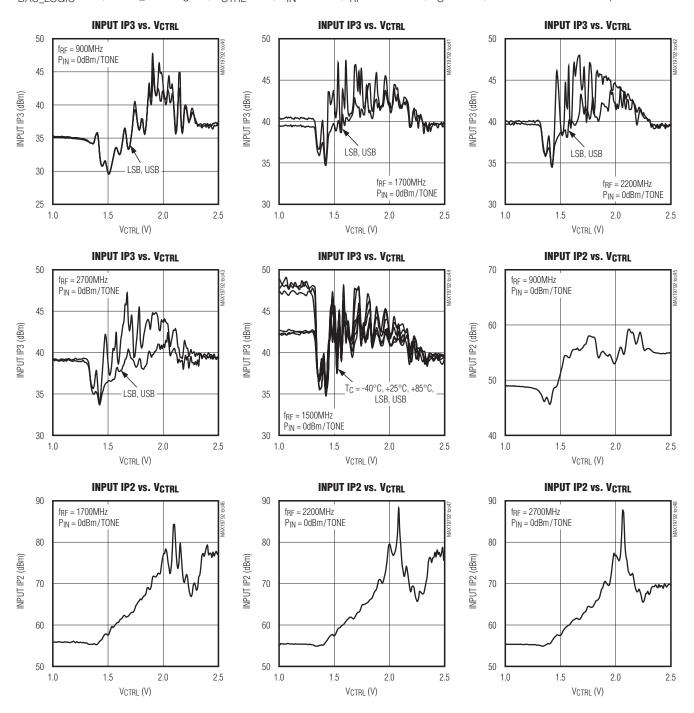

## **Typical Operating Characteristics (continued)**

$( \underline{\textit{Typical Application Circuit}}, \textbf{V}_{\textbf{CC}} = \textbf{5V}, \text{ configured for single attenuator, RF ports are driven from } 50\Omega \text{ sources and loaded into } 50\Omega, \\ \textbf{V}_{DAC\_LOGIC} = \textbf{0V}, \textbf{RDBK\_EN} = \textbf{Logic 0}, \textbf{V}_{CTRL} = \textbf{1V}, \textbf{P}_{IN} = \textbf{0dBm}, \textbf{f}_{RF} = \textbf{1500MHz}, \textbf{T}_{C} = \textbf{25}^{\circ}\text{C}, \text{ unless otherwise noted.} ).$

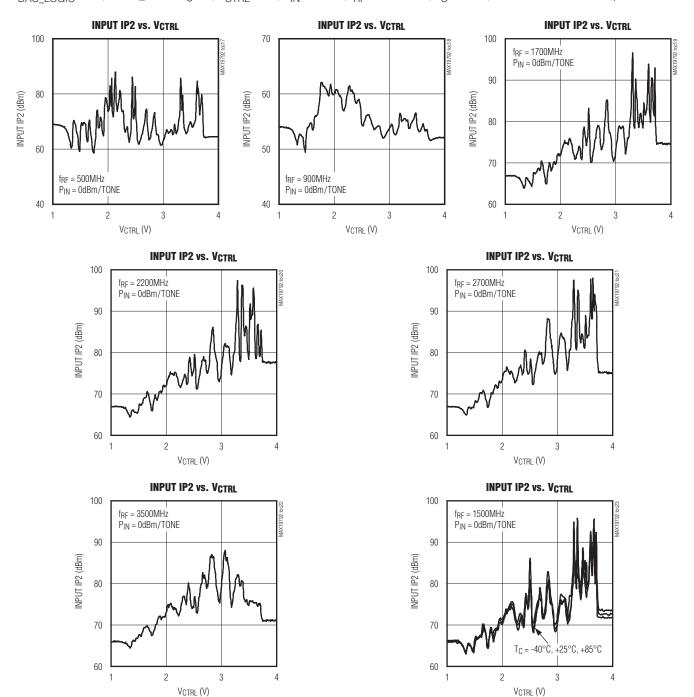

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

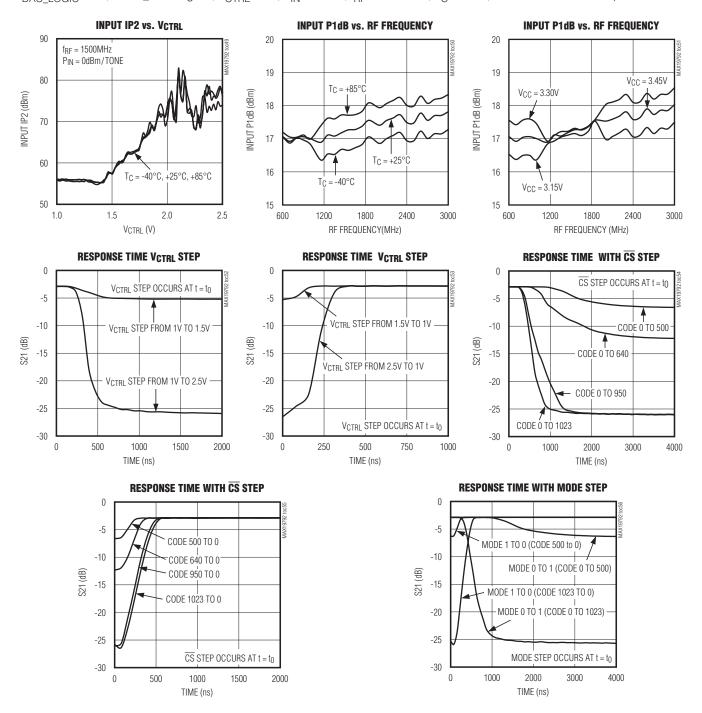

## **Typical Operating Characteristics (continued)**

$( \underline{\textit{Typical Application Circuit}}, \textbf{V}_{\textbf{CC}} = \textbf{5V}, \text{ configured for single attenuator, RF ports are driven from } 50\Omega \text{ sources and loaded into } 50\Omega, \\ \textbf{V}_{DAC\_LOGIC} = \textbf{0V}, \textbf{RDBK\_EN} = \textbf{Logic 0}, \textbf{V}_{CTRL} = \textbf{1V}, \textbf{P}_{IN} = \textbf{0dBm}, \textbf{f}_{RF} = \textbf{1500MHz}, \textbf{T}_{C} = \textbf{25}^{\circ}\text{C}, \text{ unless otherwise noted.} ).$

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

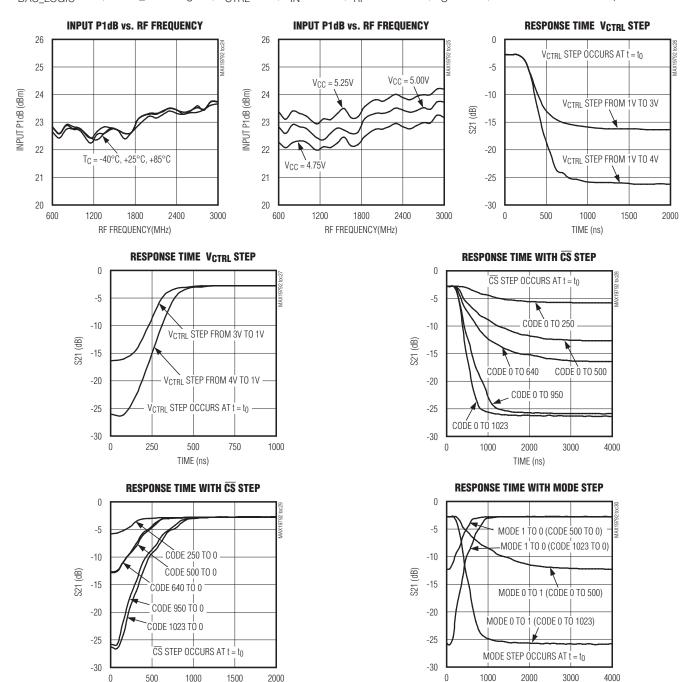

## **Typical Operating Characteristics (continued)**

$\frac{(\textit{Typical Application Circuit}, \textit{V}_{\textit{CC}} = \textit{5V}, \text{ configured for single attenuator, RF ports are driven from } 50\Omega \text{ sources and loaded into } 50\Omega, \\ V_{DAC\_LOGIC} = 0V, RDBK\_EN = Logic 0, V_{CTRL} = 1V, P_{IN} = 0 \\ \text{dBm}, f_{RF} = 1500 \\ \text{MHz}, T_{C} = 25 \\ \text{°C}, unless otherwise noted.} ).$

Maxim Integrated 10

TIME (ns)

TIME (ns)

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

## Typical Operating Characteristics (continued)

$\frac{(\textit{Typical Application Circuit}, \textbf{V}_{\textbf{CC}} = \textbf{3.3V}, \text{ configured for single attenuator, RF ports are driven from } {50\Omega} \text{ sources and loaded into } {50\Omega}, \\ \text{V}_{DAC\_LOGIC} = \text{OV}, \text{RDBK\_EN} = \text{logic 0}, \\ \text{V}_{CTRL} = \text{1V}, \\ \text{P}_{IN} = \text{0dBm}, \\ \text{f}_{RF} = \text{1500MHz}, \\ \text{T}_{C} = \text{25°C}, \\ \text{unless otherwise noted.}).$

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

# **Typical Operating Characteristics (continued)**

$( \begin{tabular}{ll} \hline \textit{Typical Application Circuit}, \textbf{V}_{\textbf{CC}} = \textbf{3.3V}, \text{ configured for single attenuator, RF ports are driven from } 50\Omega \text{ sources and loaded into } 50\Omega, \\ \hline \textit{V}_{DAC\_LOGIC} = 0 \text{V}, \begin{tabular}{ll} RDBK\_EN = logic 0, V_{CTRL} = 1 \text{V}, P_{IN} = 0 \text{dBm}, f_{RF} = 1500 \text{MHz}, T_{C} = 25 ^{\circ}\text{C}, unless otherwise noted.). \\ \hline \end{tabular}$

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

## **Typical Operating Characteristics (continued)**

$\frac{(\textit{Typical Application Circuit}, \textbf{V}_{\textbf{CC}} = \textbf{3.3V}, \text{ configured for single attenuator, RF ports are driven from } {50\Omega} \text{ sources and loaded into } {50\Omega}, \\ \text{V}_{\text{DAC\_LOGIC}} = \text{0V}, \text{RDBK\_EN} = \text{logic 0}, \\ \text{V}_{\text{CTRL}} = \text{1V}, \\ \text{P}_{\text{IN}} = \text{0dBm}, \\ \text{f}_{\text{RF}} = \text{1500MHz}, \\ \text{T}_{\text{C}} = \text{25}^{\circ}\text{C}, \\ \text{unless otherwise noted.}).$

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

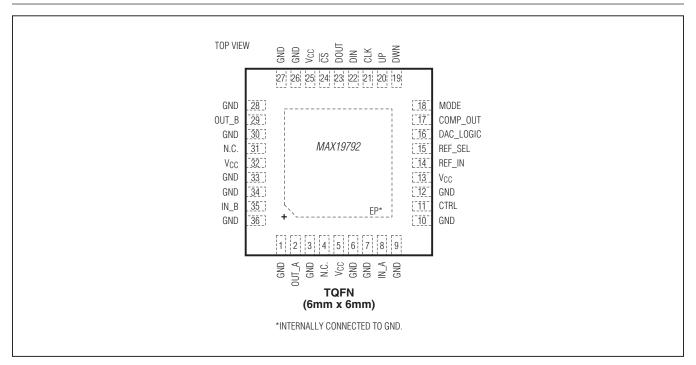

# **Pin Configuration**

# **Pin Description**

| PIN                                                     | NAME            | DESCRIPTION                                                                                                                                                                                                                                  |

|---------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 6, 7, 9, 10,<br>12, 26, 27, 28,<br>30, 33, 34, 36 | GND             | Ground. Connect to the board's ground plane using low-inductance layout techniques.                                                                                                                                                          |

| 2                                                       | OUT_A           | Attenuator A RF Output. Internally matched to $50\Omega$ over the operating frequency band. This pin, if used, requires a DC block. If this attenuator is not used, the pin can be left unconnected.                                         |

| 4, 31                                                   | N.C.            | No Internal Connection. This pin can be left open or ground.  Note: If a common layout is desired to support the MAX19794, connect a 0402 capacitor to ground on each of these pins.                                                         |

| 5                                                       | V <sub>CC</sub> | Attenuator A Power Supply. Bypass to GND with a capacitor and resistor, as shown in the<br>Typical Application Circuit.                                                                                                                      |

| 8                                                       | IN_A            | Attenuator A RF Input. Internally matched to $50\Omega$ over the operating frequency band. This pin, if used, requires a DC block. If this attenuator is not used, the pin can be left unconnected.                                          |

| 11                                                      | CTRL            | Attenuator Control Voltage Input. <b>Except in test mode, where no voltage can be applied to this pin.</b> V <sub>CC</sub> must be present unless using a current-limiting resistor as noted in the <i>Applications Information</i> section. |

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

# Pin Description (continued)

| PIN   | NAME            | DESCRIPTION                                                                                                                                                                                                                                                                                                   |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13    | V <sub>CC</sub> | Analog Supply Voltage. Bypass to GND with a capacitor as close as possible to the device. See the <i>Typical Application Circuit</i> .                                                                                                                                                                        |

| 14    | REF_IN          | DAC Reference Voltage Input (Optional)                                                                                                                                                                                                                                                                        |

| 15    | REF_SEL         | DAC Reference Voltage Selection Logic Input Logic = 0 to enable on-chip DAC reference. Logic = 1 to use off-chip DAC reference (pin 14).                                                                                                                                                                      |

| 16    | DAC_LOGIC       | DAC Logic Control Input (Table 1)                                                                                                                                                                                                                                                                             |

| 17    | COMP_OUT        | Comparator Logic Output. Use a 4.7pF capacitor to reduce any potential rise-time glitching when the comparator changes state.                                                                                                                                                                                 |

| 18    | MODE            | Attenuator Control Mode Logic Input Logic = 1 to enable attenuator step control. Logic = 0 to enable attenuator SPI control.                                                                                                                                                                                  |

| 19    | DWN             | Down Pulse Input Logic pulse = 0 for each step-down.                                                                                                                                                                                                                                                          |

| 20    | UP              | Up Pulse Input Logic pulse = 0 for each step-up.                                                                                                                                                                                                                                                              |

| 19/20 | DWN/UP          | Logic = 0 to both pins to reset the attenuator to a minimum attenuation state                                                                                                                                                                                                                                 |

| 21    | CLK             | SPI Clock Input                                                                                                                                                                                                                                                                                               |

| 22    | DIN             | SPI Data Input                                                                                                                                                                                                                                                                                                |

| 23    | DOUT            | SPI Data Output                                                                                                                                                                                                                                                                                               |

| 24    | CS              | SPI Chip-Select Input                                                                                                                                                                                                                                                                                         |

| 25    | V <sub>CC</sub> | Digital Supply Voltage. Bypass to GND with a capacitor as close as possible to the device. See the <i>Typical Application Circuit</i> .                                                                                                                                                                       |

| 29    | OUT_B           | Attenuator B RF Output. Internally matched to $50\Omega$ over the operating frequency band. This pin, if used, requires a DC block. If this attenuator is not used, the pin can be left unconnected.                                                                                                          |

| 32    | V <sub>CC</sub> | Attenuator B Power Supply. Bypass to GND with a capacitor and resistor, as shown in the<br>Typical Application Circuit.                                                                                                                                                                                       |

| 35    | IN_B            | Attenuator B RF Input. Internally matched to $50\Omega$ over the operating frequency band. This pin, if used, requires a DC block. If this attenuator is not used, the pin can be left unconnected.                                                                                                           |

| _     | EP              | Exposed Pad. Internally connected to GND. Solder this exposed pad to a PCB pad that uses multiple ground vias to provide heat transfer out of the device into the PCB ground planes. These multiple via grounds are also required to achieve the noted RF performance. See the Layout Considerations section. |

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

## **Detailed Description**

The MAX19792 is a dual general-purpose analog VVA designed to interface with  $50\Omega$  systems operating in the 500MHz to 4000MHz frequency range. Each attenuator provides 23.2dB of attenuation range with a linear control slope of 8.5dB/V. Both attenuators share a common analog control and can be cascaded together to yield 46.4dB of total dynamic range with a combined linear control slope of 17dB/V. Alternatively, the on-chip 4-wire SPI-controlled 10-bit DAC can be used to control both attenuators. In addition, a step-up/down feature allows user-programmable attenuator stepping through command pulses without reprogramming the SPI interface.

## **Applications Information**

### **Attenuation Control and Features**

The device has various states used to control the analog attenuator along with some monitoring conditions. The device can be controlled by an external control voltage, an internal SPI bus, or a combination of the two. The various states are described in Table 1. The SPI bus has multiple registers used to control the device when not configured for the analog-only mode. For cases where CTRL is used, the control range is 1V to 4V for  $V_{CC} = 5V$ , and is 1V to 2.5V for  $V_{CC} = 3.3V$ .

Up to 23.2dB of attenuation control range is provided per attenuator. At the insertion-loss setting, the single attenuator's loss is approximately 2.7dB. If a larger attenuation-control range is desired, the second on-chip attenuator can be connected in series to provide an additional 23.2dB of gain-control range.

Note that the on-chip control driver simultaneously adjusts both on-chip attenuators. It is suggested that a current-limiting resistor be included in series with CTRL to limit the input current to less than 40mA, should the control voltage be applied when  $V_{CC}$  is not present. A series resistor of greater than  $200\Omega$  provides complete protection for 5V control voltage ranges.

### **Analog-Only Mode Control**

In the Table 1 state (0, 0), the attenuators are controlled using a voltage applied to the CTRL pin of the device and the on-chip DAC is disabled. In cases where features of the SPI bus are not needed, the part can be operated in a pure analog control mode by grounding pins 14–25. This method allows the MAX19792 to be pin compatible with the MAX19790.

#### **DAC Mode Control**

In the Table 1 state (1, 0), the attenuators are controlled by the on-chip 10-bit DAC register. See the *Register Mode Up/Down Operation* section. In this condition, no signal is applied to the CTRL pin and the load on the CTRL pin should be >  $100k\Omega$ . The DAC is set using the SPI-loaded code in the registers, along with the setting of the MODE pin.

# Analog Mode Control with Alarm Monitoring

In the Table 1 state (0, 1), the attenuators are controlled using a voltage applied to the CTRL pin of the device. See the *Register Mode Up/Down Operation* section. In this condition, the DAC is enabled and a voltage is also applied to the CTRL pin. The on-chip switches are set to compare the DAC voltage to the CTRL voltage at the comparator input; the output of the comparator (COMP\_OUT) trips from high to low when VCTRL exceeds the on-chip DAC voltage.

#### **DAC Test Mode**

In the Table 1 state (1, 1), the attenuators are controlled by the on-chip 10-bit DAC register. See the *Register Mode Up/Down Operation* section. In this condition, the DAC is enabled and the DAC voltage appears at the CTRL pin. In this condition, no signal can be applied to the CTRL pin and the load on the CTRL pin should be >  $100k\Omega$ . This mode is only used in production testing of the DAC voltage and is not recommended for customer use.

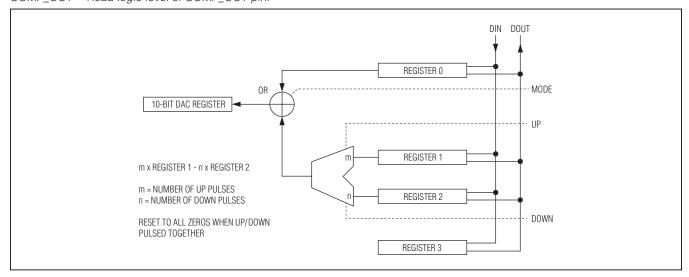

### **Register Mode Up/Down Operation**

The device has four 13-bit registers that are used for the operation of the device. The first bit is the read/write bit, the following two are address bits, and the remaining 10 are the desired data bits. The read/write bit determines whether the register is being written to or read from. The next two address bits select the desired register to write or read from. These address bits can be seen in Table 2. Table 3 describes the contents of the four registers.

Figure 1 shows the configuration of the internal registers of the device and Figure 2 shows the timing of the SPI bus. Register 0 sets the DAC code to the desired value, register 1 selects the step-up code, and register 2 selects the step-down code.

The device also contains a mode control pin (Table 4), along with UP and DWN controls (Table 5). When MODE is 0, the contents of register 0 get loaded into the 10-bit DAC register and set the value of the on-chip DAC. In this condition, the UP and DWN control pins have no effect on

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

the part. In MODE 1, the effective DAC code fed to the 10-bit DAC register is equal to:

m x Register 1 - n x Register 2

where m and n are the number of UP and DWN control steps accumulated, respectively.

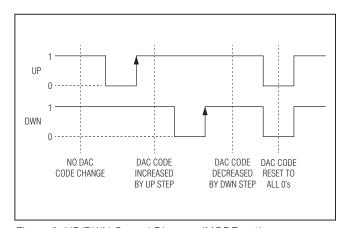

After powering up the device, UP and DWN should both be set to 0 to reset the m and n counters to 0. This results in a 10-bit all 0 code out of the mathematical block in Figure 1, and applied to the 10-bit DAC register that drives the DAC. To increase (decrease) the code using the UP (DWN) pin, the DWN (UP) pin must be high and the UP (DWN) pin should be pulsed low to high. The device is designed to produce no wraparounds when using UP and DWN stepping so that the DAC code maxes out at 1023 or goes no lower than 0. See Figure 3 for the UP and DWN control operation.

Switching back to MODE = 0 produces the same 10-bit DAC code as was previously loaded into register 0. Switching back to MODE = 1 results in the previous 10-bit DAC code from the register 1 and 2 combiner/multiplier block.

Register 3 is used to set the RDBK\_EN register in the write mode and is used to read back the RDBK\_EN register and COMP\_OUT in the read mode.

### SPI Interface

The device can be controlled with a 4-wire, SPI-compatible serial interface. Figure 2 shows a timing diagram for the interface. In the write mode, a 13-bit word is loaded into the device through the DIN pin, with  $\overline{\text{CS}}$  set low. The first bit of the word in the write mode is 0, and the next two bits select the register to be written to (Table 2). The next 10 bits contain the data to be written to the selected register. After the 13 bits are shifted in, a low-to-high  $\overline{\text{CS}}$  command is applied and this latches the 10 bits into the selected register. The entire write command is ignored if  $\overline{\text{CS}}$  is pulsed low to high before the last data bit is successfully captured.

For the read cycle, the first bit clocked in is a 1 and this establishes that a register is to be read. The next two clocked bits form the address of the register to be read (Table 2). In this read mode, data starts to get clocked out of the DOUT pin after A0 is captured. The DOUT pin goes to a high-impedance state after the 10 bits are transmitted or if  $\overline{\text{CS}}$  goes high at any point during the transmission.

### **Voltage Reference**

The device has an on-chip voltage reference for the DAC and a provision to operate with an off-chip reference. Table 6 provides details in selecting the desired reference.

**Table 1. Attenuator Control Logic States**

| DAC_LOGIC | RDBK_EN<br>(D9, REG 3) | INTERNAL SWITCH<br>STATES        | ATTENUATOR                                                                                                                                                                                                                       | 10-BIT DAC                                                             |

|-----------|------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 0         | 0                      | S1 = closed<br>S2, S3, S4 = open | Controlled by an external analog voltage on the CTRL pin.                                                                                                                                                                        | Disabled                                                               |

| 1         | 0                      | S1, S3, S4 = open<br>S2 = closed | Controlled by an on-chip DAC; no voltage is applied to the CTRL pin.                                                                                                                                                             | Enabled                                                                |

| 0         | 1                      | S1, S3, S4 = closed<br>S2 = open | Controlled by an external analog voltage on the CTRL pin. CTRL is compared with the DAC output. The comparator drives the COMP_OUT pin.                                                                                          | Enabled<br>(update DAC code<br>to estimate voltage<br>on the CTRL pin) |

| 1         | 1                      | S1, S2 = closed<br>S3, S4 = open | Controlled by an on-chip DAC. The DAC output is connected to the CTRL pin. This state can be used to test the DAC output. In this condition, no voltage can be applied to the CTRL pin and the load on this pin must be > 100kΩ. | Enabled                                                                |

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

**Table 2. Address Data Bits**

| R/W | A1 | A0 | DESCRIPTION                     |

|-----|----|----|---------------------------------|

| 0   | 0  | 0  | Write to register 0 using DIN   |

| 0   | 0  | 1  | Write to register 1 using DIN   |

| 0   | 1  | 0  | Write to register 2 using DIN   |

| 0   | 1  | 1  | Write to register 3 using DIN   |

| 1   | 0  | 0  | Read from register 0 using DOUT |

| 1   | 0  | 1  | Read from register 1 using DOUT |

| 1   | 1  | 0  | Read from register 2 using DOUT |

| 1   | 1  | 1  | Read from register 3 using DOUT |

**Table 3. Register Definitions**

| D9                                                  | D8                                                | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0            |

|-----------------------------------------------------|---------------------------------------------------|----|----|----|----|----|----|----|---------------|

| REGISTER 0 (Read/Write Bits, 10-Bit DAC Code)       |                                                   |    |    |    |    |    |    |    |               |

| DAC MSB                                             | _                                                 | _  | _  | _  | _  | _  | _  | _  | DAC LSB       |

| REGISTER 1 (Read/W                                  | REGISTER 1 (Read/Write Bits, 10-Bit Step-Up Code) |    |    |    |    |    |    |    |               |

| Step-up MSB                                         | _                                                 | _  | _  | _  | _  | _  | _  | _  | Step-up LSB   |

| REGISTER 2 (Read/Write Bits, 10-Bit Step-Down Code) |                                                   |    |    |    |    |    |    |    |               |

| Step-down MSB                                       | _                                                 | _  | _  | _  | _  | _  | _  | _  | Step-down LSB |

| REGISTER 3 (Write Bits)*                            |                                                   |    |    |    |    |    |    |    |               |

| RDBK_EN                                             | Not used (set to 0)                               |    |    |    |    |    |    |    |               |

| REGISTER 3 (Read B                                  | REGISTER 3 (Read Bits)**                          |    |    |    |    |    |    |    |               |

| RDBK_EN                                             | COMP_<br>OUT Not used (set to 0)                  |    |    |    |    |    |    |    |               |

<sup>\*</sup>RDBK\_EN = Enable bit for the voltage comparator that drives the COMP\_OUT pin.

<sup>\*\*</sup>RDBK\_EN = Enable bit for the voltage comparator that drives the COMP\_OUT pin. COMP\_OUT = Read logic level of COMP\_OUT pin.

Figure 1. Register Configuration Diagram

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

## Table 4. Attenuator-Mode Control Logic State

| MODE PIN | ATTENUATOR                                                                                                                               |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | SPI-mode control (the DAC code is located in register 0).                                                                                |

| 1        | Step-mode control using the UP and DWN pins (the step-up code is located in register 1 and the step-down code is located in register 2). |

# Table 5. Step-Mode Logic State (MODE = 1)

| UP            | DWN           | ATTENUATOR                                                                                                         |

|---------------|---------------|--------------------------------------------------------------------------------------------------------------------|

| Logic 0       | Logic 0       | Reset the DAC for the minimum attenuation state (DAC code = 0000000000).                                           |

| Logic 0 pulse | Logic 1       | Increase the DAC code* by the amount located in register 1.  UP is pulsed from high to low to high (see Figure 3). |

| Logic 1       | Logic 0 pulse | Decrease the DAC code* by amount located in register 2.  DWN is pulsed from high to low to high (see Figure 3).    |

<sup>\*</sup>Continued UP or DWN stepping results in saturation (no code wrapping).

### Table 6. REF\_SEL Logic State

| REF_SEL | DAC REFERENCE                                               |

|---------|-------------------------------------------------------------|

| 0       | Uses an on-chip DAC reference.                              |

| 1       | User provides off-chip DAC reference voltage on REF_IN pin. |

### **SPI Interface Programming**

Figure 2. SPI Timing Diagram

Figure 3. UP/DWN Control Diagram (MODE = 1)

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

### **Layout Considerations**

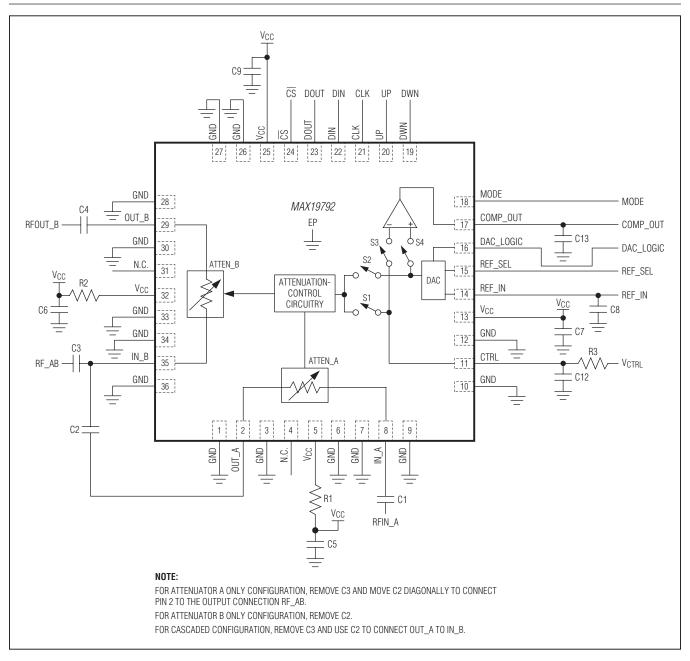

A properly designed PCB is an essential part of any RF/ microwave circuit. Keep RF signal lines as short as possible to reduce losses, radiation, and inductance. For best performance, route the ground-pin traces directly to the exposed pad underneath the package. This pad MUST be connected to the ground plane of the board by using multiple vias under the device to provide the best RF and thermal conduction path. Solder the exposed pad on the bottom of the device package to a PCB. Pins 4 and 31 for the MAX19792 have no internal connection. These two pins are in place to support the MAX19794 part in the family. The MAX19794 requires an additional bypass capacitor on each of these pins for proper operation. If desired to have a common layout to support the MAX19794, then include these capacitors in the common layout. Refer to the MAX19794 data sheet for details.

### **Power-Supply Bypassing**

Proper voltage-supply bypassing is essential for high-frequency circuit stability. Bypass each V<sub>CC</sub> pin with capacitors placed as close as possible to the device. Place the smallest capacitor closest to the device. See the *Typical Application Circuit* and Table 7 for details.

### Exposed Pad RF and Thermal Considerations

The exposed pad (EP) of the device's 36-pin TQFN package provides a low thermal-resistance path to the die. It is important that the PCB on which the IC is mounted be designed to conduct heat from this contact.

In addition, provide the EP with a low-inductance RF ground path for the device. The EP must be soldered to a ground plane on the PCB, either directly or through an array of plated via holes. Soldering the pad to ground is also critical for efficient heat transfer. Use a solid ground plane wherever possible.

Table 7. Typical Application Circuit Component Values

| DECICNATION     | OTV | DESCRIPTION                                                                                                                                                                                                                                                           |  |  |

|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DESIGNATION QTY |     | DESCRIPTION                                                                                                                                                                                                                                                           |  |  |

| C1, C2, C4      | 3   | 22pF ±5%, 50V C0G ceramic capacitors (0402)                                                                                                                                                                                                                           |  |  |

| C3              | 1   | 22pF ±5%, 50V C0G ceramic capacitors (0402) Not installed for two attenuators in cascade.                                                                                                                                                                             |  |  |

| C5–C9           | 5   | 1000pF ±5%, 50V C0G ceramic capacitors (0402)                                                                                                                                                                                                                         |  |  |

| C12             | 1   | 120pF ±5%, 50V C0G ceramic capacitor (0402) Provides some external noise filtering along with R3.                                                                                                                                                                     |  |  |

| C13             | 0   | Not installed, 4.7pF capacitor could be used to reduce any potential rise time glitching when the comparator changes state.                                                                                                                                           |  |  |

| R1, R2          | 2   | 10Ω ±5% resistors* (0402)                                                                                                                                                                                                                                             |  |  |

| R3              | 1   | 200Ω ±5% resistor (0402) Use this resistor to provide some lowpass noise filtering when used with C12. The value of R3 slows down the response time. R3 also provides protection for the device in case V <sub>CTRL</sub> is applied without V <sub>CC</sub> present. |  |  |

| U1              | 1   | Maxim MAX19792                                                                                                                                                                                                                                                        |  |  |

<sup>\*</sup>Add two additional 10 $\Omega$  series resistors between  $V_{CC}$ 's leading to C5 and C6, unless a  $V_{CC}$  power plane is used.

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

# **Typical Application Circuit**

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

### **Ordering Information**

| PART          | TEMP RANGE      | PIN-PACKAGE |

|---------------|-----------------|-------------|

| MAX19792ETX+  | -40°C to +100°C | 36 TQFN-EP* |

| MAX19792ETX+T | -40°C to +100°C | 36 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

PROCESS: SiGe BiCMOS

# **Chip Information**

# **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE        | LAND        |

|------------|---------|----------------|-------------|

| TYPE       | CODE    | NO.            | PATTERN NO. |

| 36 TQFN-EP | T3666+2 | <u>21-0141</u> |             |

<sup>\*</sup>EP = Exposed pad.

T = Tape and reel.

# 500MHz to 4000MHz Dual Analog Voltage Variable Attenuator with On-Chip 10-Bit SPI-Controlled DAC

## **Revision History**

| REVISIOI<br>NUMBER |      | DESCRIPTION                                                    | PAGES<br>CHANGED                     |

|--------------------|------|----------------------------------------------------------------|--------------------------------------|

| 0                  | 6/12 | Initial release                                                | _                                    |

| 1                  | 9/12 | Updated Electrical Characteristics table, corrected TOC titles | 3, 4, 6, 7, 8, 9,<br>10, 11, 12, 13, |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.