# Quad/Octal Input Network Clock Generator/Synchronizer

Data Sheet AD9548

#### **FEATURES**

Supports Stratum 2 stability in holdover mode Supports reference switchover with phase build-out Supports hitless reference switchover Auto/manual holdover and reference switchover

4 pairs of reference input pins with each pair configurable as a single differential input or as 2 independent single-ended inputs

Input reference frequencies from 1 Hz to 750 MHz

Reference validation and frequency monitoring (1 ppm)

Programmable input reference switchover priority

30-bit programmable input reference divider

4 pairs of clock output pins with each pair configurable as a single differential LVDS/LVPECL output or as 2 single-

Output frequencies up to 450 MHz

ended CMOS outputs

30-bit integer and 10-bit fractional programmable feedback divider

Programmable digital loop filter covering loop bandwidths from 0.001 Hz to 100 kHz

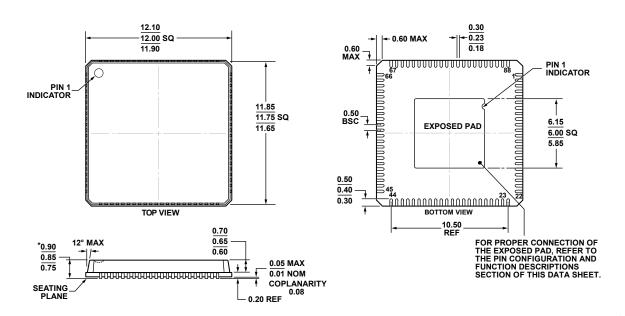

Optional low noise LC-VCO system clock multiplier Optional crystal resonator for system clock input On-chip EEPROM to store multiple power-up profiles Software controlled power-down 88-lead LFCSP package

#### **APPLICATIONS**

Network synchronization

Cleanup of reference clock jitter

GPS 1 pulse per second synchronization

SONET/SDH clocks up to OC-192, including FEC

Stratum 2 holdover, jitter cleanup, and phase transient control

Stratum 3E and Stratum 3 reference clocks Wireless base station controllers Cable infrastructure Data communications

#### **GENERAL DESCRIPTION**

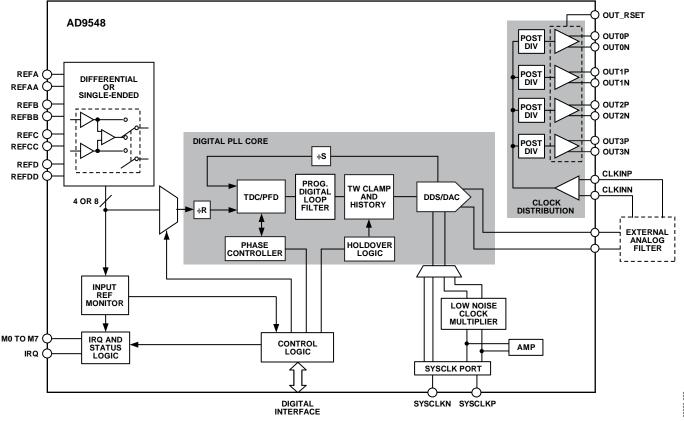

The AD9548 provides synchronization for many systems, including synchronous optical networks (SONET/SDH). The AD9548 generates an output clock synchronized to one of up to four differential or eight single-ended external input references. The digital PLL allows for reduction of input time jitter or phase noise associated with the external references. The AD9548 continuously generates a clean (low jitter), valid output clock even when all references have failed by means of a digitally controlled loop and holdover circuitry.

The AD9548 operates over an industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

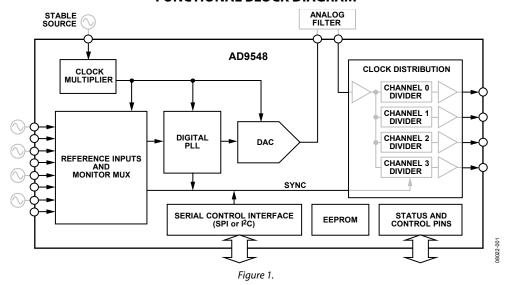

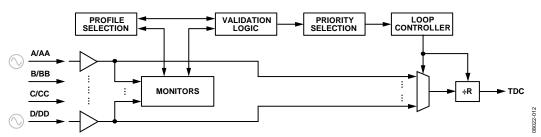

#### **FUNCTIONAL BLOCK DIAGRAM**

**Data Sheet**

## AD9548

## **TABLE OF CONTENTS**

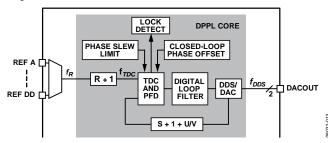

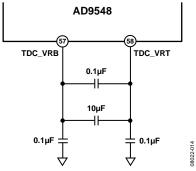

| Features 1                                         | Digital PLL (DPLL) Core32                                                    |

|----------------------------------------------------|------------------------------------------------------------------------------|

| Applications 1                                     | Direct Digital Synthesizer                                                   |

| General Description1                               | Tuning Word Processing                                                       |

| Functional Block Diagram1                          | Loop Control State Machine                                                   |

| Revision History                                   | System Clock Inputs                                                          |

| Specifications4                                    | SYSCLK PLL Multiplier                                                        |

| Supply Voltage4                                    | Clock Distribution40                                                         |

| Supply Current4                                    | Status and Control                                                           |

| Power Dissipation4                                 | Multifunction Pins (M0 to M7)44                                              |

| Logic Inputs (M7 to M0, RESET, TDI, TCLK, TMS)5    | IRQ Pin45                                                                    |

| Logic Outputs (M7 to M0, IRQ, TDO)5                | Watchdog Timer46                                                             |

| System Clock Inputs (SYSCLKP/SYSCLKN)5             | EEPROM46                                                                     |

| Distribution Clock Inputs (CLKINP/CLKINN)6         | Serial Control Port51                                                        |

| Reference Inputs (REFA/REFAA to REFD/REFDD)        | SPI/I <sup>2</sup> C Port Selection                                          |

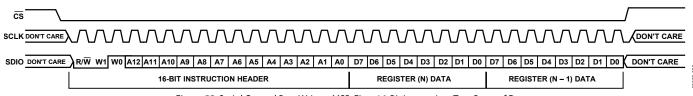

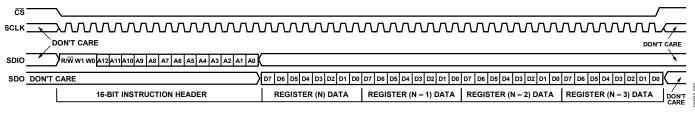

| Reference Monitors                                 | SPI Serial Port Operation51                                                  |

| Reference Switchover Specifications 8              | I <sup>2</sup> C Serial Port Operation56                                     |

| Distribution Clock Outputs (OUT0 to OUT3)8         | Input/Output Programming Registers                                           |

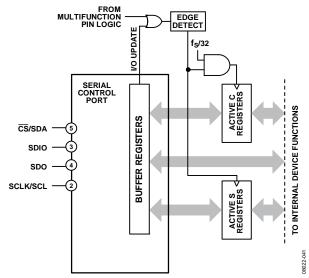

| DAC Output Characteristics (DACOUTP/DACOUTN) 9     | Buffered/Active Registers                                                    |

| Time Duration of Digital Functions10               | Autoclear Registers                                                          |

| Digital PLL10                                      | Register Access Restrictions                                                 |

| Digital PLL Lock Detection10                       | Register Map60                                                               |

| Holdover Specifications                            | Register Map Bit Descriptions                                                |

| Serial Port Specifications—SPI Mode11              | Serial Port Configuration (Register 0x0000 to                                |

| Serial Port Specifications—I <sup>2</sup> C Mode11 | Register 0x0005)70                                                           |

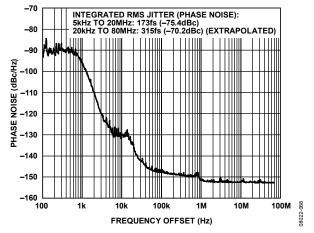

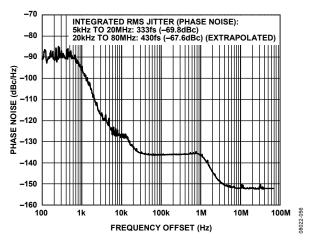

| Jitter Generation                                  | System Clock (Register 0x0100 to Register 0x0108)                            |

| Absolute Maximum Ratings14                         | General Configuration (Register 0x0200 to Register 0x0214) 72                |

| ESD Caution14                                      | DPLL Configuration (Register 0x0300 to Register 0x031B) 75                   |

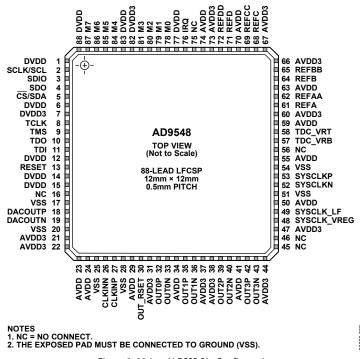

| Pin Configuration and Function Descriptions15      | Clock Distribution Output Configuration (Register 0x0400 to Register 0x0419) |

| Typical Performance Characteristics                | Reference Input Configuration (Register 0x0500 to                            |

| nput/Output Termination Recommendations            | Register 0x0507)81                                                           |

| Getting Started24                                  | Profile Registers (Register 0x0600 to Register 0x07FF) 83                    |

| Power-On Reset                                     | Operational Controls (Register 0x0A00 to Register 0x0A10) 92                 |

| Initial M0 to M7 Pin Programming24                 | Clock Part Serial ID (Register 0x0C00 to Register 0x0C07) 97                 |

| Device Register Programming24                      | Status Readback (Register 0x0D00 to Register 0x0D19) 97                      |

| Theory of Operation26                              | Nonvolatile Memory (EEPROM) Control (Register 0x0E00 to                      |

| Overview                                           | Register 0x0E03)                                                             |

| Reference Clock Inputs                             | EEPROM Storage Sequence (Register 0x0E10 to                                  |

| Reference Monitors                                 | Register 0x0E3F)                                                             |

| Reference Profiles                                 | Power Supply Partitions 106                                                  |

| Reference Switchover                               | 3.3 V Supplies                                                               |

| 1.8 V Supplies 106                                                | Calculation of the $\gamma$ Register Values                       | 110   |

|-------------------------------------------------------------------|-------------------------------------------------------------------|-------|

| Thermal Performance                                               | Calculation of the δ Register Values                              | 110   |

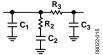

| Calculating Digital Filter Coefficients                           | Outline Dimensions                                                |       |

| Calculation of the $\alpha$ Register Values                       | Ordering Guide                                                    | 113   |

| Calculation of the β Register Values109                           | •                                                                 |       |

| REVISION HISTORY                                                  |                                                                   |       |

| 12/14—Rev. F to Rev. G                                            | Changes to Read Section                                           | 52    |

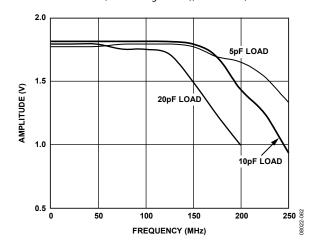

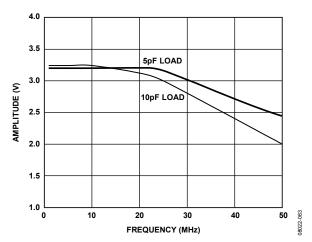

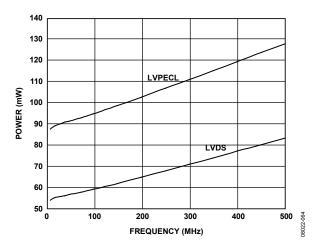

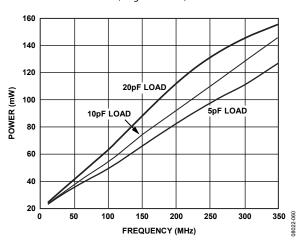

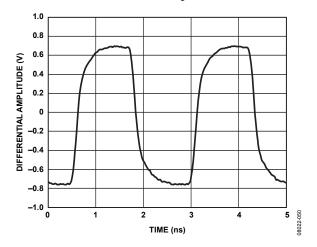

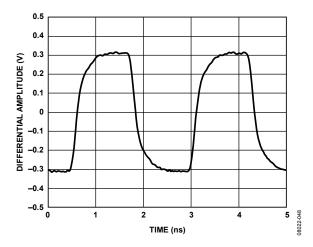

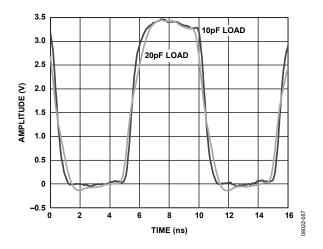

| Changes to Figure 7 Caption to Figure 12 Caption19                | Added Figure 56                                                   |       |

| Changes to System Clock Period Section39                          | Changes to t <sub>C</sub> Parameter, Description Column, Table 33 |       |

| Changes to Table 3662                                             | Added Table Summary Statement, Table 36                           |       |

| C.141.960 to 140.000                                              | Changes to Table 36                                               |       |

| 6/14—Rev. E to Rev. F                                             | Added User Scratch Pad (Eight Bytes), Address 0x0C00 to           |       |

| Changes to Table 2115                                             | Address 0x0C07, Table 36                                          | 67    |

| Added Figure 34; Renumbered Sequentially23                        | Changes to Table 39                                               |       |

| Changed Initial Pin Programming Section to Initial M0 to M7       | Added Clock Part Serial ID (Register 0x0C00 to                    |       |

| Pin Programming Section24                                         | Register 0x0C07) Section and Table 131                            | 98    |

| Changes to Frequency Tuning Word History Section36                | Changes to Table 142                                              |       |

| Added Disabling Accidental Automatic EEPROM Download              | Added Table 153                                                   |       |

| Section48                                                         | Added Table 154                                                   |       |

| Changes to Buffered/Active Registers Section59                    |                                                                   |       |

| Changes to Register Map Section, Opt Column, Table 3660           | 7/11—Rev. A to Rev. B                                             |       |

| Changes to Table 65                                               | Changed AD9584 to AD9548                                          | 32    |

|                                                                   | Changed 437,749,988,378,041 to 43,774,988,378,041                 |       |

| 12/13—Rev. D to Rev. E                                            | Change to Calculating Digital Filter Coefficients Section         |       |

| Changes to Calculating Digital Filter Coefficients Section109     |                                                                   |       |

| Changes to Calculation of the $\alpha$ Register Values Section110 | 10/10—Rev. 0 to Rev. A                                            |       |

| Change to Careanine of the street tales of the control minimize   | Changes to Timing Parameter, Table 17                             | 1     |

| 6/13—Rev. C to Rev. D                                             | Added Low Loop Bandwidth Applications Using a TCXO/OCX            |       |

| Change to Table 1610                                              | Section and Choosing a System Clock Oscillator Frequency          |       |

| Changes to IRQ Pin Section46                                      | Section                                                           |       |

| Changes to Programming the EEPROM to Include a Clock              | Moved System Clock Period Section                                 | 39    |

| Part ID Section50                                                 | Changes to Addr 0002, Table 35                                    | 60    |

| Changes to Bit 0, Table 12194                                     | Changes to Addr 0600, Table 35                                    |       |

| Changes to Status Readback (Register 0x0D00 to Register           | Changes to Addr 0632, Table 35                                    | 63    |

| 0x0D19) Section98                                                 | Changes to Addr 0680, Table 35                                    |       |

| · · · · · · · · · · · · · · · · · · ·                             | Changes to Addr 06B2, Table 35                                    | 65    |

| 2/13—Rev. B to Rev. C                                             | Changes to Address 0002 Description, Table 38                     |       |

| Change to Pin 53, Description Column, Table 2117                  | Changes to Bit 7 and Bit 6, Table 78                              |       |

| Added Figure 33, Renumbered Sequentially23                        | Changes to Address 0629 and Address 062A, Table 87 and B          |       |

| Changes to Automatic Priority-Based Reference Switchover          | and Bit 6, Table 88                                               | 85    |

| Section; Added Table 23, Renumbered Sequentially30                | Changes to Address 065B and Address 065C, Table 97 and E          | 3it 7 |

| Changes to Low Loop Bandwidth Applications Using a                | and Bit 6, Table 98                                               | 87    |

| TCXO/OCXO Section                                                 | Changes to Address 06A9 and Address 06AA, Table 107               |       |

| Changes to EEPROM Upload Section and EEPROM                       | Changes to Bit 7 and Bit 6, Table 108                             |       |

| Download Section48                                                | Changes to Address 06DB and Address 06DC, Table 117               |       |

| Added Programming the EEPROM to Include a Clock                   |                                                                   |       |

| Part ID Section 50                                                | 4/09—Revision 0: Initial Version                                  |       |

## **SPECIFICATIONS**

Minimum (min) and maximum (max) values apply for the full range of supply voltage and operating temperature variations. Typical (typ) values apply for AVDD3 = DVDD\_I/O = 3.3 V; AVDD = DVDD = 1.8 V;  $T_A = 25 ^{\circ}\text{C}$ ;  $I_{DAC} = 20 \text{ mA}$  (full scale), unless otherwise noted.

#### **SUPPLY VOLTAGE**

Table 1.

| Parameter                  | Min   | Тур  | Max   | Unit | Test Conditions/Comments                                        |

|----------------------------|-------|------|-------|------|-----------------------------------------------------------------|

| SUPPLY VOLTAGE             |       |      |       |      |                                                                 |

| DVDD3                      | 3.135 | 3.30 | 3.465 | V    | Pin 7, Pin 82                                                   |

| DVDD                       | 1.71  | 1.80 | 1.89  | V    | Pin 1, Pin 6, Pin 12, Pin 14, Pin 15, Pin 77, Pin 83, Pin 88    |

| AVDD3                      | 3.135 | 3.30 | 3.465 | V    | Pin 21, Pin 22, Pin 47, Pin 60, Pin 66, Pin 67, Pin 73          |

| 3.3 V Supply (Typical)     | 3.135 | 3.30 | 3.465 | V    | Pin 31, Pin 37, Pin 38, Pin 44                                  |

| 1.8 V Supply (Alternative) | 1.71  | 1.80 | 1.89  | V    | Pin 31, Pin 37, Pin 38, Pin 44                                  |

| AVDD                       | 1.71  | 1.80 | 1.89  | V    | Pin 23, Pin 24, Pin 29, Pin 34, Pin 41, Pin 50, Pin 55, Pin 59, |

|                            |       |      |       |      | Pin 63, Pin 70, Pin 74                                          |

#### **SUPPLY CURRENT**

The test conditions for the maximum (max) supply current are the same as the test conditions for the All Blocks Running parameter of Table 3. The test conditions for the typical (typ) supply current are the same as the test conditions for the Typical Configuration parameter of Table 3.

Table 2.

| Parameter                  | Min | Тур | Max | Unit | Test Conditions/Comments                                                               |

|----------------------------|-----|-----|-----|------|----------------------------------------------------------------------------------------|

| SUPPLY CURRENT             |     |     |     |      |                                                                                        |

| I <sub>DVDD3</sub>         |     | 1.5 | 3   | mA   | Pin 7, Pin 82                                                                          |

| $I_{DVDD}$                 |     | 190 | 215 | mA   | Pin 1, Pin 6, Pin 12, Pin 14, Pin 15, Pin 77, Pin 83, Pin 88                           |

| I <sub>AVDD3</sub>         |     | 52  | 75  | mA   | Pin 21, Pin 22, Pin 47, Pin 60, Pin 66, Pin 67, Pin 73                                 |

| $I_{AVDD3}$                |     |     |     |      |                                                                                        |

| 3.3 V Supply (Typical)     |     | 24  | 110 | mA   | Pin 31, Pin 37, Pin 38, Pin 44                                                         |

| 1.8 V Supply (Alternative) |     | 24  | 110 | mA   | Pin 31, Pin 37, Pin 38, Pin 44                                                         |

| lavdd                      |     | 135 | 163 | mA   | Pin 23, Pin 24, Pin 29, Pin 34, Pin 41, Pin 50, Pin 55, Pin 59, Pin 63, Pin 70, Pin 74 |

#### **POWER DISSIPATION**

Table 3.

| Parameter             | Min | Тур | Max  | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                              |

|-----------------------|-----|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER DISSIPATION     |     |     |      |      |                                                                                                                                                                                                                                                                                       |

| Typical Configuration |     | 800 | 1100 | mW   | f <sub>SYSCLK</sub> = 20 MHz <sup>1</sup> ; f <sub>s</sub> = 1 GHz <sup>2</sup> ; f <sub>DDS</sub> = 122.88 MHz <sup>3</sup> ; one LVPECL clock distribution output running at 122.88 MHz (all others powered down); one input reference running at 100 MHz (all others powered down) |

| All Blocks Running    |     | 900 | 1400 | mW   | $f_{SYSCLK} = 20 \text{ MHz}^1$ ; $f_S = 1 \text{ GHz}^2$ ; $f_{DDS} = 399 \text{ MHz}^3$ ; all clock distribution outputs configured as LVPECL at 399 MHz; all input references configured as differential at 100 MHz; fractional-N active (R = 10, S = 39, U = 9, V = 10)           |

| Full Power-Down       |     | 13  |      | mW   | Conditions = typical configuration; no external pull-up or pull-down resistors                                                                                                                                                                                                        |

| Parameter                     | Min | Тур  | Max | Unit | Test Conditions/Comments                                                                                  |

|-------------------------------|-----|------|-----|------|-----------------------------------------------------------------------------------------------------------|

| Incremental Power Dissipation |     |      |     |      | Conditions = typical configuration; table values show the change in power due to the indicated operation. |

| SYSCLK PLL Off                |     | -105 |     | mW   | $f_{SYSCLK} = 1 \text{ GHz}^1$ ; high frequency direct input mode.                                        |

| Input Reference On            |     |      |     |      |                                                                                                           |

| Differential                  |     | 7    |     | mW   |                                                                                                           |

| Single-Ended                  |     | 13   |     | mW   |                                                                                                           |

| Output Distribution Driver On |     |      |     |      |                                                                                                           |

| LVDS                          |     | 70   |     | mW   |                                                                                                           |

| LVPECL                        |     | 75   |     | mW   |                                                                                                           |

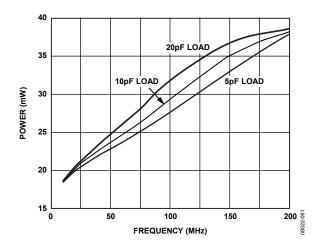

| CMOS                          |     | 65   |     | mW   | A single 3.3 V CMOS output with a 10 pF load.                                                             |

$<sup>^1</sup>$  fsysclk is the frequency at the SYSCLKP and SYSCLKN pins.  $^2$  fs is the sample rate of the output DAC.  $^3$  fDDS is the output frequency of the DDS.

#### LOGIC INPUTS (M7 TO M0, RESET, TDI, TCLK, TMS)

#### Table 4.

| Parameter                                            | Min | Тур | Max  | Unit | Test Conditions/Comments |

|------------------------------------------------------|-----|-----|------|------|--------------------------|

| LOGIC INPUTS (M7 to M0, RESET, TDI, TCLK, TMS)       |     |     |      |      |                          |

| Input High Voltage (V <sub>IH</sub> )                | 2.1 |     |      | V    |                          |

| Input Low Voltage (V <sub>IL</sub> )                 |     |     | 0.8  | V    |                          |

| Input Current (I <sub>INH</sub> , I <sub>INL</sub> ) |     | ±80 | ±200 | μΑ   |                          |

| Input Capacitance (C <sub>IN</sub> )                 |     | 3   |      | pF   |                          |

## LOGIC OUTPUTS (M7 TO M0, IRQ, TDO)

#### Table 5.

| Parameter                              | Min | Тур | Max | Unit | Test Conditions/Comments |

|----------------------------------------|-----|-----|-----|------|--------------------------|

| LOGIC OUTPUTS (M7 to M0, IRQ, TDO)     |     |     |     |      |                          |

| Output High Voltage (V <sub>OH</sub> ) | 2.7 |     |     | V    | I <sub>OH</sub> = 1 mA   |

| Output Low Voltage (V <sub>OL</sub> )  |     |     | 0.4 | V    | $I_{OL} = 1 \text{ mA}$  |

| IRQ Leakage Current                    |     |     |     |      | Open-drain mode          |

| Active Low Output Mode                 |     |     | 1   | μΑ   | V <sub>OH</sub> = 3.3 V  |

| Active High Output Mode                |     |     | 1   | μΑ   | $V_{OL} = -0 V$          |

#### SYSTEM CLOCK INPUTS (SYSCLKP/SYSCLKN)

#### Table 6.

| Parameter                              | Min  | Тур | Max  | Unit   | Test Conditions/Comments                                                                                                                                                                                                 |

|----------------------------------------|------|-----|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM CLOCK PLL BYPASSED              |      |     |      |        |                                                                                                                                                                                                                          |

| Input Frequency Range                  | 500  |     | 1000 | MHz    |                                                                                                                                                                                                                          |

| Minimum Input Slew Rate                | 1000 |     |      | V/µs   | Minimum limit imposed for jitter performance                                                                                                                                                                             |

| Duty Cycle                             | 40   |     | 60   | %      |                                                                                                                                                                                                                          |

| Common-Mode Voltage                    |      | 1.2 |      | V      | Internally generated                                                                                                                                                                                                     |

| Differential Input Voltage Sensitivity | 100  |     |      | mV p-p | Minimum voltage across pins required to ensure switching between logic states; the instantaneous voltage on either pin must not exceed the supply rails; can accommodate single-ended input by ac grounding unused input |

| Input Capacitance                      |      | 2   |      | pF     | Single-ended, each pin                                                                                                                                                                                                   |

| Input Resistance                       |      | 2.5 |      | kΩ     |                                                                                                                                                                                                                          |

| Parameter                              | Min   | Тур | Max  | Unit   | Test Conditions/Comments                                                                                                                                                                                                 |

|----------------------------------------|-------|-----|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM CLOCK PLL ENABLED               |       |     |      |        |                                                                                                                                                                                                                          |

| PLL Output Frequency Range             | 900   |     | 1000 | MHz    |                                                                                                                                                                                                                          |

| Phase-Frequency Detector (PFD) Rate    |       |     | 150  | MHz    |                                                                                                                                                                                                                          |

| Frequency Multiplication Range         | 6     |     | 255  |        | Assumes valid system clock and PFD rates                                                                                                                                                                                 |

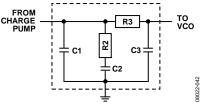

| VCO Gain                               |       | 70  |      | MHz/V  |                                                                                                                                                                                                                          |

| High Frequency Path                    |       |     |      |        |                                                                                                                                                                                                                          |

| Input Frequency Range                  | 100.1 |     | 500  | MHz    |                                                                                                                                                                                                                          |

| Minimum Input Slew Rate                | 200   |     |      | V/µs   | Minimum limit imposed for jitter performance                                                                                                                                                                             |

| Frequency Divider Range                | 1     |     | 8    |        | Binary steps (M = 1, 2, 4, 8)                                                                                                                                                                                            |

| Common-Mode Voltage                    |       | 1   |      | V      | Internally generated                                                                                                                                                                                                     |

| Differential Input Voltage Sensitivity | 100   |     |      | mV p-p | Minimum voltage across pins required to ensure switching between logic states; the instantaneous voltage on either pin must not exceed the supply rails; can accommodate single-ended input by ac grounding unused input |

| Input Capacitance                      |       | 3   |      | pF     | Single-ended, each pin                                                                                                                                                                                                   |

| Input Resistance                       |       | 2.5 |      | kΩ     |                                                                                                                                                                                                                          |

| Low Frequency Path                     |       |     |      |        |                                                                                                                                                                                                                          |

| Input Frequency Range                  | 3.5   |     | 100  | MHz    |                                                                                                                                                                                                                          |

| Minimum Input Slew Rate                | 50    |     |      | V/µs   | Minimum limit imposed for jitter performance                                                                                                                                                                             |

| Common-Mode Voltage                    |       | 1.2 |      | V      | Internally generated                                                                                                                                                                                                     |

| Differential Input Voltage Sensitivity | 100   |     |      | mV p-p | Minimum voltage across pins required to ensure switching between logic states; the instantaneous voltage on either pin must not exceed the supply rails; can accommodate single-ended input by ac grounding unused input |

| Input Capacitance                      |       | 3   |      | рF     | Single-ended, each pin                                                                                                                                                                                                   |

| Input Resistance                       |       | 4   |      | kΩ     |                                                                                                                                                                                                                          |

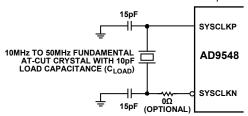

| Crystal Resonator Path                 |       |     |      |        |                                                                                                                                                                                                                          |

| Crystal Resonator Frequency Range      | 10    |     | 50   | MHz    | Fundamental mode, AT cut                                                                                                                                                                                                 |

| Maximum Crystal Motional Resistance    |       |     | 100  | Ω      | See the System Clock Inputs section for recommendations                                                                                                                                                                  |

## DISTRIBUTION CLOCK INPUTS (CLKINP/CLKINN)

Table 7.

| Parameter                                 | Min  | Тур | Max | Unit   | Test Conditions/Comments                                                                                                                                                 |

|-------------------------------------------|------|-----|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DISTRIBUTION CLOCK INPUTS (CLKINP/CLKINN) |      |     |     |        |                                                                                                                                                                          |

| Input Frequency Range                     | 62.5 |     | 500 | MHz    |                                                                                                                                                                          |

| Minimum Slew Rate                         | 75   |     |     | V/µs   | Minimum limit imposed for jitter performance.                                                                                                                            |

| Common-Mode Voltage                       |      | 700 |     | mV     | Internally generated.                                                                                                                                                    |

| Differential Input Voltage Sensitivity    | 100  |     |     | mV p-p | Capacitive coupling required; can accommodate single-ended input by ac grounding unused input; the instantaneous voltage on either pir must not exceed the supply rails. |

| Differential Input Power Sensitivity      | -15  |     |     | dBm    | The same as voltage sensitivity but specified as power into a 50 $\Omega$ load                                                                                           |

| Input Capacitance                         |      | 3   |     | pF     |                                                                                                                                                                          |

| Input Resistance                          |      | 5   |     | kΩ     | Each pin has a 2.5 k $\Omega$ internal dcbias resistance.                                                                                                                |

## REFERENCE INPUTS (REFA/REFAA TO REFD/REFDD)

Table 8.

| Parameter                              | Min | Тур | Max                 | Unit | Test Conditions/Comments                                                                                                                                             |

|----------------------------------------|-----|-----|---------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIFFERENTIAL OPERATION                 |     |     |                     |      |                                                                                                                                                                      |

| Frequency Range                        |     |     |                     |      |                                                                                                                                                                      |

| Sinusoidal Input                       | 10  |     | 750                 | MHz  |                                                                                                                                                                      |

| LVPECL Input                           | 1   |     | $750 \times 10^{6}$ | Hz   |                                                                                                                                                                      |

| LVDS Input                             | 1   |     | $750 \times 10^{6}$ | Hz   |                                                                                                                                                                      |

| Minimum Input Slew Rate                | 40  |     |                     | V/µs | Minimum limit imposed for jitter performance                                                                                                                         |

| Common-Mode Input Voltage              |     | 2   |                     | V    | Internally generated                                                                                                                                                 |

| Differential Input Voltage Sensitivity |     | ±65 |                     | mV   | Minimum differential voltage across pins required to ensure switching between logic levels; the instantaneous voltage on either pin must not exceed the supply rails |

| Input Resistance                       |     | 25  |                     | kΩ   |                                                                                                                                                                      |

| Input Capacitance                      |     | 3   |                     | pF   |                                                                                                                                                                      |

| Minimum Pulse Width High               | 620 |     |                     | ps   |                                                                                                                                                                      |

| Minimum Pulse Width Low                | 620 |     |                     | ps   |                                                                                                                                                                      |

| SINGLE-ENDED OPERATION                 |     |     |                     |      |                                                                                                                                                                      |

| Frequency Range (CMOS)                 | 1   |     | $250 \times 10^{6}$ | Hz   |                                                                                                                                                                      |

| Minimum Input Slew Rate                | 40  |     |                     | V/µs | Minimum limit imposed for jitter performance                                                                                                                         |

| Input Voltage High (V <sub>IH</sub> )  |     |     |                     |      |                                                                                                                                                                      |

| 1.2 V to 1.5 V Threshold Setting       | 0.9 |     |                     | V    |                                                                                                                                                                      |

| 1.8 V to 2.5 V Threshold Setting       | 1.2 |     |                     | V    |                                                                                                                                                                      |

| 3.0 V to 3.3 V Threshold Setting       | 1.9 |     |                     | V    |                                                                                                                                                                      |

| Input Voltage Low (V <sub>IL</sub> )   |     |     |                     |      |                                                                                                                                                                      |

| 1.2 V to 1.5 V Threshold Setting       |     |     | 0.27                | V    |                                                                                                                                                                      |

| 1.8 V to 2.5 V Threshold Setting       |     |     | 0.5                 | V    |                                                                                                                                                                      |

| 3.0 V to 3.3 V Threshold Setting       |     |     | 1.0                 | V    |                                                                                                                                                                      |

| Input Resistance                       |     | 45  |                     | kΩ   |                                                                                                                                                                      |

| Input Capacitance                      |     | 3   |                     | рF   |                                                                                                                                                                      |

| Minimum Pulse Width High               | 1.5 |     |                     | ns   |                                                                                                                                                                      |

| Minimum Pulse Width Low                | 1.5 |     |                     | ns   |                                                                                                                                                                      |

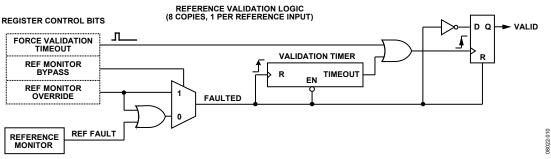

#### **REFERENCE MONITORS**

Table 9.

| Parameter                           | Min                   | Тур | Max    | Unit               | Test Conditions/Comments                                                  |

|-------------------------------------|-----------------------|-----|--------|--------------------|---------------------------------------------------------------------------|

| REFERENCE MONITORS                  |                       |     |        |                    |                                                                           |

| Reference Monitor                   |                       |     |        |                    |                                                                           |

| Loss of Reference Detection<br>Time |                       |     | 1.2    | sec                | Calculated using the nominal phase detector period $(NPDP = R/f_{REF})^1$ |

| Frequency Out-of Range Limits       | $9.54 \times 10^{-7}$ |     | 0.1    | $\Delta f/f_{REF}$ | Programmable (lower bound subject to quality of SYSCLK)                   |

| Validation Timer                    | 0.001                 |     | 65.535 | sec                | Programmable in 1 ms increments                                           |

| Redetect Timer                      | 0.001                 |     | 65.535 | sec                | Programmable in 1 ms increments                                           |

$<sup>^{1}</sup>$  f\_{REF} is the frequency of the active reference; R is the frequency division factor determined by the R-divider.

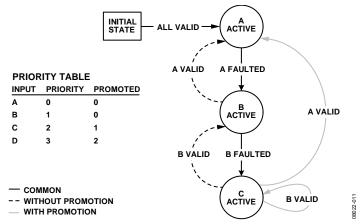

#### REFERENCE SWITCHOVER SPECIFICATIONS

Table 10.

| Parameter                                                      | Min | Тур | Max    | Unit   | Test Conditions/Comments                                                                                                                |

|----------------------------------------------------------------|-----|-----|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCE SWITCHOVER SPECIFICATIONS                            |     |     |        |        |                                                                                                                                         |

| Maximum Output Phase Perturbation (Phase Build-Out Switchover) |     | 40  | 200    | ps     | Assumes a jitter-free reference; satisfies Telcordia GR-1244-CORE requirements                                                          |

| Maximum Time/Time Slope (Hitless Switchover)                   | 315 |     | 65,535 | ns/sec | Minimum/maximum values are programmable upper bounds; a minimum value ensures <10% error; satisfies Telcordia GR-1244-CORE requirements |

| Time Required to Switch to a New Reference                     |     |     |        |        |                                                                                                                                         |

| Hitless Switchover                                             |     | 5   |        | sec    | Calculated using the nominal phase detector period (NPDP = R/f <sub>REF</sub> ) <sup>1</sup>                                            |

| Phase Build-Out Switchover                                     |     | 3   |        | sec    | Calculated using the nominal phase detector period (NPDP = R/f <sub>REF</sub> ) <sup>1</sup>                                            |

$<sup>^{1}</sup>$  f\_{REF} is the frequency of the active reference; R is the frequency division factor determined by the R-divider.

#### **DISTRIBUTION CLOCK OUTPUTS (OUT0 TO OUT3)**

Table 11.

| Parameter                                | Min            | Тур         | Max             | Unit | Test Conditions/Comments                                                                       |

|------------------------------------------|----------------|-------------|-----------------|------|------------------------------------------------------------------------------------------------|

| LVPECL MODE                              |                |             |                 |      | Using internal current setting resistor                                                        |

| Maximum Output Frequency                 |                | 725         |                 | MHz  |                                                                                                |

| Rise/Fall Time (20% to 80%)              |                | 180         | 315             | ps   | $100 \Omega$ termination across output pins                                                    |

| Duty Cycle                               | 45             |             | 55              | %    |                                                                                                |

| Differential Output Voltage Swing        | 630            | 770         | 910             | mV   | Magnitude of voltage across pins; output driver static                                         |

| Common-Mode Output Voltage               | AVDD3<br>- 1.5 | AVDD3 – 1.3 | AVDD3 –<br>1.05 | V    | Output driver static                                                                           |

| LVDS MODE                                |                |             |                 |      | Using internal current setting resistor (nominal 3.12 k $\Omega$ )                             |

| Maximum Output Frequency                 |                | 725         |                 | MHz  |                                                                                                |

| Rise/Fall Time <sup>1</sup> (20% to 80%) |                | 200         | 350             | ps   | $100 \Omega$ termination across the output pair                                                |

| Duty Cycle                               | 40             |             | 60              | %    |                                                                                                |

| Differential Output Voltage Swing        |                |             |                 |      |                                                                                                |

| Balanced, V <sub>OD</sub>                | 247            |             | 454             | mV   | Voltage swing between output pins; output driver static                                        |

| Unbalanced, $\Delta V_{\text{OD}}$       |                |             | 50              | mV   | Absolute difference between voltage swing of normal pin and inverted pin; output driver static |

| Offset Voltage                           |                |             |                 |      | ·                                                                                              |

| Common-Mode, Vos                         | 1.125          |             | 1.375           | V    | Output driver static                                                                           |

| Common-Mode Difference, ΔV <sub>OS</sub> |                |             | 50              | mV   | Voltage difference between pins; output driver static                                          |

| Short-Circuit Output Current             |                | 13          | 24              | mA   | Output driver static                                                                           |

| CMOS MODE                                |                |             |                 |      | Weak drive option not supported for operating the CMOS drivers using a 1.8 V supply            |

| Maximum Output Frequency                 |                |             |                 |      |                                                                                                |

| 3.3 V Supply                             |                |             |                 |      | 10 pF load                                                                                     |

| Strong Drive Strength Setting            |                | 250         |                 | MHz  |                                                                                                |

| Weak Drive Strength Setting              |                | 25          |                 | MHz  |                                                                                                |

| 1.8 V Supply                             |                | 150         |                 | MHz  |                                                                                                |

| Parameter                                        | Min | Тур | Max  | Unit | Test Conditions/Comments                                                                                                                                                              |

|--------------------------------------------------|-----|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rise/Fall Time <sup>1</sup> (20% to 80%)         |     |     |      |      | 10 pF load                                                                                                                                                                            |

| 3.3 V Supply                                     |     |     |      |      |                                                                                                                                                                                       |

| Strong Drive Strength Setting                    |     | 0.5 | 2    | ns   |                                                                                                                                                                                       |

| Weak Drive Strength Setting                      |     | 8   | 14.5 | ns   |                                                                                                                                                                                       |

| 1.8 V Supply                                     |     | 1.5 | 2.5  | ns   |                                                                                                                                                                                       |

| Duty Cycle                                       | 40  |     | 60   | %    | 10 pF load                                                                                                                                                                            |

| Output Voltage High (V <sub>OH</sub> )           |     |     |      |      | Output driver static; strong drive strength setting                                                                                                                                   |

| $AVDD3 = 3.3 \text{ V, } I_{OH} = 10 \text{ mA}$ | 2.6 |     |      | V    |                                                                                                                                                                                       |

| $AVDD3 = 3.3 \text{ V, } I_{OH} = 1 \text{ mA}$  | 2.9 |     |      | V    |                                                                                                                                                                                       |

| $AVDD3 = 1.8 \text{ V, } I_{OH} = 1 \text{ mA}$  | 1.5 |     |      | V    |                                                                                                                                                                                       |

| Output Voltage Low (V <sub>OL</sub> )            |     |     |      |      | Output driver static; strong drive strength setting                                                                                                                                   |

| $AVDD3 = 3.3 \text{ V, } I_{OL} = 10 \text{ mA}$ |     |     | 0.3  | V    |                                                                                                                                                                                       |

| $AVDD3 = 3.3 \text{ V, } I_{OL} = 1 \text{ mA}$  |     |     | 0.1  | V    |                                                                                                                                                                                       |

| $AVDD3 = 1.8 \text{ V}, I_{OL} = 1 \text{ mA}$   |     |     | 0.1  | V    |                                                                                                                                                                                       |

| OUTPUT TIMING SKEW                               |     |     |      |      | 10 pF load                                                                                                                                                                            |

| Between LVPECL Outputs                           |     | 14  | 125  | ps   | Rising edge only; any divide value                                                                                                                                                    |

| Between LVDS Outputs                             |     | 13  | 138  | ps   | Rising edge only; any divide value                                                                                                                                                    |

| Between CMOS 3.3 V Outputs                       |     |     |      |      |                                                                                                                                                                                       |

| Strong Drive Strength Setting                    |     | 23  | 240  | ps   |                                                                                                                                                                                       |

| Weak Drive Strength Setting                      |     | 24  |      | ps   |                                                                                                                                                                                       |

| Between CMOS 1.8 V Outputs                       |     | 40  |      | ps   | Weak drive not supported at 1.8 V                                                                                                                                                     |

| Between LVPECL Outputs and LVDS Outputs          |     | 14  | 140  | ps   |                                                                                                                                                                                       |

| Between LVPECL Outputs and CMOS Outputs          |     | 19  |      | ps   |                                                                                                                                                                                       |

| ZERO-DELAY TIMING SKEW                           |     | ±5  |      | ns   | Output relative to active input reference; output distribution synchronization to active reference feature enabled; assumes manual phase offset compensation of deterministic latency |

<sup>&</sup>lt;sup>1</sup> The listed values are for the slower edge (rise or fall).

## DAC OUTPUT CHARACTERISTICS (DACOUTP/DACOUTN)

Table 12.

| Parameter                                    | Min       | Тур | Max       | Unit | Test Conditions/Comments                                                                                                                                  |

|----------------------------------------------|-----------|-----|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAC OUTPUT CHARACTERISTICS (DACOUTP/DACOUTN) |           |     |           |      |                                                                                                                                                           |

| Frequency Range                              | 62.5      |     | 450       | MHz  |                                                                                                                                                           |

| Output Offset Voltage                        |           |     | 15        | mV   | This is the single-ended voltage at either DAC output pin (no external load) when the internal DAC code implies that no current is delivered to that pin. |

| Voltage Compliance Range                     | VSS - 0.5 | 0.5 | VSS + 0.5 | V    |                                                                                                                                                           |

| Output Resistance                            |           | 50  |           | Ω    | Single-ended, each pin has an internal $50 \Omega$ termination to VSS.                                                                                    |

| Output Capacitance                           |           | 5   |           | рF   |                                                                                                                                                           |

| Full-Scale Output Current                    |           | 20  |           | mA   | Programmable (8 mA to 31 mA; see the DAC Output section).                                                                                                 |

| Gain Error                                   | -12       |     | +12       | % FS |                                                                                                                                                           |

#### TIME DURATION OF DIGITAL FUNCTIONS

Table 13.

| Parameter                                                                                       | Min | Тур  | Max | Unit | Test Conditions/Comments                                                       |

|-------------------------------------------------------------------------------------------------|-----|------|-----|------|--------------------------------------------------------------------------------|

| TIME DURATION OF DIGITAL FUNCTIONS                                                              |     |      |     |      |                                                                                |

| EEPROM-to-Register Download Time                                                                |     | 25   |     | ms   | Using default EEPROM storage sequence (see Register 0x0E10 to Register 0x0E3F) |

| Register-to-EEPROM Upload Time                                                                  |     | 200  |     | ms   | Using default EEPROM storage sequence (see Register 0x0E10 to Register 0x0E3F  |

| Minimum Power-Down Exit Time                                                                    |     | 10.5 |     | μs   | Dependent on loop-filter bandwidth                                             |

| Maximum Time from Assertion of the RESET pin to the M0 to M7 Pins Entering High Impedance State |     | 45   |     | ns   |                                                                                |

#### **DIGITAL PLL**

#### Table 14.

| Parameter                                               | Min   | Тур | Max             | Unit    | Test Conditions/Comments                                            |

|---------------------------------------------------------|-------|-----|-----------------|---------|---------------------------------------------------------------------|

| DIGITAL PLL                                             |       |     |                 |         |                                                                     |

| Phase-Frequency Detector (PFD)<br>Input Frequency Range | 1     |     | 10 <sup>7</sup> | Hz      | Maximum $f_{PFD}^{-1}$ : $f_S/100^2$                                |

| Loop Bandwidth                                          | 0.001 |     | 10 <sup>5</sup> | Hz      | Programmable design parameter; maximum $f_{LOOP} = f_{REF}/(20R)^3$ |

| Phase Margin                                            | 30    |     | 89              | Degrees | Programmable design parameter                                       |

| Reference Input (R) Division Factor                     | 1     |     | 2 <sup>30</sup> |         | 1, 2,, 1,073,741,824                                                |

| Integer Feedback (S) Division Factor                    | 8     |     | 2 <sup>30</sup> |         | 8, 9,, 1,073,741,824                                                |

| Fractional Feedback Divide Ratio                        | 0     |     | 0.999           |         | Maximum value: 1022/1023                                            |

$<sup>^1\,</sup>f_{PFD}$  is the frequency at the input to the phase-frequency detector.  $^2\,f_S$  is the sample rate of the output DAC.

#### **DIGITAL PLL LOCK DETECTION**

#### Table 15.

| Parameter                   | Min   | Тур | Max    | Unit | Test Conditions/Comments                |

|-----------------------------|-------|-----|--------|------|-----------------------------------------|

| PHASE LOCK DETECTOR         |       |     |        |      |                                         |

| Threshold Programming Range | 0.001 |     | 65.5   | ns   |                                         |

| Threshold Resolution        |       | 1   |        | ps   |                                         |

| FREQUENCY LOCK DETECTOR     |       |     |        |      |                                         |

| Threshold Programming Range | 0.001 |     | 16,700 | ns   | Reference-to-feedback period difference |

| Threshold Resolution        |       | 1   |        | ps   |                                         |

#### **HOLDOVER SPECIFICATIONS**

#### Table 16.

| Parameter               | Min | Тур   | Max | Unit | Test Conditions/Comments                                                                                          |

|-------------------------|-----|-------|-----|------|-------------------------------------------------------------------------------------------------------------------|

| HOLDOVER SPECIFICATIONS |     |       |     |      |                                                                                                                   |

| Frequency Accuracy      |     | <0.01 |     | ppb  | Excludes frequency drift of SYSCLK source; excludes frequency drift of input reference prior to entering holdover |

$<sup>^3</sup>$  f<sub>REF</sub> is the frequency of the active reference; R is the frequency division factor determined by the R-divider.

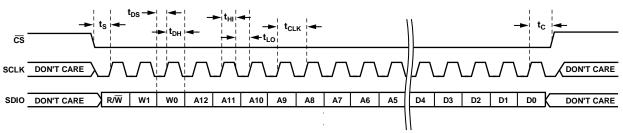

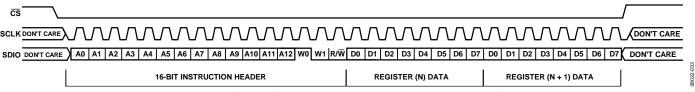

#### SERIAL PORT SPECIFICATIONS—SPI MODE

Table 17.

| Parameter                                             | Min | Тур | Max | Unit | Test Conditions/Comments          |

|-------------------------------------------------------|-----|-----|-----|------|-----------------------------------|

| CS                                                    |     |     |     |      | Internal 30 kΩ pull-up resistor   |

| Input Logic 1 Voltage                                 |     | 2.0 |     | V    |                                   |

| Input Logic 0 Voltage                                 |     | 0.8 |     | V    |                                   |

| Input Logic 1 Current                                 |     | 30  |     | μΑ   |                                   |

| Input Logic 0 Current                                 |     | 110 |     | μΑ   |                                   |

| Input Capacitance                                     |     | 2   |     | рF   |                                   |

| SCLK                                                  |     |     |     |      | Internal 30 kΩ pull-down resistor |

| Input Logic 1 Voltage                                 |     | 2.0 |     | V    |                                   |

| Input Logic 0 Voltage                                 |     | 8.0 |     | V    |                                   |

| Input Logic 1 Current                                 |     | 1   |     | μΑ   |                                   |

| Input Logic 0 Current                                 |     | 1   |     | μΑ   |                                   |

| Input Capacitance                                     |     | 2   |     | pF   |                                   |

| SDIO                                                  |     |     |     |      |                                   |

| As an Input                                           |     |     |     |      |                                   |

| Input Logic 1 Voltage                                 |     | 2.0 |     | V    |                                   |

| Input Logic 0 Voltage                                 |     | 0.8 |     | V    |                                   |

| Input Logic 1 Current                                 |     | 1   |     | μΑ   |                                   |

| Input Logic 0 Current                                 |     | 1   |     | μΑ   |                                   |

| Input Capacitance                                     |     | 2   |     | pF   |                                   |

| As an Output                                          |     |     |     |      |                                   |

| Output Logic 1 Voltage                                | 2.7 |     |     | V    | 1 mA load current                 |

| Output Logic 0 Voltage                                |     |     | 0.4 | V    | 1 mA load current                 |

| SDO                                                   |     |     |     |      |                                   |

| Output Logic 1 Voltage                                | 2.7 |     |     | V    | 1 mA load current                 |

| Output Logic 0 Voltage                                |     |     | 0.4 | V    | 1 mA load current                 |

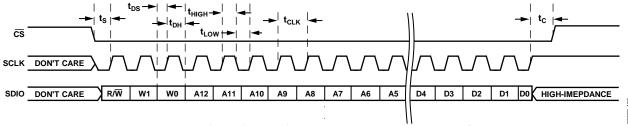

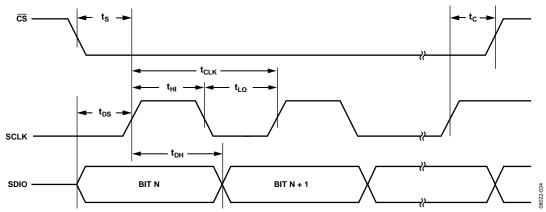

| TIMING                                                |     |     |     |      |                                   |

| SCLK                                                  |     |     |     |      |                                   |

| Clock Rate, 1/t <sub>CLK</sub>                        |     |     | 40  | MHz  |                                   |

| Pulse Width High, t <sub>HI</sub>                     | 10  |     |     | ns   |                                   |

| Pulse Width Low, t <sub>LO</sub>                      | 12  |     |     | ns   |                                   |

| SDIO to SCLK Setup, t <sub>DS</sub>                   | 3   |     |     | ns   |                                   |

| SCLK to SDIO Hold, t <sub>DH</sub>                    | 0   |     |     | ns   |                                   |

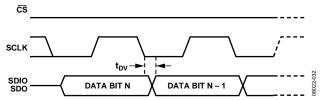

| $\underline{SCLK}$ to Valid SDIO and SDO, $t_{DV}$    |     |     | 15  | ns   |                                   |

| $\overline{CS}$ to SCLK Setup (t <sub>s</sub> )       | 10  |     |     | ns   |                                   |

| $\overline{\text{CS}}$ to SCLK Hold (t <sub>C</sub> ) | 0   |     |     | ns   |                                   |

| CS Minimum Pulse Width High                           | 6   |     |     | ns   |                                   |

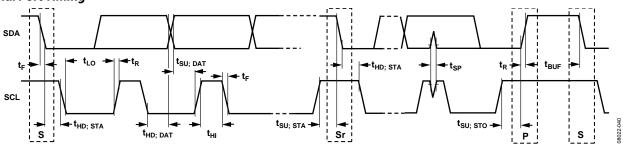

#### SERIAL PORT SPECIFICATIONS—I<sup>2</sup>C MODE

Table 18.

| Parameter                                                                             | Min              | Тур | Max                | Unit | Test Conditions/Comments           |

|---------------------------------------------------------------------------------------|------------------|-----|--------------------|------|------------------------------------|

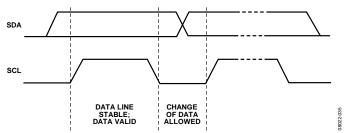

| SDA, SCL (AS INPUT)                                                                   |                  |     |                    |      | No internal pull-up/down resistor. |

| Input Logic 1 Voltage                                                                 | 0.7 × DVDD3      |     |                    | V    |                                    |

| Input Logic 0 Voltage                                                                 |                  |     | $0.3 \times DVDD3$ | V    |                                    |

| Input Current                                                                         | -10              |     | +10                | μΑ   | For $V_{IN} = 10\%$ to 90% DVDD3.  |

| Hysteresis of Schmitt Trigger Inputs                                                  | 0.015 × DVDD3    |     |                    |      |                                    |

| Pulse Width of Spikes That Must Be<br>Suppressed by the Input Filter, t <sub>SP</sub> |                  |     | 50                 | ns   |                                    |

| SDA (AS OUTPUT)                                                                       |                  |     |                    |      |                                    |

| Output Logic 0 Voltage                                                                |                  |     | 0.4                | V    | $I_0 = 3 \text{ mA}.$              |

| Output Fall Time from $V_{IHmin}$ to $V_{ILmax}$                                      | $20 + 0.1 C_b^1$ |     | 250                | ns   | 10 pF ≤ $C_b$ ≤ 400 pF.            |

Rev. G | Page 11 of 111

| Parameter                                                      | Min                                  | Тур Мах | Unit | Test Conditions/Comments                               |

|----------------------------------------------------------------|--------------------------------------|---------|------|--------------------------------------------------------|

| TIMING                                                         |                                      |         |      |                                                        |

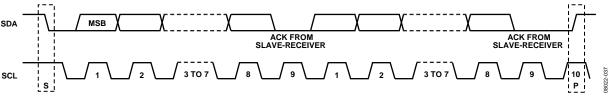

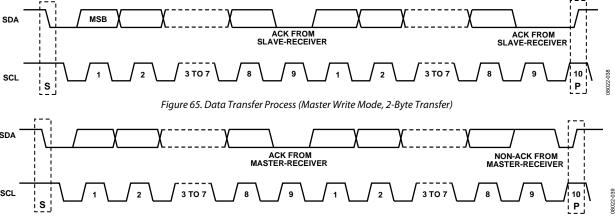

| SCL Clock Rate                                                 |                                      | 400     | kHz  |                                                        |

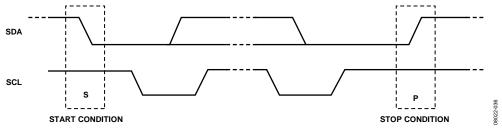

| Bus-Free Time Between a Stop and Start Condition, tBUF         | 1.3                                  |         | μs   |                                                        |

| Repeated Start Condition Setup Time, tsu; STA                  | 0.6                                  |         | μs   |                                                        |

| Repeated Hold Time Start Condition, thD;STA                    | 0.6                                  |         | μs   | After this period, the first clock pulse is generated. |

| Stop Condition Setup Time, t <sub>SU; STO</sub>                | 0.6                                  |         | μs   |                                                        |

| Low Period of the SCL Clock, t <sub>LO</sub>                   | 1.3                                  |         | μs   |                                                        |

| High Period of the SCL Clock, t <sub>H</sub>                   | 0.6                                  |         | μs   |                                                        |

| SCL/SDA Rise Time, t <sub>R</sub>                              | $20 + 0.1  C_b^{-1}$                 | 300     | ns   |                                                        |

| SCL/SDA Fall Time, t <sub>F</sub>                              | 20 + 0.1 C <sub>b</sub> <sup>1</sup> | 300     | ns   |                                                        |

| Data Setup Time, t <sub>SU; DAT</sub>                          | 100                                  |         | ns   |                                                        |

| Data Hold Time, t <sub>HD; DAT</sub>                           | 100                                  |         | ns   |                                                        |

| Capacitive Load for Each Bus Line, C <sub>b</sub> <sup>1</sup> |                                      | 400     | pF   |                                                        |

$<sup>^{1}\,\</sup>mathsf{C}_{b}$  is the capacitance (pF) of a single bus line.

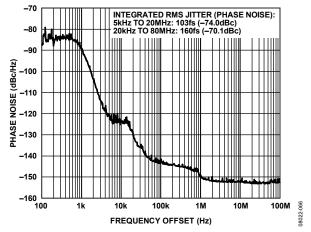

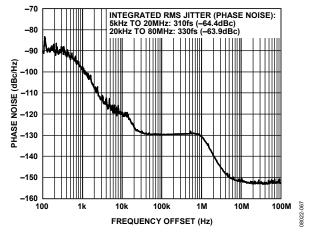

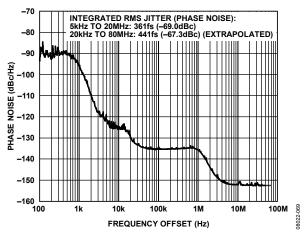

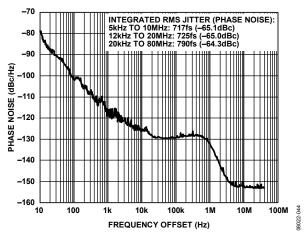

### **JITTER GENERATION**

Table 19.

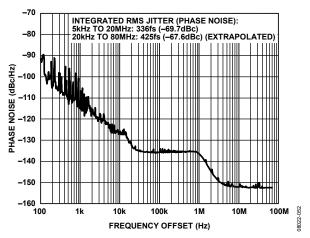

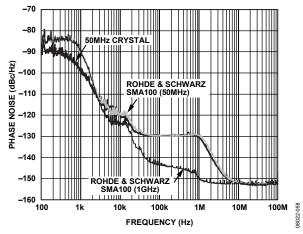

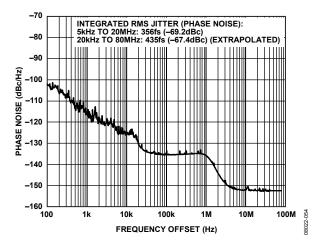

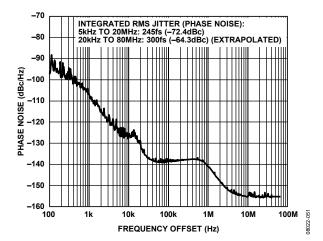

| Parameter                                                                                      | Min | Тур  | Max | Unit   | Test Conditions/Comments                                                                                                                                                                                             |

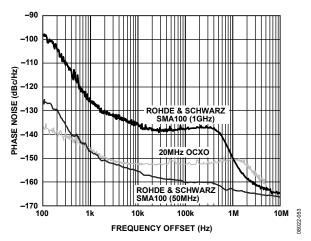

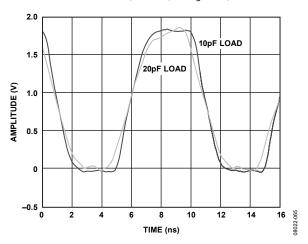

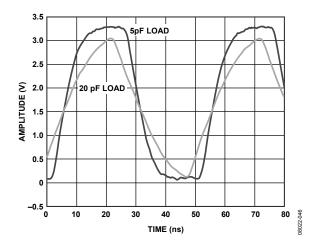

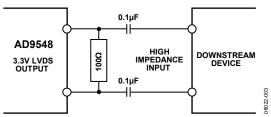

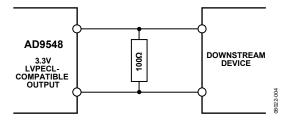

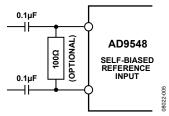

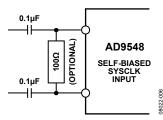

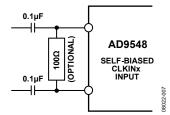

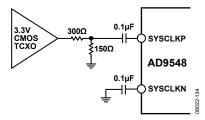

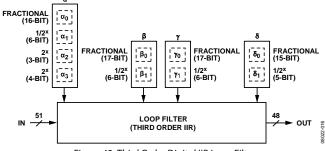

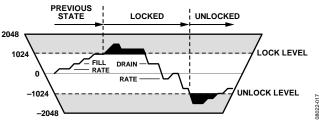

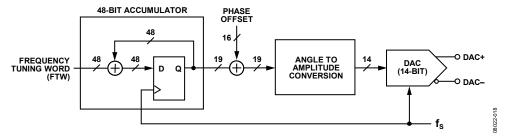

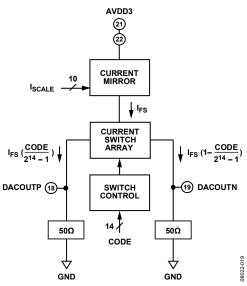

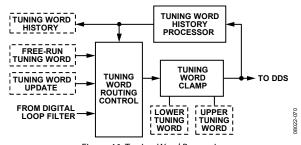

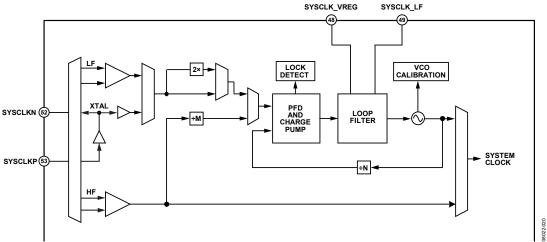

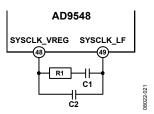

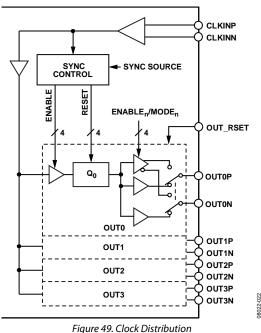

|------------------------------------------------------------------------------------------------|-----|------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|