# ATAES132A

## 32K AES Serial EEPROM Specification

## SUMMARY DATASHEET

## **Features**

## **CryptoAuthentication**

Ensures Things and Code are Real, Untampered, and Confidential

#### Secure Download and Boot Authentication and Protect Code In-transit

#### Ecosystem Control

Ensure Only OEM/Licensed Nodes and Accessories Work

#### Anti-cloning

Prevent Building with Identical BOM or Stolen Code

#### Message Security

Authentication, Message Integrity, and Confidentiality of Network Nodes (IoT)

- Crypto Element Device with Secure Hardware-based Key Storage

- 32Kb Standard Serial EEPROM Memory

- Compatible with the Atmel<sup>®</sup> AT24C32D and the Atmel AT25320B

- 16 User Zones of 2Kb Each

- High-security Features

- AES Algorithm with 128-bit Keys

- AES-CCM for Authentication

- Message Authentication Code (MAC) Capability

- Secure Storage for up to Sixteen 128-bit Keys

- Encrypted User Memory Read and Write

- Internal High-quality FIPS Random Number Generator (RNG)

- 16 High-Endurance Monotonic EEPROM Counters

- Flexible User Configured Security

- User Zone Access Rights Independently Configured

- Authentication Prior to Zone Access

- Read/Write, Encrypted, or Read-only User Zone Options

- High-speed Serial Interface Options

- 10MHz SPI (Mode 0 and 3)

- 1MHz Standard I<sup>2</sup>C Interface

- 2.5V to 5.5V Supply Voltage Range

- <250nA Sleep Current</p>

- 8-pad UDFN and 8-lead SOIC Package Options

- Temperature Range: -40°C to +85°C

### **Benefits**

- Easily Add Security by Replacing Existing Serial EEPROM

- Authenticate Consumables, Components, and Network Access

- Protect Sensitive Firmware

- Securely Store Sensitive Data and Enable Paid-for Features

- Prevent Contract Manufacturers from Overbuilding

- Manage Warranty Claims

- Securely Store Identity Data (i.e. Fingerprints and Pictures)

This is a summary document. The complete document is available on the Atmel website at www.atmel.com.

## **Description**

The Atmel ATAES132A is a high-security, Serial Electrically-Erasable and Programmable Read-Only Memory (EEPROM) providing both authentication and confidential nonvolatile data storage capabilities. Access restrictions for the 16 user zones are independently configured, and any key can be used with any zone. In addition, keys can be used for standalone authentication. This flexibility permits the ATAES132A to be used in a wide range of applications.

The AES-128 cryptographic engine operates in AES-CCM mode to provide authentication, stored data encryption/decryption, and Message Authentication Codes. Data encryption/decryption can be performed for internally stored data or for small external data packets, depending upon the configuration. Data encrypted by one ATAES132A device can be decrypted by another, and vice versa.

The ATAES132A pinout is compatible with standard SPI and I<sup>2</sup>C Serial EEPROMs to allow placement on existing PC boards. The SPI and I<sup>2</sup>C instruction sets are identical to the Atmel Serial EEPROMs. The extended security functions are accessed by sending command packets to the ATAES132A using standard write instructions, and reading responses using standard read instructions. The ATAES132A secure Serial EEPROM architecture allows it to be inserted into existing applications.

The ATAES132A device incorporates multiple physical security mechanisms to prevent the release of the internally stored secrets. Secure personalization features are provided to facilitate third-party product manufacturing.

### **Pin Descriptions and Configurations**

#### Table 1.Pin Descriptions

| Name            | Description               |

|-----------------|---------------------------|

| CS              | SPI Chip Select Bar Input |

| SO              | Serial Data Out           |

| NC              | No Connect                |

| V <sub>SS</sub> | Ground                    |

| SI/SDA          | Serial Data In            |

| SCK             | Serial Clock Input        |

| NC              | No Connect                |

| Vcc             | Supply Voltage            |

#### Table 2. Pin Configurations

| 8-lead SOIC<br>(Top View) |    |   |                 |   | UDFN<br>View) |                 |

|---------------------------|----|---|-----------------|---|---------------|-----------------|

| CS                        | 1) | 8 | CS              | 1 | 8 []]         | V <sub>CC</sub> |

| SO                        | 2  |   | SO              | 2 | 7 []]         | NC              |

| NC                        | 3  |   | NC              | 3 | 6 []]         | SCK             |

| Vss                       | 4  |   | V <sub>SS</sub> | 4 | 5 []]         | SI/SDA          |

Note: Drawings are not to scale.

2

## 1. Introduction

The ATAES132A is the first device in a family of high-security Serial EEPROMs using the Advanced Encryption Standard (AES) cryptographic algorithm. The ATAES132A provides 32Kb of EEPROM user data memory, sixteen 128-bit Key Registers, sixteen high-endurance monotonic EEPROM Counters, factory unique Die Identification Numbers, and a Configuration Memory. The Configuration Memory registers control access to the User Memory, as well as the restrictions on Key and Counter functionality.

The User Memory can be accessed directly with standard SPI or I<sup>2</sup>C commands if a user zone is configured for open or read-only access. If the user zone security is activated, then the extended ATAES132A command set is used to access the contents of a user zone. The extended ATAES132A commands are executed by writing the command packet to the virtual memory using standard SPI or I<sup>2</sup>C Write commands. The response packet is retrieved by reading it from the virtual memory using standard SPI or I<sup>2</sup>C Read commands.

The ATAES132A packages are compatible with standard SPI and I<sup>2</sup>C EEPROM footprints. This allows the ATAES132A to be inserted into many existing Serial EEPROM applications.

## 2. Security Features

All ATAES132A security features are optional. Each feature is enabled or disabled by programming configuration bits in the EEPROM Configuration Memory. Each user zone, Key, and Counter is separately and independently configured.

## 2.1 Architecture

ATAES132A contains all circuitry for performing authentication, encryption, and decryption using keys stored securely in the internal EEPROM. Since the secrets are stored securely in the ATAES132A, they do not have to be exchanged prior to executing cryptographic operations.

ATAES132A has fixed cryptographic functionality; it is not a microcontroller and cannot accept customer firmware. ATAES132A contains a hardware AES cryptographic engine and has a fixed command set. Although the functionality is fixed, it is also flexible because each feature is enabled or disabled by the customer by programming registers in the EEPROM Configuration Memory. After personalization is complete, fuses lock the configuration so it cannot be changed.

## 2.1.1 AES

The ATAES132A cryptographic functions are implemented with a hardware cryptographic engine using AES in CCM mode with a 128-bit key. AES-CCM mode provides both confidentiality and integrity checking with a single key. The integrity MAC includes both the encrypted data and additional authenticate-only data bytes, as described in each command definition. Each MAC is unique due to inclusion of a Nonce and an incrementing MacCount Register in the MAC calculation.

### 2.1.2 Hardware Security Features

The ATAES132A device contains physical security features to prevent an attacker from determining the internal secrets. ATAES132A includes tamper detectors for voltage, temperature, frequency, and light, as well as an active metal shield over the circuitry, internal memory encryption, and other various features. The ATAES132A physical design and cryptographic protocol are designed to prevent or significantly complicate most algorithmic, timing, and side-channel attacks.

## 2.2 Authentication

The authentication commands utilize AES-CCM to generate or validate a MAC value computed using an internally stored key. The command set supports both one-way and mutual authentication. One ATAES132A device can generate packets for authentication of a second ATAES132A device containing the same key. The internal authentication status register remembers only the most recent authentication attempt. A user zone can be configured to require prior authentication of a designated key before access to the user zone is permitted.

#### 2.2.1 Key Authentication

Individual keys can be configured to require a successful authentication prior to use. This requirement can be used to prevent some kinds of exhaustive attacks on the keys. The authentication requirement can be chained to require authentication of several keys prior to allowing a particular operation. The internal Authentication Status Registers remember only the most recent authentication attempt.

## 3. Electrical Characteristics

## 3.1 Absolute Maximum Ratings\*

Notice\*: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and the functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 3.2 Reliability

The ATAES132A is fabricated with the Atmel high reliability CMOS EEPROM manufacturing technology. The reliability ratings in Table 3-1 apply to each byte of the EEPROM memory.

| Table 3-1. EEPROM Reliability <sup>(1)</sup> | EEPROM Reliability <sup>(1)</sup> |

|----------------------------------------------|-----------------------------------|

|----------------------------------------------|-----------------------------------|

| Parameter                   | Min     | Typical   | Мах | Units        |

|-----------------------------|---------|-----------|-----|--------------|

| Write Endurance (each byte) | 100,000 |           |     | Write Cycles |

| Data Retention (at 55°C)    | 10      |           |     | Years        |

| Data Retention (at 35°C)    | 30      | 50        |     | Years        |

| Read Endurance              |         | Unlimited |     | Read Cycles  |

Note: 1. These specifications apply to every byte of the User Memory, Configuration Memory, and Key Memory. The Write Endurance specification also applies to the RNG EEPROM Seed Register.

## 3.3 DC Characteristics

### 3.3.1 Supply Characteristics

#### Table 3-2. Supply Voltage and Current Characteristics

Applicable over recommended operating range from  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C,  $V_{CC} = +2.5$ V to +5.5V (unless otherwise noted).<sup>(1)</sup>

| Symbol           | Parameter       | Test Conditions                                                                                                 | Min  | Тур  | Max  | Units |

|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Vcc (1)          | Supply Voltage  |                                                                                                                 | 2.50 |      | 5.50 | V     |

| I <sub>CC1</sub> | Supply Current  | $V_{CC} = 3.3V$ at $f_{max}^{(4)}$<br>SO = Open <sup>(3)</sup> , Read, Write, or AES operation.                 |      |      | 6    | mA    |

| Icc2             | Supply Current  | $V_{CC} = 5.5V$ at $f_{max}^{(4)}$<br>SO = Open <sup>(3)</sup> , Read, Write, or AES operation.                 |      |      | 10   | mA    |

| I <sub>CC3</sub> | Idle Current    | $V_{CC} = 3.3V \text{ or } 5.5V \text{ at } f_{max}^{(4)}$<br>SO = Open <sup>(3)</sup> , Waiting for a command. |      | 600  | 800  | μA    |

| ISL1             | Sleep Current   | $V_{CC} = 3.3V; \overline{CS} = V_{CC}^{(3)}$ , Sleep State                                                     |      | 0.10 | 0.25 | μA    |

| I <sub>SL2</sub> | Sleep Current   | $V_{CC} = 5.5V; \overline{CS} = V_{CC}^{(3)}$ , Sleep State                                                     |      | 0.25 | 0.50 | μA    |

| I <sub>SB1</sub> | Standby Current | $V_{CC} = 3.3V; \overline{CS} = V_{CC}^{(3)}$ , Standby State                                                   |      | 15   | 30   | μA    |

| I <sub>SB2</sub> | Standby Current | $V_{CC} = 5.5V; \overline{CS} = V_{CC}^{(3)}$ , Standby State                                                   |      | 20   | 40   | μA    |

Notes: 1. Typical values are at 25°C, and are for reference only. Typical values are not tested or guaranteed.

2. On power-up, V<sub>CC</sub> must rise continuously from V<sub>SS</sub> to the operating voltage, with a rise time no faster than 1V/µs.

3. All input pins must be held at either Vss or Vcc during this measurement. In SPI interface mode, the  $\overline{\text{CS}}$  pin must be at V<sub>cc</sub>. In I<sup>2</sup>C interface mode, the  $\overline{\text{CS}}$  pin may be in either state.

4. Measurement is performed at the maximum serial clock frequency. In the I<sup>2</sup>C interface mode, f<sub>max</sub> is 1MHz. In the SPI interface mode, f<sub>max</sub> is 10MHz.

5. The ATAES132A does not support hot swapping or hot plugging. Connecting or disconnecting this device to a system while power is energized can cause permanent damage to the ATAES132A.

#### 3.3.2 I/O Characteristics

#### Table 3-3.DC Characteristics

| Symbol                          | Parameter                                                                  | Test conditions                          | Min                   | Max                   | Units |

|---------------------------------|----------------------------------------------------------------------------|------------------------------------------|-----------------------|-----------------------|-------|

| ILI                             | Input Current                                                              | $V_{IN} = 0V \text{ or } V_{CC}$         | -3.0                  | 3.0                   | μA    |

| Ilo                             | Output Leakage                                                             | V <sub>OUT</sub> = 0V or V <sub>CC</sub> | -3.0                  | 3.0                   | μΑ    |

| VIL <sup>(1)</sup>              | Input Low-Voltage                                                          |                                          | -0.5                  | V <sub>CC</sub> x 0.3 | V     |

| V <sub>IH</sub> <sup>(1)</sup>  | Input High-Voltage                                                         |                                          | V <sub>CC</sub> x 0.7 | V <sub>CC</sub> + 0.5 | V     |

| V <sub>OL1</sub> <sup>(2)</sup> | Output Low-Voltage,<br>Except SI/SDA in I <sup>2</sup> C Mode              | I <sub>OL</sub> = 3.0mA                  | 0                     | 0.4                   | V     |

| V <sub>OH1</sub> <sup>(2)</sup> | Output High-voltage,<br>Except SI/SDA in I <sup>2</sup> C Mode             | I <sub>OH</sub> = -3.0mA                 | V <sub>CC</sub> – 0.8 | Vcc                   | V     |

| V <sub>OL2</sub>                | Output Low-voltage,<br>SI/SDA Pin in the I <sup>2</sup> C Mode <i>Only</i> | I <sub>OL</sub> = 3.0mA                  | 0                     | 0.4                   | V     |

Applicable over recommended operating range from  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C,  $V_{CC} = +2.5$ V to +5.5V (unless otherwise noted).

Notes: 1.  $V_{IL}$  min and  $V_{IH}$  max are for reference only, and are not tested.

2. In the I<sup>2</sup>C interface mode, if Auth signaling is enabled, the SO pin functions as the AuthO output. When AuthO is high, the V<sub>OH1</sub> specification applies. When AuthO is not high, the pin is in the high-impedance state; the V<sub>OL1</sub> specification is not applicable.

## 3.4 AC Characteristics

#### Table 3-4. AC Characteristics

| Symbol           | Parameter                                 | Min  | Max  | Units |

|------------------|-------------------------------------------|------|------|-------|

| t <sub>WC1</sub> | User Zone Write Cycle Time <sup>(1)</sup> | 6.0  | 9.0  | ms    |

| twc2             | Key Zone Write Cycle Time <sup>(1)</sup>  | 12.0 | 16.0 | ms    |

|                  | Command Response Time                     |      |      |       |

Applicable over recommended operating range from  $T_A = -40^{\circ}$ C to + 85°C,  $V_{CC} = +2.5$ V to +5.5V.

Note: 1. The write cycle time includes the EEPROM Erase, Write, and Automatic Data Write verification operations.

#### 3.4.1 Power-Up, Sleep, Standby, and Wake-Up Timing

#### Table 3-5. Power-Up, Sleep, and Wake-Up Timing Characteristics<sup>(1)</sup>

Applicable over recommended operating range from  $T_A = -40^{\circ}C$  to  $+ 85^{\circ}C$ ,  $V_{CC} = +2.5V$  to +5.5V.

| Symbol                 | Parameter                              | Min | Тур  | Max  | Units |

|------------------------|----------------------------------------|-----|------|------|-------|

| tpu.status             | Power-Up Time, Status                  |     | 500  | 600  | μs    |

| tpu.rdy                | Power-Up Ready Time                    |     | 1200 | 1500 | μs    |

| tsв                    | Sleep Time, Entering the Standby State |     | 65   | 100  | μs    |

| t <sub>SL</sub>        | Sleep Time, Entering the Sleep State   |     | 55   | 90   | μs    |

| twupSB.STATUS          | Wake-Up Status Time, Standby State     |     | 50   | 100  | μs    |

| twupSB.RDY             | Wake-Up Ready Time, Standby State      |     | 200  | 240  | μs    |

| twupSL.STATUS          | Wake-Up Status, Sleep State            |     | 500  | 600  | μs    |

| t <sub>WupSL.RDY</sub> | Wake-Up Ready Time, Sleep State        |     | 1200 | 1500 | μs    |

Note: 1. All values are based on characterization and are not tested. Typical values are at 25°C and are for reference only.

## 3.4.2 I<sup>2</sup>C Interface Timing

#### Table 3-6. AC Characteristics of I<sup>2</sup>C Interface

| Symbol              | Parameter                                                                 | Min | Мах | Units   |

|---------------------|---------------------------------------------------------------------------|-----|-----|---------|

| f <sub>SCK</sub>    | SCK Clock Frequency                                                       |     | 1   | MHz     |

|                     | SCK Clock Duty Cycle                                                      | 30  | 70  | percent |

| tнigн               | SCK High Time                                                             | 400 |     | ns      |

| tLOW                | SCK Low Time                                                              | 400 |     | ns      |

| tsu.sta             | Start Setup Time                                                          | 250 |     | ns      |

| t <sub>HD.STA</sub> | Start Hold Time                                                           | 250 |     | ns      |

| tsu.sto             | Stop Setup Time                                                           | 250 |     | ns      |

| tsu.dat             | Data in Setup Time                                                        | 100 |     | ns      |

| t <sub>HD.DAT</sub> | Data in Hold Time                                                         | 0   |     | ns      |

| t <sub>R</sub>      | Input Rise Time <sup>(1)</sup>                                            |     | 300 | ns      |

| t⊨                  | Input Fall Time <sup>(1)</sup>                                            |     | 100 | ns      |

| t <sub>AA</sub>     | Clock Low to Data Out Valid                                               | 50  | 550 | ns      |

| t <sub>DH</sub>     | Data Out Hold Time                                                        | 50  |     | ns      |

| t <sub>BUF</sub>    | Time bus must be free before a new transmission can start. <sup>(1)</sup> | 500 |     | ns      |

Applicable over recommended operating range from  $T_A = -40^{\circ}C$  to  $+ 85^{\circ}C$ ,  $V_{CC} = +2.5V$  to +5.5V, CL = 1 TTL Gate and 100pF (unless otherwise noted).

Notes: 1. Values are based on characterization, and are not tested.

- 2. AC measurement conditions:

- RL (connects between SDA and Vcc):  $2.0k\Omega$  (for Vcc +2.5V to +5.0V)

- Input pulse voltages: 0.3Vcc to 0.7Vcc

- Input rise and fall times: ≤ 50ns

- Input and output timing reference voltage: 0.5Vcc

#### **SPI Interface Timing** 3.4.3

#### Table 3-7. **AC Characteristics of SPI Interface**

| CL = 1 TTL Gate and 30pF (unless otherwise noted). |                     |     |     |  |  |  |

|----------------------------------------------------|---------------------|-----|-----|--|--|--|

| Symbol                                             | Parameter           | Min | Мах |  |  |  |

| foor                                               | SCK Clock Frequency | 0   | 10  |  |  |  |

| Applicable over recommended operating range from $T_A = -40^{\circ}C$ to + 85°C, $V_{CC} = +2.5V$ to +5.5V, |

|-------------------------------------------------------------------------------------------------------------|

| CL = 1 TTL Gate and 30pF (unless otherwise noted).                                                          |

| fscк            | SCK Clock Frequency            | 0  | 10 | MHz     |

|-----------------|--------------------------------|----|----|---------|

|                 | SCK Clock Duty Cycle           | 30 | 70 | percent |

| twн             | SCK High Time                  | 40 |    | ns      |

| tw∟             | SCK Low Time 40                |    |    |         |

| tcs             | CS High Time                   | 50 |    | ns      |

| tcss            | CS Setup Time                  | 50 |    | ns      |

| tсsн            | CS Hold Time                   | 50 |    | ns      |

| t <sub>SU</sub> | Data In Setup Time             | 10 |    | ns      |

| t <sub>H</sub>  | Data In Hold Time              | 10 |    | ns      |

| t <sub>RI</sub> | Input Rise Time <sup>(1)</sup> |    | 2  | μs      |

| tFI             | Input Fall Time <sup>(1)</sup> |    | 2  | μs      |

| tv              | Output Valid                   | 0  | 40 | ns      |

| tно             | Output Hold Time               | 0  |    | ns      |

| tDIS            | Output Disable Time            |    | 50 | ns      |

Note: 1. Values are based on characterization, and are not tested. Units

# 4. Ordering Information

To increase security, ATAES132A packages are not marked with the ordering code. The ATAES132A standard packages are marked with a trace code which is unique for each manufacturing lot. Contact Atmel for additional information.

## A.1 Ordering Codes

| Atmel Ordering Code | Interface<br>Configuration | Conditioning                 | Package | Lead Finish            | Temperature<br>Range           |

|---------------------|----------------------------|------------------------------|---------|------------------------|--------------------------------|

| ATAES132A-SHEQ      | SPI                        | D:-///-(1)                   |         |                        |                                |

| ATAES132A-SHER      | l <sup>2</sup> C           | Bulk <sup>(1)</sup>          | 004     | NiPdAu                 |                                |

| ATAES132A-SHEQ-T    | SPI                        |                              | 8S1     | Lead-free/Halogen-free | Industrial                     |

| ATAES132A-SHER-T    | l <sup>2</sup> C           | Tana and Deal <sup>(2)</sup> |         | (Exceeds RoHS          | Temperature<br>(-40°C to 85°C) |

| ATAES132A-MAHEQ-T   | SPI                        | Tape and Reel <sup>(2)</sup> | 8MA2    | Requirments)           |                                |

| ATAES132A-MAHER-T   | l <sup>2</sup> C           |                              |         |                        |                                |

Notes: 1. Blank = Bulk

- SOIC = 100 per tube.

- 2. -T = Tape and Reel

- SOIC = 4,000 per reel.

- UDFN = 15,000 per reel.

| Package Type |                                                                                                          |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|--|--|

| 8S1          | 8-lead, 0.150" wide body, Plastic Gull Wing Small Outline, Green (JEDEC SOIC)                            |  |  |

| 8MA2         | 8-pad, 2.0mm x 3.0mm x 0.6mm body, Thermally Enhanced Plastic Ultra Thin Dual Flat No Lead, Green (UDFN) |  |  |

## A.2 Mechanical Information

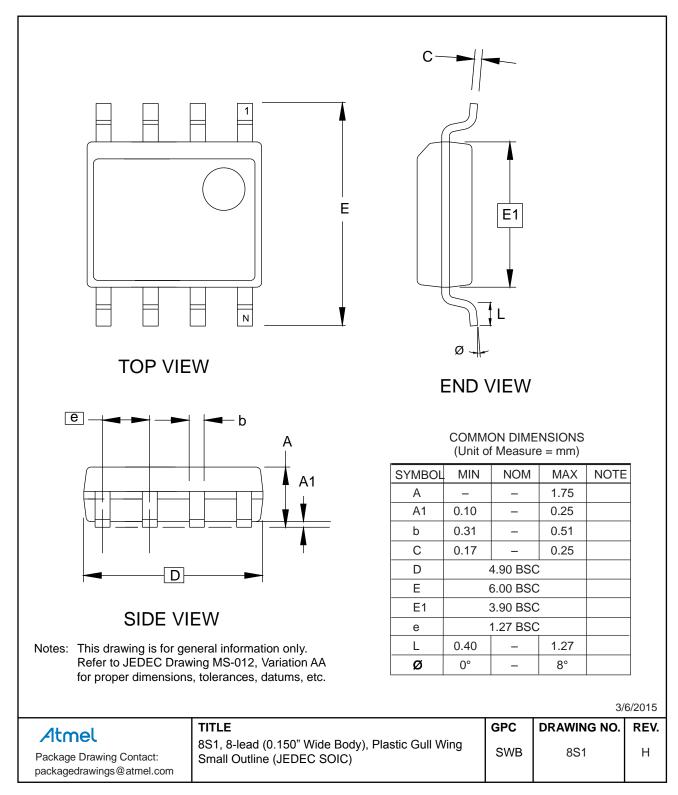

### A.2.1 8S1 — 8-lead JEDEC SOIC

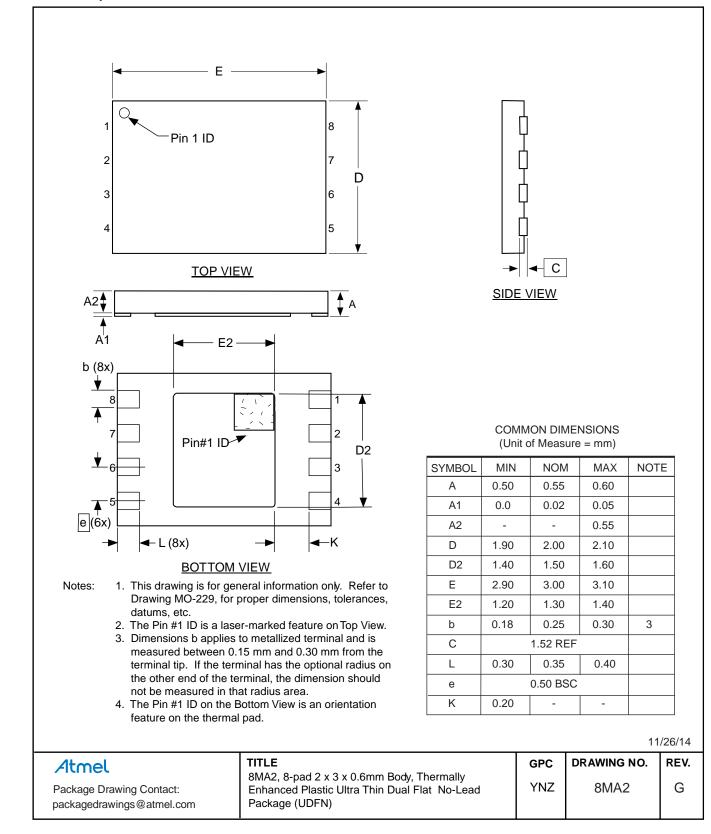

A.2.2 8MA2 — 8-pad UDFN

Atmel

# 5. Revision History

| Doc. Rev. | Date    | Comments                          |

|-----------|---------|-----------------------------------|

| 8914AS    | 03/2015 | Initial summary document release. |

# Atmel Enabling Unlimited Possibilities

**Atmel Corporation**

1600 Technology Drive, San Jose, CA 95110 USA T:

**T:** (+1)(408) 441.0311 **F:** (+1)(408) 436.4200

© 2015 Atmel Corporation. / Rev.:Atmel-8914AS-CryptoAuth-ATAES132A-Datasheet-Summary\_032015.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, CryptoAuthentication<sup>™</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL & LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as military-grade.