# GS8673ET18/36BK-725S/625S/550S

260 Pin BGA Commercial Temp Industrial Temp

# 72Mb SigmaDDR-IIIe™ Burst of 2 ECCRAM™

Up to 725 MHz 1.35V V<sub>DD</sub> 1.2V or 1.35V or 1.5V V<sub>DDO</sub>

# Features

- For use with GSI SRAM Port IP

- 2Mb x 36 and 4Mb x 18 organizations available

- 725 MHz maximum operating frequency

- 725 MT/s peak transaction rate (in millions per second)

- 52 Gb/s peak data bandwidth (in x36 devices)

- Common I/O DDR Data Bus

- Non-multiplexed SDR Address Bus

- One operation Read or Write per clock cycle

- · Burst of 2 Read and Write operations

- 3 cycle Read Latency

- On-chip ECC with virtually zero SER

- 1.35V core voltage

- 1.2V or 1.35V or 1.5V I/O interface (HSTL or SSTL)

- Configurable ODT (on-die termination)

- ZQ pin for programmable driver impedance

- ZT pin for programmable ODT impedance

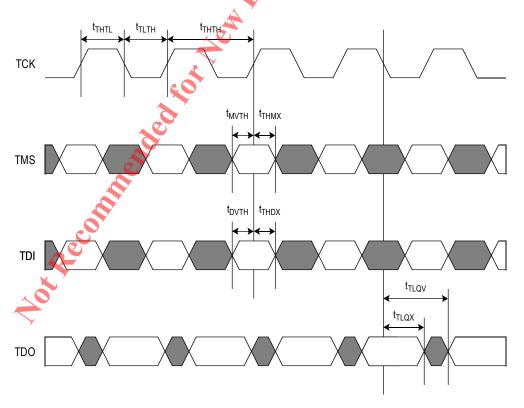

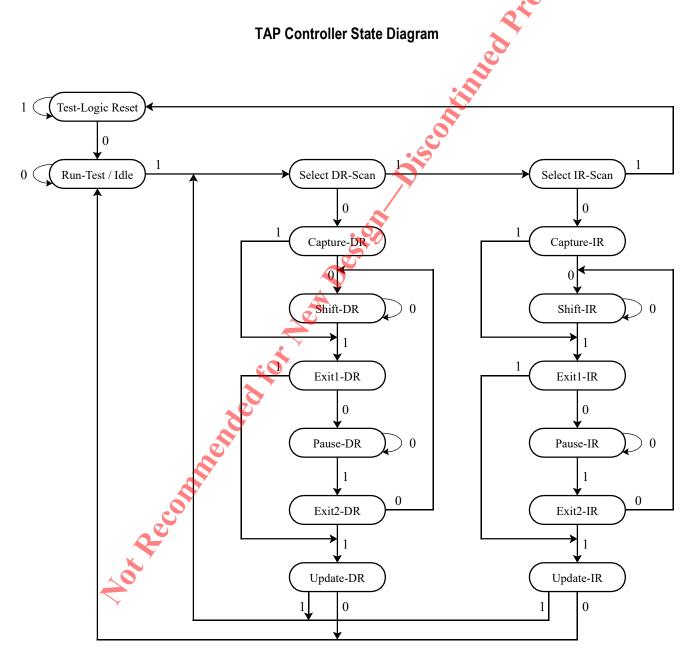

- IEEE 1149.1 JTAG-compliant Boundary Scan

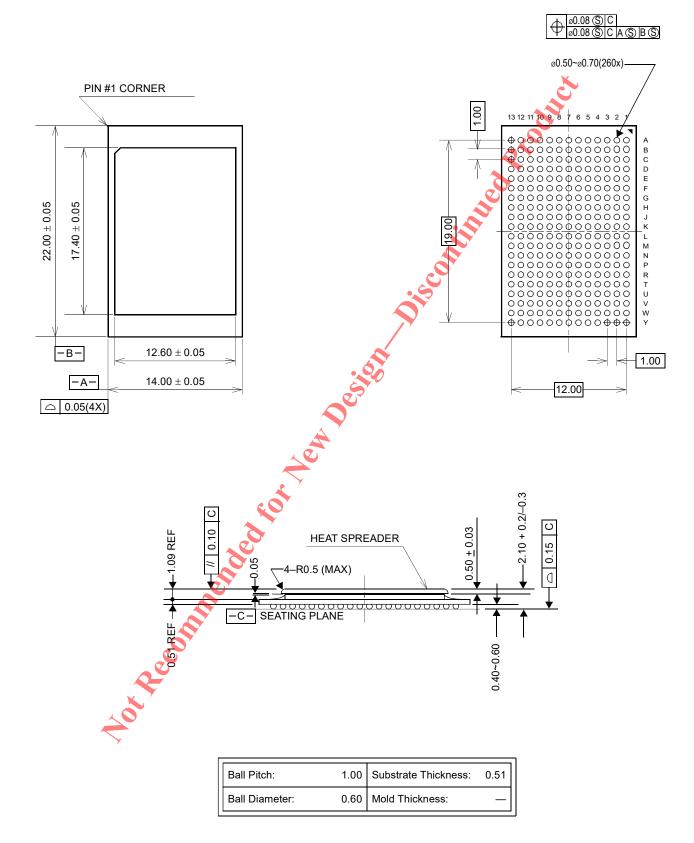

- 260 pin, 14 mm x 22 mm, 1 mm ball pitch BGA package -K: 5/6 RoHS-compliant package

# SigmaDDR-IIIe<sup>™</sup> Family Overview

SigmaDDR-IIIe ECCRAMs are the Common I/O half of the SigmaQuad-IIIe/SigmaDDR-IIIe family of high performance ECCRAMs. Although very similar to GSI's second generation of networking SRAMs (the SigmaQuad-II/SigmaDDR-II family), these third generation devices offer several new features that help enable significantly higher performance.

# A Recommen

# **Clocking and Addressing Schemes**

The GS8673ET18/36BK SigmaDDR-HIE ECCRAMs are synchronous devices. They employ three pairs of positive and negative input clocks; one pair of master clocks, <u>CK</u> and <u>CK</u>, and two pairs of write data clocks, KD[1:0] and <u>KD</u>[1:0]. All six input clocks are single-ended; that is, each is received by a dedicated input buffer.

CK and  $\overline{CK}$  are used to latch address and control inputs, and to control all output timing. KD[1:0] and  $\overline{KD}$ [1:0] are used solely to latch data inputs.

Each internal read and write operation in a SigmaDDR-IIIe B2 ECCRAM is two times wider than the device I/O bus. An input data bus de-multiplexer is used to accumulate incoming data before it is simultaneously written to the memory array. An output data multiplexer is used to capture the data produced from a single memory array read and then route it to the appropriate output drivers as needed. Therefore, the address field of a SigmaDDR-IIIe B2 ECCRAM is always one address pin less than the advertised index depth (e.g. the 4M x 18 has 2M addressable index).

# **On-Chip ECC**

GSI's ECCRAMs implement an ECC algorithm that detects and corrects all single-bit memory errors, including those induced by SER events such as cosmic rays, alpha particles, etc. The resulting Soft Error Rate of these devices is anticipated to be <0.002 FITs/Mb — a 5-order-of-magnitude improvement over comparable SRAMs with no on-chip ECC, which typically have an SER of 200 FITs/Mb or more.

All quoted SER values are at sea level in New York City.

| Speed Grade | Max Operating Frequency | Read Latency | V <sub>DD</sub> |

|-------------|-------------------------|--------------|-----------------|

| -725S       | 725 MHz                 | 3 cycles     | 1.3V to 1.4V    |

| -625S       | 625 MHz                 | 3 cycles     | 1.3V to 1.4V    |

| -550S       | 550 MHz                 | 3 cycles     | 1.3V to 1.4V    |

# Parameter Synopsis

|   | 4M x 18 (Top View) |                  |                  |                  |                 |                  |                  |                  |                 |                  |                  |                  |                  |

|---|--------------------|------------------|------------------|------------------|-----------------|------------------|------------------|------------------|-----------------|------------------|------------------|------------------|------------------|

|   | 1                  | 2                | 3                | 4                | 5               | 6                | 7                | 8                | 9               | 10               | 11               | 12               | 13               |

| Α | V <sub>DD</sub>    | $V_{DDQ}$        | V <sub>DD</sub>  | $V_{DDQ}$        | MCL             | MCH<br>(CFG)     | MCL              | ZQ               | PZT1            | $V_{DDQ}$        | V <sub>DD</sub>  | $V_{DDQ}$        | $V_{DD}$         |

| В | V <sub>SS</sub>    | NU <sub>IO</sub> | V <sub>SS</sub>  | NU               | MVQ             | MCL              | NC<br>(RSVD)     | MCL<br>(SIOM)    | PZT0            | NU               | V <sub>SS</sub>  | DQ0              | $V_{SS}$         |

| C | DQ17               | V <sub>DDQ</sub> | NU               | V <sub>DDQ</sub> | V <sub>SS</sub> | SA               | V <sub>DD</sub>  | SA               | V <sub>SS</sub> | V <sub>DDQ</sub> | NU               | V <sub>DDQ</sub> | NU <sub>IO</sub> |

| D | V <sub>SS</sub>    | NU <sub>IO</sub> | V <sub>SS</sub>  | NU               | SA              | V <sub>DDQ</sub> | NC<br>(288 Mb)   | V <sub>DDQ</sub> | NC<br>(144 Mb)  | NU               | V <sub>SS</sub>  | DQ1              | V <sub>SS</sub>  |

| Е | DQ16               | V <sub>DDQ</sub> | NU               | V <sub>DD</sub>  | V <sub>SS</sub> | SA               | V <sub>SS</sub>  | SA               | V <sub>SS</sub> | VDD              | NU               | V <sub>DDQ</sub> | NU <sub>IO</sub> |

| F | V <sub>SS</sub>    | NU <sub>IO</sub> | V <sub>SS</sub>  | NU               | SA              | V <sub>DD</sub>  | V <sub>DDQ</sub> | V <sub>DD</sub>  | SA              | NU               | V <sub>SS</sub>  | DQ2              | V <sub>SS</sub>  |

| G | DQ15               | NU <sub>IO</sub> | NUI              | NUI              | V <sub>SS</sub> | SA               | MZT1             | SA               | V <sub>SS</sub> | NU               | NUI              | DQ3              | NU <sub>IO</sub> |

| Η | DQ14               | $V_{DDQ}$        | NUI              | V <sub>DDQ</sub> | SA              | $V_{DDQ}$        | R/W              | $V_{DDQ}$        | SA              | V <sub>DDQ</sub> | NU               | $V_{DDQ}$        | NU <sub>IO</sub> |

| J | V <sub>SS</sub>    | NU <sub>IO</sub> | V <sub>SS</sub>  | NU               | V <sub>SS</sub> | SA               | V <sub>SS</sub>  | SA               | N <sub>SS</sub> | NU               | V <sub>SS</sub>  | DQ4              | V <sub>SS</sub>  |

| K | CQ1                | V <sub>DDQ</sub> | V <sub>REF</sub> | V <sub>DD</sub>  | KD1             | $V_{DD}$         | СК               | VDD              | KD0             | V <sub>DD</sub>  | V <sub>REF</sub> | $V_{DDQ}$        | CQ0              |

| L | CQ1                | $V_{SS}$         | QVLD1            | $V_{SS}$         | KD1             | $V_{DDQ}$        | CK               | V <sub>DDQ</sub> | KD0             | $V_{SS}$         | QVLD0            | $V_{SS}$         |                  |

| М | V <sub>SS</sub>    | DQ13             | V <sub>SS</sub>  | NUI              | V <sub>SS</sub> | SA               | V <sub>SS</sub>  | SA               | V <sub>SS</sub> | NUI              | V <sub>SS</sub>  | NU <sub>IO</sub> | $V_{SS}$         |

| N | NU <sub>IO</sub>   | V <sub>DDQ</sub> | NU               | V <sub>DDQ</sub> | MCL             | V <sub>DDQ</sub> | Ð                | V <sub>DDQ</sub> | MCH             | V <sub>DDQ</sub> | NU               | V <sub>DDQ</sub> | DQ5              |

| Р | NU <sub>IO</sub>   | DQ12             | NU               | NU               | V <sub>SS</sub> | SA               | MZT0             | SA               | V <sub>SS</sub> | NU               | NU               | NU <sub>IO</sub> | DQ6              |

| R | V <sub>SS</sub>    | DQ11             | V <sub>SS</sub>  | NU               | MCH             | Vpp              | V <sub>DDQ</sub> | V <sub>DD</sub>  | RST             | NU               | V <sub>SS</sub>  | NU <sub>IO</sub> | V <sub>SS</sub>  |

| Т | NU <sub>IO</sub>   | V <sub>DDQ</sub> | NU               | V <sub>DD</sub>  | V <sub>SS</sub> | SA               | V <sub>SS</sub>  | SA               | V <sub>SS</sub> | V <sub>DD</sub>  | NU               | V <sub>DDQ</sub> | DQ7              |

| U | V <sub>SS</sub>    | DQ10             | V <sub>SS</sub>  | NUI              | NUC             | V <sub>DDQ</sub> | MCL              | V <sub>DDQ</sub> | NUI             | NUI              | V <sub>SS</sub>  | NU <sub>IO</sub> | $V_{SS}$         |

| ۷ | NU <sub>IO</sub>   | V <sub>DDQ</sub> | NUI              | V <sub>DDQ</sub> | Vss             | SA<br>(x18)      | V <sub>DD</sub>  | SA<br>(B2)       | V <sub>SS</sub> | V <sub>DDQ</sub> | NUI              | V <sub>DDQ</sub> | DQ8              |

| W | V <sub>SS</sub>    | DQ9              | V <sub>SS</sub>  | NU               | тск             | MCH              | NC<br>(RSVD)     | MCL              | TMS             | NU               | V <sub>SS</sub>  | NU <sub>IO</sub> | V <sub>SS</sub>  |

| Y | V <sub>DD</sub>    | V <sub>DDQ</sub> | V <sub>DD</sub>  | VDDQ             | TDO             | ZT               | MCH              | MCL              | TDI             | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | V <sub>DD</sub>  |

### Notes:

1. Pins 5A, 5N, 6B, 7A, 7U, 8W, and 8Y must be tied Low in this device.

2. Pins 5R, 6W, 7Y, and 9N must be tied High in this device.

- 3. Pins 5U and 9U are unused in this device. They must be left unconnected or driven Low.

- 4. Pin 6A is defined as mode pin CFG in the pinout standard. It must be tied High in this device to select x18 configuration.

- 5. Pin 8B is defined as mode pin SIOM in the pinout standard. It must be tied Low in this device to select Common I/O configuration.

- 6. Pin 6V is defined as address pin SA for x18 devices. It is used in this device.

- 7. Pin 8V is defined as address pin SA for B2 devices. It is used in this device.

- 8. Pin 9D is reserved as address pin SA for 144Mb devices. It is a true no-connect in this device.

- 9. Pin 7D is reserved as address pin SA for 288Mb devices. It is a true no-connect in this device.

|   | 2M x 36 (Top View) |                  |                  |                  |                 |                          |                  |                  |                 |                  |                  |                  |                 |

|---|--------------------|------------------|------------------|------------------|-----------------|--------------------------|------------------|------------------|-----------------|------------------|------------------|------------------|-----------------|

|   | 1                  | 2                | 3                | 4                | 5               | 6                        | 7                | 8                | 9               | 10               | 11               | 12               | 13              |

| Α | $V_{DD}$           | V <sub>DDQ</sub> | V <sub>DD</sub>  | $V_{DDQ}$        | MCL             | MCL<br>(CFG)             | MCL              | ZQ               | PZT1            | V <sub>DDQ</sub> | V <sub>DD</sub>  | $V_{DDQ}$        | $V_{DD}$        |

| В | $V_{SS}$           | DQ35             | V <sub>SS</sub>  | NUI              | MVQ             | MCL                      | NC<br>(RSVD))    | MCL<br>(SIOM)    | PZT0            | NUI              | V <sub>SS</sub>  | DQ0              | $V_{SS}$        |

| C | DQ26               | V <sub>DDQ</sub> | NU               | V <sub>DDQ</sub> | $V_{SS}$        | SA                       | V <sub>DD</sub>  | SA               | V <sub>SS</sub> | V <sub>DDQ</sub> | NU               | V <sub>DDQ</sub> | DQ9             |

| D | V <sub>SS</sub>    | DQ34             | V <sub>SS</sub>  | NU               | SA              | V <sub>DDQ</sub>         | NC<br>(288 Mb)   | V <sub>DDQ</sub> | NC<br>(144 Mb)  | NU               | <b>V</b> SS      | DQ1              | $V_{SS}$        |

| Е | DQ25               | V <sub>DDQ</sub> | NU               | V <sub>DD</sub>  | $V_{SS}$        | SA                       | V <sub>SS</sub>  | SA               | V <sub>SS</sub> | VDD              | NU <sub>I</sub>  | $V_{DDQ}$        | DQ10            |

| F | V <sub>SS</sub>    | DQ33             | V <sub>SS</sub>  | NU               | SA              | V <sub>DD</sub>          | V <sub>DDQ</sub> | V <sub>DD</sub>  | SA              | N                | V <sub>SS</sub>  | DQ2              | $V_{SS}$        |

| G | DQ24               | DQ32             | NU               | NUI              | $V_{SS}$        | SA                       | MZT1             | SA               | V <sub>SS</sub> | NU               | NUI              | DQ3              | DQ11            |

| Н | DQ23               | V <sub>DDQ</sub> | NU               | V <sub>DDQ</sub> | SA              | V <sub>DDQ</sub>         | R/W              | V <sub>DDQ</sub> | SA              | V <sub>DDQ</sub> | NU               | $V_{DDQ}$        | DQ12            |

| J | $V_{SS}$           | DQ31             | V <sub>SS</sub>  | NU               | $V_{SS}$        | SA                       | V <sub>SS</sub>  | SA               | N <sub>SS</sub> | NU               | V <sub>SS</sub>  | DQ4              | $V_{SS}$        |

| Κ | CQ1                | V <sub>DDQ</sub> | V <sub>REF</sub> | V <sub>DD</sub>  | KD1             | V <sub>DD</sub>          | СК               | V <sub>DD</sub>  | KD0             | V <sub>DD</sub>  | V <sub>REF</sub> | $V_{DDQ}$        | CQ0             |

| L | CQ1                | V <sub>SS</sub>  | QVLD1            | V <sub>SS</sub>  | KD1             | V <sub>DDQ</sub>         | СК               | V <sub>DDQ</sub> | KD0             | V <sub>SS</sub>  | QVLD0            | V <sub>SS</sub>  |                 |

| М | $V_{SS}$           | DQ22             | V <sub>SS</sub>  | NUI              | $V_{SS}$        | SA                       | V <sub>SS</sub>  | SA               | V <sub>SS</sub> | NUI              | V <sub>SS</sub>  | DQ13             | $V_{SS}$        |

| N | DQ30               | V <sub>DDQ</sub> | NU               | V <sub>DDQ</sub> | MCL             | V <sub>DDQ</sub>         | Ð                | V <sub>DDQ</sub> | MCH             | V <sub>DDQ</sub> | NU               | $V_{DDQ}$        | DQ5             |

| Р | DQ29               | DQ21             | NU               | NU               | $V_{SS}$        | SA                       | MZT0             | SA               | V <sub>SS</sub> | NU               | NU               | DQ14             | DQ6             |

| R | V <sub>SS</sub>    | DQ20             | V <sub>SS</sub>  | NU               | MCH             | Vpp                      | V <sub>DDQ</sub> | V <sub>DD</sub>  | RST             | NU               | V <sub>SS</sub>  | DQ15             | $V_{SS}$        |

| Т | DQ28               | V <sub>DDQ</sub> | NU               | V <sub>DD</sub>  | V <sub>SS</sub> | SA                       | V <sub>SS</sub>  | SA               | V <sub>SS</sub> | V <sub>DD</sub>  | NU               | $V_{DDQ}$        | DQ7             |

| U | $V_{SS}$           | DQ19             | V <sub>SS</sub>  | NUI              | NUC             | V <sub>DDQ</sub>         | MCL              | V <sub>DDQ</sub> | NUI             | NUI              | V <sub>SS</sub>  | DQ16             | $V_{SS}$        |

| ۷ | DQ27               | V <sub>DDQ</sub> | NUI              | V <sub>DDQ</sub> | Vss             | NU <sub>I</sub><br>(x18) | V <sub>DD</sub>  | SA<br>(B2)       | V <sub>SS</sub> | V <sub>DDQ</sub> | NU               | $V_{DDQ}$        | DQ8             |

| W | $V_{SS}$           | DQ18             | V <sub>SS</sub>  | NU               | тск             | MCH                      | NC<br>(RSVD)     | MCL              | TMS             | NU               | V <sub>SS</sub>  | DQ17             | $V_{SS}$        |

| Y | V <sub>DD</sub>    | V <sub>DDQ</sub> | V <sub>DD</sub>  | VDDQ             | TDO             | ZT                       | MCH              | MCL              | TDI             | V <sub>DDQ</sub> | V <sub>DD</sub>  | $V_{DDQ}$        | V <sub>DD</sub> |

### Notes:

1. Pins 5A, 5N, 6B, 7A, 7U, 8W, and 8Y must be tied Low in this device.

2. Pins 5R, 6W, 7Y, and 9N must be tied High in this device.

- 3. Pins 5U and 9U are unused in this device. They must be left unconnected or driven Low.

- 4. Pin 6A is defined as mode pin CFG in the pinout standard. It must be tied Low in this device to select x36 configuration.

- 5. Pin 8B is defined as mode pin SIOM in the pinout standard. It must be tied Low in this device to select Common I/O configuration.

- 6. Pin 6V is defined as address pin SA for x18 devices. It is unused in this device, and must be left unconnected or driven Low.

- 7. Pin 8V is defined as address pin SA for B2 devices. It is used in this device.

- 8. Pin 9D is reserved as address pin SA for 144Mb devices. It is a true no-connect in this device.

- 9. Pin 7D is reserved as address pin SA for 288Mb devices. It is a true no-connect in this device.

# **Pin Description**

| Symbol                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Туре   |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| SA                          | Address — Read or Write Address is registered on ↑CK.                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input  |

| DQ[35:0]                    | Write/Read Data — Registered on ↑KD and ↑KD during Write operations; aligned with ↑CQ and ↑CQ during Read operations.<br>DQ[17:0] - x18 and x36.<br>DQ[35:18] - x36 only.                                                                                                                                                                                                                                                                                                                      | I/O    |

| QVLD[1:0]                   | Read Data Valid—Driven high one half cycle before valid read data.                                                                                                                                                                                                                                                                                                                                                                                                                             | Output |

| CK, CK                      | Primary Input Clocks — Dual single-ended. Used for latching address and control inputs, for internal timing control, and for output timing control.                                                                                                                                                                                                                                                                                                                                            | Input  |

| <u>KD</u> [1:0],<br>KD[1:0] | Write Data Input Clocks — Dual single-ended. Used for latching write data inputs.<br>KD0, KD0: latch DQ[17:0] in x36, DQ[8:0] in x18.<br>KD1, KD1: latch DQ[35:18] in x36, DQ[17:9] in x18.                                                                                                                                                                                                                                                                                                    | Input  |

| <u>CQ</u> [1:0],<br>CQ[1:0] | Echo Clocks — Free-running output (echo) clocks, tightly aligned with read data outputs. Facilitate source-synchronous operation.<br>CQ0, <u>CQ</u> 0: align with DQ[17:0] in x36, DQ[8:0] in x18.<br>CQ1, CQ1: align with DQ[35:18] in x36, DQ[17:9] in x18.                                                                                                                                                                                                                                  | Output |

| LD                          | Load Enable — Registered on↑CK.<br>LD = 0: Loads a new address and initiates a Read or Write operation.<br>LD = 1: Initiates a NOP operation.                                                                                                                                                                                                                                                                                                                                                  | Input  |

| R/W                         | Read / Write Enable — Registered on $\uparrow CK$ $R/W = 0$ : initiates a Write operation when LD = 0. $R/W = 1$ : initiates a Read operation when LD = 0.                                                                                                                                                                                                                                                                                                                                     | Input  |

| RST                         | Reset — Holds the device inactive and resets the device to its initial power-on state when asserted High. Weakly pulled Low internally.                                                                                                                                                                                                                                                                                                                                                        | Input  |

| ZQ                          | Driver Impedance Control Resistor Input — Must be connected to V <sub>SS</sub> through an external resistor RQ to program driver impedance                                                                                                                                                                                                                                                                                                                                                     | Input  |

| ZT                          | <b>ODT Impedance Control Resistor Input</b> — Must be connected to V <sub>SS</sub> through an external resistor RT to program ODT impedance.                                                                                                                                                                                                                                                                                                                                                   | Input  |

| MZT[1:0]                    | ODT Mode Select — Set the ODT state globally for all input groups. Must be tied High or Low.         MZT[1:0] = 00: disables ODT on all input groups, regardless of PZT[1:0].         MZT[1:0] = 01: enables strong ODT on select input groups, as specified by PZT[1:0].         MZT[1:0] = 10: enables weak ODT on select input groups, as specified by PZT[1:0].         MZT[1:0] = 10: enables weak ODT on select input groups, as specified by PZT[1:0].         MZT[1:0] = 11: reserved. | Input  |

| PZT[1:0]                    | OD Configuration Select — Set the ODT state for various combinations of input groups when MZT[1:0] =<br>01 or 10. Must be tied High or Low.<br>PZT[1:0] = 00: enables ODT on write data only.<br>PZT[1:0] = 01: enables ODT on write data and input clocks.<br>PZT[1:0] = 10: enables ODT on write data, address, and control.<br>PZT[1:0] = 11: enables ODT on write data, input clocks, address, and control.                                                                                | Input  |

# Pin Description (Continued)

| O Voltage Select — Indicates what voltage is supplied to the V <sub>DDQ</sub> pins. Must be tied High or Low.         MVQ = 0: Configure for 1.2V or 1.35V nominal V <sub>DDQ</sub> .         MVQ = 1: Configure for 1.5V nominal V <sub>DDQ</sub> .         Core Power Supply — 1.35V nominal core supply voltage. | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Fore Power Supply</b> — 1.35V nominal core supply voltage.                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| O Power Supply — 1.2V or 1.35V or 1.5V nominal I/O supply voltage. Configurable via MVQ pin.                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| nput Reference Voltage — Input buffer reference voltage.                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Ground                                                                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TAG Clock                                                                                                                                                                                                                                                                                                           | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TAG Mode Select — Weakly pulled High internally.                                                                                                                                                                                                                                                                    | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TAG Data Input — Weakly pulled High internally.                                                                                                                                                                                                                                                                     | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TAG Data Output                                                                                                                                                                                                                                                                                                     | Outpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>lust Connect High</b> — May be tied to $V_{DDQ}$ directly or via a 1k $\Omega$ resistor.                                                                                                                                                                                                                         | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| lust Connect Low — May be tied to $V_{SS}$ directly or via a 1k $\Omega$ resistor.                                                                                                                                                                                                                                  | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| lo Connect — There is no internal chip connection to these pins. They may be left unconnected, or tied ligh or Low.                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| lot Used Input — There is an internal chip connection to these input pins, but they are unused by the evice. They are pulled Low internally, They may be left unconnected or tied/driven Low. They should not be ed/driven High.                                                                                    | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| lot Used Input/Output — There is an internal chip connection to these I/O pins, but they are unused by the evice. The drivers are tri-stated internally. They are pulled Low internally. They may be left unconnected or ed/driven Low. They should not be tied/driven High.                                        | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                     | round<br>TAG Clock<br>TAG Mode Select — Weakly pulled High internally.<br>TAG Data Input — Weakly pulled High internally.<br>TAG Data Output<br>ust Connect High — May be tied to $V_{DDQ}$ directly or via a 1kΩ resistor.<br>ust Connect Low — May be tied to $V_{SS}$ directly or via a 1kΩ resistor.<br>ust Connect Low — May be tied to $V_{SS}$ directly or via a 1kΩ resistor.<br>of Connect — There is no internal chip connection to these pins. They may be left unconnected, or tied<br>igh or Low.<br>of Used Input — There is an internal chip connection to these input pins, but they are unused by the<br>evice. They are pulled Low internally. They may be left unconnected or tied/driven High.<br>of Used Input/Output — There is an internal chip connection to these I/O pins, but they are unused by the<br>evice. The drivers are tri-stated internally. They are pulled Low internally. They may be left unconnected or |

### **Power-Up and Reset Requirements**

For reliability purposes, power supplies must power up simultaneously, or in the following sequence:

V<sub>SS</sub>, V<sub>DD</sub>, V<sub>DDQ</sub>, V<sub>REF</sub> and inputs.

Power supplies must power down simultaneously, or in the reverse sequence.

After power supplies power up, the following start-up sequence must be followed.

### Step 1 (Recommended, but not required): Assert RST High for at least 1ms.

While RST is asserted high:

• Read and Write operations are ignored.

**Note**: If possible, RST should be asserted High before input clocks (begin toggling, and remain asserted High until input clocks are stable and toggling within specification, in order to prevent unstable, out-of-spec input clocks from causing trouble in the SRAM.

Step 2: Begin toggling input clocks.

After input clocks begin toggling, but not necessarily within specification:

• CQ,  $\overline{CQ}$  begin toggling, but not necessarily within specification.

Step 3: Wait until input clocks are stable and toggling within specification.

Step 4: De-assert RST Low (if asserted High).

Step 5: Wait at least 160K (163,840) cycles for driver and ODT impedances to calibrate.

After the impedances have calibrated:

• CQ,  $\overline{CQ}$  begin toggling within specification.

Step 6: Begin initiating Read and Write operations.

### **Reset Usage**

Although not generally recommended, RST may be asserted High at any time after completion of the initial power-up sequence described above, to reset the SRAM control logic to its initial power-on state. However, whenever RST is subsequently de-asserted Low (as in Step 4 in the power up sequence), at least 160K NOP cycles must be initiated (as in Step 5 in the power-up sequence) before Read and Write operations are initiated.

Note: Memory array content may be perturbed/corrupted when RST is asserted High.

# **Error Correction (ECC)**

These devices implement a single-bit error detection and correction algorithm (specifically, a Hamming Code) on each DDR data word (comprising two 9-bit data bytes) transmitted on each 9-bit data bus (i.e., transmitted on DQ[8:0], DQ[17:9], DQ[26:18], and DQ[35:27]). To accomplish this, 5 ECC parity bits (invisible to the user) are utilized per every 18 data bits (visible to the user).

The ECC algorithm neither corrects nor detects multi-bit errors. However, ECCRAMs are architected in such a way that a single SER event very rarely causes a multi-bit error across any given "transmitted data unit", where a "transmitted data unit" represents the data transmitted as the result of a single read or write operation to a particular address. The extreme carity of multi-bit errors results in the SER mentioned previously (i.e., <0.002 FITs/Mb (measured at sea level)).

Not only does the on-chip ECC significantly improve SER performance, but it also frees up the entire memory array for data storage. Frequently, SRAM applications allocate 1/9th of the memory array (i.e., one "error bit" per eight "data bits") for error detection (either simple parity error detection, or system-level ECC error detection and correction). Such error-bit allocation is unnecessary with ECCRAMs; the entire memory array can be utilized for data storage, effectively providing 12.5% greater storage capacity compared to SRAMs of the same density not equipped with on-chip ECC.

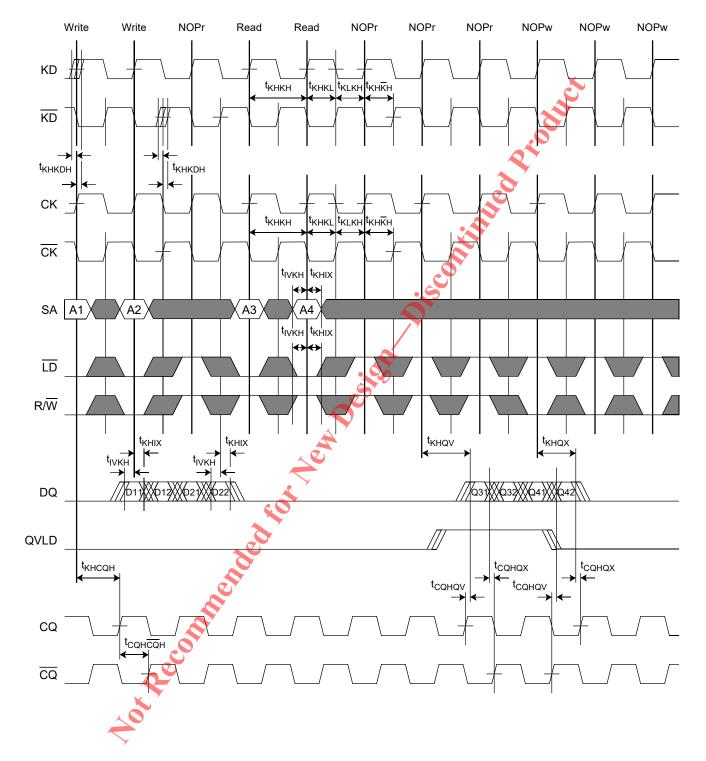

# Input Timing

These devices utilize three pairs of positive and negative input clocks, CK & CK and KD[1:0] & KD[1:0], to latch the various synchronous inputs. Specifically:

↑CK latches all address (SA) inputs.

CK latches all control ( $\overline{LD}$ ,  $R/\overline{W}$ ) inputs.

KD[1:0] and  $\overline{KD}[1:0]$  latch particular write data (DQ) inputs, as follows:

- $\uparrow$ KD0 and  $\uparrow$ KD0 latch DQ[17:0] in x36, and DQ[8:0] in x18.

- $\uparrow$ KD1 and  $\uparrow$ KD1 latch DQ[35:18] in x36, and DQ[17:9] in x18.

# **Output Timing**

These devices provide two pairs of positive and negative output clocks (aka "echo clocks"), CQ[1:0] &  $\overline{CQ}$ [1:0], whose timing is tightly aligned with read data in order to enable feliable source-synchronous data transmission.

Output timing is generated by  $\uparrow CK$  and  $\uparrow \overline{CK}$  as follows:

- $\uparrow$ CK generates  $\uparrow$ CQ[1:0],  $\downarrow$ CQ[1:0],  $\blacksquare$  active, and Q2 inactive.

- .  $\uparrow \overline{CK}$  generates  $\uparrow \overline{CQ}[1:0], \downarrow CQ[1:0], Q1$  inactive, Q2 active, and QVLD active/inactive.

Note: Q1 and Q2 indicate the first and second pieces of read data transferred in any given clock cycle during Read operations.

CQ[1:0] and CQ[1:0] align with particular read data (DQ) and read data valid (QVLD) outputs, as follows:

- $\uparrow$ CQ0 and  $\uparrow$ CQ0 align with DQ[17:0], QVLD0 in x36, and with DQ[8:0], QVLD0 in x18.

- $\uparrow$ CQ1 and  $\uparrow$ CQ1 align with DQ[35:18], QLVD1 in x36, and with DQ[17:9], QVLD1 in x18.

# **Driver Impedance Control**

Programmable Driver Impedance is implemented on the following output signals:

• CQ,  $\overline{CQ}$ , DQ, QVLD.

Driver impedance is programmed by connecting an external resistor RQ between the ZQ pin and V<sub>SS</sub>.

Driver impedance is set to the programmed value within 160K cycles after input clocks are operating within specification and RST is de-asserted Low. It is updated periodically thereafter to compensate for temperature and voltage fluctuations in the system.

| Output Signal    | Pull-Down Impedance (R <sub>OUTL</sub> ) | Pull-Up Impedance (R <sub>OUTH</sub> ) |

|------------------|------------------------------------------|----------------------------------------|

| CQ, CQ, DQ, QVLD | RQ*0.2 ± 15%                             | RQ*0.2 ± 15%                           |

### Notes:

- 1.  $R_{OUTL}$  and  $R_{OUTH}$  apply when  $175\Omega \le RQ \le 225\Omega$ ..

- 2. The mismatch between R<sub>OUTL</sub> and R<sub>OUTH</sub> is less than 10%, guaranteed by design.

# **ODT Impedance Control**

Programmable ODT Impedance is implemented on the following input signals:

• CK,  $\overline{CK}$ , KD,  $\overline{KD}$ , SA,  $\overline{LD}$ , R/ $\overline{W}$ , DQ.

ODT impedance is programmed by connecting an external resistor **RT** between the ZT pin and V<sub>SS</sub>.

ODT impedance is set to the programmed value within 160K cycles after input clocks are operating within specification and RST is de-asserted Low. It is updated periodically thereafter to compensate for temperature and voltage fluctuations in the system

| Input Signal   | PZT[1:0] | MZT[1:0] | Pull-Down Impedance (R <sub>INL</sub> ) | Pull-Up Impedance (R <sub>INH</sub> ) |

|----------------|----------|----------|-----------------------------------------|---------------------------------------|

|                | X0       | XX       | disabled                                | disabled                              |

| CK, CK, KD, KD | X1       | .01      | RT ± 15%                                | RT ± 15%                              |

|                | X1       | 10       | RT*2 ± 20%                              | $RT*2 \pm 20\%$                       |

|                | 0X 👌     | XX       | disabled                                | disabled                              |

| SA, LD, R/W    | 1X 0     | 01       | RT ± 15%                                | $RT \pm 15\%$                         |

|                |          | 10       | RT*2 ± 20%                              | $RT*2 \pm 20\%$                       |

| DQ             |          | 01       | RT ± 15%                                | RT ± 15%                              |

|                | S XX     | 10       | RT*2 ± 20%                              | $RT*2 \pm 20\%$                       |

### Notes:

- 1. When MZT[1:0] = 00, ODT is disabled on all inputs. MZT[1:0] = 11 is reserved for future use.

- 2.  $R_{INL}$  and  $R_{INH}$  apply when  $105\Omega \le RT \le 135\Omega$ .

- 3. The mismatch between R<sub>INL</sub> and R<sub>INH</sub> is less than 10%, guaranteed by design.

- 4. All ODT is disabled during JTAG EXTEST and SAMPLE-Z instructions.

**Note:** When ODT impedance is enabled on a particular input, that input should always be driven High or Low; it should never be tri-stated (i.e., in a High-Z state). If the input is tri-stated, the ODT will pull the signal to  $V_{DDQ} / 2$  (i.e., to the switch point of the diff-amp receiver), which could cause the receiver to enter a meta-stable state and consume more power than it normally would. This could result in the device's operating currents being higher.

# **Truth Table**

| SA                       | LD                       | R/W                      | Current Operation | DQ (D)                     |                                           | DQ (Q)                     |                                           |

|--------------------------|--------------------------|--------------------------|-------------------|----------------------------|-------------------------------------------|----------------------------|-------------------------------------------|

| ↑СК<br>(t <sub>n</sub> ) | ↑СК<br>(t <sub>n</sub> ) | ↑CK<br>(t <sub>n</sub> ) | (t <sub>n</sub> ) | ↑KD<br>(t <sub>n+1</sub> ) | ↑ <mark>KD</mark><br>(t <sub>n+1½</sub> ) | ↑CQ<br>(t <sub>n+3</sub> ) | ↑ <mark>CQ</mark><br>(t <sub>n+3½</sub> ) |

| V                        | 1                        | Х                        | NOP               | Х                          | X                                         | Hi-Z                       | <u>z</u> / *                              |

| V                        | 0                        | 0                        | Write             | D1                         | D2                                        | Hi-z                       | <u>z</u> / *                              |

| V                        | 0                        | 1                        | Read              | Х                          | X                                         | Q1                         | Q2                                        |

### Notes:

1. 1 = High; 0 = Low; V = Valid (High or Low); X = Don't Care.

- 2. D1 and D2 indicate the first and second pieces of write data transferred during Write operations

- 3. Q1 and Q2 indicate the first and second pieces of read data transferred during Read operations.

- 4. When DQ ODT is disabled (MZT[1:0] = 00), DQ pins are tri-stated for one cycle in response to NOP and Write commands, 3 cycles after the command is sampled.

- 5. When DQ ODT is enabled (MZT[1:0] = 01 or 10), DQ drivers are disabled for one cycle in response to NOP and Write commands, 3 cycles after the command is sampled. The state of the DQ pins during that time (denoted by \* in the table above) is determined by the state of the DQ ODT, as depicted in the Extended DQ Truth Table below.

# **Extended DQ Truth Table**

| LD                       | R/W                      | Current Operation | rrent Operation DQ State   |                            |  |  |  |  |

|--------------------------|--------------------------|-------------------|----------------------------|----------------------------|--|--|--|--|

| ↑СК<br>(t <sub>n</sub> ) | ↑СК<br>(t <sub>n</sub> ) | (t <sub>n</sub> ) | ↑СК<br>(t <sub>n+2</sub> ) | ↑СК<br>(t <sub>n+3</sub> ) |  |  |  |  |

| 1                        | 0                        | NOPw              | ODT Enabled                | _                          |  |  |  |  |

| 0                        | 0                        | Write             | ODT Enabled                | -                          |  |  |  |  |

| 1                        | 1                        | NOPr              | ODT Disabled, Drive Low    | _                          |  |  |  |  |

| 0                        | 1                        | Read              | ODT Disabled, Drive Low    | Drive Read Data            |  |  |  |  |

### Notes:

- 1. DQ ODT is enabled 2 cycles after RW is sampled Low, and disabled 2 cycles after R/W is sampled High.

- 2. When DQ ODT is enabled, DQ output drivers are disabled.

- When DQ ODT is disabled, DQ output drivers are enabled, and drive Low when not driving read data.

- 3. When a Read operation is initiated in cycle "n", R/W must be High at ↑CK of cycle "n+1" (i.e. a Read operation must always be followed by a Read or NOPr operation). In that case, the DQ state in cycle "n+3" is "Drive Read Data", as indicated above.

# DQ State Transition Timing Specifications

| Parameter                            | Symbol | Min | Max | Units |

|--------------------------------------|--------|-----|-----|-------|

| CK Clock High to DQ State Transition | tKHDQT | 1.0 | 2.5 | ns    |

# NOPr and NOPw Requirements

The number of NOPw and NOPr needed during Write -> Read transitions, and the number of NOPr and NOPw needed during Read -> Write transitions, are as follows:

|         | Write -> Rea | d Transition       |     | Read -> Write Transition         |     |          |             |  |  |  |

|---------|--------------|--------------------|-----|----------------------------------|-----|----------|-------------|--|--|--|

| NOPw (a | fter Write)  | NOPr (before Read) |     | ore Read) NOPr (after Read) NOPw |     | NOPw (be | fore Write) |  |  |  |

| min     | typ          | min                | typ | min                              | typ | min      | typ         |  |  |  |

| 0       | 0            | 0                  | 1~2 | 2                                | 3~4 | 2        | 3~4         |  |  |  |

Notes:

- 1. Min NOPw after Write (0) ensures that the SRAM disables DQ ODT 1.5 cycles after it latches the last piece of write data. Typ NOPw is the same as Min NOPw because it is sufficient to ensure that the controller stops driving the last piece of write data before SRAM DQ ODT disable reaches it (as the result of a subsequent NOPr or Read), regardless of SRAM tKQ, prop delay between SRAM and controller, and operating frequency.

- 2. Min NOPr before Read (0) ensures that the SRAM drives Low 1 cycle before the begins driving the first piece of read data. Typ NOPr is greater than Min NOPr in order to ensure that the controller enables DQ ODT after SRAM Low drive reaches it (and before the SRAM drives the first piece of read data), regardless of SRAM tKQ, prop delay between SRAM and controller, and operating frequency.

- 3. Min NOPr after Read (2) ensures that the SRAM drives Low for 1 cycle after it stops driving the last piece of read data and before it enables DQ ODT (as the result of a subsequent NOPw). Typ NOPr is greater than Min NOPr in order to ensure that the controller disables DQ ODT after SRAM Low drive reaches is (and before the SRAM enables DQ ODT), accounting for SRAM tKQ, prop delay between SRAM and controller, and operating frequency.

- 4. Min NOPw before Write (3) ensures that the SRAM enables DQ ODT 1 cycle before it latches the first piece of write data. Typ NOPw is greater than Min NOPw in order to ensure that the controller begins driving the first piece of write data after SRAM DQ ODT enable reaches it, accounting for SRAM tKQ, prop delay between SRAM and controller, and operating frequency.

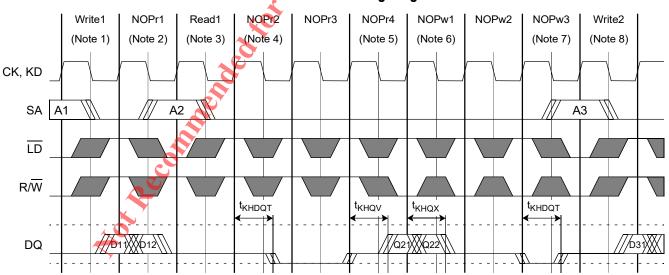

# DQ ODT Control Timing Diagram

**Note:** In the diagram above, the controller is disabling its DQ ODT except from the beginning of NOPr4 to the beginning of NOPw3. And while it is disabling its DQ ODT, the controller is driving DQ Low when it isn't driving write data. Whereas, the SRAM is enabling its DQ ODT except from the beginning of NOPr2 to the beginning of NOPw3. And while it is disabling its DQ ODT, the SRAM is driving DQ Low when it isn't driving DQ Low when it isn't driving DQ Low when it isn't driving the beginning of NOPr3.

# **Electrical Specifications**

# **Absolute Maximum Ratings**

| Parameter                       | Symbol           | Rating                                   | Units |

|---------------------------------|------------------|------------------------------------------|-------|

| Core Supply Voltage             | V <sub>DD</sub>  | -0.3 to +1.6                             | V     |

| I/O Supply Voltage when MVQ = 0 | V <sub>DDQ</sub> | -0.3 to VDD                              | V     |

| I/O Supply Voltage when MVQ = 1 | V <sub>DDQ</sub> | -0.3 to V <sub>DD</sub> + 0.3            | V     |

| Input Voltage when MVQ = 0      | V <sub>IN</sub>  | -0.3 to V <sub>DDQ</sub> + 0.3 (1.7 max) | V     |

| Input Voltage when MVQ = 1      | V <sub>IN</sub>  | -0.3 to V <sub>DDQ</sub> + 0.3 (2.0 max) | V     |

| Maximum Junction Temperature    | TJ               | 125                                      | °C    |

| Storage Temperature             | T <sub>STG</sub> | -55 to 125                               | °C    |

### Note:

Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Recommended Operating Conditions, for an extended period of time, may affect reliability of this component.

# **Recommended Operating Conditions**

| Parameter                                       | Symbol           | Min  | Тур  | Мах             | Units |

|-------------------------------------------------|------------------|------|------|-----------------|-------|

| Core Supply Voltage                             | V <sub>DD</sub>  | 1.3  | 1.35 | 1.4             | V     |

| I/O Supply Voltage - 1.2V nominal when MVQ =    | V <sub>DDQ</sub> | 1.15 | 1.2  | 1.25            | V     |

| I/O Supply Voltage - 1.35V nominal when MVQ = 0 | V <sub>DDQ</sub> | 1.3  | 1.35 | V <sub>DD</sub> | V     |

| I/O Supply Voltage - 1.5V nominal when MVQ = 1  | V <sub>DDQ</sub> | 1.4  | 1.5  | 1.6             | V     |

| Commercial Junction Temperature                 | T <sub>JC</sub>  | 0    | _    | 85              | °C    |

| Industrial Junction Temperature                 | T <sub>JI</sub>  | -40  | _    | 100             | °C    |

### Note:

For reliability purposes, power supplies must power up simultaneously, or in the following sequence:

V<sub>SS</sub>, V<sub>DD</sub>, V<sub>DDQ</sub>, V<sub>REF</sub> and Inputs.

Power supplies must power down simultaneously, or in the reverse sequence.

# Thermal Impedance

| Package | θ JA (C°/W)<br>Airflow = 0 m/s | θ JA (C°/W)<br>Airflow = 1 m/s |      |     | θ JC (C°/W) |

|---------|--------------------------------|--------------------------------|------|-----|-------------|

| FBGA    | 15.5                           | 13.1                           | 12.1 | 4.4 | 0.2         |

Rev: 1.04 8/2019

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

# I/O Capacitance

| Parameter          | Symbol           | Min | Мах | Units | Notes |

|--------------------|------------------|-----|-----|-------|-------|

| Input Capacitance  | C <sub>IN</sub>  | _   | 5.0 | pF    | 1, 3  |

| Output Capacitance | C <sub>OUT</sub> | _   | 5.5 | pF    | 2, 3  |

### Notes:

- 1.  $V_{IN} = V_{DDQ}/2$ .

- 2.  $V_{OUT} = V_{DDQ}/2$ .

- 3.  $T_A = 25^{\circ}C$ , f = 1 MHz.

# Input Electrical Characteristics when MVQ = 0

| Output Capacitance                                                                                                                                   | COUT               | _                       | 5.5                     | рг    | 2, 3    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|-------------------------|-------|---------|

| Notes:<br>1. $V_{IN} = V_{DDQ}/2$ .<br>2. $V_{OUT} = V_{DDQ}/2$ .<br>3. $T_A = 25^{\circ}$ C, f = 1 MHz.<br>nput Electrical Characteristics when MVC | Q = 0              | ž                       | Inted Produ             |       |         |

| Parameter                                                                                                                                            | Symbol             | Min                     | Max                     | Units | Notes   |

| DC Input Reference Voltage                                                                                                                           | V <sub>REFdc</sub> | 0.48 * V <sub>DDQ</sub> | 0.52 * V <sub>DDQ</sub> | V     | _       |

| DC Input High Voltage                                                                                                                                | V <sub>IH1dc</sub> | V <sub>REF</sub> + 0.08 | V <sub>DDQ</sub> + 0.15 | V     | 4       |

| DC Input Low Voltage                                                                                                                                 | V <sub>IL1dc</sub> | -0.15                   | V <sub>REF</sub> – 0.08 | V     | 4       |

| DC Input High Voltage                                                                                                                                | V <sub>IH2dc</sub> | 0.75 * V <sub>DDQ</sub> | V <sub>DDQ</sub> + 0.15 | V     | 5       |

| DC Input Low Voltage                                                                                                                                 | V <sub>IL2dc</sub> | -0.15                   | 0.25 * V <sub>DDQ</sub> | V     | 5       |

| AC Input Reference Voltage                                                                                                                           | VREFac             | 0.47 * V <sub>DDQ</sub> | 0.53 * V <sub>DDQ</sub> | V     | 1       |

| AC Input High Voltage                                                                                                                                | VIH1ac             | V <sub>REF</sub> + 0.15 | V <sub>DDQ</sub> + 0.25 | V     | 2, 3, 4 |

| AC Input Low Voltage                                                                                                                                 | V <sub>IL1ac</sub> | -0.25                   | V <sub>REF</sub> – 0.15 | V     | 2, 3, 4 |

| AC Input High Voltage                                                                                                                                | V <sub>IH2ac</sub> | V <sub>DDQ</sub> -0.2   | V <sub>DDQ</sub> + 0.25 | V     | 2, 5    |

| AC Input Low Voltage                                                                                                                                 | V <sub>IL2ac</sub> | - 0.25                  | 0.2                     | V     | 2, 5    |

Notes:

- 1. V<sub>REFac</sub> is equal to V<sub>REFdc</sub> plus noise

- 2. V<sub>IH</sub> max and V<sub>IL</sub> min apply for pulse widths less than one-quarter of the cycle time.

- 3. Input rise and fall times must be a minimum of 1 V/ns, and within 10% of each other.

- 4. Applies to: CK, CK, KD, KD, SA, LD, R/W, DQ.

- Applies to: RST, MVQ, MZT, PZT. 5.

# Input Electrical Characteristics when MVQ = 1

| Parameter                  | Symbol             | Min                     | Max                     | Units | Notes   |

|----------------------------|--------------------|-------------------------|-------------------------|-------|---------|

| DC Input Reference Voltage | V <sub>REFdc</sub> | 0.47 * V <sub>DDQ</sub> | 0.53 * V <sub>DDQ</sub> | V     | _       |

| DC Input High Voltage      | V <sub>IH1dc</sub> | V <sub>REF</sub> + 0.1  | V <sub>DDQ</sub> + 0.15 | V     | 4       |

| DC Input Low Voltage       | V <sub>IL1dc</sub> | -0.15                   | V <sub>REF</sub> 0.1    | V     | 4       |

| DC Input High Voltage      | V <sub>IH2dc</sub> | 0.75 * V <sub>DDQ</sub> | V <sub>DDQ</sub> + 0.15 | V     | 5       |

| DC Input Low Voltage       | V <sub>IL2dc</sub> | -0.15                   | 0.25 * V <sub>DDQ</sub> | V     | 5       |

| AC Input Reference Voltage | V <sub>REFac</sub> | 0.46 * V <sub>DDQ</sub> | 0.54 * V <sub>DDQ</sub> | V     | 1       |

| AC Input High Voltage      | V <sub>IH1ac</sub> | V <sub>REF</sub> + 0.2  | V <sub>DDQ</sub> + 0.25 | V     | 2, 3, 4 |

| AC Input Low Voltage       | V <sub>IL1ac</sub> | -0.25                   | V <sub>REF</sub> – 0.2  | V     | 2, 3, 4 |

| AC Input High Voltage      | V <sub>IH2ac</sub> | V <sub>DDQ</sub> -0.2   | V <sub>DDQ</sub> + 0.25 | V     | 2, 5    |

| AC Input Low Voltage       | V <sub>IL2ac</sub> | -0.25                   | 0.2                     | V     | 2, 5    |

### Notes:

$V_{REFac}$  is equal to  $V_{REFdc}$  plus noise. 1.

V<sub>IH</sub> max and V<sub>IL</sub> min apply for pulse widths less than one-quarter of the cycle time. 2.

Input rise and fall times must be a minimum of 1V/ns, and within 10% of each other. 3.

Applies to: CK, CK, KD, KD, SA, LD, R/W, DQ. 4.

Applies to: RST, MVQ, MZT, PZT. 5.

# **Output Electrical Characteristics**

| Parameter              | Symbol            | Min   | Мах                     | Units | Notes |

|------------------------|-------------------|-------|-------------------------|-------|-------|

| DC Output High Voltage | V <sub>OHdc</sub> | _     | V <sub>DDQ</sub> + 0.15 | V     | 1     |

| DC Output Low Voltage  | V <sub>OLdc</sub> | -0.15 | _                       | V     | 1     |

| AC Output High Voltage | V <sub>OHac</sub> | _     | V <sub>DDQ</sub> + 0.25 | V     | 1     |

| AC Output Low Voltage  | V <sub>OLac</sub> | -0.25 | _                       | V     | 1     |

Notes: 1. Applies to: CQ, CQ, DQ, QVLD.

# Leakage Currents

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                  | Sym             | bol M     | in      | Мах     | Units  | Notes |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|---------|---------|--------|-------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | ILI             | 1 -       | 2       | 2       | uA     | 1, 2  |

| Input Leakage Current                                                                                                                                                                                                                                                                                                                                                                                                                      | ILI             | 2 -2      | 20      | 2       | uA     | 1, 3  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | ILI             | 3 -       | 2       | 20      | uA     | 1, 4  |

| Output Leakage Current                                                                                                                                                                                                                                                                                                                                                                                                                     | I <sub>LC</sub> | ·         | 2       | 2       | uA     | 5, 6  |

| <ol> <li>Notes:         <ol> <li>V<sub>IN</sub> = V<sub>SS</sub> to V<sub>DDQ</sub>.</li> <li>Applies to: CK, CK, KD, KD, SA, LD, R/W, D<br/>Applies to: MVQ, MZT, PZT, TCK.</li> <li>Applies to: TMS, TDI (weakly pulled up).</li> <li>Applies to: RST (weakly pulled down).</li> <li>V<sub>OUT</sub> = V<sub>SS</sub> to V<sub>DDQ</sub>.</li> <li>Applies to: CQ, CQ, DQ, QVLD, TDO.</li> </ol> </li> <li>Operating Currents</li> </ol> | OQ when ODT is  | disabled. | j'sonth |         |        |       |

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                  | Symbol          | Operating | @ 1.3V  | @ 1.35V | @ 1.4V | Units |

- 1.  $V_{IN} = V_{SS}$  to  $V_{DDQ}$ .

- 2. Applies to: CK, CK, KD, KD, SA, LD, R/W, DQ when ODT is disabled. Applies to: MVQ, MZT, PZT, TCK.

- 3. Applies to: TMS, TDI (weakly pulled up).

- 4. Applies to: RST (weakly pulled down).

- 5.  $V_{OUT} = V_{SS}$  to  $V_{DDQ}$ .

- 6. Applies to: CQ, CQ, DQ, QVLD, TDO.

# **Operating Currents**

| Parameter             | Symbol    | Operating<br>Frequency | @ 1.3V<br>V <sub>DD</sub> | @ 1.35V<br>V <sub>DD</sub> | @ 1.4V<br>V <sub>DD</sub> | Units |

|-----------------------|-----------|------------------------|---------------------------|----------------------------|---------------------------|-------|

|                       | IDD       | 725 MHz                | 1640                      | 1730                       | 1830                      | mA    |

| x18 Operating Current |           | 625 MHz                | 1470                      | 1550                       | 1650                      | mA    |

|                       |           | 550 MHz                | 1330                      | 1410                       | 1490                      | mA    |

|                       | en en IDD | 725 MHz                | 2250                      | 2370                       | 2490                      | mA    |

| x36 Operating Current |           | 625 MHz                | 2000                      | 2110                       | 2230                      | mA    |

|                       |           | 550 MHz                | 1820                      | 1930                       | 2030                      | mA    |

### Notes:

- $I_{OUT} = 0 \text{ mA}; V_{IN} = V_{IH} \text{ or } V_{IL}.$ 1.

- Applies at 50% Reads + 50% Writes. 2.

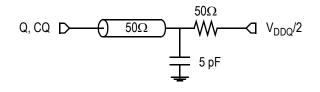

# AC Test Conditions for 1.2V nominal V<sub>DDQ</sub> (MVQ = 0)

| Parameter                                                                | Symbol           | Conditions      | Units |

|--------------------------------------------------------------------------|------------------|-----------------|-------|

| Core Supply Voltage                                                      | V <sub>DD</sub>  | 1.3 to 1.4 💉    | V     |

| I/O Supply Voltage                                                       | V <sub>DDQ</sub> | 1.15 to 1.25    | V     |

| Input Reference Voltage                                                  | V <sub>REF</sub> | 0,6             | V     |

| Input High Level                                                         | V <sub>IH</sub>  | 0.9             | V     |

| Input Low Level                                                          | V <sub>IL</sub>  | 0.3             | V     |