# 8-Channel, PDM to I<sup>2</sup>S/TDM Converter

Data Sheet ADAU7118

#### **FEATURES**

8 channels of PDM audio inputs from digital microphones 16×, 32×, or 64× decimation ratio of PDM to PCM audio data 24-bit resolution to support high sound pressure level (SPL) microphones

126 dB A-weighted SNR

4 kHz to 192 kHz output sampling rate

Bit clock rates of 64×, 128×, 192×, 256×, 384×, or 512× the output sampling rate

**Dual output PDM clocks**

**Automatic PDM clock generation**

Automatic power-down when BCLK removed

Selectable I<sup>2</sup>C control or hardware mode operation

1.2 mA DVDD operating current for 8 channels at 48 kHz frequency sampling rate and 1.8 V supply

Slave I2S or TDM output interface

Up to TDM-16 supported

Configurable TDM slot routing and sizes

I/O supply voltage from 1.70 V to 3.63 V

DVDD supply voltage from 1.10 V to 1.98 V

<5 µA typical DVDD shutdown current

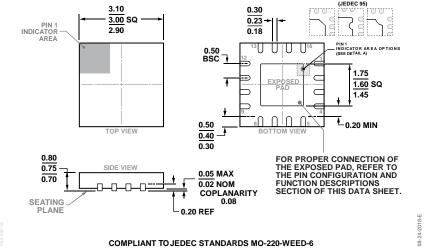

16-lead, 3 mm  $\times$  3 mm, 0.50 mm pitch LFCSP

Power-on reset

### **APPLICATIONS**

Microphone arrays

Mobile computing

Portable electronics

**Consumer electronics**

**Professional electronics**

#### **GENERAL DESCRIPTION**

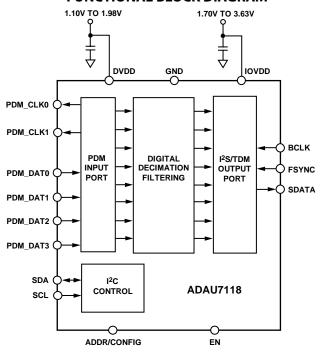

The ADAU7118 converts four stereo pulse density modulation (PDM) bitstreams into one pulse code modulation (PCM) output stream. The source for the PDM data can be eight microphones or other PDM sources. The PCM audio data is output on a serial audio interface port in either inter-IC serial (I<sup>2</sup>S) or time domain multiplexed (TDM) format.

The ADAU7118 is specified over the commercial temperature range (-40°C to +85°C). The ADAU7118 is available in a 16-lead, 3 mm  $\times$  3 mm, 0.40 mm pitch, lead frame chip scale package (LFCSP).

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Note that throughout this data sheet, multifunction pins, such as ADDR/CONFIG, are referred to either by the entire pin name or by a single function of the pin, for example, ADDR, when only that function is relevant.

# **TABLE OF CONTENTS**

| Features 1                                  |

|---------------------------------------------|

| Applications1                               |

| Functional Block Diagram1                   |

| General Description1                        |

| Revision History2                           |

| Specifications3                             |

| Absolute Maximum Ratings                    |

| Thermal Resistance                          |

| ESD Caution                                 |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

| Theory of Operation11                       |

| Power-Up and Initialization11               |

| Clocking11                                  |

| Power-Down State                            |

| Standalone Hardware Mode12                  |

| Serial Audio Output Interface13             |

| I <sup>2</sup> C Control Interface17        |

| Output Pin Drive Strength18                 |

| High-Pass Filter18                          |

| Applications Information19                  |

| Register Summary                            |

| Register Details21                          |

|                                             |

| REVISION HISTORY                            |

| 8/2019—Rev. 0 to Rev. A                     |

| Character Francisco Cartina                 |

|   | ADI Vendor ID Register                                  | 21 |

|---|---------------------------------------------------------|----|

|   | Device ID 1 Register                                    | 21 |

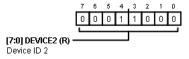

|   | Device ID 2 Register                                    | 21 |

|   | Revision Code Register                                  | 21 |

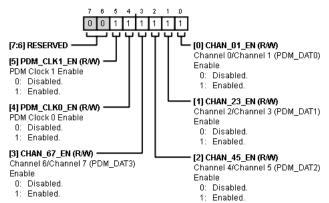

|   | Channel Pair and Clock Enables Register                 | 22 |

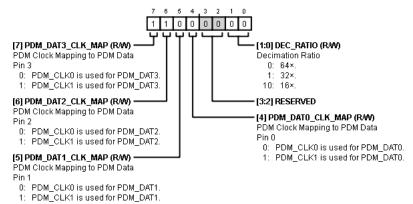

|   | Decimation Ratio and PDM Clock Mapping Controls         |    |

|   | Register                                                | 23 |

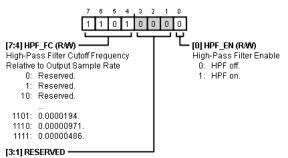

|   | High-Pass Filter Controls Register                      | 24 |

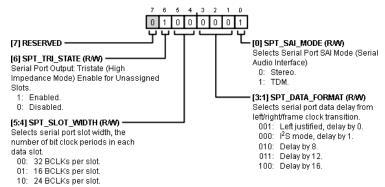

|   | Serial Port Controls 1 Register                         | 25 |

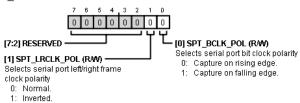

|   | Serial Port Controls 2 Register                         | 25 |

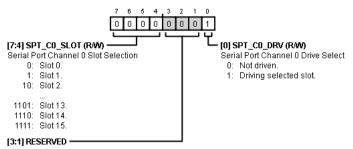

|   | Serial Port Routing and Drive Enable Channel 0 Register | 26 |

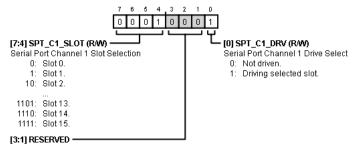

|   | Serial Port Routing and Drive Enable Channel 1 Register | 27 |

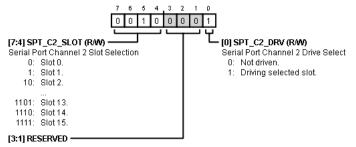

|   | Serial Port Routing and Drive Enable Channel 2 Register | 28 |

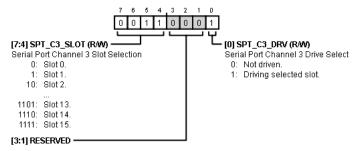

|   | Serial Port Routing and Drive Enable Channel 3 Register | 29 |

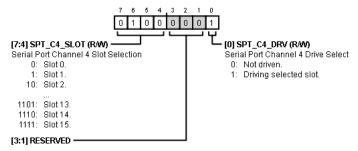

|   | Serial Port Routing and Drive Enable Channel 4 Register | 30 |

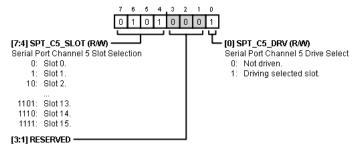

|   | Serial Port Routing and Drive Enable Channel 5 Register | 31 |

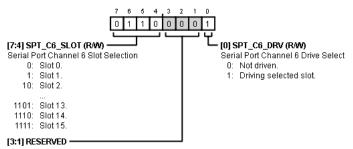

|   | Serial Port Routing and Drive Enable Channel 6 Register | 32 |

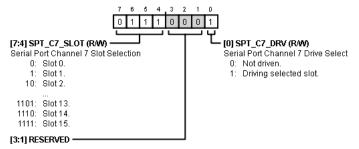

|   | Serial Port Routing and Drive Enable Channel 7 Register | 33 |

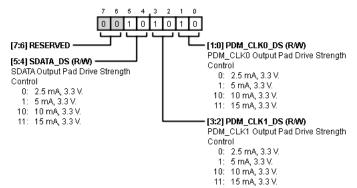

|   | Output Pad Drive Strength Controls Register             | 34 |

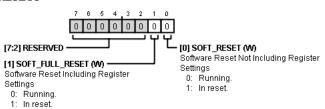

|   | Software Reset Register                                 | 34 |

| С | Outline Dimensions                                      | 35 |

|   | Ordering Guide                                          | 35 |

| 8/2019—Rev. 0 to Rev. A    |  |

|----------------------------|--|

| Change to Features Section |  |

| Changes to Ordering Guide  |  |

5/2019—Revision 0: Initial Version

# **SPECIFICATIONS**

DVDD = 1.10 V to 1.98 V, IOVDD = 1.70 V to 3.63 V,  $T_A$  = 25°C, and pins set to low drive setting, unless otherwise noted. **Table 1.**

| Parameter                                                        | Min             | Тур                  | Max            | Unit         | Test Conditions/Comments                                                                    |

|------------------------------------------------------------------|-----------------|----------------------|----------------|--------------|---------------------------------------------------------------------------------------------|

| DIGITAL INPUT                                                    |                 |                      |                |              |                                                                                             |

| Input Voltage                                                    |                 |                      |                |              |                                                                                             |

| High Level (V <sub>IH</sub> )                                    | 0.7 ×<br>IOVDD  |                      |                | V            |                                                                                             |

| Low Level (V <sub>IL</sub> )                                     |                 |                      | 0.3 ×<br>IOVDD | V            |                                                                                             |

| Input Leakage                                                    |                 |                      |                |              |                                                                                             |

| High Level (I <sub>IH</sub> )                                    |                 |                      | 2.5            | μΑ           | Digital input pins with pull-down resistor                                                  |

| Low Level (I <sub>IL</sub> ) at 0 V                              |                 |                      | 1              | μΑ           | Digital input pins with pull-down resistor                                                  |

| Input Capacitance (C <sub>I</sub> )                              |                 | 2                    |                | pF           | Guaranteed by design                                                                        |

| DIGITAL OUTPUT                                                   |                 |                      |                |              |                                                                                             |

| Output Voltage                                                   |                 |                      |                |              |                                                                                             |

| High Level (V <sub>OH</sub> )                                    | 0.85 ×<br>IOVDD |                      |                | V            | Source current when output is high (I <sub>OH</sub> ) = 1 mA                                |

| Low Level (V <sub>OL</sub> )                                     |                 |                      | 0.1 ×<br>IOVDD | V            | Source current when output is low (I <sub>OL</sub> ) = 1 mA                                 |

| Digital Output Pins,<br>Output Drive<br>IOVDD = 1.8 V<br>Nominal |                 |                      |                |              | Digital output pins drive low impedance PCB traces to a high impedance digital input buffer |

| Drive Strength<br>Setting                                        |                 |                      |                |              |                                                                                             |

| 2.5 mA                                                           | 0.7             |                      |                | mA           |                                                                                             |

| 5 mA                                                             | 1.4             |                      |                | mA           |                                                                                             |

| 10 mA                                                            | 2.8             |                      |                | mA           |                                                                                             |

| 15 mA                                                            | 4.2             |                      |                | mA           |                                                                                             |

| IOVDD = 3.3 V<br>Nominal<br>Drive Strength                       |                 |                      |                |              |                                                                                             |

| Setting                                                          |                 |                      |                |              |                                                                                             |

| 2.5 mA                                                           | 2.5             |                      |                | mA           |                                                                                             |

| 5 mA                                                             | 5               |                      |                | mA           |                                                                                             |

| 10 mA                                                            | 10              |                      |                | mA           |                                                                                             |

| 15 mA                                                            | 15              |                      |                | mA           |                                                                                             |

| PERFORMANCE<br>Dynamic Range                                     |                 | 126                  |                | dB           | 20 Hz to 20 kHz, –60 dB input, A-weighted filter (rms), relative to                         |

| Signal-to-Noise-Ratio<br>(SNR)                                   |                 | 126                  |                | dB           | 0 dBFS output  A-weighted filter, fifth-order input, relative to 0 dBFS output              |

| Decimation Ratio                                                 | 16×             | 64×                  | 64×            |              |                                                                                             |

| Frequency Response                                               | -0.1            | ~ <b>.</b>           | +0.01          | dB           | DC to 0.45 × output sampling rate (f <sub>s</sub> )                                         |

| Stop Band                                                        | ]               | 0.566×f <sub>s</sub> | 1              | Hz           | a see and a see and a see (13)                                                              |

| Stop Band Attenuation                                            | 75              |                      |                | dB           |                                                                                             |

| Group Delay                                                      | 4.47            | 4.47                 | 4.47           | FSYNC cycles | 0.02 f <sub>s</sub> input signal, 64× decimation                                            |

|                                                                  | 5.02            | 5.02                 | 5.02           | FSYNC cycles | 0.02 f <sub>s</sub> input signal, 32× decimation                                            |

|                                                                  | 5.83            | 5.83                 | 5.83           | FSYNC cycles | 0.02 f <sub>s</sub> input signal, 16× decimation                                            |

| Parameter                                   | Min     | Тур    | Max    | Unit         | Test Conditions/Comments                                                                                                                        |

|---------------------------------------------|---------|--------|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Gain                                        | 0       | 0      | 0      | dB           | PDM to PCM                                                                                                                                      |

| Start-Up Time                               | 63      | 64     | 64     | FSYNC cycles | After power-up reset and initialization code runs                                                                                               |

| Bit Resolution                              |         | 24     |        | Bits         | Internal and output                                                                                                                             |

| Interchannel Phase                          | 0       | 0      | 0      | Degrees      | ·                                                                                                                                               |

| High-Pass Filter –3 dB<br>Point             | 0.23328 | 0.9312 | 242.4  | Hz           | $f_S$ = 48 kHz, cutoff frequency set using the HPF_FC bits located in the HPF_CONTROL register, typical value is default setting                |

| CLOCKING                                    |         |        |        |              |                                                                                                                                                 |

| Output Sampling Rate ( $f_s$ )              | 4       | 48     | 192    | kHz          | FSYNC pulse rate                                                                                                                                |

| Bit Clock Frequency<br>(f <sub>BCLK</sub> ) | 0.256   | 12.288 | 24.576 | MHz          |                                                                                                                                                 |

| PDM_CLKx Frequency $(f_{PDM\_CLK})$         | 0.256   | 3.072  | 6.144  | MHz          |                                                                                                                                                 |

| POWER                                       |         |        |        |              |                                                                                                                                                 |

| Supply Voltage                              |         |        |        |              |                                                                                                                                                 |

| Digital Voltage<br>(DVDD Pin)               | 1.10    |        | 1.98   | V            | Supply for digital circuitry                                                                                                                    |

| I/O Supply Voltage<br>(IOVDD Pin)           | 1.70    |        | 3.63   | V            | Supply for input/output (I/O) circuitry, including pads and level shifters                                                                      |

| Supply Current                              |         |        |        |              |                                                                                                                                                 |

| I/O Current<br>(IOVDD Pin)                  |         |        |        |              | Dependent on the clock rates and characteristics of external loads                                                                              |

| Operation State                             |         | 2      |        | mA           | IOVDD = 3.3 V, 48 kHz fs, TDM-8 format, all channels driven, default drive strength, 25 pF capacitance, only one PDM_CLKx pin used              |

|                                             |         | 0.86   |        | mA           | IOVDD = 1.8 V, 48 kHz f <sub>s</sub> , TDM-8 format, all channels driven, default drive strength, 25 pF capacitance, only one PDM_CLKx pin used |

| Shutdown<br>Current                         |         | 16     |        | μΑ           | Power applied, frame and bit clocks applied, and then device placed into power-down state using the procedure in Table 10                       |

|                                             |         | 3      |        | μΑ           | Power applied, frame and bit clocks applied, and then device placed into power-down state using the procedure in Table 9                        |

| Digital Current<br>(DVDD Pin)               |         |        |        |              |                                                                                                                                                 |

| Operation State                             |         | 1.4    |        | mA           | Over all temperatures, full voltage range and silicon skews, 8 channels, 48 kHz $f_{\rm S}$                                                     |

|                                             |         | 1.2    |        | mA           | DVDD = 1.8 V, 8 channels, 48 kHz fs                                                                                                             |

|                                             |         | 0.8    |        | mA           | DVDD = 1.2 V, 8 channels, 48 kHz fs                                                                                                             |

|                                             |         | 0.7    |        | mA           | DVDD = 1.8 V, 4 channels, 48 kHz fs                                                                                                             |

|                                             |         | 0.4    |        | mA           | DVDD = 1.2 V, 4 channels, 48 kHz fs                                                                                                             |

|                                             |         | 0.4    |        | mA           | DVDD = 1.8 V, 8  channels, 16  kHz fs                                                                                                           |

|                                             |         | 0.27   |        | mA           | DVDD = 1.2 V, 8 channels, 16 kHz fs                                                                                                             |

|                                             |         | 0.22   |        | mA           | DVDD = 1.8 V, 4 channels, 16 kHz fs                                                                                                             |

|                                             |         | 0.14   |        | mA           | DVDD = 1.2 V, 4 channels, 16 kHz f <sub>S</sub>                                                                                                 |

| Shutdown<br>Current                         |         | 4      |        | μΑ           | Power-down mode using either method in Table 9 or method in Table 10                                                                            |

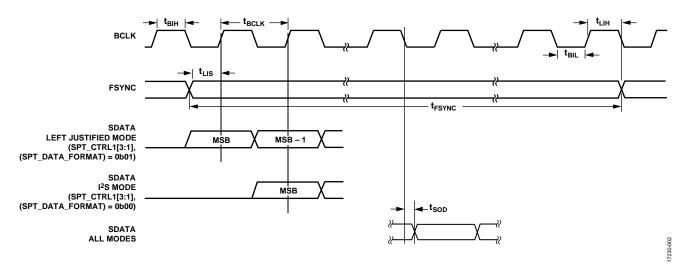

### **Serial Ports**

$T_A = -40$ °C to +85°C, DVDD = 1.10 V to 1.98 V, and IOVDD = 1.70 V to 3.63 V, unless otherwise noted.

Table 2.

| Parameter         | Min  | Max    | Unit | Description                                                                                                                                   |

|-------------------|------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| SERIAL PORT       |      |        |      |                                                                                                                                               |

| $f_{FSYNC}$       |      | 192    | kHz  | FSYNC frequency, 1/t <sub>FSYNC</sub>                                                                                                         |

| <b>t</b> FSYNC    | 5.21 |        | μs   | FSYNC period                                                                                                                                  |

| $f_{BCLK}$        |      | 24.576 | MHz  | BCLK frequency, sample rate ranging from 4 kHz to 192 kHz, 1/t <sub>BCLK</sub>                                                                |

| t <sub>BCLK</sub> | 40.7 |        | ns   | BCLK period                                                                                                                                   |

| t <sub>BIL</sub>  | 18   |        | ns   | BCLK low pulse width, slave mode, BCLK frequency = 24.576 MHz, BCLK period = 40.6 ns                                                          |

| t <sub>BIH</sub>  | 18   |        | ns   | BCLK high pulse width, slave mode, BCLK frequency = 24.576 MHz, BCLK period = 40.6 ns                                                         |

| t <sub>LIS</sub>  | 10   |        | ns   | FSYNC setup to BCLK input rising edge, slave mode, FSYNC frequency = 192 kHz                                                                  |

| t <sub>LIH</sub>  | 10   |        | ns   | FSYNC hold from BCLK input rising edge, slave mode, FSYNC frequency = 192 kHz                                                                 |

| tsod              |      | 20.63  | ns   | SDATA delay from BCLK output falling edge, 25 pf load over entire range of IOVDD, all temperatures and skews, default drive strength of 10 mA |

|                   |      | 11.71  | ns   | $IOVDD = 3.3 V \pm 10\%$ , drive strength set to 0b00, with 25 pf load                                                                        |

|                   |      | 10.37  | ns   | $IOVDD = 3.3 V \pm 10\%$ , drive strength set to 0b01, with 25 pf load                                                                        |

|                   |      | 9.03   | ns   | $IOVDD = 3.3 V \pm 10\%$ , drive strength set to 0b10, with 25 pf load                                                                        |

|                   |      | 8.72   | ns   | $IOVDD = 3.3 V \pm 10\%$ , drive strength set to 0b11, with 25 pf load                                                                        |

|                   |      | 31.02  | ns   | IOVDD = 1.7 V to 1.89 V, drive strength set to 0b00, with 25 pf load                                                                          |

|                   |      | 25.83  | ns   | IOVDD = 1.7 V to 1.89 V, drive strength set to 0b01, with 25 pf load                                                                          |

|                   |      | 20.63  | ns   | IOVDD = 1.7 V to 1.89 V, drive strength set to 0b10, with 25 pf load                                                                          |

|                   |      | 20.33  | ns   | IOVDD = 1.7 V to 1.89 V, drive strength set to 0b11, with 25 pf load                                                                          |

Figure 2. Serial Port Timing Specifications

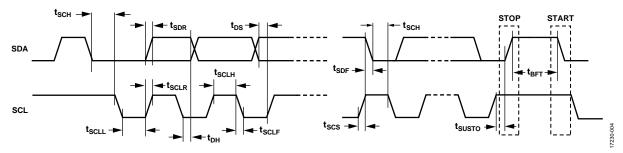

### I<sup>2</sup>C Interface—Slave

$T_A = -40$ °C to +85°C, DVDD = 1.10 V to 1.98 V, and IOVDD = 1.70 V to 3.63 V, unless otherwise noted.

Table 3.

| Parameter                   | Min  | Max  | Unit | Description                                   |

|-----------------------------|------|------|------|-----------------------------------------------|

| I <sup>2</sup> C SLAVE PORT |      |      |      |                                               |

| $f_{SCL}$                   |      | 1000 | kHz  | SCL clock frequency, not shown in Figure 3    |

| <b>t</b> sclh               | 0.26 |      | μs   | SCL pulse width high                          |

| t <sub>SCLL</sub>           | 0.5  |      | μs   | SCL pulse width low                           |

| t <sub>scs</sub>            | 0.26 |      | μs   | Start and repeated start condition setup time |

| <b>t</b> sch                | 0.26 |      | μs   | Start condition hold time                     |

| t <sub>DS</sub>             | 50   |      | ns   | Data setup time                               |

| t <sub>DH</sub>             |      | 0.45 | μs   | Data hold time                                |

| t <sub>SCLR</sub>           |      | 120  | ns   | SCL rise time                                 |

| t <sub>SCLF</sub>           |      | 120  | ns   | SCL fall time                                 |

| t <sub>SDR</sub>            |      | 120  | ns   | SDA rise time                                 |

| t <sub>SDF</sub>            |      | 120  | ns   | SDA fall time                                 |

| t <sub>BFT</sub>            | 0.5  |      | μs   | Bus-free time between stop and start          |

| <b>t</b> susto              | 0.26 |      | μs   | Stop condition setup time                     |

Figure 3. I<sup>2</sup>C Slave Port Timing Specifications

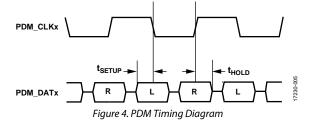

# **PDM Inputs**

$T_A = -40$ °C to +85°C, DVDD = 1.10 V to 1.98 V, IOVDD = 1.70 V to 3.63 V, and PDM data is latched on both edges of the clock (see Figure 4), unless otherwise noted.

Table 4.

| Parameter           | t <sub>MIN</sub> | t <sub>MAX</sub> | Unit | Description     |

|---------------------|------------------|------------------|------|-----------------|

| Timing Requirements |                  |                  |      |                 |

| <b>t</b> setup      | 9                |                  | ns   | Data setup time |

| t <sub>HOLD</sub>   | 3                |                  | ns   | Data hold time  |

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 5.

| Parameter                                      | Rating                          |

|------------------------------------------------|---------------------------------|

| DVDD to Ground                                 | 1.98 V                          |

| IOVDD to Ground                                | 3.63 V                          |

| Digital Inputs                                 | GND – 0.3 V to<br>IOVDD + 0.3 V |

| Maximum Operating Ambient Temperature<br>Range | −40°C to +85°C                  |

| Junction Temperature Range                     | −65°C to +165°C                 |

| Storage Temperature Range                      | −65°C to +150°C                 |

| Soldering (60 sec)                             | 300°C                           |

| Electrostatic Discharge (ESD) Susceptibility   | 4.5 kV                          |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

**Table 6. Thermal Resistance**

| Package Type | $\Theta_{JA}^{1}$ | $\theta_{JC}^2$ | Unit |

|--------------|-------------------|-----------------|------|

| CP-16-22     | 57                | 15              | °C/W |

<sup>&</sup>lt;sup>1</sup> Thermal impedance simulated values are based on a JEDEC 1S0P thermal test board. See JEDEC JESD-51.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board with four thermal vias. See JEDEC JESD-51.

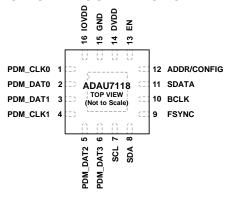

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

EXPOSED PAD. THE EXPOSED PAD MUST BE GROUNDED BY SOLDERING IT

TO A GROUNDED COPPER PAD OF EQUIVALENT SIZE ON THE PCB.

THERMAL VIAS ARE NOT NECESSARY.

Figure 5. Pin Configuration

**Table 7. Pin Function Descriptions**

| Pin No. | Mnemonic    | Description                                                                                                                                                                                                                    |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PDM_CLK0    | PDM Output Clock 0.                                                                                                                                                                                                            |

| 2       | PDM_DAT0    | PDM Input Data 0.                                                                                                                                                                                                              |

| 3       | PDM_DAT1    | PDM Input Data 1.                                                                                                                                                                                                              |

| 4       | PDM_CLK1    | PDM Output Clock 1.                                                                                                                                                                                                            |

| 5       | PDM_DAT2    | PDM Input Data 2.                                                                                                                                                                                                              |

| 6       | PDM_DAT3    | PDM Input Data 3.                                                                                                                                                                                                              |

| 7       | SCL         | I <sup>2</sup> C Serial Clock Input.                                                                                                                                                                                           |

| 8       | SDA         | I <sup>2</sup> C Data.                                                                                                                                                                                                         |

| 9       | FSYNC       | I <sup>2</sup> S/TDM Frame Sync or Left/Right Clock.                                                                                                                                                                           |

| 10      | BCLK        | I <sup>2</sup> S/TDM Bit Clock.                                                                                                                                                                                                |

| 11      | SDATA       | I <sup>2</sup> S/TDM Serial Data Output.                                                                                                                                                                                       |

| 12      | ADDR/CONFIG | I <sup>2</sup> C Address or Standalone Configuration Selection.                                                                                                                                                                |

| 13      | EN          | Chip Enable.                                                                                                                                                                                                                   |

|         |             | Ground this pin to disable the device and put it in low power mode.                                                                                                                                                            |

|         |             | Apply IOVDD to this pin to enable normal operation. All register settings are preserved when the device is disabled. However, the bit clock counters, and the audio data resets, which is the same as performing a soft reset. |

| 14      | DVDD        | Internal Core Digital Power Supply.                                                                                                                                                                                            |

| 15      | GND         | Ground.                                                                                                                                                                                                                        |

| 16      | IOVDD       | Digital Input/Output Power Supply.                                                                                                                                                                                             |

| EP      | EPAD        | Exposed Pad. The exposed pad must be grounded by soldering it to a grounded copper pad of equivalent size on the PCB. Thermal vias are not necessary.                                                                          |

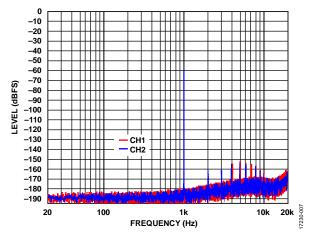

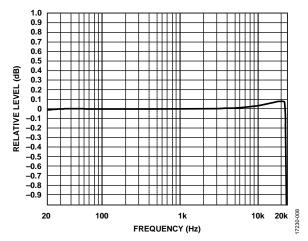

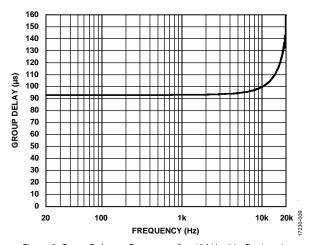

# TYPICAL PERFORMANCE CHARACTERISTICS

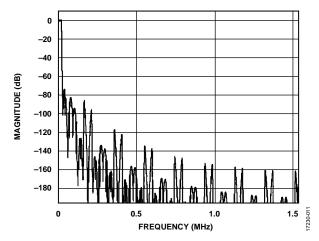

Figure 6. FFT,  $f_S = 48 \text{ kHz}$ , -60 dBFS Input,  $64 \times \text{Decimation}$ , Fifth Order

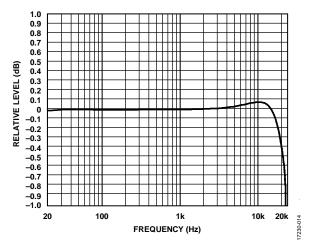

Figure 7. Relative Level vs. Frequency at -10 dBFS Normalized, 64× Decimation,  $f_S = 48$  kHz

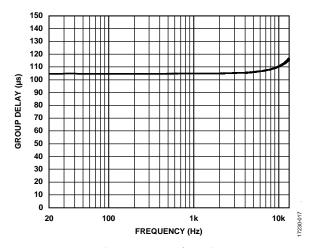

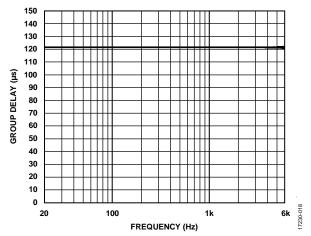

Figure 8. Group Delay vs. Frequency,  $f_S = 48$  kHz,  $64 \times$  Decimation

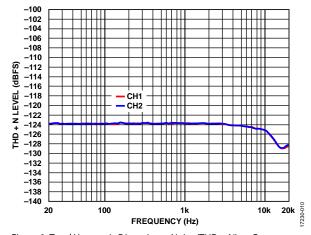

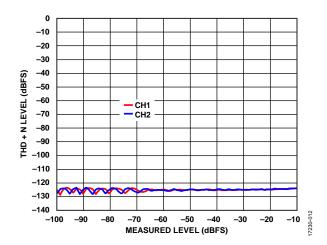

Figure 9. Total Harmonic Distortion + Noise (THD + N) vs. Frequency at -10 dBFS Unweighted,  $f_S = 48$  kHz,  $64 \times$  Decimation, Fifth Order

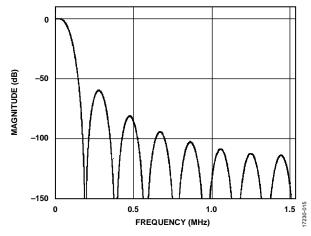

Figure 10. Magnitude vs. Frequency, 48 kHz Output, 64× Decimation

Figure 11. THD + N Level vs. Measured Level, 1 kHz, Unweighted, 64× Decimation, Fifth Order,  $f_S = 48$  kHz

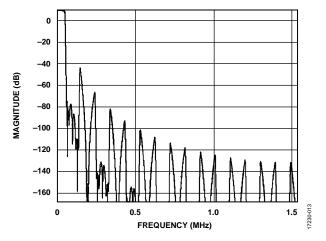

Figure 12. Magnitude vs. Frequency, 48 kHz Output, 32× Decimation

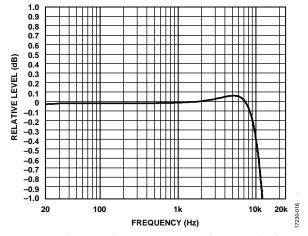

Figure 13. Relative Level vs. Frequency at -10 dBFS Normalized,  $32 \times$  Decimation,  $f_S = 48$  kHz

Figure 14. Magnitude vs. Frequency, 48 kHz Output, 16× Decimation

Figure 15. Relative Level vs. Frequency at -10 dBFS Normalized,  $16 \times$  Decimation,  $f_S = 48$  kHz

Figure 16. Group Delay vs. Frequency,  $f_s = 48$  kHz,  $32 \times$  Decimation

Figure 17. Group Delay vs. Frequency,  $f_S = 48$  kHz,  $16 \times$  Decimation

# THEORY OF OPERATION

The ADAU7118 provides up to 8 channels of decimation from a 1-bit PDM source to a 24-bit PCM audio. The downsampling ratio is typically  $64 \times f_s$ , with  $f_s$  being the PCM output sampling rate, but the downsampling ratio can also be set at  $32 \times f_s$  or  $16 \times f_s$  to facilitate higher output sampling rates. All channels decimate at the same ratio. The 24-bit downsampled PCM audio is output via standard I²S or TDM format.

The input sources for the ADAU7118 can be any device that has a slave PDM output, such as a digital microphone. The output pins of these microphones can connect directly to the input pins of the ADAU7118. There are two separate PDM\_CLKx outputs that are replications of the same signal to allow easier drive of multiple sources. Each PDM\_CLKx can be disabled individually.

The PDM\_DATx input pins are connected to the data output of the PDM sources. Internally, there are 8 channels, Channel 0 through Channel 7. The mapping of PDM\_DATx inputs to the internal channels is detailed in Table 8.

Table 8. PDM\_DATx to Internal Channel Mapping

| Two of the state o |              |                  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|--|--|--|--|--|

| Input Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PDM_CLK Edge | Internal Channel |  |  |  |  |  |

| PDM_DAT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Falling      | 0                |  |  |  |  |  |

| PDM_DAT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Rising       | 1                |  |  |  |  |  |

| PDM_DAT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Falling      | 2                |  |  |  |  |  |

| PDM_DAT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Rising       | 3                |  |  |  |  |  |

| PDM_DAT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Falling      | 4                |  |  |  |  |  |

| PDM_DAT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Rising       | 5                |  |  |  |  |  |

| PDM_DAT3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Falling      | 6                |  |  |  |  |  |

| PDM_DAT3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Rising       | 7                |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                  |  |  |  |  |  |

Each internal channel pair associated with each PDM\_DATx pin can be disabled to save power if those channels are not used.

Each PDM data pin must be assigned to either the PDM\_CLK0 or PDM\_CLK1 clock sources, using the decimation ratio and PDM clock mapping controls register (DEC\_RATIO\_CLK\_MAP), to ensure compliance with timing specifications. The PDM\_CLKx assignment must be the actual PDM clock that is driving the PDM microphone. By default, PDM\_DAT0 and PDM\_DAT1 are mapped to PDM\_CLK0, and PDM\_DAT2 and PDM\_DAT3 are mapped to PDM\_CLK1. This mapping of the two clock sources to the four data input pins can be modified by the PDM\_DATx\_CLK\_MAP bits.

### **POWER-UP AND INITIALIZATION**

The ADAU7118 requires two power supplies to function: the IOVDD and the DVDD. Both power supplies can be applied at the same time. If the power supplies are applied at different times, the IOVDD must be applied first and then the DVDD at any point after. There are no timing restrictions.

After the power supplies have stabilized, the device initializes and is ready to accept incoming I<sup>2</sup>S clocks or I<sup>2</sup>C commands based on the mode of operation.

After the initialization is complete, and I<sup>2</sup>S clocks are applied, it takes 16 full frame sync cycles to begin sending out PDM clocks.

When the PDM clocks start, and after another 48 frame sync cycles, the PDM data shows up on the SDATA pin. These 64 frame sync cycles are listed in Table 1.

The ADAU7118 can operate in two modes of operation: standalone hardware and I<sup>2</sup>C. See the Standalone Hardware Mode section or the I<sup>2</sup>C Control Interface section for more details.

### **CLOCKING**

After power is applied and the power-up initialization is complete, the device is ready to accept I2S clocks. At that point, it takes 16 full frame sync cycles for the device to fully initialize and start sending PDM clocks. If during normal operation the bit clock or frame sync is removed, the ADAU7118 PDM\_CLKx outputs stop immediately, and the ADAU7118 goes into a lower power state automatically. See the Power-Down State section for more details. When the clocks resume, the ADAU7118 relocks to the bit clock and the frame sync signals and adjusts the PDM\_CLKx outputs accordingly. The length of time before the PDM clock outputs resume is 4 frames  $\pm$  1 frame to lock to the incoming signal. If the format of the clock signals change, the ADAU7118 detects this change at the end of the frame and stops the PDM clock outputs. Then, the device reconfigures and resumes sending PDM clocks with no user intervention. Again, the length of time before the PDM clock outputs resume usually takes 4 frames ±1 frame to lock to the incoming signal.

The ADAU7118 requires a BCLK rate that is a minimum of 64× the frame sync (FSYNC) sample rate. BCLK rates of 128×, 192×, 256×, 384×, and 512× the FSYNC rate are also supported. The ADAU7118 automatically detects the ratio between BCLK and FSYNC and generates a PDM clock output at 64 × the FSYNC rate by default. If lower decimation ratios are selected in Register 0x05, DEC\_RATIO\_CLK\_MAP, the PDM output clock rate corresponds with the DEC\_RATIO bits setting. The minimum sampling rate is 4 kHz, and the maximum sampling rate is 192 kHz. The PDM clock range is 256 kHz to 6.144 MHz. Internally, all processing is done at the PDM\_CLK rate.

The two PDM clock outputs, PDM\_CLK0 and PDM\_CLK1, are separate buffered outputs of the same clock. However, the incoming PDM data is clocked in using the signal present at the actual clock pin and not the internal clock going out to the pin. The reason for this is to allow the clock rise time to be slowed by the external capacitance in a similar manner to the PDM data signal. It is recommended to associate the incoming PDM data with the clock output that is actually connected to the PDM microphone. The DEC\_RATIO\_CLK\_MAP register, Register 0x05, is used to assign one of the two clocks to each PDM data input.

#### **POWER-DOWN STATE**

The ADAU7118 can be placed into a power-down state by using one of two methods available. The preferred method is by using register writes to place the device into the lowest possible power-down state. However, for when the ADAU7118 operates in standalone mode, use the second method, which uses the enable pin (EN).

With a system controller and when entering the low power state, disable the PDM clocks and disable the channel outputs by writing a zero to Register 0x04 (ENABLES register). Then, the frame and bit clocks can be removed (stopped) to place the device in the power-down state. Allow enough time for the I<sup>2</sup>C write to complete before stopping the clocks. A minimum of one full frame after the I<sup>2</sup>C write completes is enough wait time. It is not necessary to lower the EN pin, it does not lower the power draw any further. See Table 9 for more details.

Table 9. Placing the ADAU7118 into the Power-Down State Using Register Writes

| Step | Action                          |

|------|---------------------------------|

| 1    | Write a zero into Register 0x04 |

| 2    | Wait at least one frame period  |

| 3    | Stop the frame and bit clocks   |

When the ADAU7118 is in standalone mode, the device can be placed into the power-down state by applying a low signal to the EN pin and then waiting a minimum of one full frame to place the device into the power-down state. See Table 10 for more details. Note that if a pull-up resistor is used on the EN pin, the additional current through this pull-up resistor must be added to the values in Table 1.

Table 10. Placing the ADAU7118 into the Power-Down State when Operating in Standalone Mode

| Step | Action                            |

|------|-----------------------------------|

| 1    | Apply a low voltage to the EN pin |

| 2    | Wait at least one frame period    |

| 3    | Stop the frame and bit clocks     |

To come out of the power-down mode, the order for restarting the clocks vs. enabling the device does not matter. Enabling the device refers to either raising the EN pin or enabling the device by writing to Register 0x04.

#### STANDALONE HARDWARE MODE

Because all channels default to enable and output, the device can be used with the default control settings without I²C and with any setting of the ADDR/CONFIG pin, except for hardware mode. If the ADDR/CONFIG pin is left open, the device is in standalone hardware mode and I²C communications are not possible. See Table 14 for details on the ADDR/CONFIG pin settings. In standalone hardware mode, the settings of the I²C SCL pin and SDA pin can select different functionality by changing the state of some registers from their default. See Table 11 for details of the differences from the default settings.

To achieve the lowest power in standalone hardware mode operation when a BCLK is present, the EN pin is still functional and can be pulled low, placing the device into a low power mode. The EN pin also performs a soft reset but does not reset any of the register settings. Stopping the bit clock and frame sync clocks also places the device into a low power state. See the Clocking section for more details.

Table 11. Standalone Hardware Mode Settings: Changes From Default Settings

| Tubic 11. 0        | Tuble 11. Standardie Hardware Mode Settings. Changes 110m Delaant Settings |                         |                                               |                                            |                                                   |  |  |  |  |

|--------------------|----------------------------------------------------------------------------|-------------------------|-----------------------------------------------|--------------------------------------------|---------------------------------------------------|--|--|--|--|

| SCL Pin<br>Tied to | SDA Pin<br>Tied to                                                         | Operation<br>Settings   | PDM Clock Settings:<br>ENABLES, Register 0x04 | Channel Enables:<br>ENABLES, Register 0x04 | Drive Strength                                    |  |  |  |  |

| IOVDD              | IOVDD                                                                      | 4-channel               | PDM_CLK1_EN bit = 0,<br>disabled              | CHAN_45_EN bit = 0,<br>CHAN_67_EN bit = 0  | Default setting = 10                              |  |  |  |  |

| IOVDD              | GND                                                                        | 8-channel high drive    | Default settings                              | All channels enabled                       | SDATA_DS = 11, PDM_CLK0_DS = 11, PDM_CLK1_EN = 11 |  |  |  |  |

| GND                | IOVDD                                                                      | 6-channel               | Default settings                              | CHAN_67_EN = 0                             | Default setting = 10                              |  |  |  |  |

| GND                | GND                                                                        | 6-channel high<br>drive | Default settings                              | CHAN_67_EN = 0                             | SDATA_DS = 11, PDM_CLK0_DS = 11, PDM_CLK1_EN = 11 |  |  |  |  |

#### **SERIAL AUDIO OUTPUT INTERFACE**

The ADAU7118 supports I<sup>2</sup>S and TDM serial output formats. Up to 16 TDM slots can be used. TDM slot widths of 16 bits, 24 bits, and 32 bits are supported. Any internal channel can be routed to any output slot via the SPT\_Cx\_SLOT bits. By default, each channel is routed to its same number slot. For example, Channel 1 goes to Slot 1 and Channel 6 goes to Slot 6. Each channel can be set to drive during their set slot or not drive (tristate high impedance mode) via their respective SPT\_Cx\_DRV bit. I2S mode or TDM mode selection is via the SPT\_SAI\_MODE bit (Bit 0) in the SPT\_ CTRL1 register. The SDATA pin is in tristate high impedance mode, except when the port is driving serial data by default. It is possible for two or more channels to be set to the same TDM slot. In that case, the lowest channel number wins and drives its data into the slot. The data of the other channel never appears anywhere. There is no cross-checking of register settings to prevent the user from doing this, but the device is not damaged, only the data is missing from the output.

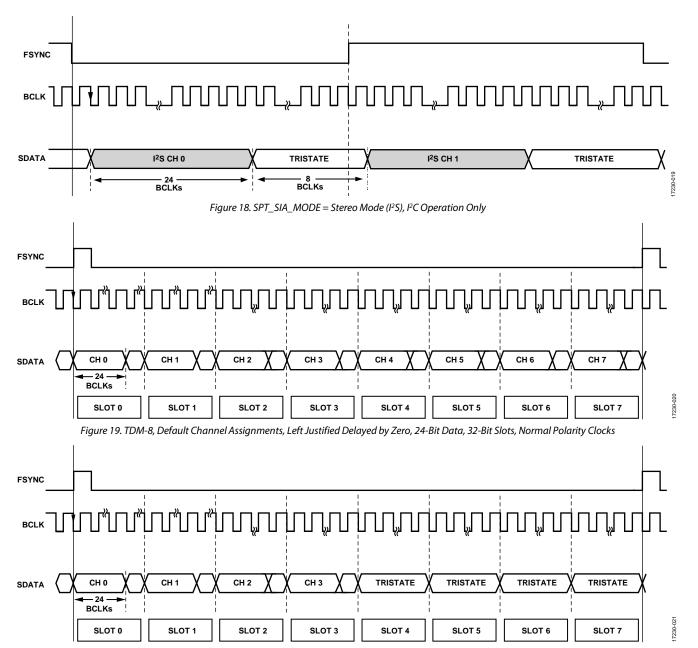

The SPT\_CTRL1 register, SPT\_SAI\_MODE bit (Bit 0) sets the serial port audio interface mode. The two modes are stereo and TDM. The primary difference between these two modes is the format of the frame sync clock that is expected and the polarity of the active edge of the clock.

With the SPT\_SAI\_MODE bit set to 0, and the SPT\_LRCLK\_POL bit (Bit 1, Register SPT\_CTRL2) set to 0, the serial port is in stereo mode with the clock polarity set to normal. In this mode, only two channels of data are expected to be sent. The frame starts with the falling edge of the frame sync, and the expected duty cycle is 50% high and 50% low. Channel 0 sends out its data when the clock is low, and as soon as the frame sync goes high, the data from Channel 0 is stopped, and Channel 1 begins sending. Both edges of the frame sync clock are used. If the duty cycle is not 50/50, there may be errors in the resulting data. In this mode of operation, the ADAU7118 does not expect 32-bit clock transitions for each channel. All bit clock to frame sync ratios are supported.

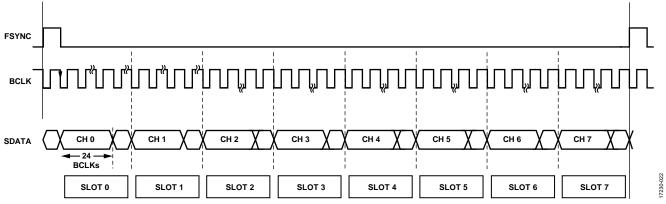

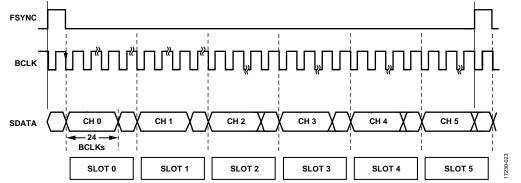

With the SPT\_SAI\_MODE bit set to 1, and the SPT\_LRCLK\_POL bit set to 0, the serial port is in TDM mode with the clock polarity set to normal. In this mode, there can be as few as a single channel transmitted or as many as 8 channels spread out across 16 data slots of a TDM-16 format.

The ADAU7118 can support six different bit clock rates of  $64\times$ ,  $128\times$ ,  $192\times$ ,  $256\times$ ,  $384\times$ , or  $512\times$  the output sampling rate. These bit clock rates are combined with the three different TDM slot sizes of 16-bit, 24-bit, or 32-bit slots, selected in the SPT\_CTRL1 register,

Bits[5:4] (SPT\_SLOT\_WIDTH), to result in 18 combinations of TDM formats that are supported. Note that some of these formats do not have an even number of full width slots (see Table 12).

Note that as soon as the next frame sync edge is detected, the ADAU7118 restarts from Slot 0, and any data in the previous frame that was never reached is lost. This process is how to achieve unusual TDM formats like TDM-5 or TDM-10. In addition, only TDM-16 or less is supported for placing data into a TDM slot. Data cannot be placed into slots above 16. The ADAU7118 can be configured to tristate all unused TDM slots, which includes all the slots above the first 16 slots for modes that have more than 16 slots.

In TDM mode, the frame sync is expected to be a positive going pulse that is at least one bit clock period wide. The falling edge is not important and is not looked at as long as it is low long enough to meet the timing specification read as a low before going back high. The frame starts with the rising edge of this pulse. The data is clocked out according to the slot width and data format specified in the SPT\_CTRL1 register, Register 0x07. The ADAU7118 continues to send data until all active channels are sent and then the device waits for the next frame sync clock edge to start sending the next set of frame samples. If TDM-16 is used and the ADAU7118 is set to output Channel 0 to Channel 7 into Slot 0 to Slot 7, the ADAU7118 can tristate for the remainder of the frame, allowing another ADAU7118 to output its 8 channels on to Slot 8 to Slot 15. These slots do not have to be consecutive. The two devices may interleave their respective data if properly set up to do this. The serial port can be set up to only drive when there is data to drive into a data slot. If one or more of the eight channels is not used, the channel can be assigned to drive a slot or tristate during that data slot in the TDM data stream, which is done using Bit 0 in the SPT\_Cx registers.

The SPT\_LRCLK\_POL bit, left/right clock polarity, can be set to 1 and the bit inverts the expected frame clock. In stereo mode with the SPT\_LRCLK\_POL bit set to 1, Channel 0 is sent out when the frame sync is high so the start of the frame is a low to high transition.

In TDM mode, with the SPT\_LRCLK\_POL bit set to 1, the expected frame sync pulse is negative going so that the frame starts with the high to low transition.

The SPT\_DATA\_FORMAT bits (Bits[3:1]) in the SPT\_CTRL1 register allow for the justification of the data within the 32-bit data slot. The left justified mode, delayed by one bit clock period, and the right justified modes for 24-bit, 20-bit, and 16-bit data word sizes are all supported.

Table 12. Number of Slots in Supported TDM Bit Clock Rates vs. Slot Size Setting

|                      | SPT_CTRL1, Bits[5:4] |                   |                   |  |  |

|----------------------|----------------------|-------------------|-------------------|--|--|

| Bit Clock Rate       | 0b01, 16-Bit Slot    | 0b10, 24-Bit Slot | 0b00, 32-Bit Slot |  |  |

| 64 × f <sub>s</sub>  | 4                    | 21                | 2                 |  |  |

| $128 \times f_S$     | 8                    | 5 <sup>1</sup>    | 4                 |  |  |

| $192 \times f_S$     | 12                   | 8                 | 6                 |  |  |

| $256 \times f_s$     | 16                   | 10 <sup>1</sup>   | 8                 |  |  |

| $384 \times f_S$     | 24                   | 16                | 12                |  |  |

| 512 × f <sub>s</sub> | 32                   | 21 <sup>1</sup>   | 16                |  |  |

<sup>&</sup>lt;sup>1</sup> This combination produces a partial final TDM slot that is not included in the number of slots. The data in that final slot is invalid. The number of slots shown in the table are the full width slots.

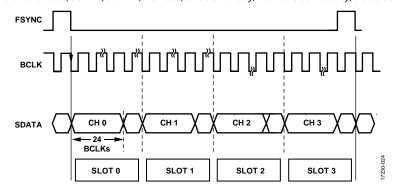

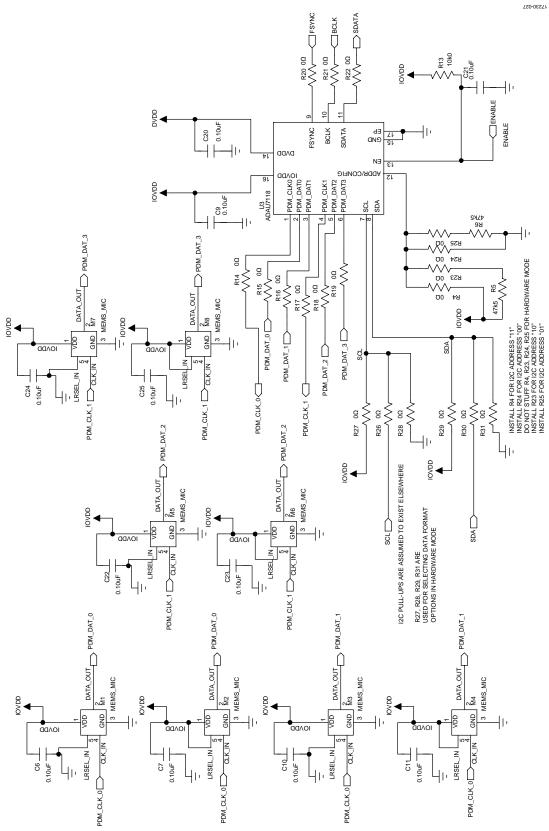

Figure 20. TDM-8, Left Justified Zero BCLK Delay, Only Channel 0 to Channel 3 Enabled

$Figure~21.~TDM-8~Hardware~Mode,~SCL=1,~SDA=0,~l^2C~Mode,~One~BCLK~Delay,~Normal~Clock~Polarity,~Default~Channel~Assignments$

Figure 22. TDM-6, Hardware Mode, SCL = 0, SDA = x,  $f^{C}$  Mode, One BCLK Delay, Normal Clock Polarity, Default Channel Assignments

Figure 23. TDM-4, Hardware Mode, SCL = 1, SDA = 1, I<sup>2</sup>C Mode, One BCLK Delay, Normal Clock Polarity, Default Channel Assignments

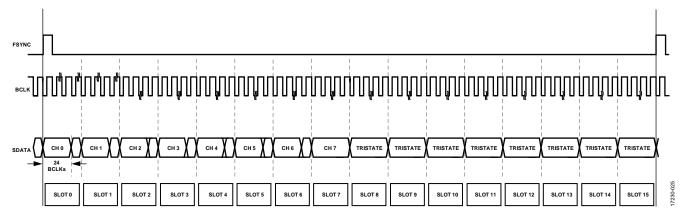

Figure 24. TDM-16, Default Channel Assignments, Left Justified Zero BCLK Delay, Normal Clock Polarity

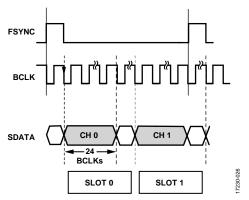

Figure 25. TDM-2, I<sup>2</sup>C Mode, One BCLK Delay, Normal Clock Polarity, Default Channel Assignments

# I<sup>2</sup>C CONTROL INTERFACE