# WM8255

## Single Channel 16-bit CIS/CCD AFE with RGB LED Current Drive

## DESCRIPTION

The WM8255 is a 16-bit analogue front end/digitiser IC which processes and digitises the analogue output signals from CCD sensors or Contact Image Sensors (CIS) at pixel sample rates of up to 12 MSPS.

The device includes a complete signal processing channel containing Reset Level Clamping, Correlated Double Sampling, Programmable Gain and Offset adjust functions. Internal multiplexers allow fast switching of offset and gain for line-by-line colour processing. The output from this channel is time multiplexed into a high-speed 16-bit Analogue to Digital Converter. The digital output data is available in a 2 bit or 4-bit wide multiplexed format.

An internal 4-bit DAC is supplied for internal reference level generation. This may be used during CDS to reference CIS signals or during Reset Level Clamping to clamp CCD signals. An external reference level may also be supplied. ADC references are generated internally, ensuring optimum performance from the device.

The device includes an RGB LED current drive using current and PWM functionality to control the operation of sensor LEDs.

The device typically uses an analogue supply voltage of 5.75V and a digital interface supply of 3.3V.

## FEATURES

- 16-bit ADC

- 12 MSPS conversion rate

- Low power 250 mW typical

- 5.75V and 3.3V supply operation

- Single channel operation

- Correlated double sampling

- Programmable gain (8-bit resolution)

- Programmable offset adjust (8-bit resolution)

- Programmable clamp voltage

- RGB LED current drive using current and PWM

- 2-bit or 4-bit wide multiplexed data output format

- Internally generated voltage references

- 28-lead QFN package

- 3 wire serial control interface

## APPLICATIONS

- Flatbed and sheetfeed scanners

- USB compatible scanners

- Multi-function peripherals

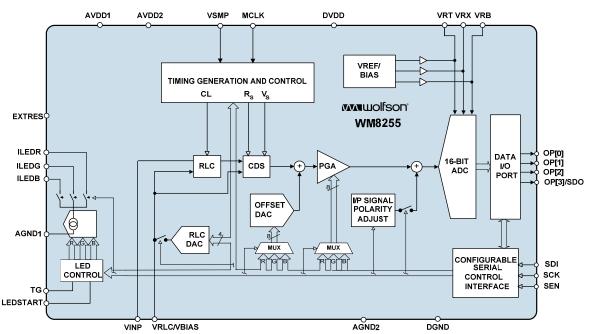

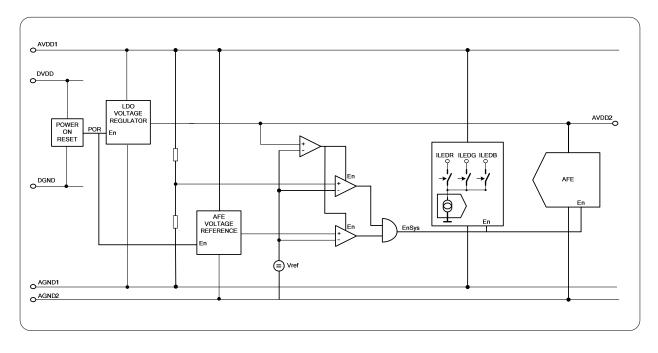

## **BLOCK DIAGRAM**

## TABLE OF CONTENTS

| DESCRIPTION                                                                  | 1    |

|------------------------------------------------------------------------------|------|

| FEATURES                                                                     | 1    |

| APPLICATIONS                                                                 | 1    |

| BLOCK DIAGRAM                                                                |      |

| TABLE OF CONTENTS                                                            |      |

| PIN CONFIGURATION                                                            |      |

| ORDERING INFORMATION                                                         |      |

|                                                                              |      |

| PIN DESCRIPTION                                                              |      |

| ABSOLUTE MAXIMUM RATINGS                                                     |      |

| RECOMMENDED OPERATING CONDITIONS                                             |      |

| THERMAL PERFORMANCE<br>ELECTRICAL CHARACTERISTICS                            | 6    |

| ELECTRICAL CHARACTERISTICS                                                   | 7    |

| INPUT VIDEO SAMPLING                                                         | 10   |

| OUTPUT DATA TIMING                                                           | 10   |

| SERIAL INTERFACE                                                             |      |

| PWM TIMING                                                                   |      |

| DEVICE DESCRIPTION                                                           | . 13 |

| INTRODUCTION                                                                 |      |

| INPUT SAMPLING                                                               | 13   |

| RESET LEVEL CLAMPING (RLC)                                                   | 13   |

| CDS/NON-CDS PROCESSING                                                       |      |

| OFFSET ADJUST AND PROGRAMMABLE GAIN                                          | -    |

| ADC INPUT BLACK LEVEL ADJUST                                                 |      |

| OVERALL SIGNAL FLOW SUMMARY                                                  |      |

| CALCULATING OUTPUT FOR ANY GIVEN INPUT                                       |      |

|                                                                              |      |

|                                                                              |      |

| LED CURRENT DRIVE SEQUENCE SYNCHRONISATION AND PROGRESSION                   |      |

| LED CURRENT DRIVE INTENSITY CONTROL<br>LED CURRENT DRIVE CURRENT PWM CONTROL |      |

| LED CURRENT DRIVE CURRENT PWM CONTROL                                        |      |

| CURRENT ACCURACY AND ABSOLUTE MAXIMUM CURRENT LIMIT                          |      |

| LED CONTROL WORKED EXAMPLE                                                   | 30   |

| CONTROL WORKED EXAMPLE                                                       |      |

| TIMING REQUIREMENTS                                                          |      |

| PROGRAMMABLE VSMP DETECT CIRCUIT                                             |      |

| REFERENCES                                                                   |      |

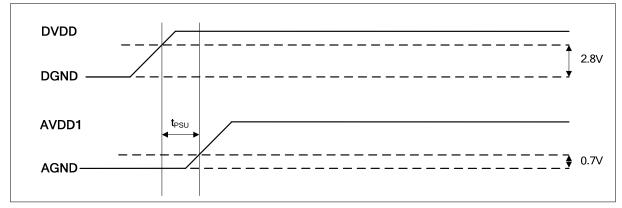

| POWER SUPPLY                                                                 |      |

| POWER MANAGEMENT                                                             |      |

| POWER ON SEQUENCE                                                            |      |

| OPERATING MODES                                                              |      |

| OPERATING MODE TIMING DIAGRAMS                                               |      |

| DEVICE REVISION CODES                                                        |      |

| DEVICE CONFIGURATION                                                         | . 40 |

| REGISTER MAP                                                                 |      |

| EXTENDED PAGE REGISTERS                                                      |      |

| REGISTER MAP DESCRIPTION                                                     |      |

| EXTENDED PAGE REGISTER MAP DESCRIPTION                                       |      |

| RECOMMENDED EXTERNAL COMPONENTS                                              |      |

|                                                                              |      |

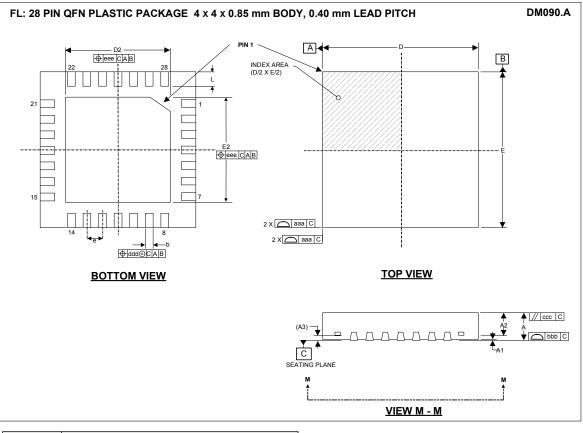

| PACKAGE DIMENSIONS | 47 |

|--------------------|----|

| QFN 5 X 5 X 0.85MM |    |

| QFN 4 X 4 X 0.85MM |    |

| IMPORTANT NOTICE   |    |

| ADDRESS:           | -  |

| REVISION HISTORY   |    |

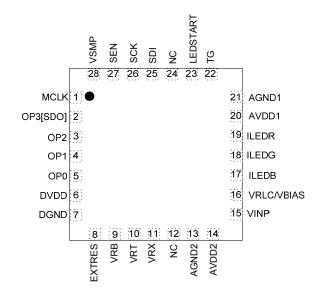

## **PIN CONFIGURATION**

## **ORDERING INFORMATION**

| DEVICE         | TEMPERATURE<br>RANGE | PACKAGE                  | MOISTURE<br>SENSITIVITY LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|----------------|----------------------|--------------------------|-------------------------------|-------------------------------|

|                |                      | 4x4x0.85mm               |                               |                               |

| WM8255BGEFL/V  | 0 to 85°C            | 28-lead QFN              | MSL3                          | 260°C                         |

|                |                      | (Pb-free)                |                               |                               |

|                |                      | 4x4x0.85mm               |                               |                               |

| WM8255BGEFL/RV | 0 to 85°C            | 28-lead QFN              | MSL3                          | 260°C                         |

|                |                      | (Pb-free, tape and reel) |                               |                               |

Note:

Reel quantity = 3,500

## **PIN DESCRIPTION**

| <b>PIN NO</b> | NAME       | TYPE            | DESCRIPTION                                                                                |                                                                              |                      |                      |  |  |

|---------------|------------|-----------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------|----------------------|--|--|

| 1             | MCLK       | Digital input   |                                                                                            | lock is applied at N tim<br>reafter depending on i                           |                      |                      |  |  |

|               |            |                 | Digital multiplexed of                                                                     | utput data bus.                                                              |                      |                      |  |  |

|               |            |                 |                                                                                            | 15:d0) is available in a<br>output is also available<br>heet on page 18.     |                      |                      |  |  |

|               |            |                 | Α                                                                                          | В                                                                            | С                    | D                    |  |  |

| 2             | OP[3]/SDO  | Digital output  | d15                                                                                        | d11                                                                          | d7                   | d3                   |  |  |

| 3             | OP[2]      | Digital output  | d14                                                                                        | d10                                                                          | d6                   | d2                   |  |  |

| 4             | OP[1]      | Digital output  | d13                                                                                        | d9                                                                           | d5                   | d1                   |  |  |

| 5             | OP[0]      | Digital output  | d12                                                                                        | d8                                                                           | d4                   | d0                   |  |  |

|               |            |                 | address bit 4=1 and                                                                        | [3]/SDO may be used<br>SEN has been pulsed<br>section for further deta       | high. See Serial Int |                      |  |  |

| 6             | DVDD       | Supply          | Digital supply (3.3V)                                                                      |                                                                              |                      |                      |  |  |

| 7             | DGND       | Supply          | Digital ground (0V).                                                                       |                                                                              |                      |                      |  |  |

| 8             | EXTRES     | Analogue input  | External resistor cor<br>ground via a suitable                                             |                                                                              | ute current control. | Must be connected to |  |  |

| 9             | VRB        | Analogue output | Lower reference vol<br>This pin must be cor                                                | tage.<br>nnected to AGND via a                                               | a decoupling capacit | or.                  |  |  |

| 10            | VRT        | Analogue output | Upper reference voltage.<br>This pin must be connected to AGND via a decoupling capacitor. |                                                                              |                      |                      |  |  |

| 11            | VRX        | Analogue output | Input return bias vol                                                                      | tage                                                                         |                      |                      |  |  |

|               |            |                 | This pin must be cor                                                                       | nnected to AGND via a                                                        | a decoupling capacit | tor.                 |  |  |

| 12            | NC         | No Connect      | Not Connected.                                                                             |                                                                              |                      |                      |  |  |

| 13            | AGND2      | Supply          | Analogue ground pir                                                                        | ר (0V)                                                                       |                      |                      |  |  |

| 14            | AVDD2      | Supply          |                                                                                            | 3V) Not required to be<br>r must be connected to                             |                      | being used. A        |  |  |

| 15            | VINP       | Analogue input  | Video input.                                                                               |                                                                              |                      |                      |  |  |

| 16            | VRLC/VBIAS | Analogue I/O    | This pin would typica                                                                      | e output voltage for RL<br>ally be connected to A<br>ally driven if programn | GND via a decoupli   |                      |  |  |

| 17            | ILEDB      | Analogue input  | Blue LED pin                                                                               |                                                                              |                      |                      |  |  |

| 18            | ILEDG      | Analogue input  | Green LED pin                                                                              |                                                                              |                      |                      |  |  |

| 19            | ILEDR      | Analogue input  | Red LED pin                                                                                |                                                                              |                      |                      |  |  |

| 20            | AVDD1      | Supply          | Analogue Supply (5.                                                                        | 75V)                                                                         |                      |                      |  |  |

| 21            | AGND1      | Supply          | Analogue ground (0)                                                                        | V).                                                                          |                      |                      |  |  |

| 22            | TG         | Digital input   | Line synchronisation                                                                       |                                                                              |                      |                      |  |  |

| 23            | LEDSTART   | Digital input   | LED start pulse                                                                            |                                                                              |                      |                      |  |  |

| 24            | NC         | No Connect      | Not Connected.                                                                             |                                                                              |                      |                      |  |  |

| 25            | SDI        | Digital input   | Serial data input.                                                                         |                                                                              |                      |                      |  |  |

| 26            | SCK        | Digital input   | Serial clock                                                                               |                                                                              |                      |                      |  |  |

| 27            | SEN        | Digital input   | Enables the serial in                                                                      | terface when high.                                                           |                      |                      |  |  |

| 28            | VSMP       | Digital input   | Video sample synch                                                                         | ronisation pulse.                                                            |                      |                      |  |  |

## ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

The WM8255 has been classified as MSL1, which has an unlimited floor life at  $<30^{\circ}$ C / 85% Relative Humidity and therefore will not be supplied in moisture barrier bags.

| CONDITION                                            | MIN        | MAX         |

|------------------------------------------------------|------------|-------------|

| Analogue supply voltage: AVDD1                       | GND - 0.3V | GND + 7V    |

| Analogue supply voltage: AVDD2                       | GND - 0.3V | GND + 4.2V  |

| Digital core supply and I/O voltage: DVDD            | GND - 0.3V | GND + 4.2V  |

| Digital ground: DGND                                 | GND - 0.3V | GND + 0.3V  |

| Analogue grounds AGND                                | GND - 0.3V | GND + 0.3V  |

| Digital inputs, digital outputs and digital I/O pins | GND - 0.3V | DVDD + 0.3V |

| Analogue input VINP                                  | GND - 0.3V | AVDD + 0.3V |

| Other pins                                           | GND - 0.3V | AVDD + 0.3V |

| Operating temperature range: T <sub>A</sub>          | 0°C        | +85°C       |

Notes:

- 1. GND denotes the voltage of any ground pin.

- 2. AGND and DGND pins are intended to be operated at the same potential. Differential voltages between these pins will degrade performance.

## **RECOMMENDED OPERATING CONDITIONS**

| CONDITION                            | SYMBOL         | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------|----------------|------|------|------|-------|

| Operating temperature range          | T <sub>A</sub> | 0    |      | 85   | °C    |

| Analogue supply voltage              | AVDD1          | 4.75 | 5.75 | 6.0  | V     |

| Analogue supply voltage <sup>1</sup> | AVDD2          | 2.97 | 3.3  | 3.63 | V     |

| Digital Core and I/O supply voltage  | DVDD           | 2.97 | 3.3  | 3.63 | V     |

#### Notes

- 1. AVDD2 supply not required if using AVDD1. AVDD2 would require connection to ground via a capacitor in that situation.

- 2. If AVDD2 is being used, both AVDD2 and DVDD should be operated at the same potential.

## THERMAL PERFORMANCE

| PARAMETER                                                     | SYMBOL                | TEST CONDITIONS             | MIN | TYP   | MAX | UNIT |

|---------------------------------------------------------------|-----------------------|-----------------------------|-----|-------|-----|------|

| Performance                                                   |                       |                             |     |       |     |      |

| Thermal resistance – junction to case (5x5x0.9mm package)     | $R_{	extsf{	heta}JC}$ |                             |     | 10.27 |     | °C/W |

| Thermal resistance – junction to ambient (5x5x0.9mm package)  | $R_{	extsf{	heta}JA}$ | T <sub>ambient</sub> = 25°C |     | 29.45 |     | °C/W |

| Thermal resistance – junction to ambient (4x4x0.85mm package) | $R_{	extsf{	heta}JA}$ |                             |     | 24.05 |     | °C/W |

#### Notes:

1. Figures given are for package mounted on 4-layer FR4 according to JESD51-5 and JESD51-7.

## **ELECTRICAL CHARACTERISTICS**

### **Test Conditions**

AVDD1 = 5.75V, DVDD = 3.3V, AGND = DGND = AVDD2 = 0V,  $T_A = 25^{\circ}C$ , MCLK = 24MHz, mode 1 unless otherwise stated.

| PARAMETER                            | SYMBOL               | TEST<br>CONDITIONS                | MIN       | TYP  | MAX   | UNIT    |

|--------------------------------------|----------------------|-----------------------------------|-----------|------|-------|---------|

| Overall System Specification (incl   | uding 16-bit A       | DC, PGA, Offset and CDS f         | unctions) |      |       | 1       |

| Full-scale input voltage range       |                      | Max Gain                          |           | 0.24 |       | Vp-p    |

| (see Note 1)                         |                      | Min Gain                          |           | 2.56 |       | Vp-p    |

| Input signal limits (see Note 2)     | V <sub>IN</sub>      |                                   | 0         |      | AVDD1 | V       |

| Full-scale transition error          |                      | Gain = 0dB;<br>PGA[7:0] = 07(hex) | -50       | 10   | +50   | mV      |

| Zero-scale transition error          |                      | Gain = 0dB;<br>PGA[7:0] = 07(hex) | -50       | 10   | +50   | mV      |

| Differential non-linearity           | DNL                  |                                   |           | 1.5  |       | LSB     |

| Integral non-linearity               | INL                  |                                   |           | 25   |       | LSB     |

| Input referred noise                 |                      |                                   |           | 9    |       | LSB rms |

| References                           |                      |                                   |           |      |       |         |

| Upper reference voltage              | VRT                  |                                   |           | 2.05 |       | V       |

| Lower reference voltage              | VRB                  |                                   |           | 1.05 |       | V       |

| Diff. reference voltage (VRT-VRB)    | V <sub>RTB</sub>     |                                   |           | 1.0  |       | V       |

| Output resistance VRT, VRB, VRX      |                      |                                   |           | 1    |       | Ω       |

| VRLC/Reset-Level Clamp (RLC)         |                      |                                   | •         |      |       |         |

| RLC switching impedance              |                      |                                   | 10        | 50   | 100   | Ω       |

| VRLC short-circuit current           |                      |                                   |           | 8    |       | mA      |

| VRLC output resistance               |                      |                                   |           | 2    |       | Ω       |

| VRLC Hi-Z leakage current            |                      | VRLC = 0 to AVDD1                 |           |      | 1     | μA      |

| RLCDAC resolution                    |                      |                                   |           | 4    |       | bits    |

| RLCDAC step size                     | V <sub>RLCSTEP</sub> |                                   |           | 0.24 |       | V/step  |

| RLCDAC output voltage at code 0(hex) | V <sub>RLCBOT</sub>  |                                   |           | 0.3  |       | V       |

| RLCDAC output voltage at code F(hex) | V <sub>RLCTOP</sub>  |                                   |           | 3.9  |       | V       |

| Offset DAC, Monotonicity Guarant     | teed                 |                                   | •         | •    |       | •       |

| Resolution                           |                      |                                   |           | 8    |       | bits    |

| Differential non-linearity           | DNL                  |                                   |           | 0.6  |       | LSB     |

| Integral non-linearity               | INL                  |                                   |           | 2    |       | LSB     |

| Step size                            |                      |                                   |           | 1.96 |       | mV/step |

| Output voltage                       |                      | Code 00(hex)                      | -220      | -250 | -280  | mV      |

|                                      |                      | Code FF(hex)                      | +220      | +250 | +280  | mV      |

Notes:

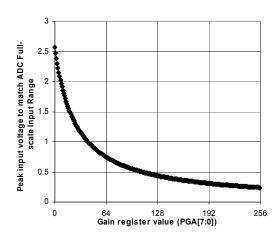

1. **Full-scale input voltage** denotes the peak input signal amplitude that can be gained to match the ADC input range.

2. Input signal limits are the limits within which the full-scale input voltage signal must lie.

## **Test Conditions**

AVDD1 = 5.75V, DVDD = 3.3V, AGND = DGND = AVDD2 = 0V,  $T_A$  = 25°C, MCLK = 24MHz unless otherwise stated.

| PARAMETER                                         | SYMBOL             | TEST<br>CONDITIONS    | MIN        | ТҮР                                  | MAX        | UNIT |

|---------------------------------------------------|--------------------|-----------------------|------------|--------------------------------------|------------|------|

| Programmable Gain Amplifier                       |                    |                       | ·          |                                      | •          |      |

| Resolution                                        |                    |                       |            | 8                                    |            | bits |

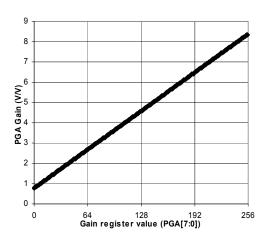

| Gain equation                                     |                    |                       | 0.7        | $78 + \frac{PGA[7:0] \times 7}{255}$ | 57         | V/V  |

| Max gain                                          | G <sub>MAX</sub>   |                       | 8          | 8.35                                 | 8.7        | V/V  |

| Min gain                                          | G <sub>MIN</sub>   |                       | 0.72       | 0.78                                 | 0.82       | V/V  |

| Internal channel offset                           | V <sub>OFF</sub>   |                       |            | 10                                   |            | mV   |

| Analogue to Digital Converter                     | <u>.</u>           |                       |            |                                      |            |      |

| Resolution                                        |                    |                       |            | 16                                   |            | bits |

| Maximum Speed                                     |                    |                       |            |                                      | 12         | MSPS |

| Full-scale input range                            | V <sub>FS</sub>    |                       |            | 2.0                                  |            | V    |

| (2*(VRT-VRB))                                     |                    |                       |            |                                      |            |      |

| DIGITAL SPECIFICATIONS                            |                    |                       |            |                                      |            |      |

| Digital Inputs                                    |                    |                       |            |                                      |            |      |

| High level input voltage                          | VIH                |                       | 0.7 * DVDD |                                      |            | V    |

| Low level input voltage                           | VIL                |                       |            |                                      | 0.2 * DVDD | V    |

| High level input current                          | I <sub>IH</sub>    |                       |            |                                      | 1          | μA   |

| Low level input current                           | IIL                |                       |            |                                      | 1          | μA   |

| Input capacitance                                 | Cı                 |                       |            | 5                                    |            | pF   |

| Digital Outputs                                   | <u>.</u>           |                       |            |                                      |            |      |

| High level output voltage                         | V <sub>OH</sub>    | I <sub>OH</sub> = 1mA | DVDD - 0.5 |                                      |            | V    |

| Low level output voltage                          | V <sub>OL</sub>    | I <sub>OL</sub> = 1mA |            |                                      | 0.5        | V    |

| Supply Currents (LED Current D                    | AC switched o      | ff)                   |            |                                      |            |      |

| Total supply current – active                     |                    |                       |            | 42.5                                 |            | mA   |

| Total analogue AVDD, supply current – active      | I <sub>AVDD</sub>  |                       |            | 39                                   |            | mA   |

| Total digital core, DVDD, supply current – active | I <sub>DVDD1</sub> |                       |            | 3.5                                  |            | mA   |

| Supply current – full power down mode             |                    |                       |            | 500                                  |            | μA   |

Notes:

1. Digital I/O supply current depends on the capacitive load attached to the pin. The Digital I/O supply current is measured with approximately 50pF attached to the pin.

| PARAMETER                                        | SYMBOL         | TEST<br>CONDITIONS      | MIN             | ТҮР | MAX     | UNIT |

|--------------------------------------------------|----------------|-------------------------|-----------------|-----|---------|------|

| EXTERNAL LED CURRENT DRIV                        | E              |                         |                 |     |         |      |

| Coarse Absolute LED Current Dr                   | ive Range Adjı | ıst                     |                 |     |         |      |

| E                                                | EXTRES = 13K7  | ohm +/- 1% over process | and temperature | -   |         |      |

| Coarse LED Current Full Scale                    | ILEDCRE0       | LEDIRNG = 00            | 25              |     | 32      | mA   |

| Range with External Reference                    | ILEDCRE1       | LEDIRNG = 01            | 30              |     | 42.25   | mA   |

| including absolute and<br>temperature tolerances | ILEDCRE2       | LEDIRNG = 10            | 40              |     | 56.5    | mA   |

|                                                  | ILEDCRE3       | LEDIRNG = 11            | 50              |     | 68      | mA   |

|                                                  |                |                         |                 |     |         |      |

| Coarse LED Current Maximum                       | ILEDMAX        | LEDIMAX = 0             | 28              |     | 45      | mA   |

| Limit Range                                      | ILEDMAX        | LEDIMAX = 1             | 35              |     | 53      | mA   |

|                                                  |                |                         |                 |     |         |      |

| FINE LED ABSOLUTE CURRENT                        | DRIVE          |                         |                 |     |         |      |

| Resolution                                       | ILEDFRes       |                         |                 | 8   |         | bits |

| Range                                            | ILEDFRan       |                         | ILEDCRXX        |     |         |      |

| Zero Current                                     |                |                         |                 |     | 0       | mA   |

| Differential non-linearity                       | ILEDFDNL       | No missing codes        | -1              |     | 1.15    | LSB  |

| Integral non-linearity                           | ILEFINL        |                         |                 |     | 1       | LSB  |

| Compliance Voltage ILEDR                         | ILEDRVC        | ILED=50mA               | 0.75+           |     | AVDD1 - | V    |

|                                                  |                |                         | AGND            |     | 0.5V    |      |

| Compliance Voltage ILEDG and                     | ILEDGBVC       | ILED=50mA               | 0.25+           |     | AVDD1 - | V    |

| ILEDB                                            |                |                         | AGND            |     | 0.5V    |      |

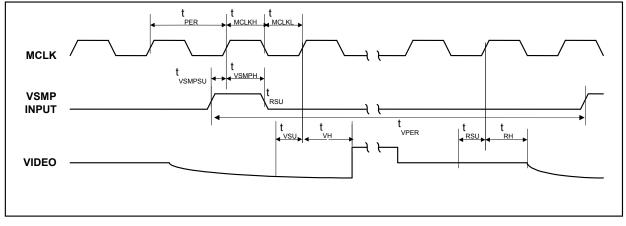

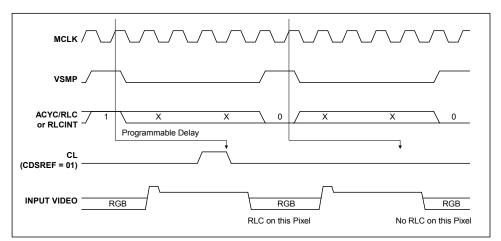

## **INPUT VIDEO SAMPLING**

### Figure 1 Input Video Timing

#### Note:

1. See Page 35 (Programmable VSMP Detect Circuit) for video sampling description.

#### **Test Conditions**

AVDD1 = 5.75V, DVDD = 3.3V, AGND = DGND = AVDD2 = 0V, T<sub>A</sub> = 25°C, MCLK = 24MHz unless otherwise stated.

| PARAMETER               | SYMBOL              | TEST CONDITIONS | MIN  | TYP | MAX | UNITS |

|-------------------------|---------------------|-----------------|------|-----|-----|-------|

| MCLK period             | t <sub>PER</sub>    |                 | 41.5 |     |     | ns    |

| MCLK high period        | t <sub>MCLKH</sub>  |                 | 25   |     |     | ns    |

| MCLK low period         | t <sub>MCLKL</sub>  |                 | 25   |     |     | ns    |

| VSMP period             | t <sub>VPER</sub>   |                 | 83   |     |     | ns    |

| VSMP set-up time        | t <sub>vsmpsu</sub> |                 | 6    |     |     | ns    |

| VSMP hold time          | t <sub>vsmph</sub>  |                 | 3    |     |     | ns    |

| Video level set-up time | t <sub>vsu</sub>    |                 | 10   |     |     | ns    |

| Video level hold time   | t <sub>vH</sub>     |                 | 3    |     |     | ns    |

| Reset level set-up time | t <sub>RSU</sub>    |                 | 10   |     |     | ns    |

| Reset level hold time   | t <sub>RH</sub>     |                 | 3    |     |     | ns    |

#### Notes:

1.  $t_{VSU}$  and  $t_{RSU}$  denote the set-up time required after the input video signal has settled.

2. Parameters are measured at 50% of the rising/falling edge.

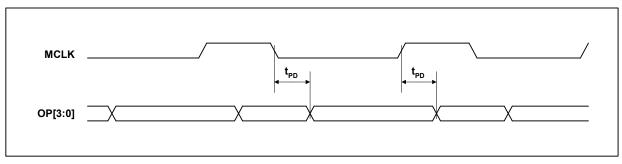

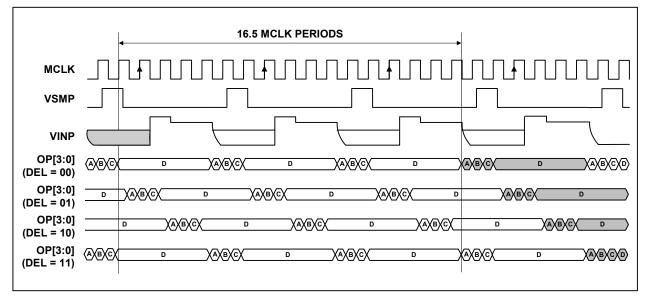

## OUTPUT DATA TIMING

### Figure 2 Output Data Timing

#### **Test Conditions**

AVDD1 = 5.75V, DVDD = 3.3V, AGND = DGND = AVDD2 = 0V, T<sub>A</sub> = 25°C, MCLK = 24MHz unless otherwise stated.

| PARAMETER                | SYMBOL          | TEST CONDITIONS                | MIN | TYP | MAX | UNITS |

|--------------------------|-----------------|--------------------------------|-----|-----|-----|-------|

| Output propagation delay | t <sub>PD</sub> | $I_{OH}$ = 1mA, $I_{OL}$ = 1mA | 3   | 8   | 15  | ns    |

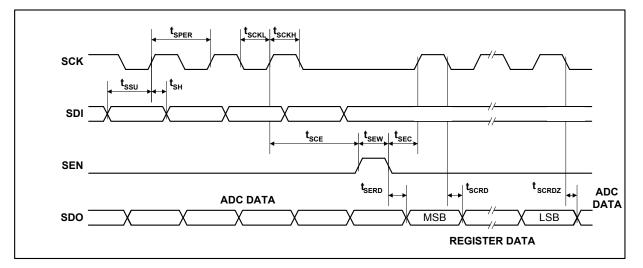

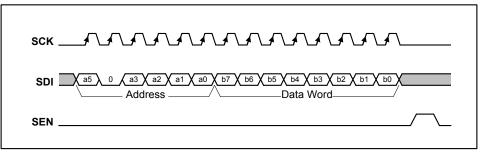

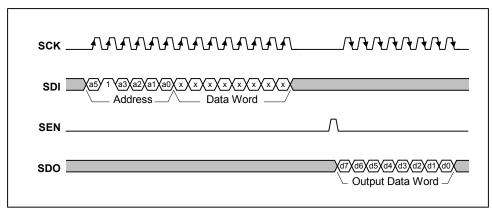

## SERIAL INTERFACE

### Figure 3 Serial Interface Timing

#### **Test Conditions**

AVDD1 = 5.75V, DVDD = 3.3V, AGND = DGND = AVDD2 = 0V,  $T_A = 25^{\circ}C$ , MCLK = 24MHz unless otherwise stated.

| PARAMETER                      | SYMBOL             | TEST CONDITIONS | MIN  | TYP | MAX | UNITS |

|--------------------------------|--------------------|-----------------|------|-----|-----|-------|

| SCK period                     | t <sub>SPER</sub>  |                 | 41.6 |     |     | ns    |

| SCK high                       | t <sub>scкн</sub>  |                 | 18.8 |     |     | ns    |

| SCK low                        | t <sub>scкL</sub>  |                 | 18.8 |     |     | ns    |

| SDI set-up time                | t <sub>ssu</sub>   |                 | 6    |     |     | ns    |

| SDI hold time                  | t <sub>sH</sub>    |                 | 6    |     |     | ns    |

| SCK to SEN set-up time         | t <sub>SCE</sub>   |                 | 12   |     |     | ns    |

| SEN to SCK set-up time         | t <sub>SEC</sub>   |                 | 12   |     |     | ns    |

| SEN pulse width                | t <sub>SEW</sub>   |                 | 25   |     |     | ns    |

| SEN low to SDO = Register data | t <sub>SERD</sub>  |                 |      |     | 30  | ns    |

| SCK low to SDO = Register data | t <sub>SCRD</sub>  |                 |      |     | 30  | ns    |

| SCK low to SDO = ADC data      | t <sub>scrdz</sub> |                 |      |     | 30  | ns    |

Note:

1. Parameters are measured at 50% of the rising/falling edge

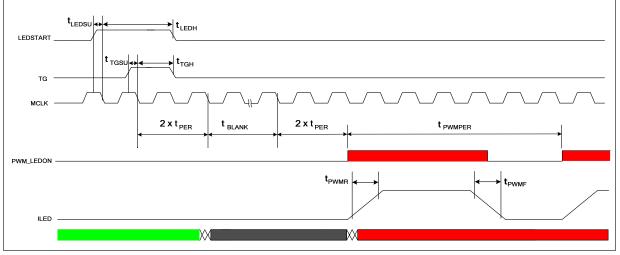

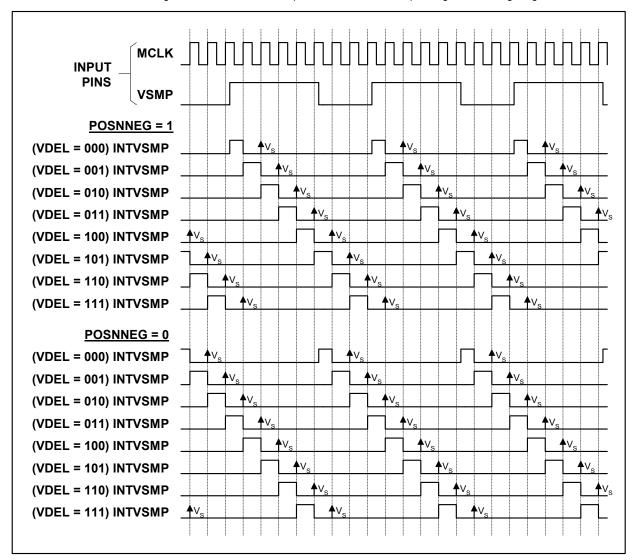

## **PWM TIMING**

Figure 4 PWM Timing

#### **Test Conditions**

AVDD1 = 5.75V, DVDD = 3.3V, AGND = DGND = AVDD2 = 0V, T<sub>A</sub> = 25°C, MCLK = 24MHz unless otherwise stated.

| PARAMETER                    | SYMBOL                               | TEST CONDITIONS | MIN                                   | TYP         | MAX                      | UNITS |

|------------------------------|--------------------------------------|-----------------|---------------------------------------|-------------|--------------------------|-------|

| PWM LED Current Drive Contro | 1                                    |                 |                                       |             |                          |       |

| PWM Period                   | t <sub>PWMPER</sub>                  |                 | (CLKDIV+1)                            | ns          |                          |       |

| PWM Duty Cycle               |                                      |                 | LEDPW                                 | -           |                          |       |

| PWM Period Resolution        |                                      |                 | (CL                                   | KDIV +1) *  | t <sub>PER</sub>         | ns    |

| PWM Period Range             |                                      |                 | (CLKDI                                | V +1) * 409 | 96 * t <sub>PER</sub>    | ns    |

| PWM Duty Cycle Resolution    |                                      |                 | (Cl                                   | -KDIV +1) * | t <sub>PER</sub>         | ns    |

| PWM Duty Cycle Range         |                                      |                 | (CLKDIV +1) * 4096 * t <sub>PER</sub> |             |                          | ns    |

| PWM Enable Coarse Adjust     | t <sub>PWMMaxCount</sub>             |                 | t <sub>PWMPER</sub> *1                |             | t <sub>PWMPER</sub> *128 | ns    |

| LEDSTART set-up time         | T <sub>LEDSU</sub>                   |                 | 6                                     |             |                          | ns    |

| LEDSTART hold time           | T <sub>LEDH</sub>                    |                 | 3                                     |             |                          | ns    |

| TG set-up time               | t <sub>TGSU</sub>                    |                 | 6                                     |             |                          | ns    |

| TG hold time                 | t <sub>TGH</sub>                     |                 | 3                                     |             |                          | ns    |

| PWM Rise / Fall Time         | t <sub>PWMR</sub> /t <sub>PWMF</sub> |                 | 1                                     |             | 5                        | us    |

| Minimum blank period         | t <sub>BLANK</sub>                   |                 | 25                                    |             |                          | us    |

#### Notes:

- 1. For LED Current Drive Description refer to Page 17.

- 2. The Blank period starts on the  $2^{nd}$  falling edge of MCLK after TG goes high.

- 3. CLKDIV, LEDPWMPER and LEDPWMDC are register settings. For further details see Table 10.

## DEVICE DESCRIPTION

### INTRODUCTION

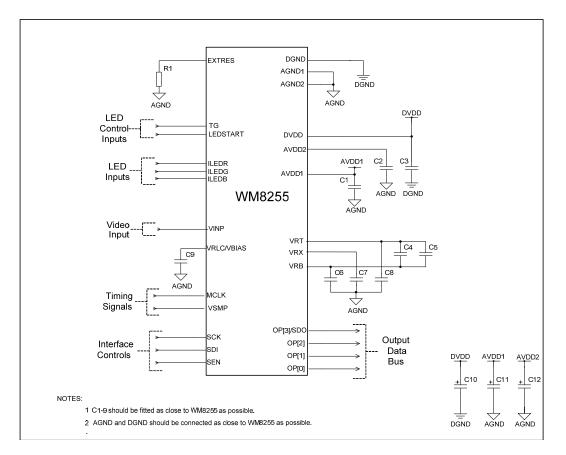

A block diagram of the device showing the signal path is presented on Page 1.

The WM8255 processes the sampled video signal on VINP with respect to the video-reset level or an internally/externally generated reference level through the analogue-processing channel.

This processing channel consists of an Input Sampling block with optional Reset Level Clamping (RLC) and Correlated Double Sampling (CDS), an 8-bit programmable offset DAC and an 8-bit Programmable Gain Amplifier (PGA).

The ADC then converts each resulting analogue signal to a 16-bit digital word. The digital output from the ADC is presented on a 4-bit wide bus.

On-chip control registers determine the configuration of the device, including the offsets and gains applied to each channel. These registers are programmable via a serial interface.

The device can control the brightness and timing of the Red, Green and Blue LEDs used in a CIS sensor. This is controlled via the serial control interface and external timing pins.

### **INPUT SAMPLING**

The WM8255 has a single analogue processing channel and ADC, which can be used in a flexible manner to process both monochrome and line-by-line colour inputs.

**Monochrome:** The selected input (VINP) is sampled, processed by the analogue channel, and converted by the ADC. The same offset DAC and PGA register values are always applied.

**Colour Line-by-Line:** VINP is sampled and processed by the analogue channel before being converted by the ADC. The gains and offset register values applied to the PGA and offset DAC can be switched between the independent Red, Green and Blue digital registers (e.g. Red  $\rightarrow$  Green $\rightarrow$  Blue  $\rightarrow$  Red...) at the start of each line in order to facilitate line-by-line colour operation. The INTM[1:0] bits determine which register contents are applied (see Table 1) to the PGA and offset DAC. By using the INTM[1:0] bits to select the desired register values only one register write is required at the start of each new colour line.

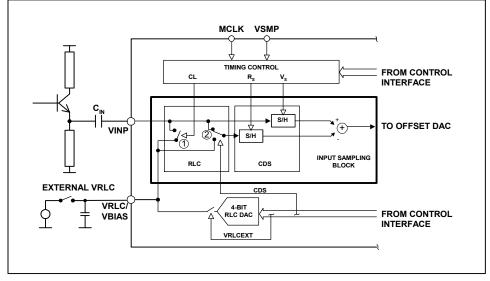

## **RESET LEVEL CLAMPING (RLC)**

To ensure that the signal applied to the WM8255 VINP pin lies within the valid input range (0V to AVDD) the CCD output signal is usually level shifted by coupling through a capacitor,  $C_{IN}$ . When active, the RLC circuit clamps the WM8255 side of this capacitor to a suitable voltage during the CCD reset period. The RLCINT register bit controls is used to activate the Reset Level Clamp circuit.

A typical input configuration is shown in Figure 5. The Timing Control Block generates a clamp pulse, CL, from MCLK and VSMP (when RLCINT is high). When CL is active the voltage on the WM8255 side of C<sub>IN</sub>, at VINP, is forced to the VRLC/VBIAS voltage (V<sub>VRLC</sub>) by switch 1. When the CL pulse turns off, the voltage at VINP initially remains at V<sub>VRLC</sub> but any subsequent variation in sensor voltage (from reset to video level) will couple through C<sub>IN</sub> to VINP.

RLC is compatible with both CDS and non-CDS operating modes, as selected by switch 2. Refer to the CDS/non-CDS Processing section.

Figure 5 Reset Level Clamping and CDS Circuitry

Reset Level Clamping is controlled by register bit RLCINT. Figure 6 illustrates the effect of the RLCINT bit for a typical CCD waveform, with CL applied during the reset period.

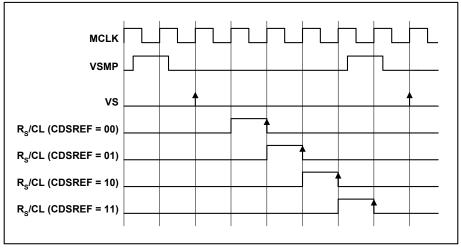

The RLCINT register bit is sampled on the positive edge of MCLK that occurs during each VSMP pulse. The sampled level, high (or low) controls the presence (or absence) of the internal CL pulse on the next reset level. The position of CL can be adjusted by using control bits CDSREF[1:0]

Figure 6 Relationship of RLCINT, MCLK and VSMP to Internal Clamp Pulse, CL

The VRLC/VBIAS pin can be driven internally by a 4-bit DAC (RLCDAC) by writing to control bits RLCV[3:0]. The RLCDAC range and step size may be increased by writing to control bit RLCDACRNG. Alternatively, the VRLC/VBIAS pin can be driven externally by writing to control bit VRLCEXT to disable the RLCDAC and then applying a d.c. voltage to the pin.

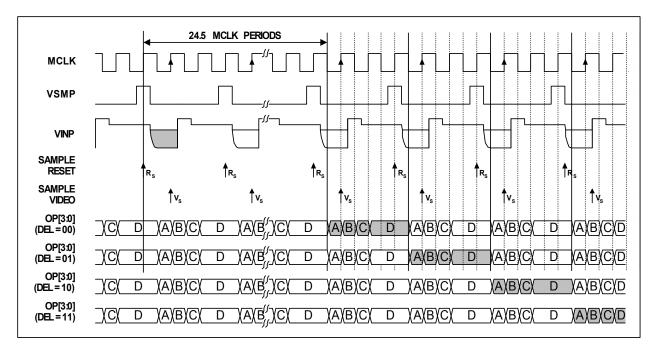

## **CDS/NON-CDS PROCESSING**

For CCD type input signals, the signal may be processed using CDS, which will remove pixel-by-pixel common mode noise. For CDS operation, the video level is processed with respect to the video reset level, regardless of whether RLC has been performed. To sample using CDS, control bit CDS must be set to 1 (default), this controls switch 2 (Figure 5) and causes the signal reference to come from the video reset level. The time at which the reset level is sampled, by clock  $R_s/CL$ , is adjustable by programming control bits CDSREF[1:0].

Figure 7 Reset Sample and Clamp Timing

For CIS type sensor signals, non-CDS processing is used. In this case, the video level is processed with respect to the voltage on pin VRLC/VBIAS, generated internally or externally as described above. The VRLC/VBIAS pin is sampled by  $R_s$  at the same time as  $V_s$  samples the video level in this mode.

## OFFSET ADJUST AND PROGRAMMABLE GAIN

The output from the CDS block is a differential signal, which is added to the output of an 8-bit Offset DAC to compensate for offsets and then amplified by an 8-bit PGA. The gain and offset can be set for each of three colours by writing to control bits DACx[7:0] and PGAx[7:0] (where x can be R, G or B).

In colour line-by-line mode the gain and offset coefficients that are applied to the PGA and offset DAC can be multiplexed by control of the INTM[1:0] bits as shown in Table 1.

| INTM[1:0] | DESCRIPTION                                                                               |

|-----------|-------------------------------------------------------------------------------------------|

| 00        | Red offset and gain registers are applied to offset DAC and PGA (DACR[7:0] and PGAR[7:0]) |

| 01        | Green offset and gain registers applied to offset DAC and PGA (DACG[7:0] and PGAG[7:0])   |

| 10        | Blue offset and gain registers applied to offset DAC and PGA (DACB[7:0] and PGAB[7:0])    |

| 11        | Reserved.                                                                                 |

### Table 1 Offset DAC and PGA Register Control

The gain characteristic of the WM8255 PGA is shown in Figure 8. Figure 9 shows the maximum input voltage (at VINP) that can be gained up to match the ADC full-scale input range (2.0V).

Figure 8 PGA Gain Characteristic

Figure 9 Peak Input Voltage to Match ADC Full-scale Range

## ADC INPUT BLACK LEVEL ADJUST

The output from the PGA should be offset to match the full-scale range of the ADC ( $V_{FS} = 2.0V$ ). For negative-going input video signals, a black level (zero differential) output from the PGA should be offset to the top of the ADC range by setting register bits PGAFS[1:0]=10. For positive going input signal the black level should be offset to the bottom of the ADC range by setting PGAFS[1:0]=11. Bipolar input video is accommodated by setting PGAFS[1:0]=00 or PGAFS[1:0]=01 (zero differential input voltage gives mid-range ADC output).

## **OVERALL SIGNAL FLOW SUMMARY**

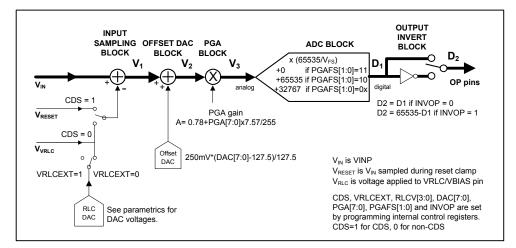

Figure 10 represents the processing of the video signal through the WM8255.

Figure 10 Overall Signal Flow

The **INPUT SAMPLING BLOCK** produces an effective input voltage  $V_1$ . For CDS, this is the difference between the input video level  $V_{IN}$  and the input reset level  $V_{RESET}$ . For non-CDS this is the difference between the input video level  $V_{IN}$  and the voltage on the VRLC/VBIAS pin,  $V_{VRLC}$ , optionally set via the RLC DAC.

The **OFFSET DAC BLOCK** then adds the amount of fine offset adjustment required to move the black level of the input signal towards 0V, producing  $V_2$ .

The **PGA BLOCK** then amplifies the white level of the input signal to maximise the ADC range, outputting voltage  $V_3$ .

The ADC BLOCK then converts the analogue signal, V<sub>3</sub>, to a 16-bit unsigned digital output, D<sub>1</sub>.

The digital output is then inverted, if required, through the OUTPUT INVERT BLOCK to produce D2.

### **CALCULATING OUTPUT FOR ANY GIVEN INPUT**

The following equations describe the processing of the video and reset level signals through the WM8255.

#### INPUT SAMPLING BLOCK: INPUT SAMPLING AND REFERENCING

If CDS = 1, (i.e. CDS operation) the previously sampled reset level,  $V_{\text{RESET}}$ , is subtracted from the input video.

$V_1$  =  $V_{IN} - V_{RESET}$  Eqn. 1

If CDS = 0, (non-CDS operation) the simultaneously sampled voltage on pin VRLC is subtracted instead.

$V_1$  =  $V_{IN} - V_{VRLC}$  Eqn. 2

If VRLCEXT = 1, V<sub>VRLC</sub> is an externally applied voltage on pin VRLC/VBIAS.

If VRLCEXT = 0,  $V_{VRLC}$  is the output from the internal RLC DAC.

$V_{VRLC}$  =  $(V_{RLCSTEP} * RLCV[3:0]) + V_{RLCBOT}$  Eqn. 3

$V_{\text{RLCSTEP}}$  is the step size of the RLC DAC and  $V_{\text{RLCBOT}}$  is the minimum output of the RLC DAC.

### OFFSET DAC BLOCK: OFFSET (BLACK-LEVEL) ADJUST

The resultant signal  $V_1$  is added to the Offset DAC output.

| V <sub>2</sub> | = | <b>V</b> <sub>1</sub> + {250mV * (DAC[7:0]-127.5) } / 127.5 | Eqn. 4 |

|----------------|---|-------------------------------------------------------------|--------|

|----------------|---|-------------------------------------------------------------|--------|

#### PGA NODE: GAIN ADJUST

The signal is then multiplied by the PGA gain,

| V <sub>3</sub> | = | <b>V</b> <sub>2</sub> * [0.78+(PGA[7:0]*7.57)/255] | Eqn. 5 |

|----------------|---|----------------------------------------------------|--------|

|----------------|---|----------------------------------------------------|--------|

### ADC BLOCK: ANALOGUE-DIGITAL CONVERSION

The analogue signal is then converted to a 16-bit unsigned number, with input range configured by PGAFS[1:0].

| $D_1[15:0] = INT\{ (V_3/V_{FS}) * 65535\} + 32767$        | PGAFS[1:0] = 00 or 01 | Eqn. 6 |

|-----------------------------------------------------------|-----------------------|--------|

| $D_1[15:0] = INT\{ (V_3/V_{FS}) * 65535 \}$               | PGAFS[1:0] = 11       | Eqn. 7 |

| $D_1[15:0] = INT\{ (V_3/V_{FS}) * 65535\} + 65535$        | PGAFS[1:0] = 10       | Eqn. 8 |

| where the ADC full coole range $V_{\rm c} = 2.0V_{\rm c}$ |                       |        |

where the ADC full-scale range,  $V_{FS}$  = 2.0V

if  $D_1[15:0] < 0$   $D_1[15:0] = 0$

if **D**<sub>1</sub>[15:0] > 65535 **D**<sub>1</sub>[15:0] = 65535

#### **OUTPUT INVERT BLOCK: POLARITY ADJUST**

The polarity of the digital output may be inverted by control bit INVOP.

| $D_2[15:0] = D_1[15:0]$ (INVOP =                                    | = 0)        | Eqn. 9  |

|---------------------------------------------------------------------|-------------|---------|

| <b>D</b> <sub>2</sub> [15:0] = 65535 - <b>D</b> <sub>1</sub> [15:0] | (INVOP = 1) | Eqn. 10 |

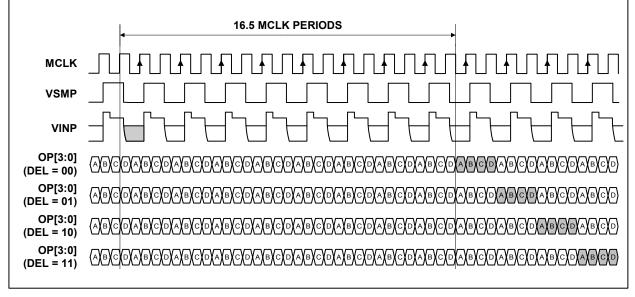

## **OUTPUT FORMATS**

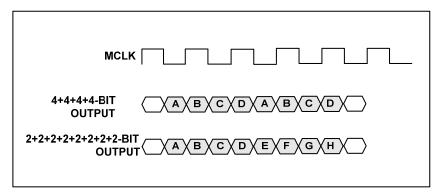

The digital data output from the ADC is available in a 4-bit wide multiplexed. Latency of valid output data with respect to VSMP is programmable by writing to control bits DEL[1:0]. The latency is shown in the Operating Mode Timing Diagrams section.

Figure 11 shows the output data formats for all modes. Table 2 summarises the output data obtained for each format.

Figure 11 Output Data Formats (4 bit - Modes 1 & 3, 2 bit - Mode 1 )

| OUTPUT FORMAT         | OUTPUT<br>PINS | OUTPUT                                                                                                             |

|-----------------------|----------------|--------------------------------------------------------------------------------------------------------------------|

| 4+4+4-bit<br>(nibble) | OP[3:0]        | A = d15, d14, d13, d12<br>B = d11, d10, d9, d8<br>C = d7, d6, d5, d4<br>D = d3, d2, d1, d0                         |

| 2+2+2+2+2+2+2-bit     | OP[1:0]        | A = d15, d14<br>B = d13, d12<br>C = d11, d10<br>D = d9, d8<br>E = d7, d6<br>F = d5, d4<br>G = d3, d2<br>H = d1, d0 |

Table 2 Details of Output Data Shown in Figure 11

## LED CURRENT DRIVE CONTROL

The WM8255 allows the user to control:

- the sequence of illumination

- the period of illumination

- the intensity of illumination

of the red, blue and green LEDs used to illuminate the image during a scan.

A sequence state machine is used to progress the sequence and control the duration of the LED selection. The progression of the sequence state machine is dependent on whether the WM8255 is in colour mode or monochromatic mode. The intensity of illumination is controlled on either control of the LED drive current or pulsing of the LED driving current.

#### LED CURRENT DRIVE SEQUENCE CONTROL

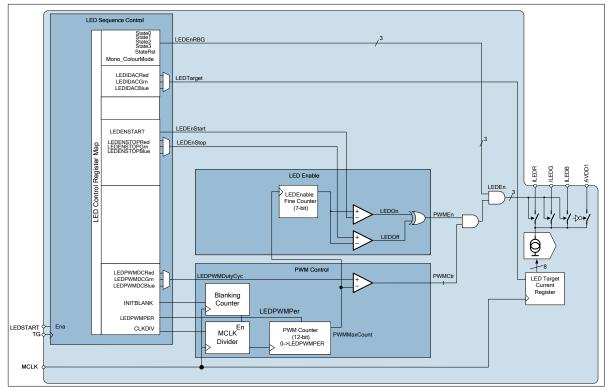

With reference to Figure 12, the WM8255 uses a LED sequence state machine to control the sequence and duration of the illumination of the red, green and blue LEDs.

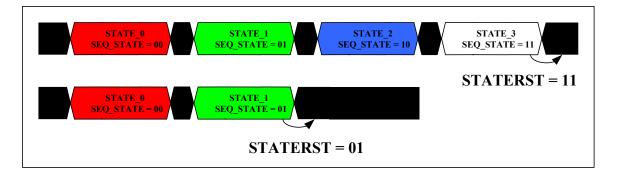

The LED sequence state machine can progress through up to 4 states each sequence. Each of the sequence states (STATE\_0 to STATE\_3) may be set to one of four values to determine on whether a red, green or blue LED is illuminated or all LEDs are off. The register STATERST will determine the number of states the sequence state machine can progress through. Once the sequence state machine has reached the reset state, the LED state machine will remain in this state until again initiated.

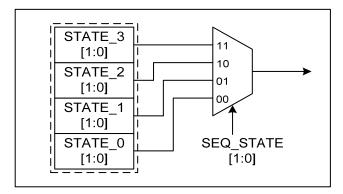

#### LED CURRENT DRIVE SEQUENCE DEFINITION

Figure 13 illustrates the functionality of the sequence state mapping. The current state of the sequence machine (SEQ\_STATE) is an internal register used to select one of the four register state mappings. This register increments until the value specified by STATERST at which point the sequence will hold. Figure 14 shows two examples when STATERST is set to "11<sub>bin</sub>" for a 4 state sequence, and to "01<sub>bin</sub>" for a 2 state sequence.

Figure 12 Block Diagram of PWM LED Control

Figure 13 State Mapping Functionality

Figure 14 Setting the Sequence Length with STATERST

## LED CURRENT DRIVE SEQUENCE SYNCHRONISATION AND PROGRESSION

The trigger to progress the state machine through the sequence states is dependent on whether the LED driver is operating in colour mode or monochrome mode.

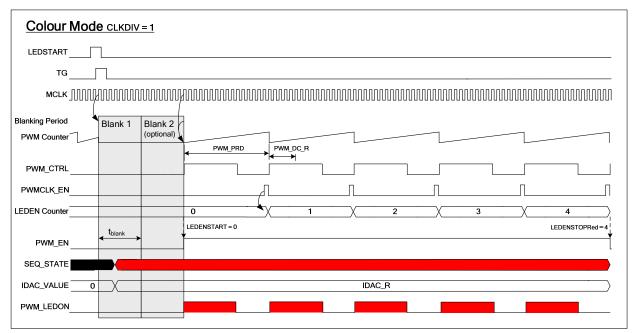

#### COLOUR MODE

In Colour Mode operation, LEDSTART and TG are used to synchronise and progress the sequence state machine. This allows a single LED change for each line scan.

With both LEDSTART and TG high, the sequence state machine is synchronously set to STATE\_0 by MCLK. With LEDSTART low and at the next high pulse of TG, the sequence state machine is progressed to the next state, STATE\_1, by MCLK. This is repeated until the maximum number of states determined by STATERST has been reached. At this point the LED drive current will be switched away from the selected LED. The sequence state machine will be held in this state until restarted by LEDSTART and TG.

If at any time both TG and LEDSTART are high, the sequence is synchronously set back to STATE\_0 by MCLK.

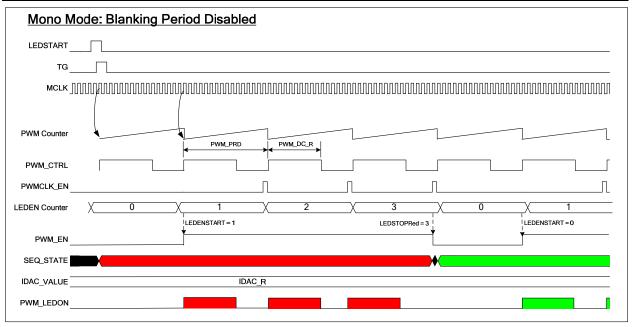

#### MONOCHROME (COMPOSITE) MODE

In Monochrome Mode, the progression between sequence states is triggered by the completion of the previous sequence state. This allows a complete LED sequence change for each line scan.

With both TG and LEDSTART high, the sequence state machine is synchronously set to the STATE\_0 by MCLK. When the STATE\_0 has reached the end of its enable period, the sequence state machine is progressed to the next state by MCLK. This is repeated until the maximum number of states determined by STATERST has been reached. At this point the LED drive current will be switched away from the selected LEDs. The sequence state machine will be held in this state until restarted by LEDSTART and TG.

If at any time both TG and LEDSTART are high, the sequence is synchronously set back to STATE\_0 by MCLK.

### LED CURRENT DRIVE INTENSITY CONTROL

The LED current driver is programmable to allow the LED light intensity to be adjusted independent of the LED light wavelength. Two methods are available for this:

- The absolute LED current drive may be set using a programmable 8-bit current DAC. The current DAC range for each of the LEDs may be adjusted to one of four ranges using the register LEDIRNG.

- The LED current drive may be pulsed using a pulse width modulated. The pulse width modulated period is set using the register LEDPWMPER and on time using the registers LEDPWMDCR, LEDPWMDCB and LEDPWMDCG.

Control of the absolute LED current drive and PWM modulation are independently programmable for each of the red, green and blue LEDs using the register map. The signals LEDSTART, TG and MCLK determine timing.

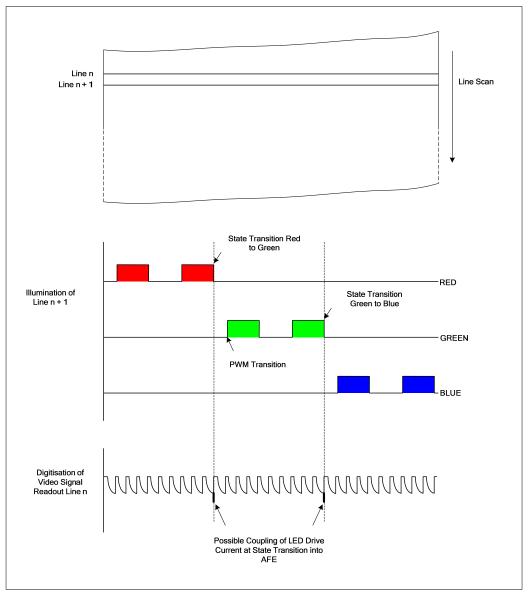

#### LED CURRENT DRIVE STATE TRANSITION AND PWM SWITCHING

The WM8255 is the combination of a LED current switching matrix and an AFE. With reference to Figure 15, during a typical line scan the video signal of the previous line scan is digitised by the AFE while the image of the current line scan is illuminated. To suppress any switching noise of the LED switching matrix coupling into the AFE, care is taken while switching the current.

Two types of current switching are available in the WM8255, state transition switching and PWM switching. State transition switching occurs when either a new LED is to be selected or the LED current DAC has to be updated. PWM transition switching occurs when the illumination intensity is controlled by pulsing the LED drive current. In colour mode, state transition switching should occur at the start of a line scan. In mono mode, state transition switching can occur during the line scan. In either colour mode or mono mode, PWM transition switching can occur during the line scan.

#### Figure 15 Relationship between Line Scan Illumination and Video Signal Readout

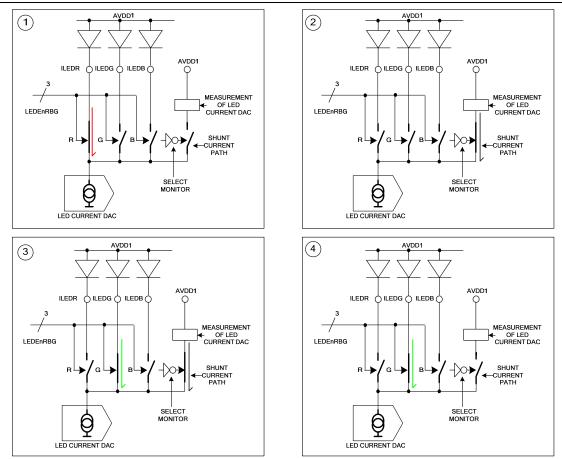

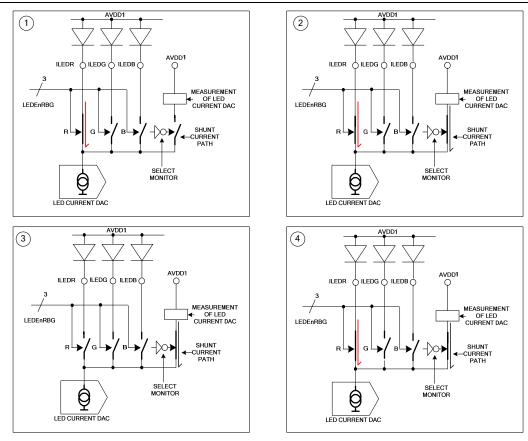

Two current switching techniques are used for state and PWM transition switching, slew rate controlled current switching and current steering switching.

With reference to Figure 16, the LED drive current has three blocks, the LED current DAC, the LED RGB matrix switch and a shunt current path switch.

With reference to Figure 16, for current slew rate controlled switching, the LED current DAC value is reset from the current value to zero then set to an updated value. Slew rate limited current switch may be partitioned into four operations:

Figure 16 Current Slew Rate Controlled Switching

- 1. The red RGB switch is initially closed and the LED drive current will flow in the red diode

- The Red RGB switch will open and the shunt current path switch is closed. The LED drive current will flow in the shunt current path. During this period the LED current DAC is reset to zero then updated to the next value. No current will flow in any LEDs.

- 3. The green RGB switch will be closed.

- 4. The auxiliary current path switch will be opened and LED drive current will flow in the green LED.

The finite time taken for a slew rate controlled current switch is the period necessary to change the value of the LED current DAC. The slew rate of the current change is limited by the dynamic performance of the LED current DAC. During this time the LED IDAC current will flow through the shunt current path switch and no illumination will occur. This period of time is defined by blanking period

#### MONO MODE REQUIREMENTS

During a slew rate limited current switch of the LED IDAC, the change of current flowing in the IDAC will couple a minor disturbance into the AFE. In colour mode this disturbance is not an issue since the state change switching will occur at the beginning of a line scan when no imaging is occurring. In mono mode a red, blue and green state switching may occur during a line scan and couple correlated switching noise into the signal path.

In mono mode to minimise switching noise into the signal path::

- The blanking period must be disabled. In this mode during a state change, no slew rate limiting switching will occur, Only the RGB switches will be switched. Table 3 defines the method to disable blanking during a state transition.

- In this mode of operation, between states the absolute value of the LED IDAC current must not change.

\_

In this mode of operation, setting the duty cycle to zero is an invalid state. The RGB switches should be used to switch off the LED current.

This method will have no effect on colour mode performance.

| BLANKING DISABLE CODE SET                                                                         |                                                                                            |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Address                                                                                           | Data                                                                                       | Comment                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 0x01 0xA3                                                                                         |                                                                                            | This will put the part into test configuration mode. Any address will now point to                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                   |                                                                                            | the extended page reconfiguration register                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 0x24 0x1C                                                                                         |                                                                                            | This will:                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                                                                                                   |                                                                                            | force the LED IDAC control state machine to stay on at all time                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                                                                                   |                                                                                            | - force the value to be held in LEDIDACR to be loaded into the LED current DAC                                                                                                                                                                                                                                             |  |  |  |  |  |

| 0x01                                                                                              | 0x23                                                                                       | This will take the part back into normal operating mode.                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 1. If this COMPLI                                                                                 |                                                                                            | peration is not carried out TOGETHER the part may go into an unsupported mode                                                                                                                                                                                                                                              |  |  |  |  |  |

| 1. If this COMPLI<br>To finish a mono<br>options are availa                                       | mode scan with blanki<br>ble for a complete res                                            | ing period disabled and perform another operation, the part needs to get into a know state. Two et of the device or a reset of the LED sequence controller:                                                                                                                                                                |  |  |  |  |  |

| 1. If this COMPLI<br>To finish a mono<br>options are availa<br><b>Option 1:</b> WM828             | mode scan with blanki                                                                      | ing period disabled and perform another operation, the part needs to get into a know state. Two et of the device or a reset of the LED sequence controller:                                                                                                                                                                |  |  |  |  |  |

| 1. If this COMPLI<br>To finish a mono<br>options are availa<br>Option 1: WM823<br>Address         | mode scan with blanki<br>ble for a complete res<br>55 global reset from bl                 | ng period disabled and perform another operation, the part needs to get into a know state. Two<br>et of the device or a reset of the LED sequence controller:                                                                                                                                                              |  |  |  |  |  |

| To finish a mono<br>options are availa<br><b>Option 1:</b> WM825<br><b>Address</b><br>0x04        | mode scan with blanki<br>ble for a complete res<br>55 global reset from bl<br>Data<br>0x00 | Ing period disabled and perform another operation, the part needs to get into a know state. Two et of the device or a reset of the LED sequence controller:  anking period disable  Comment  This will reset the WM8255 into its default condition. The part should now be fully                                           |  |  |  |  |  |

| 1. If this COMPLI<br>To finish a mono<br>options are availa<br>Option 1: WM82!<br>Address<br>0x04 | mode scan with blanki<br>ble for a complete res<br>55 global reset from bl<br>Data<br>0x00 | Ing period disabled and perform another operation, the part needs to get into a know state. Two et of the device or a reset of the LED sequence controller:  anking period disable  Comment  This will reset the WM8255 into its default condition. The part should now be fully reconfigured into the user configuration. |  |  |  |  |  |

Table 3 Blanking Period Disable

With reference to Figure 17 for current steering,

- 1. The appropriate RGB matrix switch is closed allowing the LED current DAC current to flow in the LED

- 2. The first step to switch off the LED current is to close the shunt current path switch

- 3. The LED is switched off by opening the RGB switch matrix.

- 4. To switch on the LED, first the shunt current path switch is closed and the cycle repeats.

A make before break switch sequence is used when the LED is switched on or off. As a result the LED current DAC always has a path to flow and never changes value.

Figure 17 Current Steering Switching

## LED CURRENT DRIVE CURRENT PWM CONTROL

During each sequence state, the LED control module can be pulsed by Pulse Width Modulating (PWM) the LED current drive. For each sequence state, the PWM frequency, duty cycle, and number of PWM cycles can be configured.

The PWM controller consists of two blocks; the MCLK divider and the PWM counter. The MCLK divider divides the MCLK by an amount set by the register CLKDIV.

The divided MCLK is then used to clock the PWM counter. The PWM counter will increment until it reaches its maximum count set by the register LEDPWMPER. At this point, the PWM counter will reset to zero, then continue to increment. This will set the period of the PWM control.

As the PWM counter is incremented, its state is compared with the duty cycle setting, which is set by the value in register LEDPWMDC. PWMCtrl is set while the counter value is smaller than the duty cycle setting. When the counter is larger than or equal to the duty cycle, PWMCTRL is reset for the rest of the PWM period. This will set the duty cycle of the PWM control.

The reset of the PWM counter will increment the LEDEnable counter. When the LEDEnable counter has reached LEDENSTART, PWMEn is set high, which allows PWMCtrl to control the LED current drive. The LEDEnable counter will continue to increment until it has reached LEDENSTOP. At this point PWMEn is set low, which stops PWMCtrl from controlling the LED current drive. This will set the number of cycles of the PWM control.

The PWM frequency is defined by LEDPWMPER and the divider CLKDIV. LEDPWMPER and CLKDIV may be calculated as the nearest integral of the MCLK frequency divided by the PWM frequency. If the maximum value of LEDPWMPER would reach its maximum before the desired PWM period is achieved, CLKDIV should be incremented to scale LEDPWMPER correctly.

The PWM duty cycle is defined by LEDPWMDC and CLKDIV. For a chosen PWM frequency, an integral number of PWM cycles for the period of TG may be calculated. The range of the PWM period and the duty cycle can be up to  $(2^{4} \times 2^{12})$  MCLK cycles.

There is an operational difference in monochrome mode in that LEDENSTART is only used in the first state. In subsequent states the LED enable is always activated after the appropriate number of blanking periods (LEDENSTOP is used in the same method as colour mode operation).

#### NON PWM MODE

The PWM functionality can be disabled and just the current DAC can be used. The duty cycle LEDPWMDC register for each colour should be set to equal the duty cycle period register, LEDPWMPER. The value of both these registers should be set to an appropriate value.

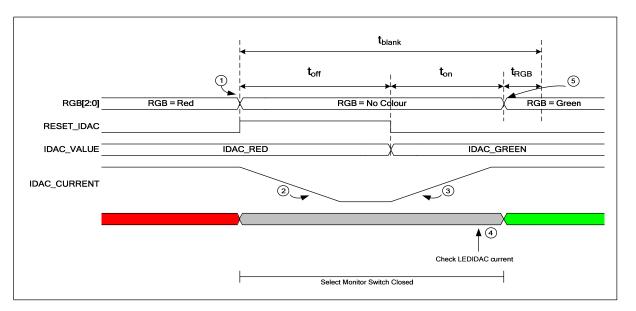

### LED CURRENT DRIVE CURRENT BLANKING PERIOD

At the start of a LED sequence state transition the LED controller performs a blanking period. The blanking period is a period of time reserved to switch to the next LED drive current state in the sequence. In addition, during the blanking period the absolute LED drive current will be updated, a Safe Operating Area (SOA) test may be performed and finally the next LED in the sequence will be selected then driven. At completion of the blanking period, the PWM controller is enabled.

Figure 18 shows a basic blanking period during a state transition of switching the Red LED off, then Green LED on.

The blanking period may be split into a sequence of five operations:

- 1. The Red RGB switch will be switched off and any current forced to flow in the shunt current path.

- 2. The LED current DAC will be disabled. During this period, the current flow in the auxiliary current path will tend to zero.

- The LED current DAC value will be updated to the value necessary to drive the Green LED. During this time, the current flow in the auxiliary current path will tend to the updated LED current DAC current.

- 4. A SOA test will be performed on the updated LED current DAC current.

- 5. The Green RGB switch will be switched on.

The transition from one state to the next takes the finite time defined by the period  $t_{\text{blank}}$ .

With reference to Table 4, the basic blanking period may be optimised dependant on the mode of operation.

Figure 18 LED Current DAC Current during a Blanking Period

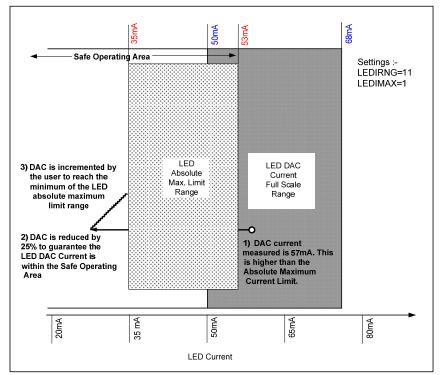

| ILIMITEN [1:0] | DESCRIPTION                                                                                                                                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00             | At a state transition, one blanking period will be used before the LED can be enabled.                                                                                                                        |

|                | LED DAC current will be changed and next LED in sequence shall be selected. No Safe Operating Area test will be performed.                                                                                    |

| 01             | At a state transition, two blanking periods will be used before the LED can be enabled.                                                                                                                       |

|                | During the first blanking period, should the LED DAC current exceed LEDIMAX, ILIMITFLAG is set and the LED DAC current is reduced by the percentage set by ILIMITDEC.                                         |

|                | During the second blanking period, should the LED current exceed LEDIMAX, ILIMITFLAG is set and the LED DAC current will be shutdown.                                                                         |

| 10             | At a state transition, one blanking period will be used before the LED can be enabled.                                                                                                                        |

|                | Should the LED current exceed LEDIMAX, ILIMITFLAG is set. The LED current will not be reduced automatically. In this situation, the user should take measures to protect the LED by reducing the LED current. |

| 11             | Not a valid setting                                                                                                                                                                                           |

Table 4 Modes of Operation of ILIMITEN Register

#### SETTING THE INITBLANK REGISTER

With reference to Figure 19, the period  $t_{BLANK}$  is the initial blank period with no illumination. The initial blank period time must be controlled by setting a value for a 9-bit register INITBLANK. Setting this register will enable a counter that is clocked by MCLK to allow for the necessary minimum 25 microseconds. The last three LSBs are fixed to zero and only the 6 MSBs are adjustable.

The value needed for the register INITBLANK is calculated by :-

(t<sub>BLANK</sub> \*0.8)/ MCLK period = INITBLANK<sub>dec</sub>. This number should be rounded up to an integral decimal number.