# RENESAS

# DATASHEET

## ISL54225

High-Speed USB 2.0 (480Mbps) Multiplexer with Overvoltage Protection (OVP)

FN7627 Rev 0.00 July 2, 2010

The ISL54225 is a single supply dual 2:1 multiplexer that can operate from a single 2.7V to 5.25V supply. It contains two SPDT (Single Pole/Double Throw) switches configured as a DPDT. The part was designed for switching or routing of USB High-Speed signals and/or USB Full-speed signals in portable battery powered products.

The  $6.5\Omega$  switches were specifically designed to pass USB high speed/full speed data signals. They have high bandwidth and low capacitance to pass USB high speed data signals with minimal DISTORTION.

The ISL54225 has OVP circuitry on the D-/D+ COM pins that opens the USB in-line switches when the voltage at these pins exceeds 3.8V (typ) or goes negative by -0.5V (typ). It isolates fault voltages up to +5.25V or down to

-5V from getting passed to the other-side of the switch, thereby protecting the USB transceivers.

The digital logic inputs are 1.8V logic compatible when operated with a 2.7V to 3.6V supply. The ISL54225 has an output enable pin to open all the switches. It can be used to facilitate proper bus disconnect and connection when switching between the USB sources.

The ISL54225 is available in 10 Ld 1.8mmx1.4mm  $\mu$ TQFN and 10 Ld TDFN packages. It operates over a temperature range of -40°C to +85°C.

## Features

- High-Speed (480Mbps) and Full-Speed (12Mbps) Signaling Capability per USB 2.0

- 1.8V Logic Compatible (2.7V to +3.6V Supply)

- Enable Pin to Open all Switches

- Low Power Mode

- Power OFF Protection

- D-/D+ Pins Overvoltage Protection for +5.25V and -5V Fault Voltages

- -3dB Frequency 780MHz

- Low ON Capacitance @ 240MHz 3.3pF

- Low ON-Resistance  $6.5\Omega$

- Single Supply Operation ( $V_{DD}$ ) 2.7V to 5.25V

- Available in  $\mu TQFN$  and TDFN Packages

- Pb-Free (RoHS Compliant)

- Compliant with USB 2.0 Short Circuit and Overvoltage Requirements Without Additional External Components

### Applications\*(see page 16)

- MP3 and other Personal Media Players

- Cellular/Mobile Phones

- PDAs

- Digital Cameras and Camcorders

- USB Switching

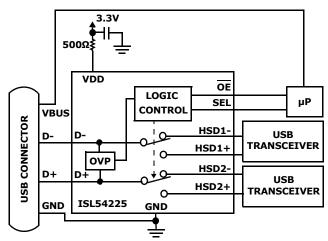

## **Typical Application**

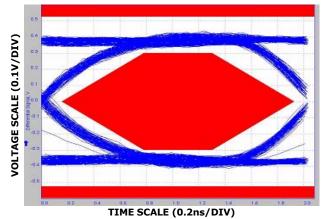

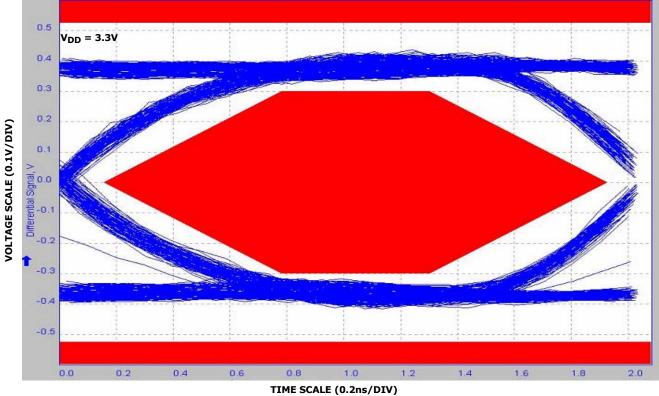

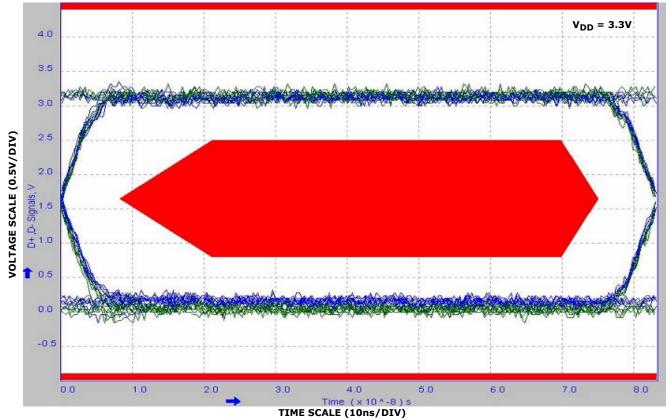

## USB 2.0 HS Eye Pattern With Switches in the Signal Path

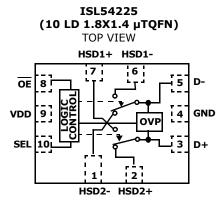

## **Pin Configuration**

ISL54225 (10 LD 3X3 TDFN) TOP VIEW PD LOGIC 10 VDD SEL 1 CONTROL 9 OE HSD2- 2 HSD2+ 3 8 HSD1+ 7 HSD1-D+ 4 GND 5 OVP 6 D-

NOTE:

1. Switches Shown for SEL = Logic "1" and  $\overline{OE}$  = Logic "0".

## **Pin Descriptions**

| μTQFN | TDFN | PIN<br>NAME | DESCRIPTION                            |

|-------|------|-------------|----------------------------------------|

| 1     | 2    | HSD2-       | USB Data Port Channel 2                |

| 2     | 3    | HSD2+       | USB Data Port Channel 2                |

| 3     | 4    | D+          | USB Data COM Port                      |

| 4     | 5    | GND         | Ground Connection                      |

| 5     | 6    | D-          | USB Data COM Port                      |

| 6     | 7    | HSD1-       | USB Data Port Channel 1                |

| 7     | 8    | HSD1+       | USB Data Port Channel 1                |

| 8     | 9    | OE          | Bus Switch Enable                      |

| 9     | 10   | VDD         | Power Supply                           |

| 10    | 1    | SEL         | Select Logic Control Input             |

| -     | PD   | PD          | Thermal Pad. Tie to Ground or<br>Float |

## **Truth Table**

| OE | SEL | HSD1-,<br>HSD1+ | HSD2-,<br>HSD2+ | STATE     |

|----|-----|-----------------|-----------------|-----------|

| 0  | 0   | ON              | OFF             | Normal    |

| 0  | 1   | OFF             | ON              | Normal    |

| 1  | 0   | OFF             | OFF             | Low Power |

| 1  | 1   | OFF             | OFF             | Normal    |

Logic "0" when  $\leq$  0.5V, Logic "1" when  $\geq$  1.4V with a 2.7V to 3.6V Supply.

Note: In Low Power mode there is no persistence checking when in OVP condition.

### TABLE 1. USB - OVP POSSIBLE SITUATIONS AND TRIP POINT VOLTAGE

|              |                                  |                 |           | TRIP POINT |        |

|--------------|----------------------------------|-----------------|-----------|------------|--------|

| CODEC SUPPLY | SWITCH SUPPLY (V <sub>DD</sub> ) | COMs SHORTED TO | PROTECTED | MIN        | MAX    |

| 2.7V to 3.3V | 2.7V to 5.25V                    | VBUS            | Yes       | 3.63V      | 3.95V  |

| 2.7V to 3.3V | 2.7V to 5.25V                    | -5V             | Yes       | -0.76V     | -0.29V |

## **Ordering Information**

| PART<br>NUMBER                | PART<br>MARKING | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free)                       | PKG.<br>DWG. # |

|-------------------------------|-----------------|---------------------|--------------------------------------------|----------------|

| ISL54225IRUZ-T (Notes 2, 3)   | U0              | -40 to +85          | 10 Ld 1.8x1.4mm $\mu$ TQFN (Tape and Reel) | L10.1.8x1.4A   |

| ISL54225IRUZ-T7A (Notes 2, 3) | U0              | -40 to +85          | 10 Ld 1.8x1.4mm $\mu$ TQFN (Tape and Reel) | L10.1.8x1.4A   |

| ISL54225IRTZ (Note 4)         | 4225            | -40 to +85          | 10 Ld 3x3 TDFN                             | L10.3x3A       |

| ISL54225IRTZ-T (Notes 2, 4)   | 4225            | -40 to +85          | 10 Ld 3x3 TDFN (Tape and Reel)             | L10.3x3A       |

| ISL54225IRTZEVAL1Z            | Evaluation Bo   | ard                 |                                            |                |

NOTES:

2. Please refer to  $\underline{TB347}$  for details on reel specifications.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL54225</u>. For more information on MSL please see techbrief <u>TB363</u>.

### **Absolute Maximum Ratings**

| VDD to GND         -0.3V to 6.5V           VDD to Dx         10.5V           Dx to HSD1x, HSD2x         8.6V           Input Voltages         10.5V |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| HSD2x, HSD1x 0.3V to 6.5V                                                                                                                           |

| SEL, $\overline{OE}$                                                                                                                                |

| Output Voltages                                                                                                                                     |

| D+, D5V to 6.5V                                                                                                                                     |

| Continuous Current (HSD2x, HSD1x)±40mA                                                                                                              |

| Peak Current (HSD2x, HSD1x)                                                                                                                         |

| (Pulsed 1ms, 10% Duty Cycle, Max)±100mA                                                                                                             |

| ESD Rating:                                                                                                                                         |

| Human Body Model (Tested per JESD22-A114-F)>5.5kV                                                                                                   |

| Machine Model (Tested per JESD22-A115-A) >250V                                                                                                      |

| Charged Device Model (Tested per JESD22-C101-D) >2kV                                                                                                |

| Latch-up Tested per JEDEC; Class II Level A at +85°C                                                                                                |

### **Thermal Information**

| Thermal Resistance (Typical)       | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------|----------------------|------------------------|

| 10 Ld µTQFN Package (Note 6, 7)    | . 210                | 165                    |

| 10 Ld TDFN Package (Notes 8, 9).   | . 58                 | 22                     |

| Maximum Junction Temperature (Plas | stic Package         | ) +150°C               |

| Maximum Storage Temperature Rang   | e65°                 | C to +150°C            |

| Pb-Free Reflow Profile             |                      | ee link below          |

| http://www.intersil.com/pbfree/Pb- | FreeReflow.          | <u>asp</u>             |

|                                    |                      |                        |

### **Recommended Operating Conditions**

| Temperature Range                    | -40°C to +85°C  |

|--------------------------------------|-----------------|

| V <sub>DD</sub> Supply Voltage Range | . 2.7V to 5.25V |

| Logic Control Input Voltage          | 0V to 5.25V     |

| Analog Signal Range                  |                 |

| $V_{DD} = 2.7V$ to 5.25V             | 0V to 3.6V      |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 6.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 7. For  $\theta_{JC}\text{, the ``case temp" location is taken at the package top center.$

- 8.  $\theta_{JA}$  is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 9. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

| Electrical Specifications - 2.7V to 5.25V Supply | Test Conditions: $V_{DD} = +3.3V$ , GND = 0V, $V_{SELH} = 1.4V$ ,                                 |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------|

|                                                  | $V_{SELL} = 0.5V$ , $V_{\overline{OEH}} = 1.4V$ , $V_{\overline{OEL}} = 0.5V$ , (Note 10), Unless |

|                                                  | Otherwise Specified. Boldface limits apply over the operating                                     |

|                                                  | temperature range, -40°C to +85°C.                                                                |

| PARAMETER                                       | TEST CONDITIONS                                                                                            | TEMP<br>(°C) | MIN<br>(Notes 11, 12) | ТҮР | MAX<br>(Notes 11, 12) | UNITS |  |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------|-----------------------|-----|-----------------------|-------|--|--|--|

| ANALOG SWITCH CHAR                              | ANALOG SWITCH CHARACTERISTICS                                                                              |              |                       |     |                       |       |  |  |  |

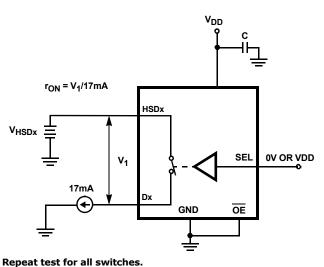

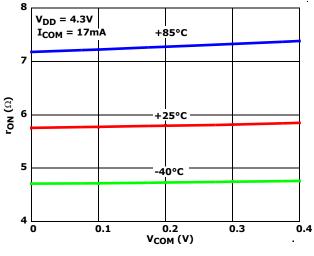

| ON-Resistance, r <sub>ON</sub>                  | $V_{DD}$ = 2.7V, SEL = 0.5V or 1.4V, $\overline{OE}$ = 0.5V,                                               | 25           | -                     | 6.5 | 8                     | Ω     |  |  |  |

| (High-Speed)                                    | $I_{Dx} = 17$ mA, $V_{HSD1x}$ or $V_{HSD2x} = 0$ V to 400mV (see Figure 3, Note 15)                        | Full         | -                     | -   | 10                    | Ω     |  |  |  |

| r <sub>ON</sub> Matching Between                | $V_{DD} = 2.7V$ , SEL = 0.5V or 1.4V, $\overline{OE} = 0.5V$ ,                                             | 25           | -                     | 0.2 | 0.45                  | Ω     |  |  |  |

| Channels, ∆r <sub>ON</sub><br>(High-Speed)      | $I_{Dx} = 17$ mA, $V_{HSD1x}$ or $V_{HSD2x} = Voltage at max rON, (Notes 14, 15)$                          | Full         | -                     | -   | 0.5                   | Ω     |  |  |  |

| r <sub>ON</sub> Flatness, R <sub>FLAT(ON)</sub> |                                                                                                            |              | -                     | 0.3 | 0.5                   | Ω     |  |  |  |

| (High-Speed)                                    | $I_{Dx} = 17$ mA, $V_{HSD1x}$ or $V_{HSD2x} = 0$ V to 400mV,<br>(Notes 13, 15)                             | Full         | -                     | -   | 1                     | Ω     |  |  |  |

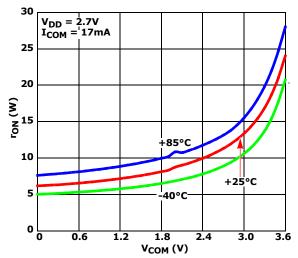

| ON-Resistance, r <sub>ON</sub>                  | $V_{DD} = 3.3V$ , SEL = 0.5V or 1.4V, $\overline{OE} = 0.5V$ ,                                             | 25           | -                     | 12  | 20                    | Ω     |  |  |  |

|                                                 | $I_{COMx} = 17$ mA, $V_{D+}$ or $V_{D-} = 3.3V$ (See Figure 4, Note 15)                                    | Full         | -                     | -   | 25                    | Ω     |  |  |  |

| OFF Leakage Current,                            | $V_{DD}$ = 5.25V, SEL = $V_{DD}$ and $\overline{OE}$ = $V_{DD}$ or                                         | 25           | -20                   | 1   | 20                    | nA    |  |  |  |

| IHSD1x(OFF)                                     | OE = 0V, V <sub>Dx</sub> = 0.3V, 3.3V, V <sub>HSD1x</sub> = 3.3V,<br>0.3V, V <sub>HSD2x</sub> = 0.3V, 3.3V | Full         | -                     | 30  | -                     | nA    |  |  |  |

| ON Leakage Current,                             | $V_{DD} = 5.25V, SEL = \overline{OE} = 0V, V_{Dx} = 0.3V, 3.3V,$                                           | 25           | -                     | 2   | 3                     | μA    |  |  |  |

| <sup>I</sup> HSD1x(ON)                          | V <sub>HSD1X</sub> = 0.3V, 3.3V, V <sub>HSD2x</sub> = 3.3V, 0.3V                                           |              | -                     | -   | 4                     | μA    |  |  |  |

| OFF Leakage Current,                            | $V_{DD} = 5.25V$ , SEL = $\overline{OE} = 0V$ or $\overline{OE} = V_{DD}$ ,                                | 25           | -20                   | 1   | 20                    | nA    |  |  |  |

| IHSD2x(OFF)                                     | V <sub>Dx</sub> = 3.3V, 0.3V, V <sub>HSD2x</sub> = 0.3V, 3.3V,<br>V <sub>HSD1x</sub> = 3.3V, 0.3V          | Full         | -                     | 30  | -                     | nA    |  |  |  |

### Electrical Specifications - 2.7V to 5.25V Supply Test Conditions: V<sub>DD</sub> = +3.3V, GND = 0V, V<sub>SELH</sub> = 1.4V,

Test Conditions:  $V_{DD} = +3.3V$ , GND = 0V,  $V_{SELH} = 1.4V$ ,  $V_{SELL} = 0.5V$ ,  $V_{\overline{OEH}} = 1.4V$ ,  $V_{\overline{OEL}} = 0.5V$ , (Note 10), Unless Otherwise Specified. **Boldface limits apply over the operating temperature range, -40°C to +85°C. (Continued)**

| PARAMETER                                                           | TEST CONDITIONS                                                                                                                                                                                                        | TEMP<br>(°C) |       | ТҮР  | MAX<br>(Notes 11, 12) | UNITS |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|------|-----------------------|-------|

| ON Leakage Current,                                                 | $V_{DD} = 5.25V, SEL = V_{DD}, \overline{OE} = 0V, V_{Dx} = 0.3V,$                                                                                                                                                     | 25           | -     | 2    | 3                     | μA    |

| I <sub>HSD2x(ON)</sub>                                              | 3.3V, V <sub>HSD2x</sub> = 0.3V, 3.3V, V <sub>HSD1x</sub> = 3.3V, 0.3V                                                                                                                                                 | Full         | -     | -    | 4                     | μA    |

| Power OFF Leakage<br>Current, I <sub>D+</sub> , I <sub>D-</sub>     | $V_{DD} = 0V, V_{D+} = 5.25V, V_{D-} = 5.25V,$<br>SEL = $\overline{OE} = V_{DD}$                                                                                                                                       | 25           | -     | 5    | 13                    | μA    |

| Power OFF Logic Current, $I_{SEL}$ , $I_{\overline{OE}}$            | $V_{DD} = 0V, SEL = \overline{OE} = 5.25V$                                                                                                                                                                             | 25           | -     | 19   | 26                    | μA    |

| Power OFF D+/D- Current,<br>I <sub>HSDX+</sub> , I <sub>HSDX-</sub> | $V_{DD} = 0V$ , SEL = $\overline{OE} = V_{DD}$ ,<br>$V_{HSDX+} = V_{HSDX-} = 5.25V$                                                                                                                                    | 25           | -     | 0.05 | 1                     | μA    |

| OVERVOLTAGE PROTECT                                                 | ION DETECTION                                                                                                                                                                                                          |              |       |      |                       |       |

| Positive Fault-Protection<br>Trip Threshold, V <sub>PFP</sub>       | $V_{DD}$ = 2.7V to 5.25V, SEL = 0V or $V_{DD}$ , $\overline{OE}$ = 0V See Table 1 on page 2                                                                                                                            | 25           | 3.63  | 3.8  | 3.95                  | V     |

| Negative Fault-Protection<br>Trip Threshold, V <sub>NFP</sub>       | $V_{DD}$ = 2.7V to 5.25V, SEL = 0V or $V_{DD}$ , $\overline{OE}$ = 0V<br>See Table 1 on page 2                                                                                                                         | 25           | -0.76 | -0.5 | -0.29                 | V     |

| OFF Persistence Time<br>Fault Protection Response                   | Negative OVP Response: $V_{DD}$ = 2.7V, SEL = 0V<br>or $V_{DD}$ , $\overline{OE}$ = 0V, $V_{Dx}$ = 0V to -5V, $R_L$ = 15k $\Omega$                                                                                     | 25           | -     | 1    | -                     | μs    |

| Time                                                                | Positive <u>OVP</u> Response: $V_{DD} = 2.7V$ , SEL = 0V<br>or $V_{DD}$ , $\overline{OE} = 0V$ , $V_{DX} = 0V$ to 5.25V, $R_L = 15k\Omega$                                                                             | 25           | -     | 2    | -                     | μs    |

| ON Persistence Time<br>Fault Protection Recovery<br>Time            | $V_{DD}$ = 2.7V, SEL = 0V or $V_{DD}$ , $\overline{OE}$ = 0V, $V_{Dx}$ = 0V to 5.25V or 0V to -5V, $R_L$ = 15k $\Omega$                                                                                                | 25           | -     | 40   | -                     | μs    |

| DYNAMIC CHARACTERIS                                                 | TICS                                                                                                                                                                                                                   |              |       |      |                       |       |

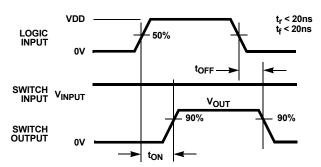

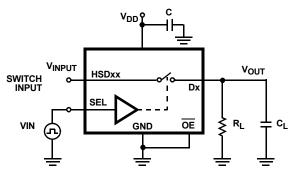

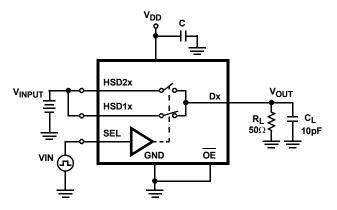

| Turn-ON Time, t <sub>ON</sub>                                       | $V_{DD}$ = 3.3V, $V_{INPUT}$ = 3V, $R_L$ = 50 $\Omega$ , $C_L$ = 50pF (see Figure 1)                                                                                                                                   | 25           | -     | 110  | -                     | ns    |

| Turn-OFF Time, t <sub>OFF</sub>                                     | $V_{DD}$ = 3.3V, $V_{INPUT}$ = 3V, $R_L$ = 50 $\Omega$ , $C_L$ = 50pF (see Figure 1)                                                                                                                                   | 25           | -     | 70   | -                     | ns    |

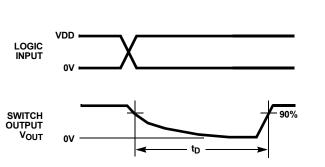

| Break-Before-Make Time<br>Delay, t <sub>D</sub>                     | $V_{DD}$ = 3.3V, R <sub>L</sub> = 50 $\Omega$ , C <sub>L</sub> = 50pF (see Figure 2)                                                                                                                                   | 25           | -     | 40   | -                     | ns    |

| Turn-ON Enable Time,<br><sup>t</sup> ENABLE                         | $V_{DD}$ = 3.3V, $V_{INPUT}$ = 3V, $R_L$ = 15k $\Omega$ ,<br>$C_L$ = 50pF, Time out of All-Off state                                                                                                                   | 25           | -     | 90   | -                     | ns    |

| Turn-OFF Disable Time,<br><sup>t</sup> DISABLE                      | $V_{DD} = 3.3V$ , $V_{INPUT} = 3V$ , $R_L = 15k\Omega$ ,<br>$C_L = 50pF$ , Time into All-Off state, Time is<br>highly dependent on the load ( $R_L$ , $C_L$ ) time<br>constant.                                        | 25           | -     | 120  | -                     | ns    |

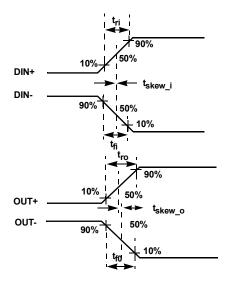

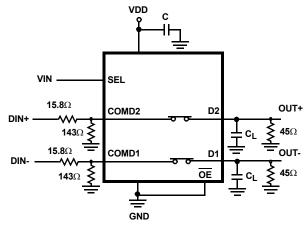

| Skew, (t <sub>SKEWOUT</sub> - t <sub>SKEWIN</sub> )                 | $      V_{DD} = 3.3V, SEL = 0V \text{ or } 3.3V, \overline{OE} = 0V, R_L = 45\Omega, \\       C_L = 10pF, t_R = t_F = 500ps \text{ at } 480Mbps, (Duty Cycle = 50%) (see Figure 6)                                   $ | 25           | -     | 50   | -                     | ps    |

| Rise/Fall Degradation<br>(Propagation Delay), t <sub>PD</sub>       | $V_{DD}$ = 3.3V, SEL = 0V or 3.3V, $\overline{OE}$ = 0V, $R_L$ = 45 $\Omega$ , $C_L$ = 10pF (see Figure 6)                                                                                                             | 25           | -     | 250  | -                     | ps    |

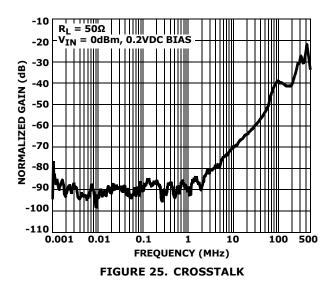

| Crosstalk                                                           | $V_{DD} = 3.3V, R_{L} = 50\Omega, f = 240MHz$ (see Figure 5)                                                                                                                                                           | 25           | -     | -32  | -                     | dB    |

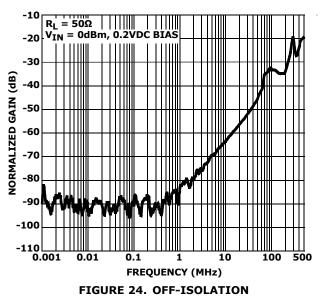

| OFF-Isolation                                                       | $V_{DD}$ = 3.3V, $\overline{OE}$ = 3.3V, $R_L$ = 50 $\Omega$ , f = 240MHz                                                                                                                                              | 25           | -     | -30  | -                     | dB    |

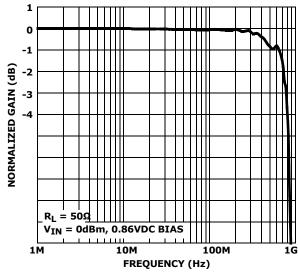

| -3dB Bandwidth                                                      | Signal = 0dBm, 0.2VDC offset, $R_L = 50\Omega$                                                                                                                                                                         | 25           | -     | 780  | -                     | MHz   |

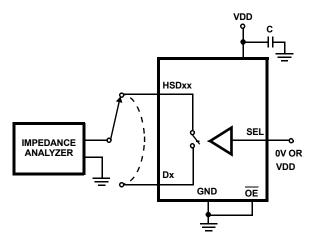

| OFF Capacitance, C <sub>HSxOFF</sub>                                | f = 1MHz, V <sub>DD</sub> = 3.3V, SEL = 0V or 3.3V,<br>$\overline{OE} = V_{DD}$ (see Figure 4)                                                                                                                         | 25           | -     | 2.5  | -                     | pF    |

| COM ON Capacitance,<br>C <sub>DX(ON)</sub>                          | f = 1MHz, V <sub>DD</sub> = 3.3V, SEL = 0V or 3.3V,<br>$\overline{OE} = 0$ V (see Figure 4)                                                                                                                            | 25           | -     | 5.4  | -                     | pF    |

## Electrical Specifications - 2.7V to 5.25V Supply

Test Conditions:  $V_{DD} = +3.3V$ , GND = 0V,  $V_{SELH} = 1.4V$ ,  $V_{SELL} = 0.5V$ ,  $V_{\overline{OEH}} = 1.4V$ ,  $V_{\overline{OEL}} = 0.5V$ , (Note 10), Unless Otherwise Specified. **Boldface limits apply over the operating temperature range, -40°C to +85°C. (Continued)**

| PARAMETER                                                      | TEST CONDITIONS                                                                                                  | TEMP<br>(°C) | MIN<br>(Notes 11, 12) | ТҮР | MAX<br>(Notes 11, 12) | UNITS |  |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|-----|-----------------------|-------|--|

| COM ON Capacitance,<br>C <sub>DX(ON)</sub>                     | $\frac{f}{OE} = 240MHz, V_{DD} = 3.3V, SEL = 0V \text{ or } 3.3V,$<br>$\frac{f}{OE} = 0V \text{ (see Figure 4)}$ | 25           | -                     | 3.3 | -                     | pF    |  |

| POWER SUPPLY CHARAC                                            | TERISTICS                                                                                                        |              |                       |     |                       |       |  |

| Power Supply Range, V <sub>DD</sub>                            |                                                                                                                  | Full         | 2.7                   |     | 5.25                  | V     |  |

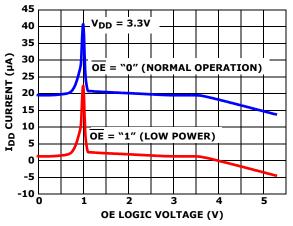

| Positive Supply Current, I <sub>DD</sub>                       | $V_{DD}$ = 5.25V, SEL = 0V or $V_{DD}$ , $\overline{OE}$ = 0V                                                    | 25           | -                     | 45  | 58                    | μA    |  |

|                                                                |                                                                                                                  | Full         | -                     | -   | 66                    | μA    |  |

| Positive Supply Current, I <sub>DD</sub>                       | $V_{DD} = 3.6V$ , SEL = 0V or $V_{DD}$ , $\overline{OE} = 0V$                                                    | 25           | -                     | 23  | 30                    | μA    |  |

|                                                                |                                                                                                                  | Full         | -                     | -   | 35                    | μA    |  |

| Positive Supply Current,                                       | $V_{DD} = 3.6V$ , SEL = 0V, $\overline{OE} = V_{DD}$                                                             | 25           | -                     | 5   | 6                     | μA    |  |

| I <sub>DD</sub> (Low Power State)                              |                                                                                                                  | Full         | -                     | -   | 10                    | μA    |  |

| Positive Supply Current, I <sub>DD</sub>                       | $V_{DD}$ = 4.3V, SEL = 2.6V, $\overline{OE}$ = 0V or 2.6V                                                        | 25           | -                     | 35  | 45                    | μA    |  |

|                                                                |                                                                                                                  | Full         | -                     | -   | 52                    | μA    |  |

| Positive Supply Current, I <sub>DD</sub>                       | $V_{DD}$ = 3.6V, SEL = 1.4V, $\overline{OE}$ = 0V or 1.4V                                                        | 25           | -                     | 25  | 32                    | μA    |  |

|                                                                |                                                                                                                  | Full         | -                     | -   | 38                    | μA    |  |

| DIGITAL INPUT CHARAC                                           | TERISTICS                                                                                                        |              | I                     |     | I                     |       |  |

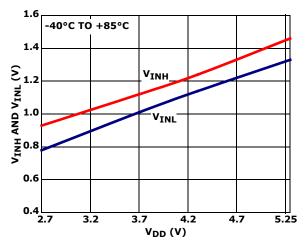

| Input Voltage Low, V <sub>SELL</sub> ,<br>V <del>OE</del> L    | V <sub>DD</sub> = 2.7V to 3.6V                                                                                   | Full         | -                     | -   | 0.5                   | V     |  |

| Input Voltage High, V <sub>SELH</sub> ,<br>V <mark>ОЕ</mark> Н | V <sub>DD</sub> = 2.7V to 3.6V                                                                                   | Full         | 1.4                   | -   | 5.25                  | V     |  |

| Input Voltage Low, V <sub>SELL</sub> ,<br>V <del>OE</del> L    | V <sub>DD</sub> = 3.7V to 4.2V                                                                                   | Full         | -                     | -   | 0.7                   | V     |  |

| Input Voltage High, V <sub>SELH</sub> ,<br>V <del>ОЕ</del> Н   | V <sub>DD</sub> = 3.7V to 4.2                                                                                    | Full         | 1.7                   | -   | 5.25                  | V     |  |

| Input Voltage Low, V <sub>SELL</sub> ,<br>V <del>OE</del> L    | V <sub>DD</sub> = 4.3V to 5.25V                                                                                  | Full         | -                     | -   | 0.8                   | V     |  |

| Input Voltage High, V <sub>SELH</sub> ,<br>V <del>OE</del> H   | V <sub>DD</sub> = 4.3V to 5.25V                                                                                  | Full         | 2.0                   | -   | 5.25                  | V     |  |

| Input Current, I <sub>SELL</sub> , I <u>OE</u> H               | $V_{DD} = 5.25V$ , SEL = 0V, $\overline{OE} = 5.25V$                                                             | Full         | -                     | 3.3 | -                     | nA    |  |

| Input Current, I <sub>SELH</sub>                               | $V_{DD}$ = 5.25V, SEL = 5.25V, 4M $\Omega$ pull-down resistor                                                    | Full         | -                     | 1.4 | -                     | μA    |  |

| Input Current, I <u>OE</u> L                                   | $V_{DD} = 5.25V, \overline{OE} = 0V, 4M\Omega$ pull-up resistor                                                  | Full         | -                     | 1.4 | -                     | μA    |  |

NOTES:

10.  $V_{LOGIC}$  = Input voltage to perform proper function.

11. The algebraic convention, whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

- 12. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 13. Flatness is defined as the difference between maximum and minimum value of ON-resistance over the specified analog signal range.

- 14.  $r_{ON}$  matching between channels is calculated by subtracting the channel with the highest max  $r_{ON}$  value from the channel with lowest max  $r_{ON}$  value, between HSD2+ and HSD2- or between HSD1+ and HSD1-.

- 15. Limits established by characterization and are not production tested.

Logic input waveform is inverted for switches that have the opposite logic sense.

Repeat test for all switches.  $C_L$  includes fixture and stray capacitance.

$$V_{OUT} = V_{(INPUT)} \frac{R_L}{R_L + r_{ON}}$$

FIGURE 1A. MEASUREMENT POINTS

TS FIGURE 1B. TEST CIRCUIT FIGURE 1. SWITCHING TIMES

Repeat test for all switches.  $\ensuremath{\mathsf{C}}_{\ensuremath{\mathsf{L}}}$  includes fixture and stray capacitance.

FIGURE 2A. MEASUREMENT POINTS

FIGURE 2B. TEST CIRCUIT

FIGURE 3. ron TEST CIRCUIT

## Test Circuits and Waveforms (Continued)

Repeat test for all switches.

### FIGURE 4. CAPACITANCE TEST CIRCUIT

**FIGURE 6A. MEASUREMENT POINTS**

Signal direction through switch is reversed, worst case values are recorded. Repeat test for all switches.

#### FIGURE 5. CROSSTALK TEST CIRCUIT

|tro - tri| Delay Due to Switch for Rising Input and Rising Output Signals.

|tfo - tfi| Delay Due to Switch for Falling Input and Falling Output Signals.

|tskew\_0| Change in Skew through the Switch for Output Signals.

|tskew\_i| Change in Skew through the Switch for Input Signals.

### FIGURE 6B. TEST CIRCUIT

**FIGURE 6. SKEW TEST**

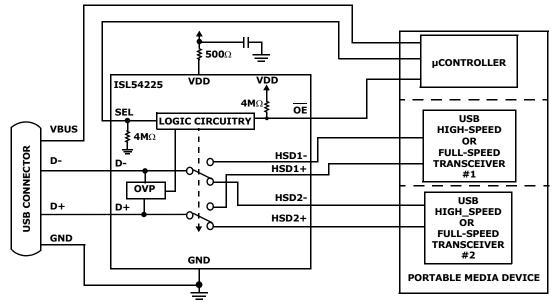

## **Application Block Diagram**

## **Detailed Description**

The ISL54225 device is a dual single pole/double throw (SPDT) analog switch configured as a DPDT that operates from a single DC power supply in the range of 2.7V to 5.25V.

It was designed to function as a dual 2-to-1 multiplexer to select between two USB high-speed differential data signals in portable battery powered products. It is offered in a TDFN, and a small  $\mu TQFN$  packages for use in MP3 players, cameras, PDAs, cellphones, and other personal media players. The device has an enable pin to open all switches and put the part in a low power state.

The part contains special overvoltage detection and protection (OVP) circuitry on the D-/D+ COM pins. This circuitry acts to open the USB in-line switches when the part senses a voltage on the COM pins that is >3.8V (typ) or < -0.5V (typ). It isolates voltages up to 5.25V and down to -5V from getting through to the other side of the switch to protect the USB transceivers connected at the signal pins (HSD1-, HSD1+, HSD2-, HSD2+).

The part consists of four  $6.5\Omega$  high speed (HSx) switches. These switches have high bandwidth and low capacitance to pass USB high-speed (480Mbps) differential data signals with minimal edge and phase distortion. They can also swing from 0V to 3.6V to pass USB full speed (12Mbps) differential data signals with minimal distortion.

The ISL54225 was designed for MP3 players, cameras, cellphones, and other personal media player applications that have multiple high-speed or full-speed transceivers sections and need to multiplex between these USB sources to a single USB host (computer). A typical application block diagram of this functionality is previously shown.

A detailed description of the HS switches is provided in the following section.

### High-Speed (HSx) Data Switches

The HSx switches (HSD1-, HSD1+, HSD2-, HSD2+) are bi-directional switches that can pass USB high-speed and USB full-speed signals when  $V_{DD}$  is in the range of 2.7V to 5.25V.

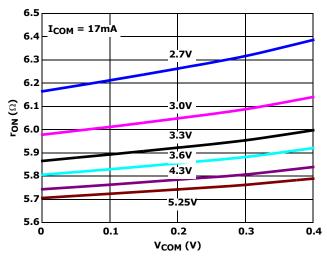

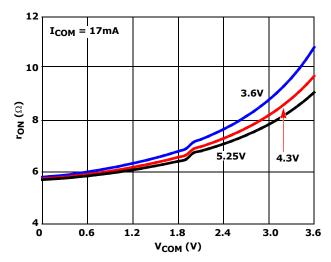

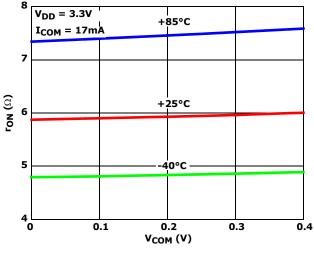

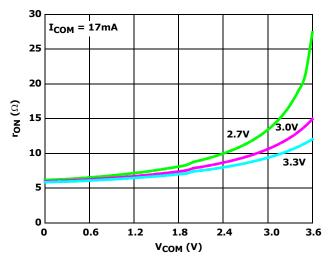

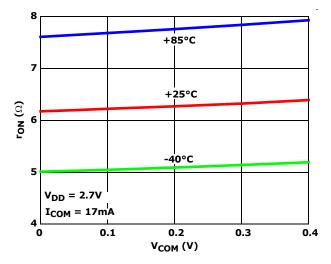

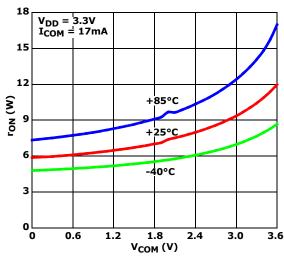

When powered with a 2.7V supply, these switches have a nominal  $r_{ON}$  of  $6.5\Omega$  over the signal range of 0V to 400mV with a  $r_{ON}$  flatness of  $0.3\Omega$ . The  $r_{ON}$  matching between the HSD1x switches and HSD2x switches over this signal range is only  $0.2\Omega$ , ensuring minimal impact by the switches to USB high-speed signal transitions. As the signal level increases, the  $r_{ON}$  switch resistance increases. At signal level of 3.3V, the switch resistance is nominally  $12\Omega$ . See Figures 9, 10, 11, 12, 13, 14, 15 and 16 in the "Typical Performance Curves" beginning on page 12.

The HSx switches were specifically designed to pass USB 2.0 high-speed (480Mbps) differential signals in the range of 0V to 400mV. They have low capacitance and high bandwidth to pass the USB high-speed signals with minimum edge and phase distortion to meet USB 2.0 high speed signal quality specifications. See Figure 21 in the "Typical Performance Curves" on page 14 for USB High-speed Eye Pattern taken with switch in the signal path.

The HSx switches can also pass USB full-speed signals (12Mbps) with minimal distortion and meet all the USB requirements for USB 2.0 full-speed signaling. See Figure 22 in the "Typical Performance Curves" on page 14 for USB Full-speed Eye Pattern taken with switch in the signal path.

The HS1 channel switches are active (turned ON) whenever the SEL voltage is logic "0"(Low) and the  $\overline{OE}$  voltage is logic "0"(Low).

The HS2 channel switches are active (turned ON) whenever the SEL voltage is logic "1" (High) and the  $\overline{\text{OE}}$  voltage is logic "0" (Low).

### **OVERVOLTAGE PROTECTION (OVP)**

The maximum normal operating signal range for the HSx switches is from 0V to 3.6V. For normal operation, the signal voltage should not be allowed to exceed these voltage levels or go below ground by more than -0.3V.

However, in the event that a positive voltage > 3.8V (typ) to 5.25V, such as the USB 5V V<sub>BUS</sub> voltage, gets shorted to one or both of the COM+ and COM- pins or a negative voltage < -0.5V (typ) to -5V gets shorted to one or both of the COM pins, the ISL54225 has OVP circuitry to detect the overvoltage condition and open the SPDT switches to prevent damage to the USB down-stream transceivers connected at the signal pins (HS1D-, HS1D+, HS2D-, HS2D+).

The OVP and power-off protection circuitry allows the COM pins (D-, D+) to be driven up to 5.25V while the V<sub>DD</sub> supply voltage is in the range of 0V to 5.25V. In this condition, the part draws < 100µA of I<sub>COMx</sub> and I<sub>DD</sub> current and causes no stress to the IC. In addition, the SPDT switches are OFF and the fault voltage is isolated from the other side of the switch.

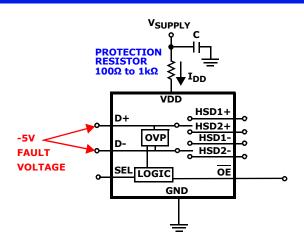

## External V<sub>DD</sub> Series Resistor to Limit $\mathbf{I}_{DD}$ Current during Negative OVP Condition

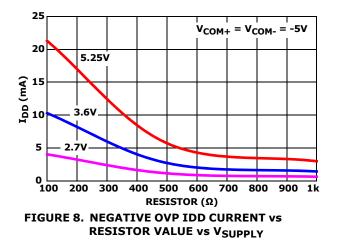

A 100 $\Omega$  to 1k $\Omega$  resistor in series with the VDD pin (see Figure 7) is required to limit the IDD current draw from the system power supply rail during a negative OVP fault event.

With a negative -5V fault voltage at both COM pins, the graph in Figure 8 shows the IDD current draw for different external resistor values for supply voltages of 2.7V, 3.6V, and 5.25V. With a 500 $\Omega$  resistor, the current draw is limited to around 5mA. When the negative fault voltage is removed, the I<sub>DD</sub> current will return to it's normal operation current of 25µA to 45µA.

The series resistor also provides improved ESD and latch-up immunity. During an overvoltage transient event (such as occurs during system level IEC 61000 ESD testing), substrate currents can be generated in the IC that can trigger parasitic SCR structures to turn ON, creating a low impedance path from the VDD power supply to ground. This will result in a significant amount of current flow in the IC, which can potentially create a latch-up state or permanently damage the IC. The external VDD resistor limits the current during this over-stress situation and has been found to prevent latch-up or destructive damage for many overvoltage transient events.

Under normal operation, the low microamp  $I_{DD}$  current of the IC produces an insignificant voltage drop across the series resistor resulting in no impact to switch operation or performance.

FIGURE 7. VDD SERIES RESISTOR TO LIMIT IDD CURRENT DURING NEGATIVE OVP AND FOR ENHANCED ESD AND LATCH-UP IMMUNITY

### **ISL54225 Operation**

The following will discuss using the ISL54225 shown in the "Application Block Diagram" on page 9.

### POWER

The power supply connected at the VDD pin provides the DC bias voltage required by the ISL54225 part for proper operation. The ISL54225 can be operated with a  $V_{DD}$  voltage in the range of 2.7V to 5.25V.

For lowest power consumption you should use the lowest  $\ensuremath{\mathsf{V}_{\text{DD}}}$  supply.

A  $0.01\mu F$  or  $0.1\mu F$  decoupling capacitor should be connected from the VDD pin to ground to filter out any power supply noise from entering the part. The capacitor should be located as close to the VDD pin as possible.

In a typical application,  $V_{DD}$  will be in the range of 2.8V to 4.3V and will be connected to the battery or LDO of the portable media device.

### LOGIC CONTROL

The state of the ISL54225 device is determined by the voltage at the SEL pin and the  $\overline{OE}$  pin. SEL is only active when the  $\overline{OE}$  pin is logic "0" (Low). Refer to "Truth Table" on page 2.

The ISL54225 logic pins are designed to minimize current consumption when the logic control voltage is lower than the V<sub>DD</sub> supply voltage. With V<sub>DD</sub> = 3.6V and logic pins at 1.4V, the part typically draws only 25µA. With V<sub>DD</sub> = 4.3V and logic pins at 2.6V, the part typically draws only 35µA. Driving the logic pins to the V<sub>DD</sub> supply rail minimizes power consumption.

The SEL pin and  $\overline{\text{OE}}$  pin have special circuitry that allows them to be driven with a voltage higher than the V<sub>DD</sub> supply voltage. These pins can be driven up to 5.25V with a V<sub>DD</sub> supply in the range of 2.7V to 5.25V.

The SEL pin is internally pulled low through  $4M\Omega$  resistor to ground. The  $\overline{OE}$  pin is internally pulled high through a  $4M\Omega$  resistor to VDD. These pins can be tri-stated by a µProcessor or left floating.

### **Logic Control Voltage Levels**

TABLE 2. LOGIC CONTROL VOLTAGE LEVELS

| V <sub>DD</sub> SUPPLY | LOGIC = ` | `0″ (LOW)                |                         | : = ``1"<br>GH) |

|------------------------|-----------|--------------------------|-------------------------|-----------------|

| RANGE                  | OE        | SEL                      | OE                      | SEL             |

| 2.7V to 3.6V           | ≤0.5V     | ≤0.5V<br>or<br>floating  | ≥1.4V<br>or<br>floating | ≥1.4V           |

| 3.7V to 4.2V           | ≤0.7V     | ≤0.7V<br>or<br>floating  | ≥1.7V<br>or<br>floating | ≥1.7V           |

| 4.3V to 5.25V          | ≤ 0.8V    | ≤ 0.8V<br>or<br>floating | ≥2.0V<br>or<br>floating | ≥2.0V           |

### **HSD1 USB Channel**

If the SEL pin = Logic "0" and the  $\overline{OE}$  pin = Logic "0", high-speed Channel 1 will be ON. The HSD1- and HSD1+ switches are ON and the HSD2- and HSD2+ switches are OFF (high impedance).

When a computer or USB hub is plugged into the common USB connector and Channel 1 is active, a link will be established between the USB 1 transceiver section of the media player and the computer. The device will be able to transmit and receive data from the computer.

### **HSD2 USB Channel**

If the SEL pin = Logic "1" and the  $\overline{OE}$  pin = Logic "0", high-speed Channel 2 will be ON. The HSD2- and HSD2+ switches are ON and the HSD1- and HSD1+ switches are OFF (high impedance).

When a USB cable from a computer or USB hub is connected at the common USB connector and the part has Channel 2 active, a link will be established between the USB 2 driver section of the media player and the computer. The device will be able to transmit and receive data from the computer.

### **All Switches OFF Mode**

If the SEL pin = Logic "0" and the  $\overline{OE}$  pin = Logic "1", all of the switches will turn OFF (high impedance) and the part will be put in a low power mode. In this mode, the part draws only 10µA (max) of current across the operating temperature range. In the low power mode, the persistence checking of the OVP circuitry is de-activated.

If the SEL pin = Logic "1" and the  $\overline{OE}$  pin = Logic "1", all of the switches will turn OFF (high impedance). In this state the complete OTV circuitry is activated.

The all OFF state can be used to switch between the two USB sections of the media player. When disconnecting from one USB device to the other USB device, you can momentarily put the ISL54225 switch in the "all off" state in order to get the computer to disconnect from the one device so it can properly connect to the other USB device when that channel is turned ON.

Whenever the ISL54225 senses a fault condition on the COM pins, all switches will be turned OFF regardless of the voltage levels at the SEL and  $\overline{\text{OE}}$  pins.

### USB 2.0 V<sub>BUS</sub> Short Requirements

The USB specification in section 7.1.1 states a USB device must be able to withstand a  $V_{BUS}$  short (4.4V to 5.25V) or a -1V short to the D+ or D- signal lines when the device is either powered off or powered on for at least 24 hours.

The ISL54225 part has special power-off protection and OVP detection circuitry to meet these short circuit requirements. This circuitry allows the ISL54225 to provide protection to the USB down-stream transceivers connected at its signal pins (HS1D-, HS1D+, HS2D-, HS2D+) to meet the USB specification short circuit requirements.

The power-off protection and OVP circuitry allows the COM pins (D-, D+) to be driven up to 5.25V or down to -5V while the V<sub>DD</sub> supply voltage is in the range of OV to 5.25V. In these overvoltage conditions with a 500 $\Omega$  external VDD resistor, the part draws < 55 $\mu$ A of current into the COM pins and causes no stress/damage to the IC. In addition, all switches are OFF and the shorted V<sub>BUS</sub> voltage will be isolated from getting through to the other side of the switch channels, thereby protecting the USB transceivers.

## **Typical Performance Curves** T<sub>A</sub> = +25°C, Unless Otherwise Specified

FIGURE 11. ON-RESISTANCE vs SUPPLY VOLTAGE vs SWITCH VOLTAGE

FIGURE 13. ON-RESISTANCE vs SWITCH VOLTAGE

FIGURE 10. ON-RESISTANCE vs SUPPLY VOLTAGE vs SWITCH VOLTAGE

FIGURE 12. ON-RESISTANCE vs SWITCH VOLTAGE

FIGURE 14. ON-RESISTANCE vs SWITCH VOLTAGE

## Typical Performance Curves T<sub>A</sub> = +25°C, Unless Otherwise Specified (Continued)

FIGURE 15. ON-RESISTANCE vs SWITCH VOLTAGE

FIGURE 17. DIGITAL SWITCHING POINT vs SUPPLY VOLTAGE

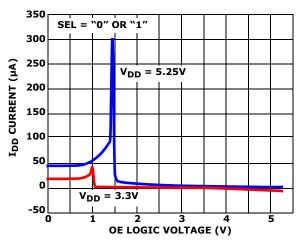

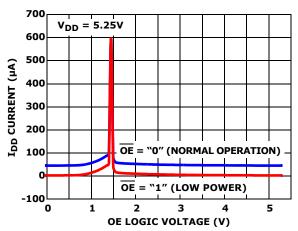

FIGURE 19. IDD vs SEL LOGIC VOLTAGE vs OE STATE

FIGURE 16. ON-RESISTANCE vs SWITCH VOLTAGE

FIGURE 18. I<sub>DD</sub> vs OE LOGIC VOLTAGE vs V<sub>DD</sub>

## **Typical Performance Curves** T<sub>A</sub> = +25°C, Unless Otherwise Specified (Continued)

FIGURE 21. EYE PATTERN: 480Mbps WITH USB SWITCHES IN THE SIGNAL PATH

FIGURE 22. EYE PATTERN: 12Mbps WITH USB SWITCHES IN THE SIGNAL PATH

## Typical Performance Curves T<sub>A</sub> = +25°C, Unless Otherwise Specified (Continued)

FIGURE 23. FREQUENCY RESPONSE

## **Die Characteristics**

### SUBSTRATE AND TDFN THERMAL PAD POTENTIAL (POWERED UP):

GND

### TRANSISTOR COUNT:

1297

### **PROCESS:**

Submicron CMOS

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

|   | DATE   | REVISION | CHANGE           |

|---|--------|----------|------------------|

|   | 7/2/10 | FN7627.0 | Initial Release. |

| L |        | I        | ł                |

## Products

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <u>www.intersil.com/products</u> for a complete list of Intersil product families.

\*For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: <u>ISL54225</u>

To report errors or suggestions for this datasheet, please go to www.intersil.com/askourstaff

FITs are available from our website at http://rel.intersil.com/reports/search.php

© Copyright Intersil Americas LLC 2010. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN7627 Rev 0.00 July 2, 2010

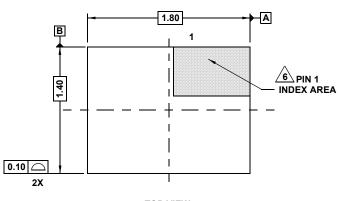

## Package Outline Drawing

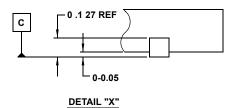

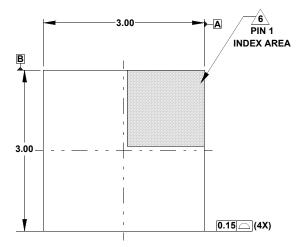

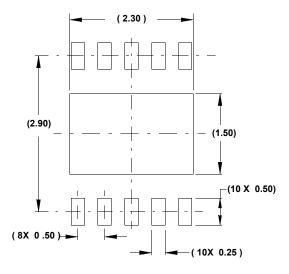

### L10.1.8x1.4A

10 LEAD ULTRA THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 5, 3/10  $\,$

BOTTOM VIEW

TYPICAL RECOMMENDED LAND PATTERN

NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- A Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. JEDEC reference MO-255.

- Chi The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

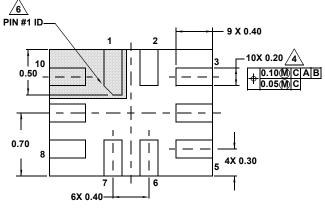

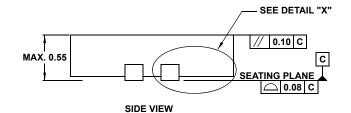

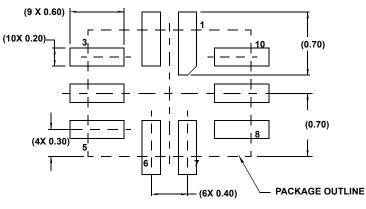

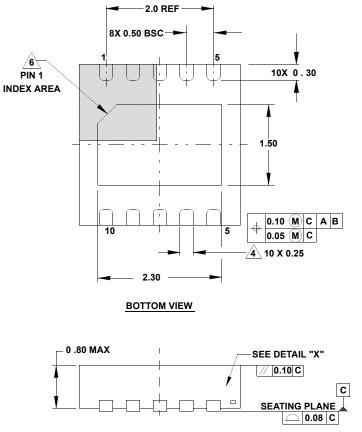

## Package Outline Drawing

### L10.3x3A

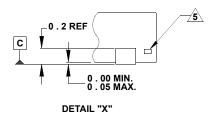

10 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE Rev 5, 3/10

TYPICAL RECOMMENDED LAND PATTERN

NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm\,0.05$  Angular  $\pm2.50^\circ$

- A. Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Compliant to JEDEC MO-229-WEED-3 except exposed pad length (2.30mm).