# Digital Signal Processor with PWM Modulator for Speaker System

### General Description

The NJU26060-04A is a high performance 24-bit digital signal processor included sampling rate converter (SRC), PWM modulators.

The NJU26060-04A provides eala & eala Rebirth, eala Stereo Expander of NJRC Original Sound Enhancement, Dynamic Bass Boost, 256TAP FIR Filter, 12bands PEQ, two systems Limiter. These kinds of sound functions are suitable for TV, minicomponent, CD radio-cassette, speakers system and other audio products.

### Package

NJU26060V-04A

### Features

#### - Hardware

24bit Fixed-point Digital Signal Processing

Clock Frequency : 24.576MHz, Embedded PLL Circuit

Sampling rate converter (SRC) : Fs=8kHz to 192kHz 48kHz

• PWM modulator : 4ch Outputs (2 stereos)

• Digital interface transmitter (DIT) : 1 port

• Digital Audio Interface : 3 Input ports / 2 Output ports (switch over from PWM output)

Digital Audio Format

I<sup>2</sup>S 24bit, Left-justified, Right-justified, BCK: 32/64fs

• Master / Slave Mode

- Sampling Rate Converter: Slave mode

- DSP: Master Mode

• Host Interface : I<sup>2</sup>C Bus (Fast-mode/400kbps)

Power Supply

Input terminal:

Package

V<sub>DD</sub> = 3.3V

5V Input tolerant

SSOP44 (Pb-Free)

### - Software

- Input Signal Selector

- Input Signal Detector

- HPF

- 12Bands PEQ

- 256Taps FIR Filter

- Limiter (SDO0/SDO1)

- DRC (3Bands)

- eala / eala Rebirth

- eala Stereo Expander

- DBB (Dynamic Bass Boost)

- Xover (HPF/LPF)

- BEEP

- SubWoofer Output

- Master Volume

- Input Trimmer / Output Trimmer

<sup>\*</sup> The detail hardware specification of the NJU26060-04A is described in the "NJU26060 Series Hardware Specification".

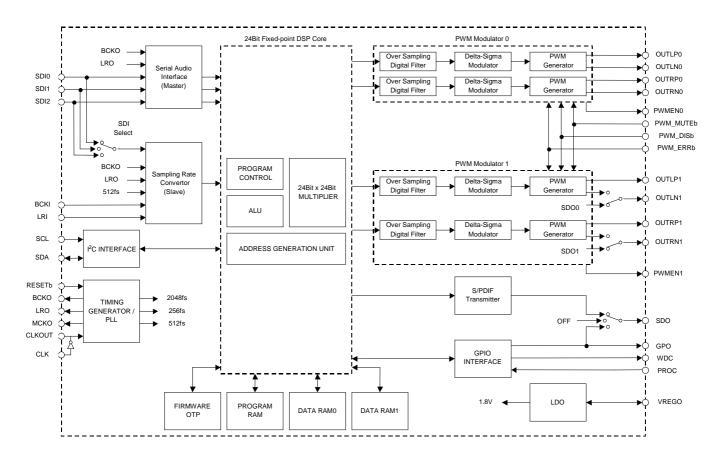

## ■ DSP Block Diagram

Fig 1. NJU26060-04A Hardware Block Diagram

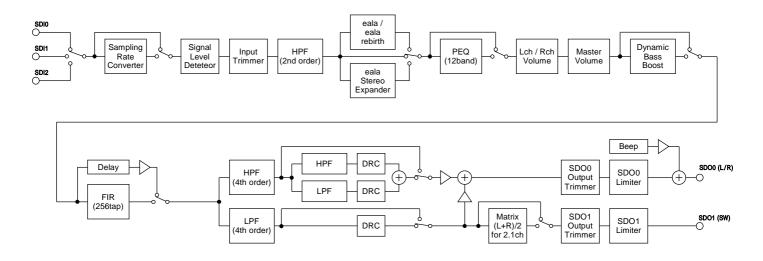

# ■ Function Block Diagram

Fig 2. NJU26060-04A Block Diagram

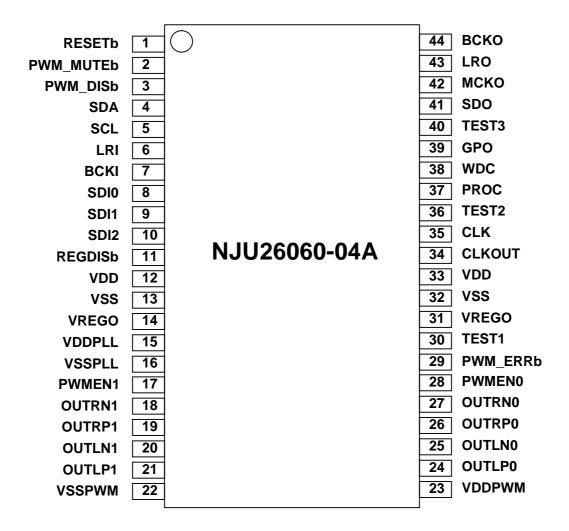

# **■** Pin Configuration

Fig 3. NJU26060-04A Pin Configuration

# NJU26060-04A

# ■ Pin Description

Table 1. Pin Description

| Table I. Pil | Description |     |                                                                                      |

|--------------|-------------|-----|--------------------------------------------------------------------------------------|

| Pin No.      | Symbol      | I/O | Description                                                                          |

| 1            | RESETb      | I   | Reset (RESETb="Low" : DSP Reset)                                                     |

| 2            | PWM_MUTEb   | l+  | PWM Block Mute request input                                                         |

| 3            | PWM_DISb    | l+  | PWM Block Standby request input                                                      |

| 4            | SDA         | OD  | I <sup>2</sup> C serial data I/O (connect to VSS with 3.3kohm when this is not used) |

| 5            | SCL         | ı   | I <sup>2</sup> C clock (connect to VSS when this is not used)                        |

| 6            | LRI         | I-  | LR Clock Input for Fs conversion side                                                |

| 7            | BCKI        | I-  | Bit Clock Input for Fs conversion side                                               |

| 8            | SDI0        | I-  | Audio Data Input 0                                                                   |

| 9            | SDI1        | I-  | Audio Data Input 1                                                                   |

| 10           | SDI2        | I-  | Audio Data Input 2                                                                   |

| 11           | REGDISb     | I   | Built-in Power Supply Enable (connect to VDD)                                        |

| 12           | VDD         | Р   | Power Supply +3.3V                                                                   |

| 13           | VSS         | G   | GND                                                                                  |

| 14           | VREGO       | PI  | Built-in Power Supply Bypass (connect capacitors 10uF and 0.01uF)                    |

| 15           | VDDPLL      | PA  | PLL Power Supply +1.8V (connect to VREGO)                                            |

| 16           | VSSPLL      | GA  | PLL Power Supply GND                                                                 |

| 17           | PWMEN1      | 0   | PWM1 enable output (PWMEN1='1': enable)                                              |

| 18           | OUTRN1      | OP  | PWM1 R- output / Audio Data output 1 (setting Firmware)                              |

| 19           | OUTRP1      | OP  | PWM1 R+ output                                                                       |

| 20           | OUTLN1      | OP  | PWM1 L- output / Audio Data output 0 (setting Firmware)                              |

| 21           | OUTLP1      | OP  | PWM1 L+ output                                                                       |

| 22           | VSSPWM      | GP  | PWM Power Supply GND                                                                 |

| 23           | VDDPWM      | PP  | PWM Power Supply +3.3V (decoupling capacitor is required to stable power supply)     |

| 24           | OUTLP0      | OP  | PWM0 L+ output                                                                       |

| 25           | OUTLN0      | OP  | PWM0 L- output                                                                       |

| 26           | OUTRP0      | OP  | PWM0 R+ output                                                                       |

| 27           | OUTRN0      | OP  | PWM0 R- output                                                                       |

| 28           | PWMEN0      | 0   | PWM0 enable output (PWMEN0='1': enable)                                              |

| 29           | PWM_ERRb    | l+  | PWM block stop request input (PWM_ERRb='0': PWM stop)                                |

| 30           | TEST1       | I   | for Test (connected to VSS)                                                          |

| 31           | VREGO       | PI  | Built-in Power Supply Bypass (connect capacitors 10uF and 0.01uF)                    |

| 32           | VSS         | G   | GND                                                                                  |

| 33           | VDD         | Р   | Power Supply +3.3V                                                                   |

| 34           | CLKOUT      | 0   | OSC Output                                                                           |

| 35           | CLK         | I   | OSC Clock Input                                                                      |

| 36           | TEST2       | I-  | for Test (connected to VSS)                                                          |

| 37           | PROC        | l+  | PROC terminal                                                                        |

| 38           | WDC         | O+  | Watch dog clock terminal                                                             |

| 39           | GPO         | OD  | Signal detection terminal                                                            |

| 40           | TEST3       | I-  | for Test (connected to VSS)                                                          |

| 41           | SDO         | 0   | OFF / DIT output 0 / GPO(same function as pin#39) (selected by command)              |

| 42           | MCKO        | 0   | Master Clock Output for A/D, D/A                                                     |

| 43           | LRO         | 0   | LR clock Output                                                                      |

| 44           | BCKO        | 0   | Bit clock Output                                                                     |

Note: I : Input O: Output

I+ : Input (Pull-up) I -: Input (Pull-down)

OD: Bi-directional (Open Drain) This pin requires a pull-up resistance.

I/O: Bi-directional PI: Built-in Power Supply Bypass

OP: PWM output(supply for VDDPWM)

**NOTICE:** Does not keep the terminal without the pull-up resistance or the pull-down resistance open. The functions of SDIO0 to SDIO2, SDO, OUTxxx depend on the IC specifications.

## Audio Clock

Three kinds of clocks are needed for digital audio data transfer.

- (1) LR clock (LRI, LRO) is needed by serial-data transmission. It is the same as the sampling frequency of a digital audio signal.

- (2) Bit clock (BCKI, BCKO) is needed by serial-data transmission. It becomes the multiple of LR clock.

- (3) Master clock (MCKO) needed by A/D, D/A converter, etc. It becomes the multiple of LR clock. It is not related to serial audio data transmission.

The NJU26060-04A support serial data format that includes 32(32fs) or 64(64fs) BCK clocks.

The NJU26060-04A supplies the clock necessary for digital audio data transmission to an external device as a master device by each terminal of MCKO, BCKO, and LRO. On the other hand, the sampling rate converter that works as a slave device takes digital audio data with the clock input to BCKI and the terminal LRI, and converts the sampling frequency into the clock system composed of MCKO/BCKO/LRO. After internal reset ends as a master clock, the terminal MCKO sets the buffer output or 2 dividing frequency the output of the input clock to the terminal CLK. The stop is also possible according to the command of the firmware.

The NJU26060-04A is used by 512 times the internal operation sampling frequency (It is 24.576MHz in the sampling frequency 48kHz). In that case, NJU26060-04A can output 64 times, 32 times the bit clock to of the LR clock one time the sampling frequency and of each, and 512 times and 256 times the master clock as a mastering device. Table 5 shows the relation of each clock.

The NJU26060 series support two clock frequencies (24.576kHz ,or 22.572kHz) as hardware specifications. However NJU26060-04A acceptable one clock frequency (24.576kHz), cause of the software on NJU26060-04A supports one clock frequency (24.576kHz).

Table 2. Supply Clock for CLK pin Frequency and BCKO,LRO,MCKO

| rable 2: Cappiy Glock for GER pin Frequency and Borto, Erro, morto |                    |                       |  |  |

|--------------------------------------------------------------------|--------------------|-----------------------|--|--|

| Clock Signal                                                       | Multiple Frequency | Clock Frequency       |  |  |

| Clock Signal                                                       |                    | 24.576MHz(for pin#35) |  |  |

| LRO                                                                | 1Fs                | 48kHz                 |  |  |

| BCKO(32Fs)                                                         | 32Fs               | 1.536MHz              |  |  |

| BCKO(64Fs)*                                                        | 64Fs               | 3.072MHz              |  |  |

| MCKO(256Fs)*                                                       | 256Fs              | 12.288MHz             |  |  |

| MCKO(512Fs)                                                        | 512Fs              | 24.576MHz             |  |  |

<sup>\*</sup> default for starting up

### Serial Audio Data Input/Output

Audio interface of the NJU26060-04A includes three data input ports: SDI0, SDI1 and SDI2 (Table 3), and three data output ports: SD00, SDO1 and SDO2 (Table 4).

Table 3. Serial Audio Input Pin Description

|         |        | •                  |

|---------|--------|--------------------|

| Pin No. | Symbol | Description        |

| 8       | SDI0   | Audio Data Input 0 |

| 9       | SDI1   | Audio Data Input 1 |

| 10      | SDI2   | Audio Data Input 2 |

Table 4. Serial Audio Output Pin Description

| Pin No. | Symbol | Description               |

|---------|--------|---------------------------|

| 20      | OUTLN1 | Audio Data Output 0 (L/R) |

| 18      | OUTRN1 | Audio Data Output 1 (SW)  |

| 41      | SDO    | OFF                       |

Pin#20, 18 can be change the function to PWM1 output. Pin#41 can be change the function to DIT (output 0) or GPO output (the function is same as Pin#39). Refer to table1.

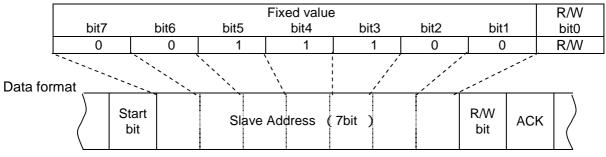

### ■ I<sup>2</sup>C bus Interface

I<sup>2</sup>C bus interface transfers data to the SDA pin and clocks data to the SCL pin. SDA pin is a bi-directional open drain and requires a pull-up resister.

The slave address is set up as Table 5. When the initialization is finished (After reset NJU26060-04A), NJU26060-04A can be communicated with Host. However until finished the initialization, the Host can't be get any correct responses.

**Note :** The serial host interface supports "Standard-Mode (100kbps)" and "Fast-Mode (400kbps)" I<sup>2</sup>C bus data transfer.

Table 5. Serial Host Interface Pin Description

\*: On "R/W bit", "0"="W", "1"="R".

# ■ General-purpose in/out pin

The NJU26060 Series has general-purpose in/out pin. On NJU26060-04A, these terminals operate as below functions (Table 6).

Table 6. General-purpose in/out pin and pin disposal

| Table of Contral parpose in Care pin and pin dispession |                        |                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No.                                              | Symbol                 | Description                                                                                                                                                                                                                                                                                                     |

| 40                                                      | TEST3<br>(Pull-down I) | Terminal for a test. Connect to VSS                                                                                                                                                                                                                                                                             |

| 39                                                      | GPO<br>(O)             | Signal detection terminal. Default is Hi-Z. Connect to VDD with pull-up resistor. It outputs Low If it detects no signal.                                                                                                                                                                                       |

| 38                                                      | WDC<br>(O)             | Output of the watchdog clock. This terminal is toggled between "Low" and "High" in the audio processing. Thus, this terminal notifies the correct operating to another devices. If monitored by watchdog IC, microcontroller, and so on, abnormal condition can be detected. The rate of WDC is 100msec (10Hz). |

| 37                                                      | PROC (I)               | PROC terminal, H: However reset the NJU26060-04A, signal processing is not started. To start signal processing, start command is required. L: After reset the NJU26060-04A, signal processing is started (default setting: master volume is 0dB).                                                               |

# **Command Table**

Table 7. Command table

| Table 7. | Command table                                  |

|----------|------------------------------------------------|

| No.      | Function                                       |

| 1        | Set Task Command                               |

| 2        | Samplerate Config Command                      |

| 3        | Smooth Control Setup Command                   |

| 4        | Input Select Command                           |

| 5        | Trimmer Command                                |

| 6        | Eala Setup Command                             |

| 7        | DBB LFE Filter Setup Command                   |

| 8        | PEQ Config Command                             |

| 9        | HPF For Input FREQ Select Command              |

| 10       | HPF For L/R FREQ Select Command                |

| 11       | LPF For SW FREQ Select Command                 |

| 12       | HPF For DRC(L/R) FREQ Select Command           |

| 13       | LPF For DRC(L/R) FREQ Select Command           |

| 14       | DRC For HPF(L/R) Time Constant Setting Command |

| 15       | DRC For LPF(L/R) Time Constant Setting Command |

| 16       | DRC For SW Time Constant Setting Command       |

| 17       | DBB Time Constant Setting Command              |

| 18       | DRC For HPF(L/R) Level Setting Command         |

| 19       | DRC For LPF(L/R) Level Setting Command         |

| 20       | DRC For SW Level Setting Command               |

| 21       | DBB Level Setting Command                      |

| 22       | L-Ch FIR Coef Load Command                     |

| 23       | R-Ch FIR Coef Load Command                     |

| 24       | System Status Config Command                   |

| 25       | PWM0 Status Config Command                     |

| 26       | PWM1 Status Config Command                     |

| 27       | No Signal Detection Setup Command              |

| 28       | SRC Reset Wait Setup Command                   |

| 29       | Delay Setup Command                            |

| 30       | No Signal Counter Read Command                 |

| 31       | No Signal Counter Reset Command                |

| 32       | No Signal Detection Output Enable Command      |

| 33       | No Signal Detection Output Disable Command     |

| 34       | Beep Command                                   |

| 35       | FIR Coef Update Command                        |

| 36       | Software Reset Command                         |

| 37       | Firmware Version Number Command                |

| 38       | Firmware Revision Number Command               |

| 39       | PWM/SRC Status Read Command                    |

| 40       | Start Command with Mute                        |

| 41       | Start Command with Unmute                      |

| 42       | No Operation Command                           |

|          |                                                |

Notes: In respect to detail command information, request New Japan Radio Co., Ltd.

#### [CAUTION]

[CAUTION]

The specifications on this databook are only given for information, without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NJR:

NJU26060-04A