## IRS2552D CCFL/EEFL BALLAST CONTROLLER IC

#### **Features**

- Drives up to two IGBT/MOSFET power devices

- Integrated programmable oscillator

- Soft start function

- 15.6 V voltage clamp on V<sub>CC</sub>

- Micro-power startup

- 0 V to 5 V input analog dimming

- Programmable ignition frequency

- Programmable ignition time

- Lamp current control

- Programmable deadtime

- Supports multi-lamp operation

- Burst dimming with soft start at every burst

- Latched open circuit protection

- Integrated bootstrap functionality

- Excellent latch immunity on all inputs & outputs

- Integrated ESD protection on all pins

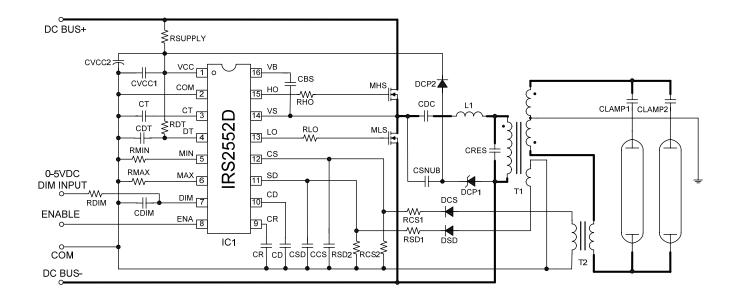

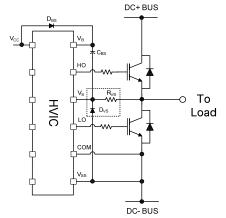

## **Typical Application**

CCFL/EEFL inverter

## **Product Summary**

| i roddot odiiiiidi y                        |                 |

|---------------------------------------------|-----------------|

| Topology                                    | Half-Bridge     |

| V <sub>OFFSET</sub>                         | 600 V           |

| V <sub>OUT</sub>                            | V <sub>CC</sub> |

| I <sub>O+</sub> & I <sub>O-</sub> (typical) | 300 mA & 450 mA |

| Deadtime (programmable)                     | 500ns ~ 2μs     |

**Package Options**

## **Typical Application Diagram**

# International TOR Rectifier

| Table of Contents                              | Page |

|------------------------------------------------|------|

| Typical Application Diagram                    | 1    |

| Qualification Information                      | 4    |

| Absolute Maximum Ratings                       | 5    |

| Recommended Operating Conditions               | 6    |

| Electrical Characteristics                     | 7    |

| Functional Block Diagram                       | 10   |

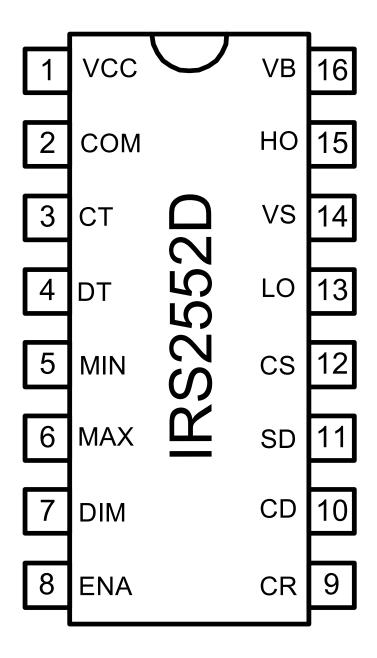

| Lead Definitions                               | 12   |

| Lead Assignments                               | 13   |

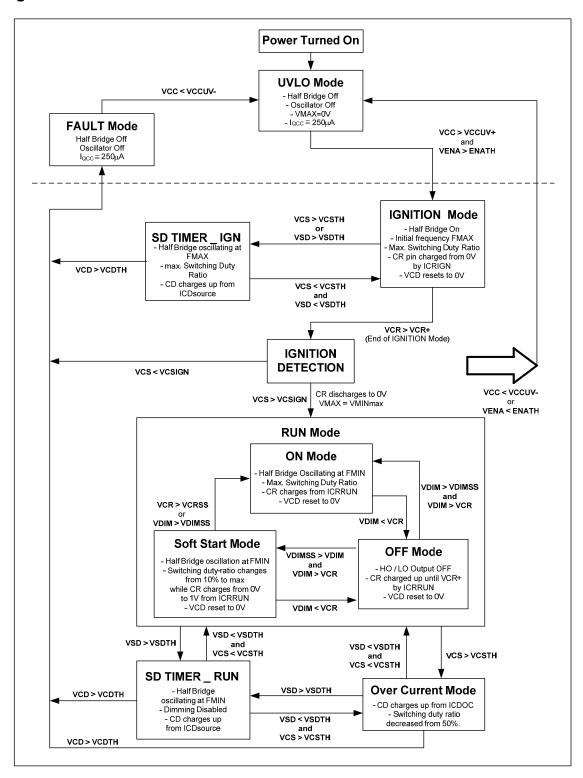

| State Diagram                                  | 14   |

| Application Information and Additional Details | 15   |

| Package Details                                | 29   |

| Part Marking Information                       | 30   |

| Ordering Information                           | 32   |

## **Description**

The IR\$2552D incorporates a high voltage half-bridge gate driver with a front end that incorporates full control functionality for CCFL/EEFL ballasts. Includes a programmable ignition and supports dimming via analog or PWM control voltage. HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The output driver features a high pulse current buffer stage designed for minimum driver cross-conduction. Noise immunity is achieved with low di/dt peak of the gate drivers, and with an undervoltage lockout hysteresis of approximately 1 V. The IR\$2552D also includes protection features for over-current and over-voltage of the lamps.

## Qualification Information<sup>†</sup>

|                            |                  | Industrial <sup>††</sup> |                                        |  |  |  |

|----------------------------|------------------|--------------------------|----------------------------------------|--|--|--|

|                            |                  |                          |                                        |  |  |  |

|                            |                  | (per JEDEC JESD 47E)     |                                        |  |  |  |

| Qualification Level        |                  |                          | nily of ICs has passed JEDEC's         |  |  |  |

|                            |                  |                          | IR's Consumer qualification level is   |  |  |  |

|                            |                  | granted by extension of  | of the higher Industrial level.        |  |  |  |

| Moisture Sensitivity Level |                  | SOIC16                   | MSL3 <sup>†††</sup>                    |  |  |  |

|                            |                  | 301016                   | (per IPC/JEDEC J-STD-020C)             |  |  |  |

|                            |                  | PDIP16                   | Not applicable                         |  |  |  |

|                            |                  | PDIP16                   | (non-surface mount package style)      |  |  |  |

|                            | Machine Model    | Class C                  |                                        |  |  |  |

| ESD                        | Macrime Model    | (per JEDEC st            | andard EIA/JESD22-A115-A)              |  |  |  |

| E3D                        | Human Body Model | Class 3A                 |                                        |  |  |  |

|                            | numan body woder |                          | (per EIA/JEDEC standard JESD22-A114-B) |  |  |  |

| IC Latch Un Tast           | IC Latab Un Taat |                          | Class I, Level A                       |  |  |  |

| IC Latch-Up Test           |                  |                          | (per JESD78A)                          |  |  |  |

| RoHS Compliant             |                  | Yes                      |                                        |  |  |  |

- † Qualification standards can be found at International Rectifier's web site <a href="http://www.irf.com/">http://www.irf.com/</a>

- †† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

- ††† Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

www.irf.com © 2009 International Rectifier

## **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                                                                          |                                   | Min.                | Max.                  | Units |

|---------------------|-------------------------------------------------------------------------------------|-----------------------------------|---------------------|-----------------------|-------|

| $V_{B}$             | High-side floating supply voltage                                                   | High-side floating supply voltage |                     | 625                   |       |

| V <sub>s</sub>      | High-side floating supply offset voltage                                            |                                   | V <sub>B</sub> - 25 | $V_{B} + 0.3$         |       |

| $V_{H}$             | High-side floating output voltage                                                   |                                   | $V_{\rm S} - 0.3$   | V <sub>B</sub> + 0.3  |       |

| $V_L$               | Low-side output voltage                                                             |                                   | -0.3                | V <sub>CC</sub> + 0.3 |       |

| V <sub>co</sub>     | VCO pin voltage                                                                     |                                   | -0.3                | $V_{CC} + 0.3$        |       |

| V <sub>CT</sub>     | CT pin voltage                                                                      |                                   | -0.3                | V <sub>CC</sub> + 0.3 |       |

| $V_{\mathrm{DT}}$   | DT pin voltage                                                                      |                                   | -0.3                | $V_{CC} + 0.3$        | V     |

| MIN                 | MIN pin voltage                                                                     |                                   | -0.3                | $V_{CC} + 0.3$        |       |

| DIM                 | DIM pin voltage                                                                     |                                   | -0.3                | $V_{CC} + 0.3$        |       |

| CR                  | CR pin voltage                                                                      |                                   | -0.3                | V <sub>CC</sub> + 0.3 |       |

| CD                  | CD pin voltage                                                                      |                                   | -0.3                | V <sub>CC</sub> + 0.3 |       |

| SD                  | SD pin voltage                                                                      |                                   | -0.3                | V <sub>CC</sub> + 0.3 |       |

| CS                  | CS pin voltage                                                                      |                                   | -0.3                | $V_{CC} + 0.3$        |       |

| I <sub>cc</sub>     | Supply current <sup>†</sup>                                                         |                                   |                     | 25                    | mA    |

| dV <sub>S</sub> /dt | Allowable offset voltage slew rate                                                  |                                   | -50                 | 50                    | V/ns  |

| P <sub>D</sub>      | Package power dissipation @ T <sub>A</sub> ≤ +25                                    | 16L-PDIP                          |                     | 1.3                   | W     |

| • В                 | °C 16L-SOIC                                                                         |                                   |                     | 1.4                   | • • • |

| Rou                 | $R_{\Theta JA}$ Thermal resistance, junction to ambient $\frac{16L-PDIP}{16L-SOIC}$ |                                   |                     | 70                    | °C/W  |

|                     |                                                                                     |                                   |                     | 82                    | 0,,,  |

| T <sub>J</sub>      | Junction temperature                                                                |                                   | -55                 | 150                   |       |

| T <sub>s</sub>      | Storage temperature                                                                 |                                   | -55                 | 150                   | °C    |

| $T_L$               | Lead temperature (soldering, 10 seconds)                                            |                                   |                     | 300                   |       |

<sup>†</sup> This IC contains a voltage clamp structure between the chip  $V_{CC}$  and COM which has a nominal breakdown voltage of 15.6 V. Please note that this supply pin should not be driven by a DC, low impedance power source greater than the  $V_{CLAMP}$  specified in the Electrical Characteristics section.

www.irf.com © 2009 International Rectifier

**Recommended Operating Conditions**For proper operation the device should be used within the recommended conditions.

| Symbol          | Definition                                            | Min.                     | Max.        | Units |

|-----------------|-------------------------------------------------------|--------------------------|-------------|-------|

| $V_{BS}$        | High-side floating supply voltage                     | $V_{CC} - 0.7$           | $V_{CLAMP}$ |       |

| V <sub>s</sub>  | Steady-state high-side floating supply offset voltage | -3.0 <sup>†</sup>        | 600         | V     |

| V <sub>cc</sub> | Supply voltage                                        | V <sub>CCUV+</sub> +0.1V | $V_{CLAMP}$ |       |

| I <sub>cc</sub> | Supply current                                        | ††                       | 10          | mA    |

| $T_J$           | Junction temperature                                  | -40                      | 125         | °C    |

Care should be taken to avoid output switching conditions where the VS node flies inductively below ground by more than 5 V.

## **Recommended Component Values**

| Symbol           | Component              | Min. | Max. | Units |

|------------------|------------------------|------|------|-------|

| R <sub>MIN</sub> | MIN pin resistor value | 5    |      |       |

| R <sub>MAX</sub> |                        |      |      | kΩ    |

| $R_{DT}$         | DT pin resistor value  | 22   |      |       |

| $C_T$            | CT pin capacitor value | 330  |      | pF    |

| $C_{DT}$         | DT pin capacitor value | 47   |      | рі    |

| $C_R$            | CR pin capacitor value | 1    |      | nF    |

| $C_D$            | CD pin capacitor value | 1    |      | 111   |

© 2009 International Rectifier www.irf.com

<sup>††</sup> Enough current should be supplied to the  $V_{CC}$  pin of the IC to keep the internal 15.6 V zener diode clamping the voltage at this pin.

## **Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 14 V,  $C_T$  = 1 nF and  $T_A$  = 25 °C unless otherwise specified. The input parameters are referenced to COM. The  $V_O$  and  $I_O$  parameters are referenced to COM and are applicable to the respective output leads: HO or LO.

| Symbol               | Definition                                                   | Min  | Тур  | Max  | Units | Test Conditions                                     |  |

|----------------------|--------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------|--|

| Low Voltag           | ge Supply Characteristics                                    |      |      |      |       |                                                     |  |

| V <sub>CCUV</sub> +  | Rising V <sub>CC</sub> undervoltage lockout threshold        | 9.5  | 10.5 | 11.5 |       |                                                     |  |

| V <sub>CCUV</sub> -  | Falling V <sub>CC</sub> undervoltage lockout threshold       | 8.5  | 9.5  | 10.5 | V     | N/A                                                 |  |

| V <sub>CCUVHYS</sub> | V <sub>CC</sub> undervoltage lockout hysteresis              | 0.5  | 1    | 1.5  |       |                                                     |  |

| I <sub>QCCUV</sub>   | Micropower startup V <sub>CC</sub> supply current            |      | 300  | 350  | μA    | V <sub>CC</sub> = V <sub>CCUV+</sub> -100 mV rising |  |

| I <sub>QCC</sub>     | Quiescent V <sub>CC</sub> supply current                     |      | 4.0  | 4.5  |       | $R_{MIN}$ = 12 k $\Omega$ , RUN<br>MODE CT = 0 V    |  |

| I <sub>QCCFLT</sub>  | V <sub>CC</sub> supply current                               |      | 0.9  | 1.3  | mA    | Fault mode                                          |  |

| I <sub>CC,FMIN</sub> | V <sub>CC</sub> current @ f <sub>osc</sub> = fMIN            |      | 4.7  | 5.3  |       | $R_{MIN}$ = 12 k $\Omega$ , RUN MODE                |  |

| $V_{CLAMP}$          | V <sub>CC</sub> clamp voltage                                | 14.6 | 15.6 | 16.6 | V     | I <sub>CC</sub> = 19 mA                             |  |

| Floating S           | upply Characteristics                                        |      |      |      |       |                                                     |  |

| I <sub>QBSUV</sub>   | Micropower startup V <sub>BS</sub> supply current            |      | 6    | 20   | μA    | $V_{CC} \le V_{CCUV}$ , $V_{CC} = V_{BS}$           |  |

| I <sub>BS</sub>      | V <sub>BS</sub> supply current                               |      | 1000 | 1200 |       | HO oscillating                                      |  |

| V <sub>BSUV+</sub>   | V <sub>BS</sub> supply undervoltage positive going threshold | 6.5  | 7.5  | 8.5  | V     | N/A                                                 |  |

| $V_{BSUV}$           | V <sub>BS</sub> supply undervoltage negative going threshold | 6.0  | 7.0  | 8.0  | V     | IN/A                                                |  |

| I <sub>LK</sub>      | Offset supply leakage current                                |      |      | 50   | μΑ    | $V_{B} = V_{S} = 600 \text{ V}$                     |  |

| Oscillator           | I/O Characteristics                                          |      |      |      |       |                                                     |  |

| f <sub>MIN</sub>     | Minimum oscillator frequency                                 | 36.5 | 39   | 42.5 | kHz   | $R_{MIN}$ = 12 k $\Omega$ , RUN MODE                |  |

| $f_{MAX}$            | Maximum oscillator frequency                                 | 67   | 69   | 71   | KI IZ | $R_{MAX}$ = 6.8 k $\Omega$ , IGNITION MODE          |  |

| V <sub>CT+</sub>     | Upper CT ramp voltage threshold                              | 4.8  | 5.0  | 5.2  | V     | NI/A                                                |  |

| V <sub>CT-</sub>     | Lower CT ramp voltage threshold                              |      | 0    |      | V     | N/A                                                 |  |

| I <sub>CT</sub>      | CT pin source current                                        | 350  | 410  | 470  | μΑ    | R <sub>MIN</sub> =12 kΩ, RUN<br>MODE                |  |

| $V_{MIN}$            | VMIN pin voltage                                             | 4.8  | 5.0  | 5.2  |       |                                                     |  |

| $V_{MAX}$            | VMAX pin voltage                                             | 4.8  | 5.0  | 5.2  | V     | N/A                                                 |  |

| $V_{MIN,FLT}$        | VMIN voltage in fault mode                                   |      | 0    |      | , v   | IN/A                                                |  |

| $V_{MAX,FLT}$        | VMAX voltage in fault mode                                   |      | 0    |      |       |                                                     |  |

## **Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 14 V,  $C_T$  = 1 nF and  $T_A$  = 25 °C unless otherwise specified. The input parameters are referenced to COM. The  $V_O$  and  $I_O$  parameters are referenced to COM and are applicable to the respective output leads: HO or LO.

| Symbol                 | Definition                                                    | Min  | Тур             | Max  | Units | Test Conditions                                  |

|------------------------|---------------------------------------------------------------|------|-----------------|------|-------|--------------------------------------------------|

| Ignition               |                                                               |      |                 |      |       |                                                  |

| I <sub>CR,IGN</sub>    | Source current at CR pin in IGN mode                          | 3.7  | 4.5             | 5.3  | μА    | $R_{MIN}$ = 12 k $\Omega$ , IGNITION MODE        |

| V <sub>CS,IGN</sub>    | Ignition detection threshold                                  | 0.57 | 0.6             | 0.63 | V     | N/A                                              |

| Gate Drive             | er Output Characteristics                                     |      | •               |      |       |                                                  |

| V <sub>OH</sub>        | High-level output voltage, V <sub>BIAS</sub> – V <sub>O</sub> |      | V <sub>CC</sub> |      | V     | L = 0.A                                          |

| V <sub>OL</sub>        | Low-level output voltage, VO                                  |      | COM             |      |       | $I_O = 0 A$                                      |

| $V_{OL,UV}$            | UV-mode output voltage, VO                                    |      | СОМ             |      | mV    | $I_O = 0 A,$ $V_{CC} \le V_{CCUV}$               |

| t <sub>R</sub>         | Output rise time                                              |      | 80              | 150  | ns    | N/A                                              |

| t <sub>F</sub>         | Output fall time                                              |      | 45              | 100  | 115   | IN/A                                             |

| $t_D$                  | Output deadtime (HO or LO)                                    | 1.0  | 1.1             | 1.2  | μs    | $R_{DT}$ = 2.2 k $\Omega$ ,<br>$C_{DT}$ = 1 nF   |

| I <sub>O+</sub>        | Output source current                                         |      | 300             |      | m ^   | NI/A                                             |

| I <sub>O-</sub>        | Output sink current                                           |      | 450             |      | mA    | N/A                                              |

| Bootstrap              | FET Characteristics                                           |      |                 |      |       |                                                  |

| $V_{B,ON}$             | V <sub>B</sub> when the bootstrap FET is on                   | 13.2 | 13.5            |      | V     | N/A                                              |

| $I_{B,CAP}$            | V <sub>B</sub> source current when FET is on                  | 40   | 55              |      | mA    | $C_{BS} = 0.1  \mu F$                            |

| I <sub>B,10V</sub>     | V <sub>B</sub> source current when FET is on                  | 9    | 12              |      | mA    | V <sub>B</sub> = 10 V                            |

| Shutdown               |                                                               |      |                 |      |       |                                                  |

| $V_{SD,TH}$            | Shutdown threshold at SD pin                                  | 1.9  | 2.0             | 2.1  | V     | N/A                                              |

| I <sub>CD,source</sub> | CD pin source current                                         | 3.7  | 4.5             | 5.3  | μΑ    | $V_{SD}>V_{SD,TH},$ $R_{MIN}=12 \text{ k}\Omega$ |

| $V_{\text{CD,TH}}$     | Threshold at which CD triggers shutdown                       | 4.8  | 5.0             | 5.2  | V     | V <sub>CC</sub> = 14 V                           |

## **Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 14 V,  $C_T$  = 1 nF and  $T_A$  = 25 °C unless otherwise specified. The input parameters are referenced to COM. The  $V_O$  and  $I_O$  parameters are referenced to COM and are applicable to the respective output leads: HO or LO.

| Symbol              | Definition                                                           | Min  | Тур  | Max  | Units | Test Conditions                                           |

|---------------------|----------------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------------|

| Over-Curr           | ent Compensation                                                     |      |      |      |       |                                                           |

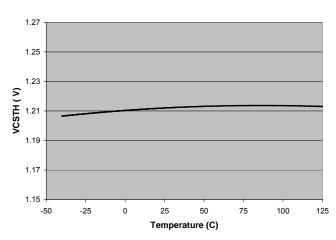

| $V_{CS,TH}$         | Current compensation threshold at CS pin                             | 1.15 | 1.21 | 1.27 | V     | N/A                                                       |

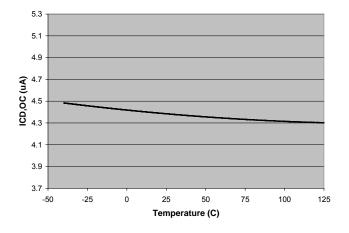

| I <sub>CD,OC</sub>  | Source current at CD pin when the IC is in current compensation mode | 3.7  | 4.5  | 5.3  | μΑ    | $V_{CS} > V_{CS,TH},$ $R_{MIN} = 12 \text{ k}\Omega$      |

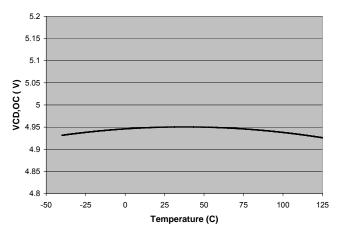

| $V_{\text{CD,oc}}$  | Voltage on CD where duty cycle reaches minimum                       | 4.8  | 5.0  | 5.2  | V     | N/A                                                       |

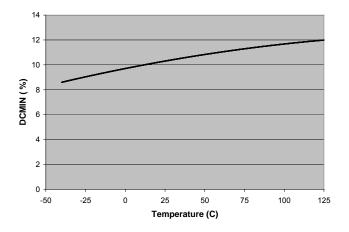

| DC <sub>MIN</sub>   | Minimum HO duty cycle                                                |      | 10%  |      |       | V <sub>CD</sub> = 4.7 V,<br>RUN MODE                      |

| Dimming             |                                                                      |      |      |      |       |                                                           |

| V <sub>CR+</sub>    | CR pin upper threshold voltage                                       | 4.8  | 5.0  | 5.2  | V     | N/A                                                       |

| $V_{CR-}$           | CR pin lower threshold voltage                                       |      | 0.2  |      | \ \   | IN/A                                                      |

| I <sub>CR,RUN</sub> | Source current at CR pin in RUN mode                                 | 125  | 150  | 175  | μΑ    | $R_{MIN} = 12 k\Omega$                                    |

| f <sub>CR</sub>     | Frequency at CR pin                                                  | 240  | 310  | 370  | Hz    | $C_R$ = 100 nF,<br>RUN MODE,<br>$R_{MIN}$ = 12 k $\Omega$ |

| Soft Start          |                                                                      | - 11 |      |      |       |                                                           |

| $DC_{MIN}$          | Minimum HO duty cycle                                                |      | 10%  |      |       | $V_{CR} = 0 V,$ $V_{DIM} < V_{DIM,SS}$                    |

| $V_{\text{CR,SS}}$  | End of soft start voltage                                            | 0.88 | 0.96 | 1.04 | V     | $V_{DIM} < V_{DIM,SS}$                                    |

| $V_{DIM,SS}$        | Soft start disable threshold                                         |      | 4.8  |      | V     | N/A                                                       |

| Enable              |                                                                      |      |      |      |       |                                                           |

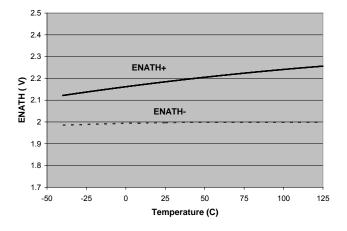

| $V_{ENATH}$         | Enable threshold                                                     | 1.9  | 2.2  | 2.5  | V     | N/A                                                       |

| V <sub>ENAHYS</sub> | Enable hysteresis                                                    |      | 200  |      | mV    | IN/A                                                      |

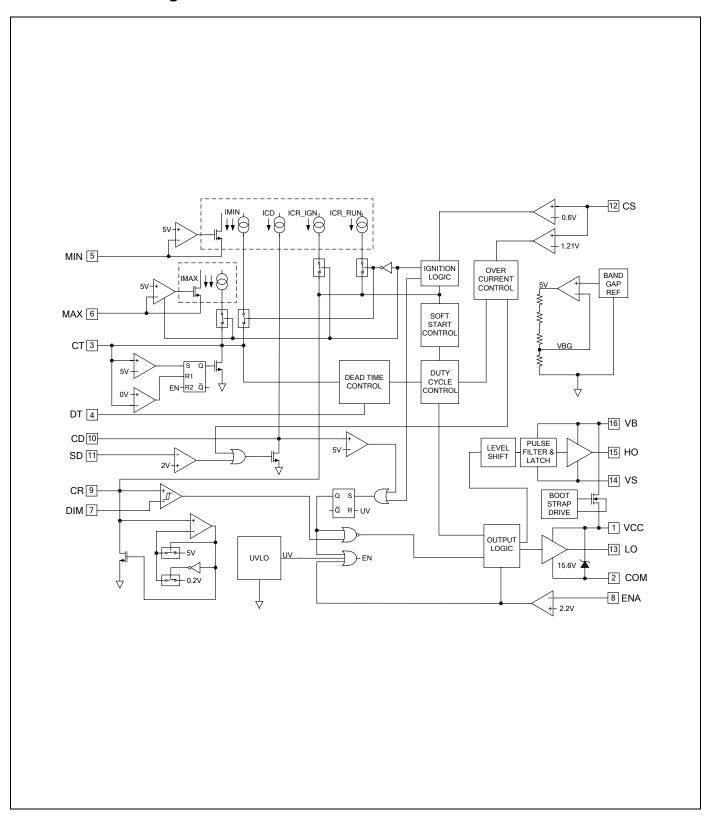

## **Functional Block Diagram**

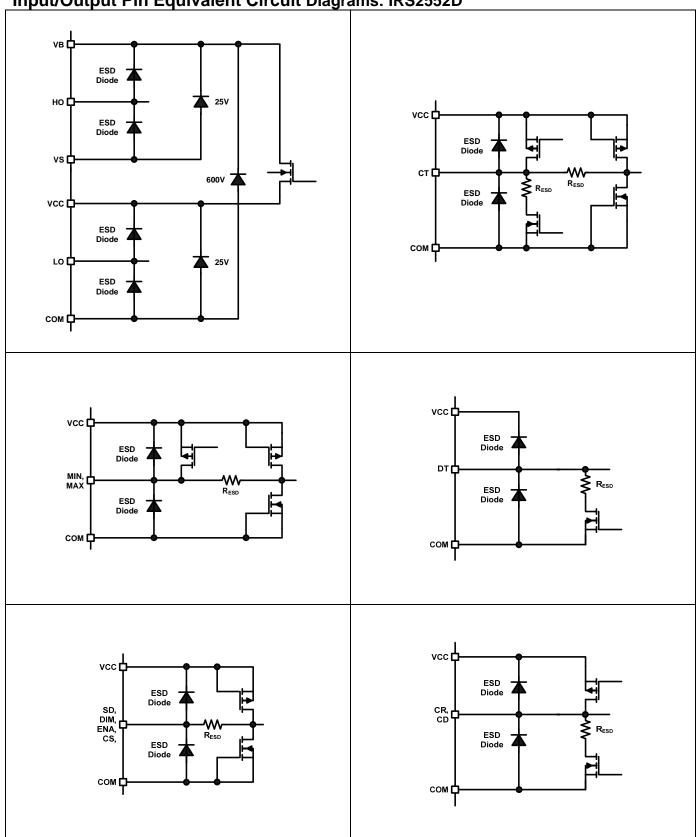

Input/Output Pin Equivalent Circuit Diagrams: IRS2552D

## **Lead Definitions**

| Symbol | Description                                                          |

|--------|----------------------------------------------------------------------|

| VCC    | Logic and internal gate drive supply voltage                         |

| COM    | IC power and signal ground                                           |

| СТ     | Oscillator timing capacitor                                          |

| DT     | Independent dead time R and C                                        |

| MIN    | RFMIN sets running frequency                                         |

| MAX    | RFMAX sets ignition mode frequency                                   |

| DIM    | 0 to 5 V DC burst mode dimming control input                         |

| ENA    | Chip Enable (2 V logic threshold)                                    |

| CR     | Burst dimming ramp                                                   |

| CD     | Shutdown delay timing                                                |

| SD     | Open load detection                                                  |

| CS     | Ignition detection (0.6 V threshold), over-current (1.2 V threshold) |

| LO     | Low side output                                                      |

| VS     | Half bridge                                                          |

| НО     | High side output                                                     |

| VB     | High side floating supply                                            |

## **Lead Assignments**

## State Diagram<sup>†</sup>

† All values are typical. Applies to application circuit on page 1.

## **Application Information and Additional Details**

Information regarding the following topics is included as subsections within this section of the datasheet.

- IGBT/MOSFET Gate Drive

- Undervoltage Lockout Protection

- Oscillator

- Deadtime

- Ignition

- Run Mode

- Lamp Current Control

- Frequency, Current and Deadtime Calculation

- Dimming Function

- Soft Start

- PCB Layout Tips

- Additional Documentation

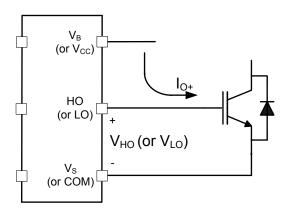

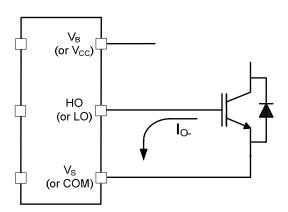

#### **IGBT/MOSFET Gate Drive**

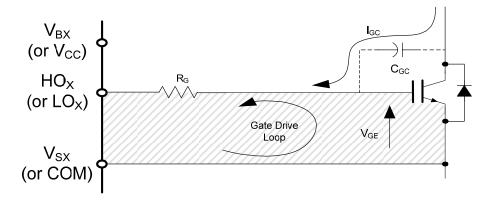

The IRS2552D HVICs are designed to drive up to two MOSFET or IGBT power devices. Figures 1 and 2 illustrate several parameters associated with the gate drive functionality of the HVIC. The output current of the HVIC, used to drive the gate of the power switch, is defined as  $I_O$ . The voltage that drives the gate of the external power switch is defined as  $V_{HO}$  for the high-side power switch and  $V_{LO}$  for the low-side power switch; this parameter is sometimes generically called  $V_{OUT}$  and in this case does not differentiate between the high-side or low-side output voltage.

Figure 1: HVIC sourcing current

Figure 2: HVIC sinking current

#### **Undervoltage Lock-Out**

The IRS2552D includes an under voltage lockout circuit such that it remains in micro-power mode until the voltage at VCC pin exceeds the  $V_{\text{CCUV+}}$  threshold. When  $V_{\text{CC}}$  exceeds the  $V_{\text{CCUV+}}$  threshold the IRS2552D oscillator starts up and gate drive signals appear at the LO and HO outputs, provided the ENABLE pin is connected to a voltage source above  $V_{\text{ENATH}}$ . The LO output will always go high first in order to pre-charge the bootstrap capacitor before the IRS2552D begins normal operation.

#### **Oscillator**

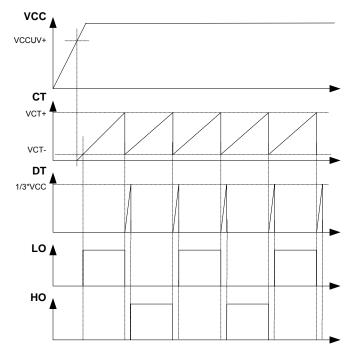

During UVLO and shutdown and the voltage at the MIN and MAX pins remain at 0 V. When  $V_{CC}$  is raised above  $V_{CCUV^+}$  the oscillator will start and LO and HO will produce output drive waveforms at frequency  $F_{MAX}$ . The MAX pin sources 5 V and the resistance connected from this point to COM determines the  $C_T$  charging current and consequently the frequency.  $R_{MIN}$  is always connected from the MIN pin to COM, which sets the RUN mode frequency. In IGNITION mode the MAX pin supplies 5 V to  $R_{MAX}$ , which is connected to COM setting a higher  $C_T$  charging current and consequently a higher ignition frequency, as  $R_{MAX}$  is smaller than  $R_{MIN}$ . In RUN mode the MAX pin is no longer active and the voltage will drop to 0V.  $C_T$  charges until the voltage reaches the 5 V threshold and then it is discharged rapidly to  $V_{CT}$ . It then begins to charge again, repeating this sequence and producing a saw tooth waveform. The MIN pin sources 5 V during IGNITION and RUN modes. The current flowing through  $F_{MIN}$  to COM determines the charging current of  $C_T$  during RUN mode and also serves as a current reference for the currents supplied from the CD and CR pins.

Figure 3: Oscillator waveforms

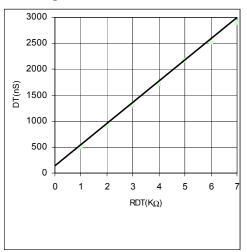

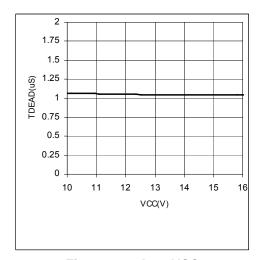

#### **Deadtime**

In the IRS2552D the dead time is determined by an independent external timing circuit comprising of  $R_{DT}$  and  $C_{DT}$  and is not affected by the values of  $C_T$ ,  $R_{MIN}$  or  $R_{MAX}$ . The DT pin voltage is held at COM when LO or HO is high.  $C_{DT}$  is charged through  $R_{DT}$ , which is connected to VCC, when DT is internally disconnected from COM at the start of the dead time. The dead time ends when  $C_{DT}$  has charged to 1/3  $V_{CC}$ . This allows the dead time to remain consistent over the working range of  $V_{CC}$ , i.e. from UVLO+ to the clamp voltage of 15.6  $V_{CC}$ .

#### Ignition

During the IGNITION phase the  $C_R$  capacitor is charged through an internal current source ICR\_IGN. When  $C_R$  reaches  $V_{CR^+}$  then if the voltage at CS is greater than  $VCS_{IGN}$ , the IRS2552D will enter RUN mode. If the voltage at the CS pin is less than  $VCS_{IGN}$  the IRS2552D will enter FAULT mode whereby LO and HO will both go low and the IRS2552D will shut down until  $V_{CC}$  is reduced below  $V_{CCUV^-}$  and then increased above  $V_{CCU^+}$ . The ignition function is achieved by applying a frequency somewhat above resonance to the output step up transformer and resonant load. This should develop sufficient voltage across the lamps to allow partial ignition and some arc current to flow. The combined lamp current is fed back to the CS pin through a suitable isolating network to determine whether the lamps have ignited successfully. If a successful ignition is detected after the voltage at  $C_R$  has reached  $V_{CR^+}$  then  $R_{MAX}$  is disconnected inside the IRS2552D and the frequency will switch immediately to

to  $F_{MIN}$ , therefore applying maximum power to the lamps. At this point the burst mode dimming function will be enabled.

#### **Run Mode**

In RUN mode an additional current source ICR\_RUN is also switched into the circuit. This causes  $C_R$  to ramp up to  $V_{CR^+}$  much more rapidly than before. The  $C_R$  pin is used to provide ignition timing as well as the burst mode dimming low frequency ramp.

If the output is open circuit a very large voltage develops at the output. This is fed back to the SD pin through some suitable isolated sensing network such that the voltage at the SD pin will exceed VSDTH during an overvoltage condition. At this stage the capacitor  $C_D$  begins to charge through a current source. When VSD > VSDTH the burst mode dimming function is disabled and the output will be continuous.

If the voltage at SD drops below VSDTH the capacitor  $C_D$  will be discharged to 0V again. If SD remains above VSDTH long enough for the  $C_D$  capacitor voltage to reach VCDMAX or about 5 V then the IRS2552D will shut down and go into fault mode.

#### **Lamp Current Control**

Additionally the half bridge current is monitored at the CS pin so that during running if too much power is supplied to the lamps the IRS2552D is able to compensate by reducing the oscillator duty cycle while maintaining the same run frequency. This prevents the lamps from being over driven preventing premature end of life. When VCS > VCSTH the  $C_D$  capacitor will begin to charge and the CD pin voltage will rise. As this occurs the duty cycle will begin to adjust, i.e. the HO on time will become gradually shorter and the LO on time will become gradually longer. The dead time will remain constant at all times. In this way the power to the output will be reduced while the frequency remains at  $f_{MIN}$ . As the CD voltage rises, the duty cycle will be further reduced. If VCS then drops below VCSTH then the duty cycle will be regulated at that point and thus the current will be maintained at this limit. If VCS remains above VCSTH then the voltage will continue to rise on  $C_D$  until it reaches VCDMAX, at which point the duty cycle reaches its minimum limit DC<sub>MIN</sub> and the IRS2552D will enter FAULT mode, requiring  $V_{CC}$  to fall below UVLO- and then rise above UVLO+ in order to re-start.

#### Frequency, Current, and Dead Time Calculation

The running frequency of the IRS2552D is given by the following formula:

$$f_{MIN} = \frac{1}{2.09 \cdot C_T \cdot R_{MIN}}$$

where  $V_{MIN}$  = 5 V, i.e. When the ignition ramp is complete and  $R_{MAX}$  has no further effect on the oscillator.

The ignition frequency given by:

$$f_{MAX} = \frac{1}{2.09 \cdot C_T \cdot R_{MAX}}$$

and the dead time is calculated by:

$$t_{DT} = R_{DT} \cdot C_{DT} \cdot \ln(1.5)$$

$$t_{DT} = 0.405 \cdot R_{DT} \cdot C_{DT}$$

Maximum duty cycle

$$DC_{MAX} = 0.5 - (t_{DT} * f)$$

The ICR charging current during ignition mode and the ICD charging current are given by:

$$ICR_{IGN} = \frac{0.06}{R_{MIN}}$$

$$ICD = \frac{0.06}{R_{MIN}}$$

The ICR charging current and frequency during run mode are given by:

$$ICR_{RUN} = \frac{1.8}{R_{MIN}}$$

$$f_{CR} = \frac{0.36}{R_{MIN} \cdot C_{CR}}$$

#### **Dimming Function**

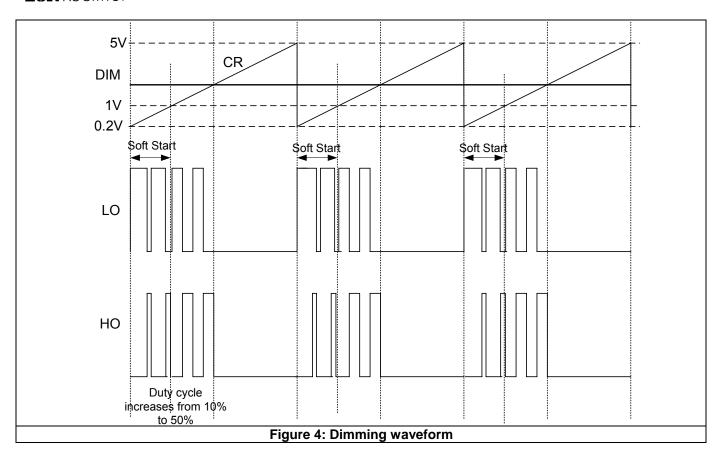

The IRS2552D supports burst mode dimming, meaning that the output drive to the lamps is pulsed on and off at a low frequency and the burst duty cycle is adjusted to control the average current and therefore the light output of the lamps. The IRS2552D contains a low frequency oscillator that generates a ramp waveform at the CR pin from 0 V to 5 V. The ramp frequency is dependent on the value of the external  $C_R$  capacitor. A DC dimming control voltage is fed into the DIM pin which is compared with the dimming ramp by means of an internal comparator, which generates the PWM signal that is used internally to switch the outputs on and off. Thus when the DIM voltage is at 5 V the outputs will be on all of the time and when it is at 0 V the outputs will be off all of the time. Alternatively a PWM dimming control signal from 0 V to 5 V can be fed directly into the DIM pin to allow external PWM control independent of the dimming ramp. During the off period the LO and HO outputs are both low.

| RUN MODE  ICCRUN charges CR up to VCR+. CR oscillates at fCR (sawtooth)  Half-bridge oscillates at FMIN. VDC reset to 0V |                                                                 |          |                  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------|------------------|--|--|--|

| SOFT START ON OFF                                                                                                        |                                                                 |          |                  |  |  |  |

|                                                                                                                          | DC increases from DC min to DC max                              | DC=DCmax | DC=0             |  |  |  |

| VDIM <vcrss< th=""><th>VCR<vcrss< th=""><th></th><th><b>VCR</b>&gt;VDIM</th></vcrss<></th></vcrss<>                      | VCR <vcrss< th=""><th></th><th><b>VCR</b>&gt;VDIM</th></vcrss<> |          | <b>VCR</b> >VDIM |  |  |  |

| VCRSS <vdim<vdimss< th=""><th>─► VCR<vdim th="" —<=""><th>VCR&gt;VDIM</th></vdim></th></vdim<vdimss<>                    | ─► VCR <vdim th="" —<=""><th>VCR&gt;VDIM</th></vdim>            | VCR>VDIM |                  |  |  |  |

| VDIM>VDIMSS VCR>VDIM                                                                                                     |                                                                 |          |                  |  |  |  |

#### Soft start

In addition the IRS2552D includes a soft start function that operates at the start of each burst, during dimming operation when VDIM < VDIM<sub>SS</sub>. The soft start will operate during the portion of the dimming ramp CR at the start of each burst from CR = 0 V to CR = VCR<sub>SS</sub>. When VCR = 0 the duty cycle will be at minimum (DCMIN) and will linearly increase to 50% (minus the dead time) when VCR reaches VCR<sub>SS</sub>. This function is enabled only in RUN mode and allows inrush currents to be eliminated during burst mode dimming, while always maintaining the frequency at  $F_{MIN}$ .

#### **PCB Layout Tips**

<u>Distance between high and low voltage components:</u> It's strongly recommended to place the components tied to the floating voltage pins  $(V_B \text{ and } V_S)$  near the respective high voltage portions of the device.

<u>Ground Plane:</u> In order to minimize noise coupling, the ground plane should not be placed under or near the high voltage floating side.

<u>Gate Drive Loops</u>: Current loops behave like antennas and are able to receive and transmit EM noise (see Figure 5). In order to reduce the EM coupling and improve the power switch turn on/off performance, the gate drive loops must be reduced as much as possible. Moreover, current can be injected inside the gate drive loop via the IGBT collector-to-gate parasitic capacitance. The parasitic auto-inductance of the gate loop contributes to developing a voltage across the gate-emitter, thus increasing the possibility of a self turn-on effect.

Figure 5: Antenna Loops

<u>Supply Capacitor:</u> It is recommended to place a bypass capacitor ( $C_{IN}$ ) between the  $V_{CC}$  and  $V_{SS}$  pins. A ceramic 1  $\mu$ F ceramic capacitor is suitable for most applications. This component should be placed as close as possible to the pins in order to reduce parasitic elements.

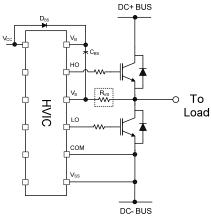

Routing and Placement: Power stage PCB parasitic elements can contribute to large negative voltage transients as the switch node; it is recommended to limit the phase voltage negative transients. In order to avoid such conditions, it is recommended to 1) minimize the high-side emitter to low-side collector distance, and 2) minimize the low-side emitter to negative bus rail stray inductance. However, where negative  $V_S$  spikes remain excessive, further steps may be taken to reduce the spike. This includes placing a resistor (5  $\Omega$  or less) between the  $V_S$  pin and the switch node (see Figure 6), and in some cases using a clamping diode between  $V_{SS}$  and  $V_S$  (see Figure 7). See DT04-4 at <a href="https://www.irf.com">www.irf.com</a> for more detailed information.

www.irf.com © 2009 International Rectifier

Figure 6: V<sub>S</sub> resistor

Figure 7: V<sub>S</sub> clamping diode

#### **Additional Documentation**

Several technical documents related to the use of HVICs are available at <a href="www.irf.com">www.irf.com</a>; use the Site Search function and the document number to quickly locate them. Below is a short list of some of these documents.

DT97-3: Managing Transients in Control IC Driven Power Stages

AN-1123: Bootstrap Network Analysis: Focusing on the Integrated Bootstrap Functionality

DT04-4: Using Monolithic High Voltage Gate Drivers

AN-978: HV Floating MOS-Gate Driver ICs

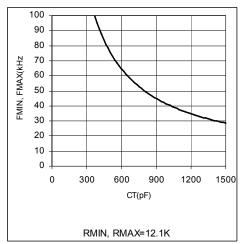

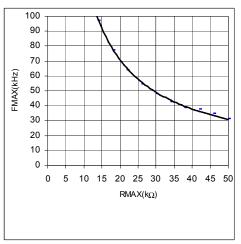

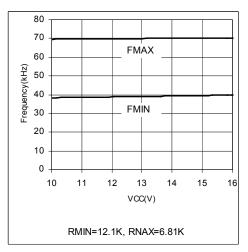

## **Programmable parameter characteristics**

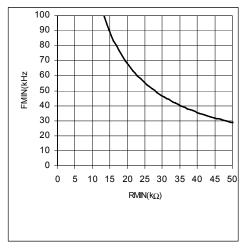

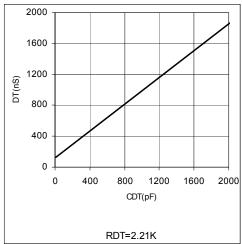

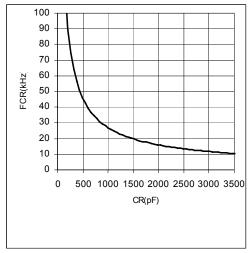

Figure 7 to 12 provide the characteristics of the programmable parameters as a function of the value of the programming components.

Figure 7: FMIN, FMAX vs. CT

Figure 9: FMAX vs. RMAX

Figure 11: DT vs. RDT

Figure 8: FMIN vs. RMIN

Figure 10: DT vs. CDT

Figure 12: FCR vs. CR

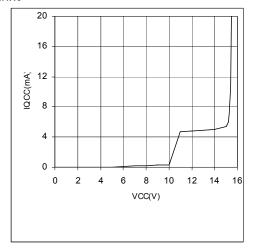

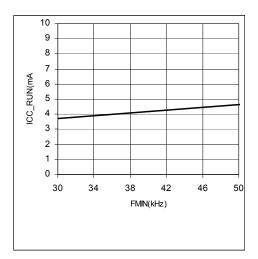

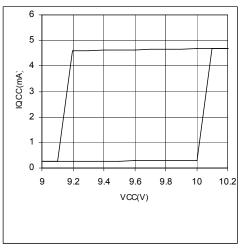

## **Parameter characteristics**

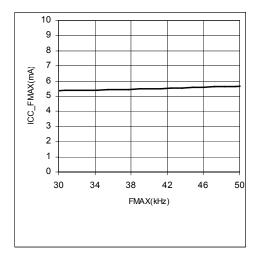

Figure 13 to 18 provide the characteristics of the main parameters as a function of VCC or the oscillator frequency

Figure 13: ICC vs. VCC

Figure15: FMIN, FMAX vs. VCC

Figure 17: ICC RUN vs. FMIN

Figure 14: IQCC vs. VCC (VCC raising and falling

Figure 16: td vs. VCC

Figure 18: ICC FMAX vs. FMAX

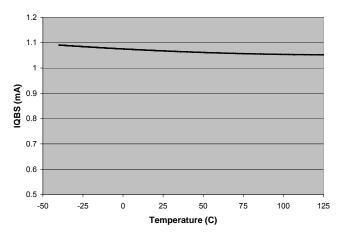

## **Parameter Temperature Trends**

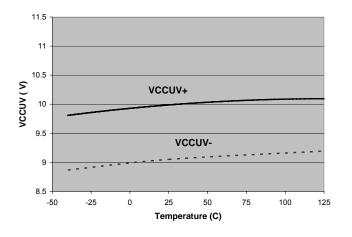

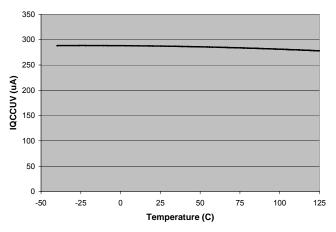

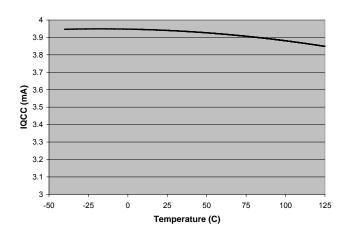

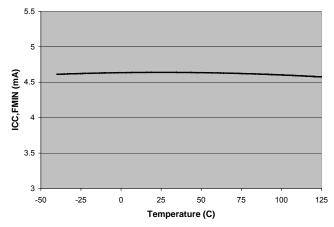

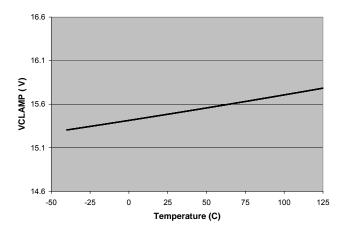

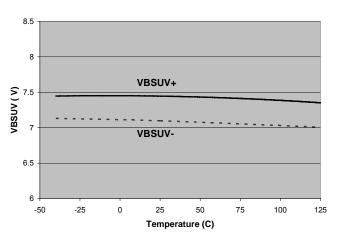

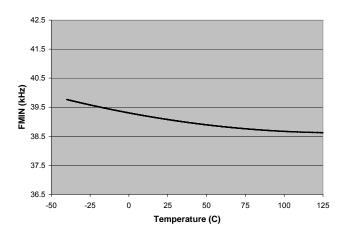

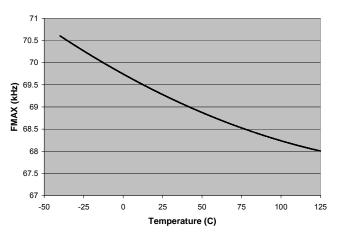

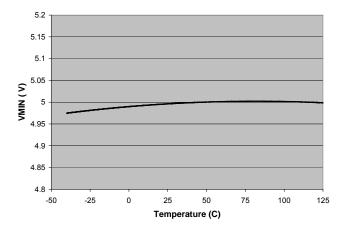

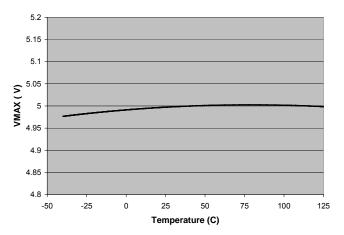

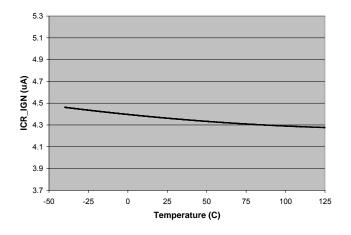

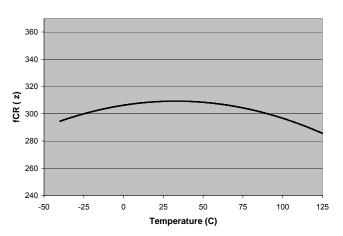

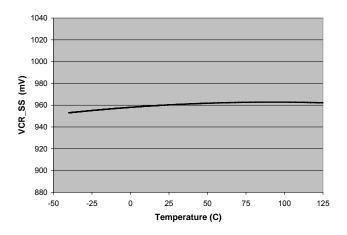

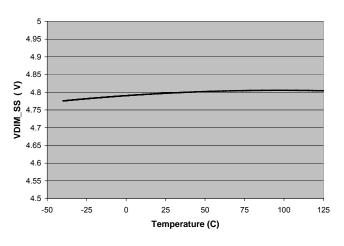

Figures 38-58 provide the characteristics of the main parameters over temperature based on three temperatures (-40 °C, 25 °C, and 125 °C) average testing.

Figure 19: VCCUV vs. temperature

Figure 20: IQCCUV vs. temperature

Figure 21: IQCC vs. temperature

Figure 22: ICC,FMIN vs. temperature

Figure 23: VCLAMP vs. temperature

Figure 24: VBSUV vs. temperature

Figure 25: fMIN vs. temperature

Figure 26: fMAX vs. temperature

Figure 27: V<sub>MIN</sub>vs. temperature

Figure 28: VMAX vs. temperature

Figure 29: I<sub>CR,IGN</sub> vs. temperature

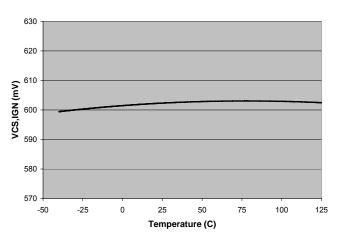

Figure 30: V<sub>cs,ign</sub> vs. temperature

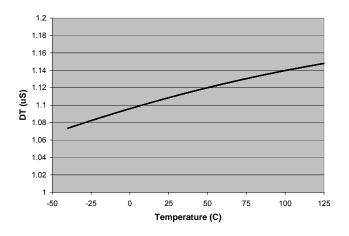

Figure 31: t<sub>D</sub> vs. temperature

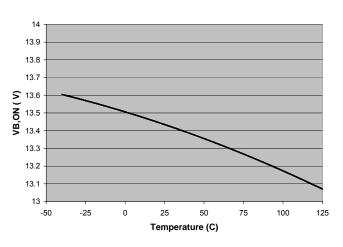

Figure 32:  $V_{B,ON}$  vs. temperature

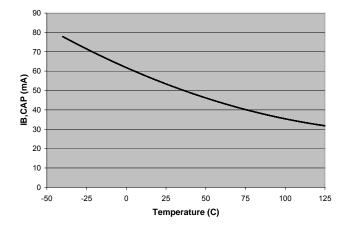

Figure 33: I<sub>B,CAP</sub> vs. temperature

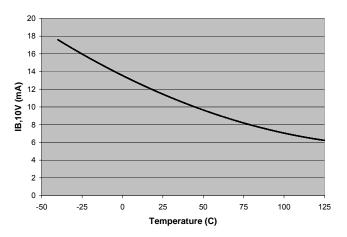

Figure 34: I<sub>B,10V</sub> vs. temperature

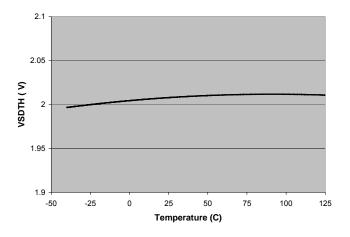

Figure 35: V<sub>SD,TH</sub> vs. temperature

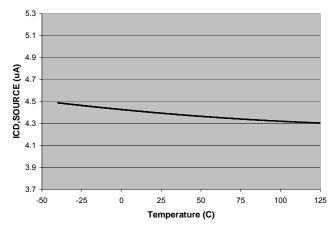

Figure 36: V<sub>CD,SOURCE</sub>vs. temperature

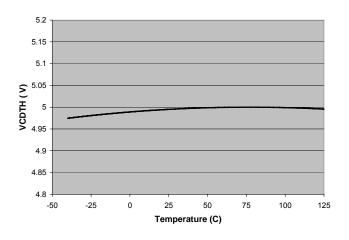

Figure 37: V<sub>CD,TH</sub> vs. temperature

Figure 38: V<sub>CDSTH</sub> vs. temperature

Figure 39:  $I_{CD,OC}$  vs. temperature

Figure 40: V<sub>CD,OC</sub> vs. temperature

Figure 41: DC<sub>MIN</sub> vs. temperature

Figure 42: f<sub>CR</sub> vs. temperature

Figure 43: V<sub>CR,SS</sub> vs. temperature

Figure 44: V<sub>DIM,SS</sub> vs. temperature

Figure 45: V<sub>ENA</sub> vs. temperature

Figure 46: IBS vs. temperature

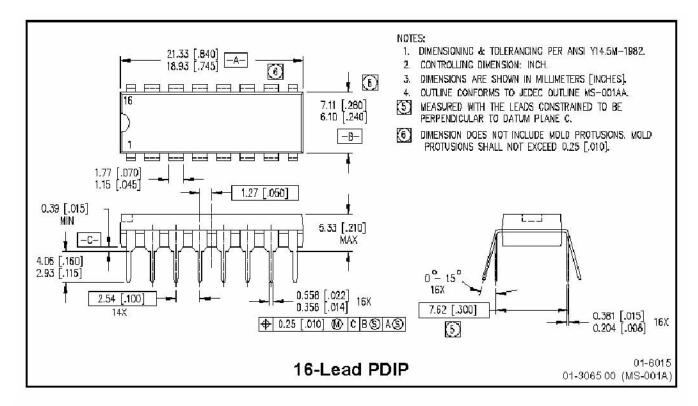

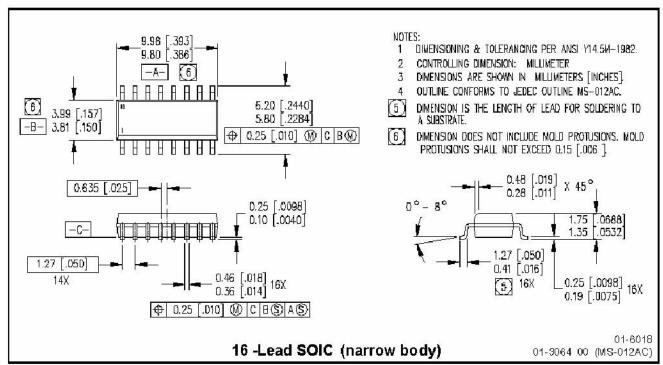

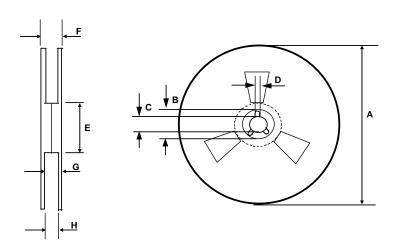

## Package Details: PDIP16 and S016N

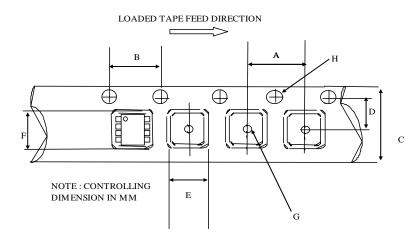

## Package Details: SOIC16N, Tape and Reel

#### CARRIER TAPE DIMENSION FOR 16SOICN

|      | Metric |       | Imp   | erial |

|------|--------|-------|-------|-------|

| Code | Min    | Max   | Min   | Max   |

| Α    | 7.90   | 8.10  | 0.311 | 0.318 |

| В    | 3.90   | 4.10  | 0.153 | 0.161 |

| С    | 15.70  | 16.30 | 0.618 | 0.641 |

| D    | 7.40   | 7.60  | 0.291 | 0.299 |

| E    | 6.40   | 6.60  | 0.252 | 0.260 |

| F    | 10.20  | 10.40 | 0.402 | 0.409 |

| G    | 1.50   | n/a   | 0.059 | n/a   |

| Н    | 1.50   | 1.60  | 0.059 | 0.062 |

**REEL DIMENSIONS FOR 16SOICN**

|      | Metric |        | Imperial |        |

|------|--------|--------|----------|--------|

| Code | Min    | Max    | Min      | Max    |

| Α    | 329.60 | 330.25 | 12.976   | 13.001 |

| В    | 20.95  | 21.45  | 0.824    | 0.844  |

| С    | 12.80  | 13.20  | 0.503    | 0.519  |

| D    | 1.95   | 2.45   | 0.767    | 0.096  |

| E    | 98.00  | 102.00 | 3.858    | 4.015  |

| F    | n/a    | 22.40  | n/a      | 0.881  |

| G    | 18.50  | 21.10  | 0.728    | 0.830  |

| Н    | 16.40  | 18.40  | 0.645    | 0.724  |

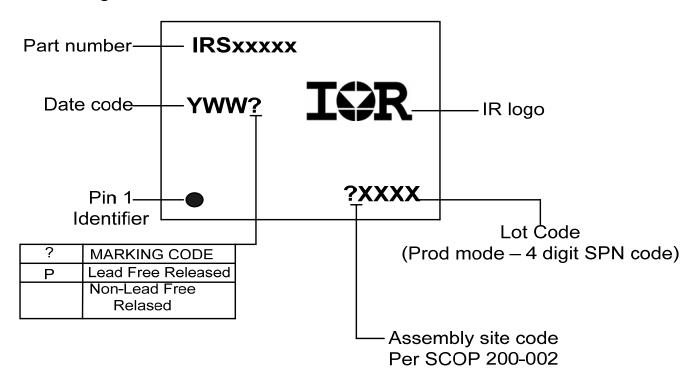

## **Part Marking Information**

## **Ordering Information**

| Base Part Number | Package Type | Standard Pack |          | Commission Boat Name on |

|------------------|--------------|---------------|----------|-------------------------|

|                  |              | Form          | Quantity | Complete Part Number    |

| IRS2552D         | PDIP16       | Tube/Bulk     | 25       | IRS2552DPBF             |

|                  | SOIC16N      | Tube/Bulk     | 45       | IRS2552DSPBF            |

|                  |              | Tape and Reel | 2500     | IRS2552DSTRPBF          |

The information provided in this document is believed to be accurate and reliable. However, International Rectifier assumes no responsibility for the consequences of the use of this information. International Rectifier assumes no responsibility for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of International Rectifier. The specifications mentioned in this document are subject to change without notice. This document supersedes and replaces all information previously supplied.

For technical support, please contact IR's Technical Assistance Center http://www.irf.com/technical-info/

#### **WORLD HEADQUARTERS:**

233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105