# 7-Port 10/100 Ethernet Switch with Audio Video Bridging and Two RGMII/MII/RMII Interfaces

# **Highlights**

- · Non-blocking wire-speed Ethernet switching fabric

- Full-featured forwarding and filtering control, including Access Control List (ACL) filtering

- · Full VLAN and QoS support

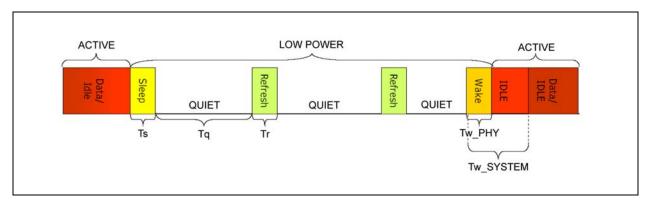

- Five ports with integrated 10/100BASE-T PHY transceivers with optional Quiet-WIRE® EMC filtering

- Two ports with 10/100/1000 Ethernet MACs and configurable RGMII/MII/RMII interfaces

- IEEE 1588v2 Precision Time Protocol (PTP) support

- IEEE 802.1AS/Qav Audio Video Bridging (AVB)

- IEEE 802.3az Energy Efficient Ethernet (EEE)

- IEEE 802.1X access control support

- EtherGreen™ power management features, including low power standby

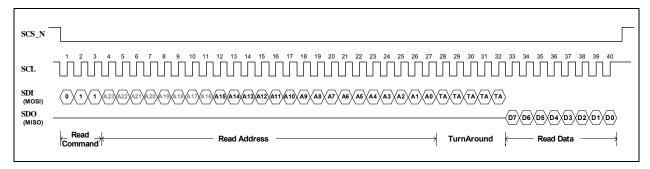

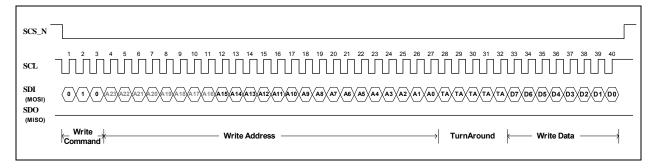

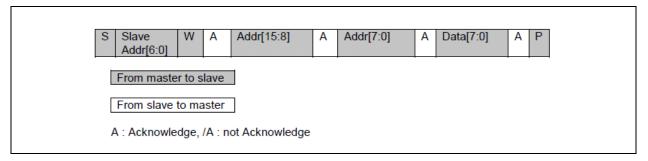

- Flexible management interface options: SPI, I<sup>2</sup>C, MIIM, and in-band management via any port

- Industrial/Extended Auto temperature range support

- 128-pin TQFP-EP (14 x 14mm) RoHS compliant pkg

# **Target Applications**

- · Industrial Ethernet (Profinet, MODBUS, Ethernet/IP)

- · Real-time Ethernet networks

- IEC 61850 networks w/ power substation automation

- Industrial control/automation switches

- · Networked measurement and control systems

- · Test and measurement equipment

# **Features**

- Switch Management Capabilities

- 10/100Mbps Ethernet switch basic functions: frame buffer management, address look-up table, queue management, MIB counters

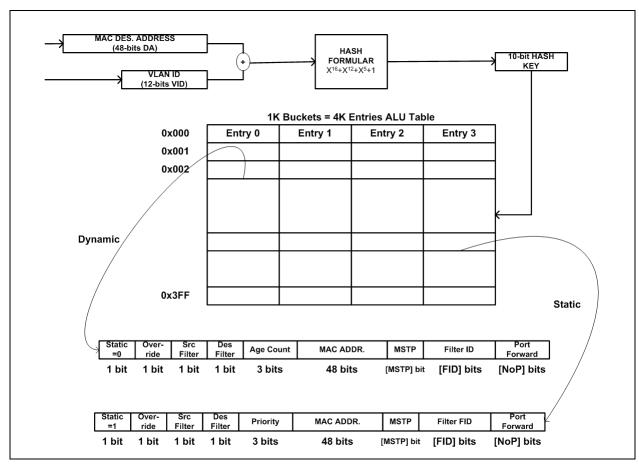

- Non-blocking store-and-forward switch fabric assures fast packet delivery by utilizing 4096 entry forwarding table with 256kByte frame buffer

- Jumbo packet support up to 9000 bytes

- Port mirroring/monitoring/sniffing: ingress and/or egress traffic to any port

- Rapid spanning tree protocol (RSTP) support for topology management and ring/linear recovery

- Multiple spanning tree protocol (MSTP) support

- Two Configurable External MAC Ports

- Reduced Gigabit Media Independent Interface (RGMII) v2.0

- Reduced Media Independent Interface (RMII) v1.2 with 50MHz reference clock input/output option

- Media Independent Interface (MII) in PHY/MAC mode

- · Five Integrated PHY Ports

- 100BASE-TX/10BASE-T/Te IEEE 802.3

- Fast Link-up option significantly reduces link-up time

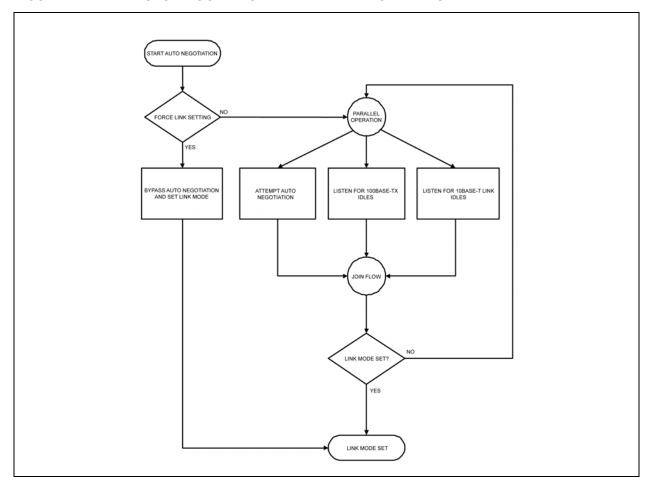

- Auto-negotiation and Auto-MDI/MDI-X support

- Energy-Efficient Ethernet (EEE) support with lowpower idle mode and clock stoppage

- On-chip termination resistors and internal biasing for differential pairs to reduce power

- Advanced Switch Capabilities

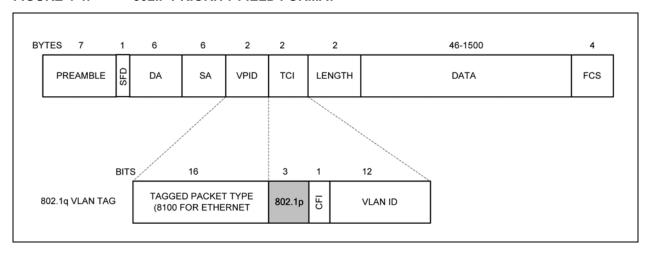

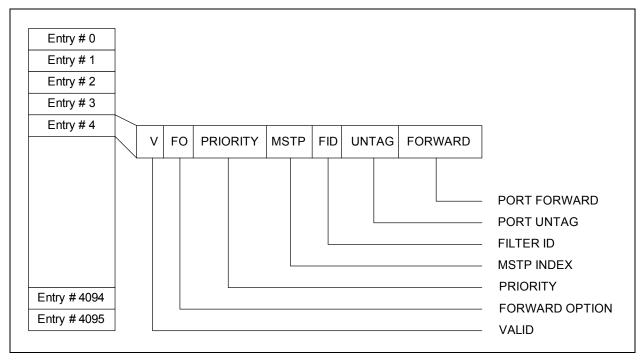

- IEEE 802.1Q VLAN support for 128 active VLAN groups and the full range of 4096 VLAN IDs

- IEEE 802.1p/Q tag insertion/removal on per port basis

- VLAN ID on per port or VLAN basis

- IEEE 802.3x full-duplex flow control and half-duplex back pressure collision control

- IEEE 802.1X access control (Port and MAC address)

- IGMP v1/v2/v3 snooping for multicast packet filtering

- IPv6 multicast listener discovery (MLD) snooping

- IPv4/IPv6 QoS support, QoS/CoS packet prioritization

- 802.1p QoS packet classification with 4 priority queues

- Programmable rate limiting at ingress/egress ports

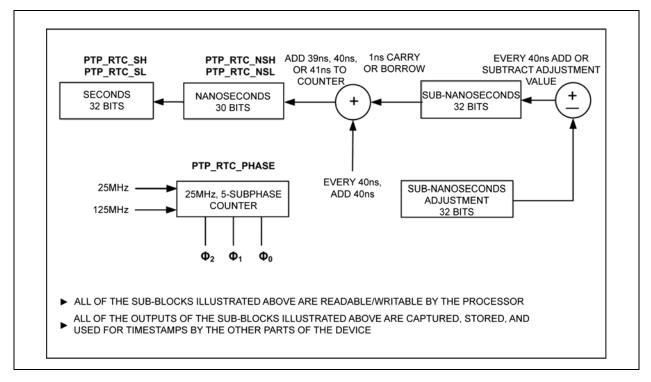

- · IEEE 1588v2 PTP and Clock Synchronization

- Transparent Clock (TC) with auto correction update

- Master and slave Ordinary Clock (OC) support

- End-to-end (E2E) or peer-to-peer (P2P)

- PTP multicast and unicast message support

- PTP message transport over IPv4/v6 and IEEE 802.3

- IEEE 1588v2 PTP packet filtering

- Synchronous Ethernet support via recovered clock

- · Audio Video Bridging (AVB)

- Compliant with IEEE 802.1BA/AS/Qat/Qav standards

- Priority queuing, Low latency cut-through mode

- gPTP time synchronization, credit-based traffic shaper

- Time aware traffic scheduler per port

- · Comprehensive Configuration Registers Access

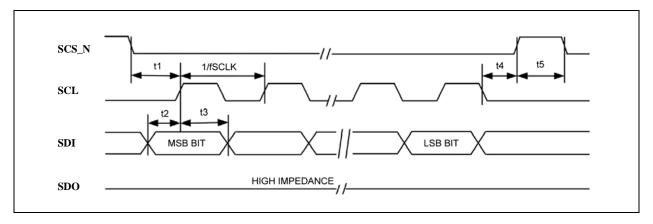

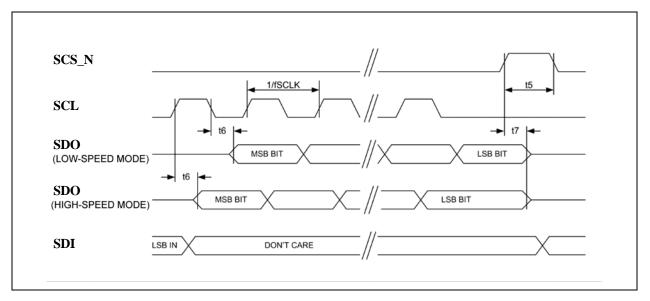

- High-speed 4-wire SPI (up to 50MHz), I<sup>2</sup>C interfaces provide access to all internal registers

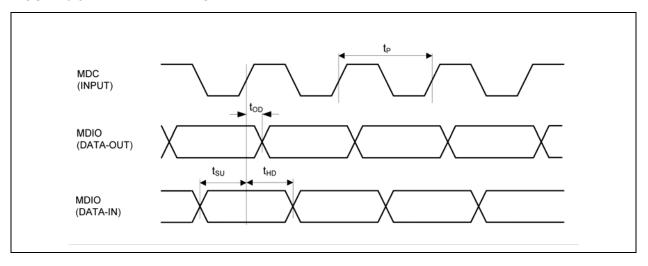

- MII Management (MIIM, MDC/MDIO 2-wire) Interface provides access to all PHY registers

- In-band management via any of the data ports

- I/O pin strapping facility to set certain register bits from I/O pins at reset time

- · Power Management

- IEEE 802.3az Energy Efficient Ethernet (EEE)

- Energy detect power-down mode on cable disconnect

- Dynamic clock tree control

- Unused ports can be individually powered down

- Full-chip software power-down

- Wake-on-LAN (WoL) standby power mode with PME interrupt output for system wake upon triggered events

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### **Most Current Documentation**

To obtain the most up-to-date version of this documentation, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table of Contents**

| 1.0 Preface                             | 4   |

|-----------------------------------------|-----|

| 2.0 Introduction                        | 8   |

| 3.0 Pin Descriptions and Configuration  | 9   |

| 4.0 Functional Description              |     |

| 5.0 Device Registers                    | 67  |

| 6.0 Operational Characteristics         |     |

| 7.0 Design Guidelines                   | 221 |

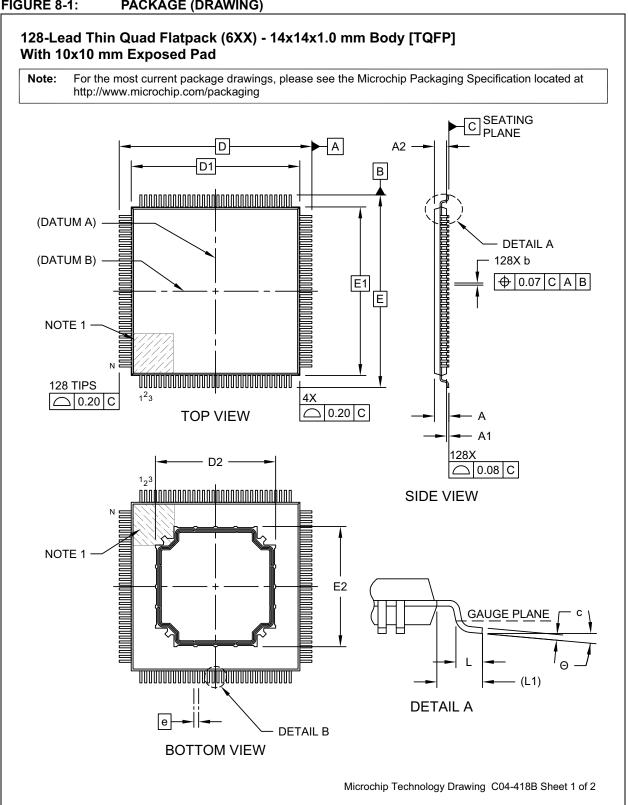

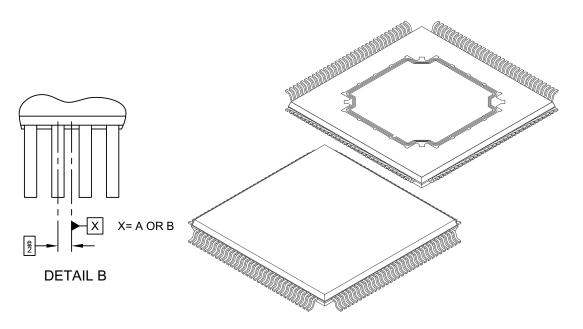

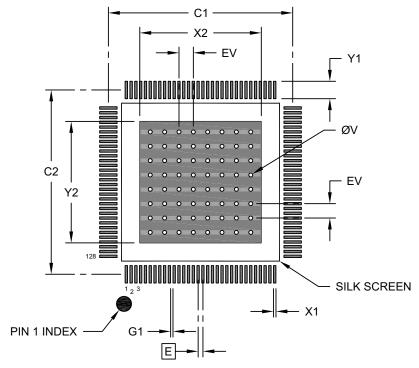

| 8.0 Package Information                 | 223 |

| Appendix A: Data Sheet Revision History | 227 |

| The Microchip Web Site                  |     |

| Customer Change Notification Service    | 230 |

| Customer Support                        |     |

| Product Identification System           |     |

# 1.0 PREFACE

# 1.1 Glossary of Terms

TABLE 1-1: GENERAL TERMS

| Term         | Description                                                                                                                                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10BASE-T     | 10 Mbps Ethernet, 3.3V signaling, IEEE 802.3 compliant                                                                                                                                                                                                  |

| 10BASE-Te    | 10 Mbps Ethernet, 2.5V signaling, IEEE 802.3 compliant                                                                                                                                                                                                  |

| 100BASE-TX   | 100 Mbps Fast Ethernet, IEEE 802.3u compliant                                                                                                                                                                                                           |

| ADC          | Analog-to-Digital Converter                                                                                                                                                                                                                             |

| AN           | Auto-Negotiation                                                                                                                                                                                                                                        |

| AVB          | Audio Video Bridging (IEEE 802.1BA, 802.1AS, 802.1Qat, 802.1Qav)                                                                                                                                                                                        |

| BLW          | Baseline Wander                                                                                                                                                                                                                                         |

| BPDU         | Bridge Protocol Data Unit. Messages which carry the Spanning Tree Protocol information.                                                                                                                                                                 |

| Byte         | 8 bits                                                                                                                                                                                                                                                  |

| CRC          | Cyclic Redundancy Check. A common technique for detection data transmission errors. CRC for Ethernet is 32 bits long.                                                                                                                                   |

| CSR          | Control and Status Registers                                                                                                                                                                                                                            |

| DA           | Destination Address                                                                                                                                                                                                                                     |

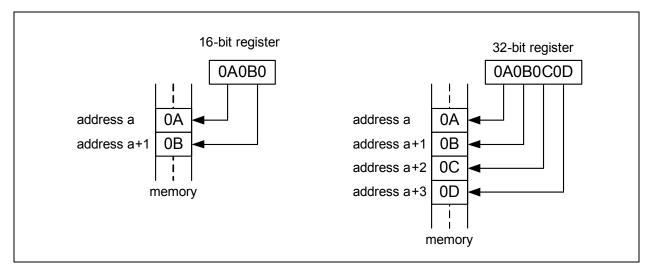

| DWORD        | 32 bits                                                                                                                                                                                                                                                 |

| EEE          | Energy Efficient Ethernet                                                                                                                                                                                                                               |

| FCS          | Frame Check Sequence. The extra checksum characters added to the end of an Ethernet frame, used for error detection and correction.                                                                                                                     |

| FID          | Frame or Filter ID. Specifies the frame identifier. Alternately is the filter identifier.                                                                                                                                                               |

| FIFO         | First In First Out buffer                                                                                                                                                                                                                               |

| FSM          | Finite State Machine                                                                                                                                                                                                                                    |

| GPIO         | General Purpose I/O                                                                                                                                                                                                                                     |

| Host         | External system (Includes processor, application software, etc.)                                                                                                                                                                                        |

| IGMP         | Internet Group Management Protocol. Defined by RFC 1112, RFC 2236, and RFC 4604 to establish multicast group membership in IPv4 networks.                                                                                                               |

| IPG          | Inter-Packet Gap. A time delay between successive data packets mandated by the network standard for protocol reasons.                                                                                                                                   |

| Jumbo Packet | A packet larger than the standard Ethernet packet (1518 bytes). Large packet sizes allow for more efficient use of bandwidth, lower overhead, less processing, etc                                                                                      |

| Isb          | Least Significant Bit                                                                                                                                                                                                                                   |

| LSB          | Least Significant Byte                                                                                                                                                                                                                                  |

| MAC          | Media Access Controller. A functional block responsible for implementing the media access control layer, which is a sublayer of the data link layer.                                                                                                    |

| MDI          | Medium Dependent Interface. An Ethernet port connection that allows network hubs or switches to connect to other hubs or switches without a null-modem, or crossover, cable.                                                                            |

| MDIX         | Media Independent Interface with Crossover. An Ethernet port connection that allows networked end stations (i.e., PCs or workstations) to connect to each other using a null-modem, or crossover, cable.                                                |

| MIB          | Management Information Base. The MIB comprises the management portion of network devices. This can include monitoring traffic levels and faults (statistical), and can also change operating parameters in network nodes (static forwarding addresses). |

TABLE 1-1: GENERAL TERMS (CONTINUED)

| Term     | Description                                                                                                                                                                                                                                                                  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII      | Media Independent Interface. The MII accesses PHY registers as defined in the IEEE 802.3 specification.                                                                                                                                                                      |

| MIIM     | Media Independent Interface Management                                                                                                                                                                                                                                       |

| MLD      | Multicast Listening Discovery. This protocol is defined by RFC 3810 and RFC 4604 to establish multicast group membership in IPv6 networks.                                                                                                                                   |

| MLT-3    | Multi-Level Transmission Encoding (3-Levels). A tri-level encoding method where a change in the logic level represents a code bit "1" and the logic output remaining at the same level represents a code bit "0".                                                            |

| msb      | Most Significant Bit                                                                                                                                                                                                                                                         |

| MSB      | Most Significant Byte                                                                                                                                                                                                                                                        |

| NRZ      | Non Return to Zero. A type of signal data encoding whereby the signal does not return to a zero state in between bits.                                                                                                                                                       |

| NRZI     | Non Return to Zero Inverted. This encoding method inverts the signal for a "1" and leaves the signal unchanged for a "0"                                                                                                                                                     |

| N/A      | Not Applicable                                                                                                                                                                                                                                                               |

| NC       | No Connect                                                                                                                                                                                                                                                                   |

| OUI      | Organizationally Unique Identifier                                                                                                                                                                                                                                           |

| PHY      | A device or function block which performs the physical layer interface function in a network.                                                                                                                                                                                |

| PLL      | Phase Locked Loop. A electronic circuit that controls an oscillator so that it maintains a constant phase angle (i.e., lock) on the frequency of an input, or reference, signal.                                                                                             |

| PTP      | Precision Time Protocol                                                                                                                                                                                                                                                      |

| RESERVED | Refers to a reserved bit field or address. Unless otherwise noted, reserved bits must always be zero for write operations. Unless otherwise noted, values are not guaranteed when reading reserved bits. Unless otherwise noted, do not read or write to reserved addresses. |

| RTC      | Real-Time Clock                                                                                                                                                                                                                                                              |

| SA       | Source Address                                                                                                                                                                                                                                                               |

| SFD      | Start of Frame Delimiter. The 8-bit value indicating the end of the preamble of an Ethernet frame.                                                                                                                                                                           |

| SQE      | Signal Quality Error (also known as "heartbeat")                                                                                                                                                                                                                             |

| SSD      | Start of Stream Delimiter                                                                                                                                                                                                                                                    |

| ТСР      | Transmission Control Protocol                                                                                                                                                                                                                                                |

| UDP      | User Datagram Protocol - A connectionless protocol run on top of IP networks                                                                                                                                                                                                 |

| UTP      | Unshielded Twisted Pair. Commonly a cable containing 4 twisted pairs of wire.                                                                                                                                                                                                |

| UUID     | Universally Unique IDentifier                                                                                                                                                                                                                                                |

| VLAN     | Virtual Local Area Network                                                                                                                                                                                                                                                   |

| WORD     | 16 bits                                                                                                                                                                                                                                                                      |

# 1.2 Buffer Types

TABLE 1-2: BUFFER TYPES

| Buffer Type | Description                                                                                                  |

|-------------|--------------------------------------------------------------------------------------------------------------|

| I           | Input                                                                                                        |

| IPU         | Input with internal pull-up (58 kΩ ±30%)                                                                     |

| IPU/O       | Input with internal pull-up (58 k $\Omega$ ±30%) during power-up/reset; output pin during normal operation   |

| IPD         | Input with internal pull-down (58 kΩ ±30%)                                                                   |

| IPD/O       | Input with internal pull-down (58 k $\Omega$ ±30%) during power-up/reset; output pin during normal operation |

| 08          | Output with 8 mA sink and 8 mA source                                                                        |

| O24         | Output with 24 mA sink and 24 mA source                                                                      |

| OPU         | Output (8mA) with internal pull-up (58 kΩ ±30%)                                                              |

| OPD         | Output (8mA) with internal pull-down (58 kΩ ±30%)                                                            |

| Α           | Analog                                                                                                       |

| AIO         | Analog bidirectional                                                                                         |

| ICLK        | Crystal oscillator input pin                                                                                 |

| OCLK        | Crystal oscillator output pin                                                                                |

| Р           | Power                                                                                                        |

| GND         | Ground                                                                                                       |

**Note:** Refer to Section 6.3, "Electrical Characteristics," on page 205 for the electrical characteristics of the various buffers.

# 1.3 Register Nomenclature

TABLE 1-3: REGISTER NOMENCLATURE

| Register Bit Type Notation | Register Bit Description                                                                                                                                                                                                                                                           |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R                          | Read: A register or bit with this attribute can be read.                                                                                                                                                                                                                           |

| W                          | Write: A register or bit with this attribute can be written.                                                                                                                                                                                                                       |

| RO                         | Read only: Read only. Writes have no effect.                                                                                                                                                                                                                                       |

| RC                         | Read to Clear: Contents is cleared after the read. Writes have no effect.                                                                                                                                                                                                          |

| WO                         | Write only: If a register or bit is write-only, reads will return unspecified data.                                                                                                                                                                                                |

| WC                         | Write One to Clear: Writing a one clears the value. Writing a zero has no effect.                                                                                                                                                                                                  |

| LL                         | <b>Latch Low:</b> Applies to certain RO status bits. If a status condition causes this bit to go low, it will maintain the low state until read, even if the status condition changes. A read clears the latch, allowing the bit to go high if dictated by the status condition.   |

| LH                         | <b>Latch High:</b> Applies to certain RO status bits. If a status condition causes this bit to go high, it will maintain the high state until read, even if the status condition changes. A read clears the latch, allowing the bit to go low if dictated by the status condition. |

| SC                         | <b>Self-Clearing:</b> Contents are self-cleared after the being set. Writes of zero have no effect. Contents can be read.                                                                                                                                                          |

| RESERVED                   | Reserved Field: Reserved fields must be written with zeros, unless otherwise indicated, to ensure future compatibility. The value of reserved bits is not guaranteed on a read.                                                                                                    |

# 1.4 References

• NXP I<sup>2</sup>C-Bus Specification (UM10204, April 4, 2014): www.nxp.com/documents/user\_manual/UM10204.pdf

# 2.0 INTRODUCTION

# 2.1 General Description

The KSZ8567R is a highly-integrated, IEEE 802.3 compliant networking device that incorporates a layer-2 managed high-performance Ethernet switch, five 10BASE-T/Te/100BASE-TX physical layer transceivers (PHYs) and associated MAC units, and two MAC ports with individually configurable RGMII/MII/RMII interfaces for direct connection to a host processor/controller, another Ethernet switch, or an Ethernet PHY transceiver.

The KSZ8567R is built upon industry-leading Ethernet technology, with features designed to offload host processing and streamline the overall design:

- · Non-blocking wire-speed Ethernet switch fabric

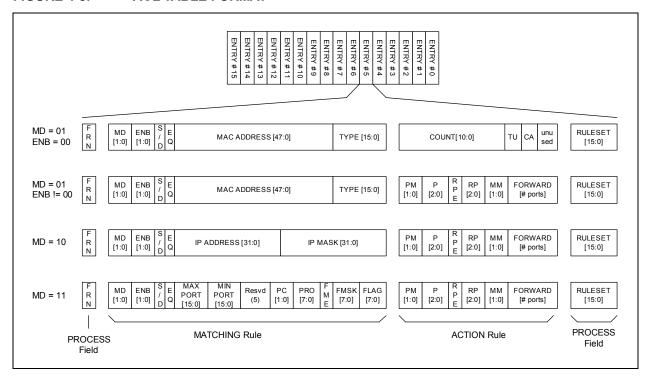

- · Full-featured forwarding and filtering control, including port-based Access Control List (ACL) filtering

- · Full VLAN and QoS support

- · Traffic prioritization with per-port ingress/egress queues and by traffic classification

- · Spanning Tree support

- IEEE 802.1X access control support

The KSZ8567R incorporates full hardware support for the IEEE 1588v2 Precision Time Protocol (PTP), including hardware time-stamping at all PHY-MAC interfaces, and a high-resolution hardware "PTP clock". IEEE 1588 provides sub-microsecond synchronization for a range of industrial Ethernet applications.

The KSZ8567R fully supports the IEEE family of Audio Video Bridging (AVB) standards, which provides high Quality of Service (QoS) for latency sensitive traffic streams over Ethernet. Time-stamping and time-keeping features support IEEE 802.1AS time synchronization. All ports feature credit based traffic shapers for IEEE 802.1Qav, and a time aware scheduler as proposed for IEEE 802.1Qbv.

The 100Mbps PHYs feature Quiet-WIRE internal filtering to reduce line emissions and enhance immunity to environmental noise. It is ideal for automotive or industrial applications where stringent radiated emission limits must be met.

A host processor can access all KSZ8567R registers for control over all PHY, MAC, and switch functions. Full register access is available via the integrated SPI or  $I^2C$  interfaces, and by in-band management via any one of the data ports. PHY register access is provided by a MIIM interface. Flexible digital I/O voltage allows the MAC port to interface directly with a 1.8/2.5/3.3V host processor/controller/FPGA.

Additionally, a robust assortment of power-management features including IEEE 802.3az Energy-Efficient Ethernet (EEE) for power savings with idle link, and Wake-on-LAN (WoL) for low power standby operation, have been designed to satisfy energy-efficient system requirements.

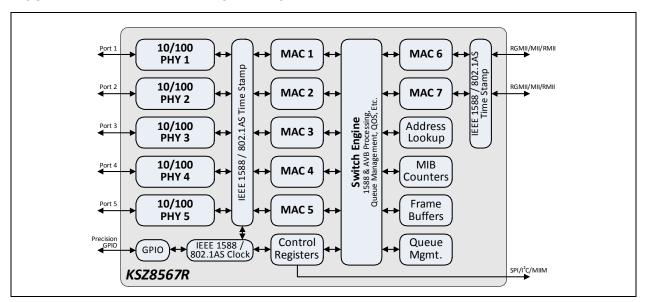

The KSZ8567R is available in industrial (-40°C to +85°C) and extended automotive (-40°C to +105°C) temperature ranges. An internal block diagram of the KSZ8567R is shown in Figure 2-1.

FIGURE 2-1: INTERNAL BLOCK DIAGRAM

# 3.0 PIN DESCRIPTIONS AND CONFIGURATION

# 3.1 Pin Assignments

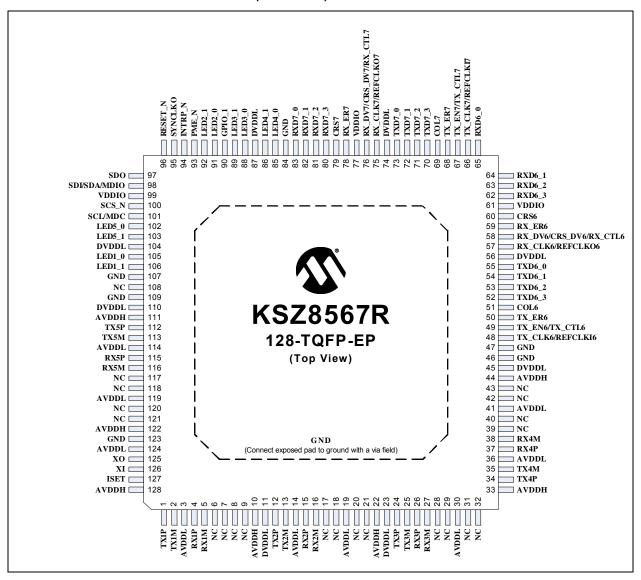

The device pin diagram for the KSZ8567R can be seen in Figure 3-1. Table 3-1 provides a KSZ8567R pin assignment table. Pin descriptions are provided in Section 3.2, "Pin Descriptions".

FIGURE 3-1: PIN ASSIGNMENTS (TOP VIEW)

**Note:** When an "\_N" is used at the end of the signal name, it indicates that the signal is active low. For example, **RESET\_N** indicates that the reset signal is active low.

The buffer type for each signal is indicated in the "Buffer Type" column of the pin description tables in Section 3.2, "Pin Descriptions". A description of the buffer types is provided in Section 1.2, "Buffer Types".

TABLE 3-1: PIN ASSIGNMENTS

| Pin | Pin Name                             | Pin | Pin Name                   | Pin | Pin Name                              | Pin | Pin Name          |

|-----|--------------------------------------|-----|----------------------------|-----|---------------------------------------|-----|-------------------|

| 1   | TX1P                                 | 33  | AVDDH                      | 65  | RXD6_0 (Note 3-1)                     | 97  | SDO               |

| 2   | TX1M                                 | 34  | TX4P                       | 66  | TX_CLK7/REFCLKI7                      | 98  | SDI/SDA/MDIO      |

| 3   | AVDDL                                | 35  | TX4M                       | 67  | TX_EN7/TX_CTL7                        | 99  | VDDIO             |

| 4   | RX1P                                 | 36  | AVDDL                      | 68  | TX_ER7                                | 100 | SCS_N             |

| 5   | RX1M                                 | 37  | RX4P                       | 69  | COL7                                  | 101 | SCL/MDC           |

| 6   | NC                                   | 38  | RX4M                       | 70  | TXD7_3                                | 102 | LED5_0            |

| 7   | NC                                   | 39  | NC                         | 71  | TXD7_2                                | 103 | LED5_1 (Note 3-1) |

| 8   | NC                                   | 40  | NC                         | 72  | TXD7_1                                | 104 | DVDDL             |

| 9   | NC                                   | 41  | AVDDL                      | 73  | TXD7_0                                | 105 | LED1_0            |

| 10  | AVDDH                                | 42  | NC                         | 74  | DVDDL                                 | 106 | LED1_1 (Note 3-1) |

| 11  | DVDDL                                | 43  | NC                         | 75  | RX_CLK7/REFCLKO7                      | 107 | GND               |

| 12  | TX2P                                 | 44  | AVDDH                      | 76  | RX_DV7/CRS_DV7/<br>RX_CTL7 (Note 3-1) | 108 | NC                |

| 13  | TX2M                                 | 45  | DVDDL                      | 77  | VDDIO                                 | 109 | GND               |

| 14  | AVDDL                                | 46  | GND                        | 78  | RX_ER7                                | 110 | DVDDL             |

| 15  | RX2P                                 | 47  | GND                        | 79  | CRS7                                  | 111 | AVDDH             |

| 16  | RX2M                                 | 48  | TX_CLK6/REFCLKI6           | 80  | RXD7_3 (Note 3-1)                     | 112 | TX5P              |

| 17  | NC                                   | 49  | TX_EN6/TX_CTL6             | 81  | RXD7_2 (Note 3-1)                     | 113 | TX5M              |

| 18  | NC                                   | 50  | TX_ER6                     | 82  | RXD7_1 (Note 3-1)                     | 114 | AVDDL             |

| 19  | AVDDL                                | 51  | COL6                       | 83  | RXD7_0 (Note 3-1)                     | 115 | RX5P              |

| 20  | NC                                   | 52  | TXD6_3                     | 84  | GND                                   | 116 | RX5M              |

| 21  | NC                                   | 53  | TXD6_2                     | 85  | LED4_0 (Note 3-1)                     | 117 | NC                |

| 22  | AVDDH                                | 54  | TXD6_1                     | 86  | LED4_1 (Note 3-1)                     | 118 | NC                |

| 23  | DVDDL                                | 55  | TXD6_0                     | 87  | DVDDL                                 | 119 | AVDDL             |

| 24  | TX3P                                 | 56  | DVDDL                      | 88  | LED3_0                                | 120 | NC                |

| 25  | TX3M                                 | 57  | RX_CLK6/REFCLKO6           | 89  | LED3_1 (Note 3-1)                     | 121 | NC                |

| 26  | RX3P                                 | 58  | RX_DV6/CRS_DV6/<br>RX_CTL6 | 90  | GPIO_1                                | 122 | AVDDH             |

| 27  | RX3M                                 | 59  | RX_ER6                     | 91  | LED2_0 (Note 3-1)                     | 123 | GND               |

| 28  | NC                                   | 60  | CRS6                       | 92  | LED2_1 (Note 3-1)                     | 124 | AVDDL             |

| 29  | NC                                   | 61  | VDDIO                      | 93  | PME_N                                 | 125 | XO                |

| 30  | AVDDL                                | 62  | RXD6_3 (Note 3-1)          | 94  | INTRP_N                               | 126 | XI                |

| 31  | NC                                   | 63  | RXD6_2 (Note 3-1)          | 95  | SYNCLKO                               | 127 | ISET              |

| 32  | NC                                   | 64  | RXD6_1 (Note 3-1)          | 96  | RESET_N                               | 128 | AVDDH             |

|     | Exposed Pad Must be Connected to GND |     |                            |     |                                       |     |                   |

Note 3-1 This pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information.

# 3.2 Pin Descriptions

This sections details the functions of the various device signals.

TABLE 3-2: PIN DESCRIPTIONS

| IABLL 3-2.                                  | FIN DESCRIPTIONS             |                |                                                                                                                                           |  |  |  |

|---------------------------------------------|------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                        | SYMBOL                       | BUFFER<br>TYPE | DESCRIPTION                                                                                                                               |  |  |  |

| Ports 5-1 10/100 Ethernet Pins              |                              |                |                                                                                                                                           |  |  |  |

| Port 5-1<br>Ethernet TX +                   | TX[5:1]P                     | AIO            | Port 5-1 100BASE-TX/10BASE-T Differential Data (+) Transmit when in MDI mode, receive when in MDI-X mode.                                 |  |  |  |

| Port 5-1<br>Ethernet TX -                   | TX[5:1]M                     | AIO            | Port 5-1 100BASE-TX/10BASE-T Differential Data (-) Transmit when in MDI mode, receive when in MDI-X mode.                                 |  |  |  |

| Port 5-1<br>Ethernet RX +                   | RX[5:1]P                     | AIO            | Port 5-1 100BASE-TX/10BASE-T Differential Data (+) Receive when in MDI mode, transmit when in MDI-X mode.                                 |  |  |  |

| Port 5-1<br>Ethernet RX -                   | RX[5:1]M                     | AIO            | Port 5-1 100BASE-TX/10BASE-T Differential Data (-) Receive when in MDI mode, transmit when in MDI-X mode.                                 |  |  |  |

|                                             | Ī                            | Ports 7-6 RG   | MII/MII/RMII Pins                                                                                                                         |  |  |  |

| Port 7-6<br>Transmit/<br>Reference<br>Clock | TX_CLK[7:6]/<br>REFCLKI[7:6] | I/O8           | MII Mode: TX_CLK[7:6] is the Port 7-6 25/2.5MHz Transmit Clock. In PHY mode this pin is an output, in MAC mode it is an input.            |  |  |  |

|                                             |                              |                | RMII Mode: REFCLKI[7:6] is the Port 7-6 50MHz Reference Clock input when in RMII Normal mode. This pin is unused when in RMII Clock mode. |  |  |  |

|                                             |                              |                | <b>RGMII Mode:</b> TX_CLK[7:6] is the Port 7-6 125/25/2.5MHz Transmit Clock input.                                                        |  |  |  |

| Port 7-6<br>Transmit<br>Enable/Control      | TX_EN[7:6]/<br>TX_CTL[7:6]   | IPD            | MII/RMII Modes: TX_EN[7:6] is the Port 7-6 Transmit Enable.                                                                               |  |  |  |

|                                             |                              |                | <b>RGMII Mode:</b> TX_CTL[7:6] is the Port 7-6 Transmit Control.                                                                          |  |  |  |

| Port 7-6<br>Transmit Error                  | TX_ER[7:6]                   | IPD            | MII Mode: Port 7-6 Transmit Error input.  RMII/RGMII Modes: Not used. Do not connect this pin in                                          |  |  |  |

|                                             |                              |                | these modes of operation.                                                                                                                 |  |  |  |

| Port 7-6<br>Collision Detect                | COL[7:6]                     | IPD/O8         | <b>MII Mode:</b> Port 7-6 Collision Detect. In PHY mode this pin is an output, in MAC mode it is an input.                                |  |  |  |

|                                             |                              |                | <b>RMII/RGMII Modes:</b> Not used. Do not connect this pin in these modes of operation.                                                   |  |  |  |

| Port 7-6<br>Transmit Data 3                 | TXD[7:6]_3                   | IPD            | MII/RGMII Modes: Port 7-6 Transmit Data bus bit 3.                                                                                        |  |  |  |

|                                             |                              |                | <b>RMII Mode:</b> Not used. Do not connect this pin in this mode of operation.                                                            |  |  |  |

| Port 7-6<br>Transmit Data 2                 | TXD[7:6]_2                   | IPD            | MII/RGMII Modes: Port 7-6 Transmit Data bus bit 2.                                                                                        |  |  |  |

|                                             |                              |                | <b>RMII Mode:</b> Not used. Do not connect this pin in this mode of operation.                                                            |  |  |  |

| Port 7-6<br>Transmit Data 1                 | TXD[7:6]_1                   | IPD            | MII/RMII/RGMII Modes: Port 7-6 Transmit Data bus bit 1.                                                                                   |  |  |  |

| Port 7-6<br>Transmit Data 0                 | TXD[7:6]_0                   | IPD            | MII/RMII/RGMII Modes: Port 7-6 Transmit Data bus bit 0.                                                                                   |  |  |  |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| NAME                                        | SYMBOL                                     | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                  |

|---------------------------------------------|--------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 7-6<br>Receive/<br>Reference<br>Clock  | RX_CLK[7:6]/<br>REFCLKO[7:6]               | I/O24          | MII Mode: RX_CLK[7:6] is the Port 7-6 25/2.5MHz Receive Clock. In PHY mode this pin is an output, in MAC mode it is an input.                                                                |

| Ciodic                                      |                                            |                | <b>RMII Mode: REFCLKO</b> [7:6] is the Port 7-6 50MHz Reference Clock output when in RMII Clock mode. This pin is unused when in RMII Normal mode.                                           |

|                                             |                                            |                | <b>RGMII Mode: RX_CLK[7:6]</b> is the Port 7-6 125/25/2.5MHz Receive Clock output.                                                                                                           |

| Port 7-6<br>Receive Data<br>Valid / Carrier | RX_DV[7:6]/<br>CRS_DV[7:6]/<br>RX_CTL[7:6] | IPD/O24        | <b>MII Mode: RX_DV</b> [7:6] is the Port 7-6 Received Data Valid output.                                                                                                                     |

| Sense / Control                             | ,                                          |                | RMII Mode: CRS_DV[7:6] is the Carrier Sense / Receive Data Valid output.                                                                                                                     |

|                                             |                                            |                | RGMII Mode: RX_CTL[7:6] is the Receive Control output.                                                                                                                                       |

|                                             |                                            |                | Note: The RX_DV7/CRS_DV7/RX_CTL7 pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information. |

| Port 7-6                                    | RX_ER[7:6]                                 | IPD/O24        | MII Mode: Port 7-6 Receive Error output.                                                                                                                                                     |

| Receive Error                               |                                            |                | <b>RMII/RGMII Modes:</b> Not used. Do not connect this pin in these modes of operation.                                                                                                      |

| Port 7-6<br>Carrier Sense                   | CRS[7:6]                                   | IPD/O8         | <b>MII Mode:</b> Port 7-6 Carrier Sense. In PHY mode this pin is an output, in MAC mode it is an input.                                                                                      |

|                                             |                                            |                | <b>RMII/RGMII Modes:</b> Not used. Do not connect this pin in these modes of operation.                                                                                                      |

| Port 7-6<br>Receive Data 3                  | RXD[7:6]_3                                 | IPD/O24        | MII/RGMII Modes: Port 7-6 Receive Data bus bit 3.                                                                                                                                            |

|                                             |                                            |                | <b>RMII Mode:</b> Not used. Do not connect this pin in this mode of operation.                                                                                                               |

|                                             |                                            |                | Note: These pins also provide configuration strap functions during hardware/software resets.  Refer to Section 3.2.1, "Configuration Straps" for additional information.                     |

| Port 7-6<br>Receive Data 2                  | RXD[7:6]_2                                 | IPD/O24        | MII/RGMII Modes: Port 7-6 Receive Data bus bit 2.                                                                                                                                            |

| 7                                           |                                            |                | <b>RMII Mode:</b> Not used. Do not connect this pin in this mode of operation.                                                                                                               |

|                                             |                                            |                | Note: These pins also provide configuration strap functions during hardware/software resets.  Refer to Section 3.2.1, "Configuration Straps" for additional information.                     |

| Port 7-6                                    | RXD[7:6]_1                                 | IPD/O24        | MII/RMII/RGMII Modes: Port 7-6 Receive Data bus bit 1.                                                                                                                                       |

| Receive Data 1                              |                                            |                | Note: These pins also provide configuration strap functions during hardware/software resets.  Refer to Section 3.2.1, "Configuration Straps" for additional information.                     |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| NAME                                                  | SYMBOL       | BUFFER<br>TYPE            | DESCRIPTION                                                                                                                                                                                                                                                |

|-------------------------------------------------------|--------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 7-6<br>Receive Data 0                            | RXD[7:6]_0   | IPD/O24                   | MII/RMII/RGMII Modes: Port 7-6 Receive Data bus bit 0.  Note: These pins also provide configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information.                            |

|                                                       |              | SPI/I <sup>2</sup> C/MIII | M Interface Pins                                                                                                                                                                                                                                           |

| SPI/I <sup>2</sup> C/MIIM<br>Serial Clock             | SCL/MDC      | IPU                       | SPI/I <sup>2</sup> C Modes: SCL serial clock.  MIIM Mode: MDC serial clock.                                                                                                                                                                                |

| SPI Data Out                                          | SDO          | O8                        | SPI Mode: Data out (also known as MISO).  I <sup>2</sup> C/MIIM Modes: Not used.                                                                                                                                                                           |

| SPI Data In /<br>I <sup>2</sup> C/MIIM Data<br>In/Out | SDI/SDA/MDIO | IPU/O8                    | SPI Mode: SDI Data In (also known as MOSI).  I <sup>2</sup> C Mode: SDA Data In/Out.  MIIM Mode: MDIO Data In/Out.  SDI and MDIO are open-drain signals when in the output state. An external pull-up resistor to VDDIO (1.0kΩ to 4.7kΩ) is required.      |

| SPI Chip Select                                       | SCS_N        | IPU                       | SPI Mode: Chip Select (active low).  I <sup>2</sup> C/MIIM Modes: Not used.  D Pins                                                                                                                                                                        |

| 5 / /                                                 |              |                           |                                                                                                                                                                                                                                                            |

| Port 1<br>LED Indicator 0                             | LED1_0       | IPU/O8                    | Port 1 LED Indicator 0.  Active low output sinks current to light an external LED.  Note: This pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information. |

| Port 1<br>LED Indicator 1                             | LED1_1       | IPU/O8                    | Port 1 LED Indicator 1.  Active low output sinks current to light an external LED.  Note: This pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information. |

| Port 2<br>LED Indicator 0                             | LED2_0       | IPU/O8                    | Port 2 LED Indicator 0.  Active low output sinks current to light an external LED.  Note: This pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information. |

| Port 2<br>LED Indicator 1                             | LED2_1       | IPU/O8                    | Port 2 LED Indicator 1. Active low output sinks current to light an external LED.  Note: This pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information.  |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| NAME                                | SYMBOL  | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                      |

|-------------------------------------|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 3<br>LED Indicator 0           | LED3_0  | IPU/O8         | Port 3 LED Indicator 0. Active low output sinks current to light an external LED.                                                                                                                                                                |

| Port 3<br>LED Indicator 1           | LED3_1  | IPU/O8         | Port 3 LED Indicator 1. Active low output sinks current to light an external LED.                                                                                                                                                                |

|                                     |         |                | Note: This pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information.                                                                           |

| Port 4<br>LED Indicator 0           | LED4_0  | IPU/O8         | Port 4 LED Indicator 0. Active low output sinks current to light an external LED.                                                                                                                                                                |

|                                     |         |                | Note: This pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information.                                                                           |

| Port 4<br>LED Indicator 1           | LED4_1  | IPU/O8         | Port 4 LED Indicator 1. Active low output sinks current to light an external LED.                                                                                                                                                                |

|                                     |         |                | Note: This pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information.                                                                           |

| Port 5<br>LED Indicator 0           | LED5_0  | IPU/O8         | Port 5 LED Indicator 0. Active low output sinks current to light an external LED.                                                                                                                                                                |

| Port 5<br>LED Indicator 1           | LED5_1  | IPU/O8         | Port 5 LED Indicator 1. Active low output sinks current to light an external LED.                                                                                                                                                                |

|                                     |         |                | Note: This pin also provides configuration strap functions during hardware/software resets. Refer to Section 3.2.1, "Configuration Straps" for additional information.                                                                           |

|                                     |         | Miscella       | aneous Pins                                                                                                                                                                                                                                      |

| Interrupt                           | INTRP_N | OPU            | Active low, open-drain interrupt.                                                                                                                                                                                                                |

|                                     |         |                | Note: This pin requires an external pull-up resistor.                                                                                                                                                                                            |

| Power<br>Management<br>Event        | PME_N   | O8             | Power Management Event. This output signal indicates that an energy detect event has occurred. It is intended to wake up the system from a low power mode.                                                                                       |

|                                     |         |                | Note: The assertion polarity is programmable (default active low). An external pull-up resistor is required for active-low operation; an external pull-down resistor is required for active-high operation.                                      |

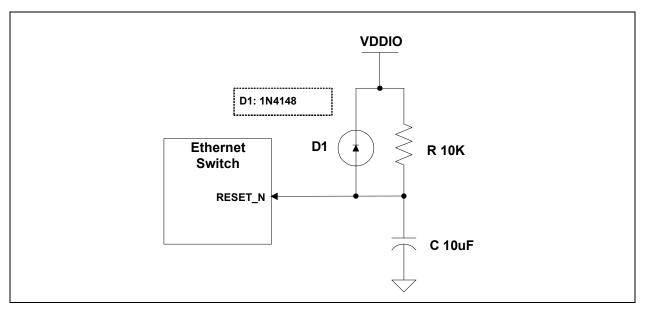

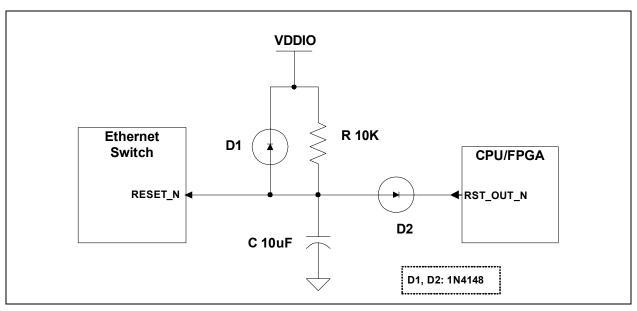

| System Reset                        | RESET_N | IPU            | Active low system reset. The device must be reset either during or after power-on. An RC circuit is suggested for power-on reset.                                                                                                                |

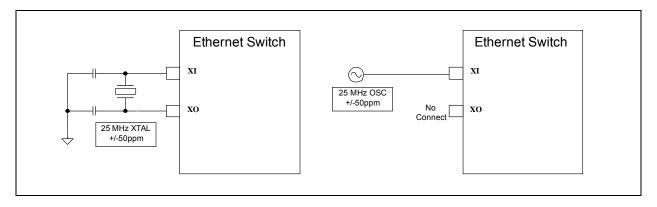

| Crystal Clock /<br>Oscillator Input | XI      | ICLK           | Crystal clock / oscillator input. When using a 25MHz crystal, this input is connected to one lead of the crystal. When using an oscillator, this pin is the input from the oscillator. The crystal oscillator should have a tolerance of ±50ppm. |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

|                                        | ,       |                | , '                                                                                                                                                                                                                                                                     |

|----------------------------------------|---------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                   | SYMBOL  | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                             |

| Crystal Clock<br>Output                | xo      | OCLK           | Crystal clock / oscillator output. When using a 25MHz crystal, this output is connected to one lead of the crystal. When using an oscillator, this pin is left unconnected.                                                                                             |

| 25/125MHz<br>Reference<br>Clock Output | SYNCLKO | O24            | 25/125MHz reference clock output, derived from the crystal input or the recovered clock of any PHY. This signal may be used for Synchronous Ethernet.                                                                                                                   |

| General<br>Purpose<br>Input/Output 1   | GPIO_1  | IPU/O8         | This signal can be used as an input or output for use by the IEEE 1588 event trigger or timestamp capture units. It will be synchronized to the internal IEEE 1588 clock. This pin can also be controlled (as an output) or sampled (as an input) via device registers. |

| Transmit Output Current Set Resistor   | ISET    | Α              | Transmit output current set resistor. This pin configures the physical transmit output current. It must be connected to GND through a 6.04k $\Omega$ 1% resistor.                                                                                                       |

| No Connect                             | NC      | -              | No Connect. For proper operation, this pin must be left unconnected.                                                                                                                                                                                                    |

|                                        |         | Power/C        | Ground Pins                                                                                                                                                                                                                                                             |

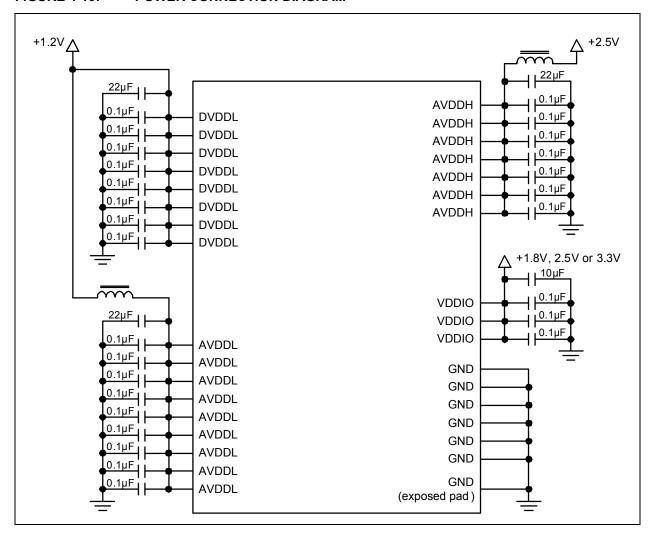

| +3.3/2.5/1.8V<br>I/O Power             | VDDIO   | Р              | +3.3V / +2.5V / +1.8V I/O Power                                                                                                                                                                                                                                         |

| +3.3/2.5V<br>Analog Power              | AVDDH   | Р              | +3.3V / +2.5V Analog Power                                                                                                                                                                                                                                              |

| +1.2V<br>Analog Power                  | AVDDL   | Р              | +1.2V Analog Power                                                                                                                                                                                                                                                      |

| +1.2V<br>Digital Power                 | DVDDL   | Р              | +1.2V Digital Power                                                                                                                                                                                                                                                     |

| Ground                                 | GND     | GND            | Ground (pins and pad)                                                                                                                                                                                                                                                   |

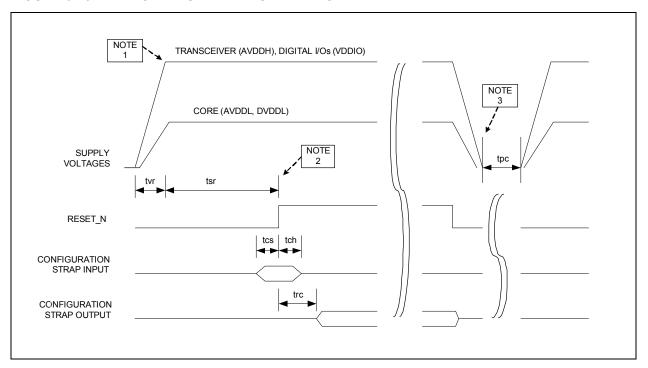

# 3.2.1 CONFIGURATION STRAPS

The KSZ8567R utilizes configuration strap pins to configure the device for different modes. While RESET\_N is low, these pins are hi-Z. Pull-up/down resistors are used to create high or low states on these pins, which are internally sampled at the rising edge of RESET\_N. All of these pins have a weak internal pull-up or pull-down resistor which provides a default level for strapping. To strap an LED pin low, use a 750 $\Omega$  to 1k $\Omega$  external pull-down resistor. To strap a non-LED pin high, use an external 1k $\Omega$  to 10k $\Omega$  pull-up resistor to VDDIO. Once RESET\_N is high, all of these pins become driven outputs.

Because the internal pull-up/down resistors are not strong, consideration must be given to any other pull-up/down resistors which may reside on the board or inside a device connected to these pins.

When an LED pin is directly driving an LED, the effect of the LED and LED load resistor on the strapping level must be considered. This is the reason for using a small value resistor to pull an LED pin low. This is especially true when an LED is powered from a voltage that is higher than **VDDIO**.

The configuration strap pins and their associated functions are detailed in Table 3-3.

TABLE 3-3: CONFIGURATION STRAP DESCRIPTIONS

| CONFIGURATION<br>STRAP PIN | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED1_0                     | Quiet-WIRE Filtering Enable 0: Quiet-WIRE filtering enabled 1: Quiet-WIRE filtering disabled (Default)                                                                                                                                                                                                                                                                                                                                                                               |

| LED1_1                     | Flow Control (All Ports)  0: Flow control disabled  1: Flow control enabled (Default)                                                                                                                                                                                                                                                                                                                                                                                                |

| LED2_1                     | Link-up Mode (All PHYs)  0: Fast Link-up: Auto-negotiation and auto MDI/MDI-X are disabled  1: Normal Link-up: Auto-negotiation and auto MDI/MDI-X are enabled (Default)  Note: Since Fast Link-up disables auto-negotiation and auto-crossover, it is suitable only for specialized applications.                                                                                                                                                                                   |

| LED4_0, LED2_0             | When LED2_1 = 1 at strap-in (Normal Link-up):  [LED4_0, LED2_0]: Auto-Negotiation Enable (All PHYs) / NAND Tree Test Mode 00: Reserved 01: Auto-negotiation disabled, forced as 100 Mbps and half duplex. Auto-MDI-X is on. 10: NAND Tree test mode 11: Auto-negotiation enabled (Default)  When LED2_1 = 0 at strap-in (Fast Link-up; All PHYs Full-Duplex; Auto-negotiation and Auto-MDI-X are off):  LED2_0: MDI/MDI-X Mode (All PHYs) 0: MDI-X 1: MDI (Default) LED4_0: Not Used |

| LED4_1, LED3_1             | [LED4_1, LED3_1]: Management Interface Mode 00: MIIM (MDIO) 01: I <sup>2</sup> C 1x: SPI (Default)                                                                                                                                                                                                                                                                                                                                                                                   |

| LED5_1                     | Switch Enable at Startup  Start Switch is disabled. The switch will not forward packets until the Start Switch bit is set in the Switch Operation Register.  Start Switch is enabled. The switch will forward packets immediately after reset. (Default)                                                                                                                                                                                                                             |

| RXD6_3, RXD6_2             | [RXD6_3, RXD6_2]: Port 6 Mode  00: RGMII (Default)  01: RMII  10: Reserved  11: MII                                                                                                                                                                                                                                                                                                                                                                                                  |

TABLE 3-3: CONFIGURATION STRAP DESCRIPTIONS (CONTINUED)

| CONFIGURATION<br>STRAP PIN | DESCRIPTION                                                                                                                                                                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD6_1                     | Port 6 MII/RMII Mode  0: MII: PHY Mode (Default) RMII: Clock Mode. RMII 50MHz reference clock is output on REFCLKO6. (Default) RGMII: No effect  1: MII: MAC Mode RMII: Normal Mode. RMII 50MHz reference clock is input on REFCLKI6. RGMII: No effect |

| RXD6_0                     | Port 6 Speed Select 0: 1000Mbps Mode (Default) 1: 100Mbps Mode  Note: If Port 6 is configured for MII or RMII, set the speed to 100Mbps.                                                                                                               |

| RXD7_3, RXD7_2             | [RXD7_3, RXD7_2]: Port 7 Mode  00: RGMII (Default)  01: RMII  10: Reserved  11: MII                                                                                                                                                                    |

| RXD7_1                     | Port 7 MII/RMII Mode  0: MII: PHY Mode (Default) RMII: Clock Mode. RMII 50MHz reference clock is output on REFCLKO7. (Default) RGMII: No effect  1: MII: MAC Mode RMII: Normal Mode. RMII 50MHz reference clock is input on REFCLKI7. RGMII: No effect |

| RXD7_0                     | Port 7 Speed Select 0: 1000Mbps Mode (Default) 1: 100Mbps Mode  Note: If Port 7 is configured for MII or RMII, set the speed to 100Mbps.                                                                                                               |

| RX_DV7/CRS_DV7/<br>RX_CTL7 | In-Band Management 0: Disable In-Band Management (Default) 1: Enable In-Band Management                                                                                                                                                                |

# 4.0 FUNCTIONAL DESCRIPTION

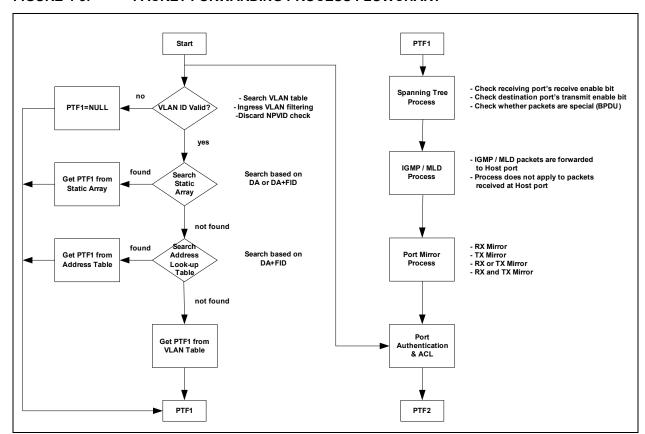

This section provides functional descriptions for the following:

- Physical Layer Transceiver (PHY)

- LEDs

- · Media Access Controller (MAC)

- Switch

- IEEE 1588 Precision Time Protocol

- · Audio Video Bridging and Time Sensitive Networks

- · NAND Tree Support

- Clocking

- Power

- · Power Management

- Management Interface

- · In-Band Management

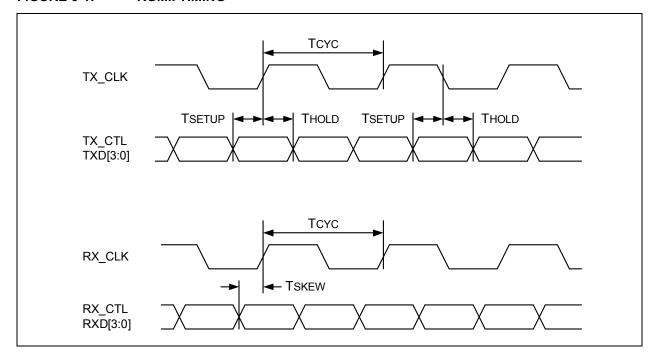

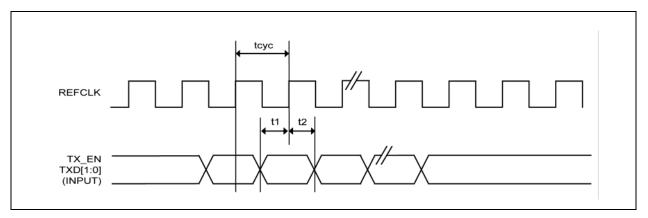

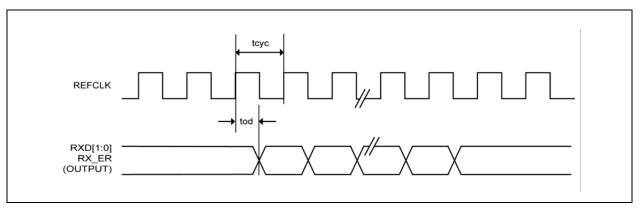

- MAC Interface (RGMII/MII/RMII Port 6-7)

# 4.1 Physical Layer Transceiver (PHY)

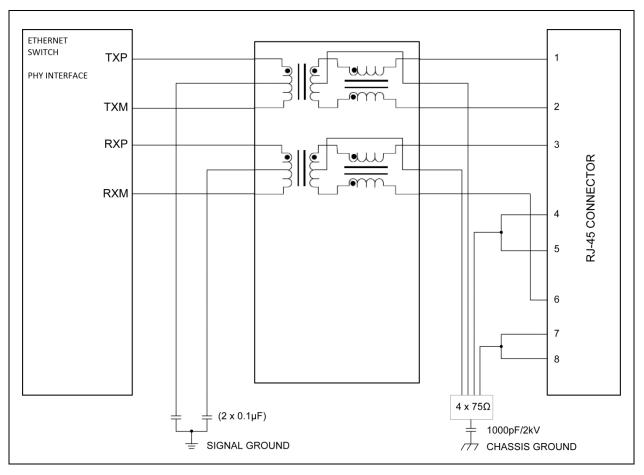

Ports 1 through 5 include completely integrated dual-speed (10BASE-T/Te, 100BASE-TX) Ethernet physical layer transceivers for transmission and reception of data over standard four-pair unshielded twisted pair (UTP), CAT-5 or better Ethernet cable. At 100Mbps, the optional Quiet-WIRE filtering feature reduced emissions while maintaining interoperability with standard 100BASE-TX devices.

The device reduces board cost and simplifies board layout by using on-chip termination resistors for the differential pairs, eliminating the need for external termination resistors. The internal chip termination and biasing provides significant power savings when compared with using external biasing and termination resistors.

## 4.1.1 100BASE-TX TRANSCEIVER

## 4.1.1.1 100BASE-TX Transmit

The 100BASE-TX transmit function performs parallel-to-serial conversion, 4B/5B coding, scrambling, NRZ-to-NRZI conversion, and MLT3 encoding and transmission.

The circuitry starts with a parallel-to-serial conversion, which converts the MII data from the MAC into a 125MHz serial bit stream. The data and control stream is then converted into 4B/5B coding, followed by a scrambler. The serialized data is further converted from NRZ-to-NRZI format, and then transmitted in MLT3 current output. An external ISET resistor sets the output current for the 1:1 transformer ratio.

The output signal has a typical rise/fall time of 4ns and complies with the ANSI TP-PMD standard regarding amplitude balance, overshoot, and timing jitter. The wave-shaped 10BASE-T/Te output driver is also incorporated into the 100BASE-TX driver.

### 4.1.1.2 100BASE-TX Receive

The 100BASE-TX receiver function performs adaptive equalization, DC restoration, MLT3-to-NRZI conversion, data and clock recovery, NRZI-to-NRZ conversion, de-scrambling, 4B/5B decoding, and serial-to-parallel conversion.

The receiving side starts with the equalization filter to compensate for inter-symbol interference (ISI) over the twisted pair cable. Since the amplitude loss and phase distortion is a function of the cable length, the equalizer has to adjust its characteristics to optimize performance. In this design, the variable equalizer makes an initial estimation based on comparisons of incoming signal strength against some known cable characteristics, and then tunes itself for optimization. This is an ongoing process and self-adjusts against environmental changes such as temperature variations.

Next, the equalized signal goes through a DC restoration and data conversion block. The DC restoration circuit is used to compensate for the effect of baseline wander and to improve the dynamic range. The differential data conversion circuit converts the MLT3 format back to NRZI. The slicing threshold is also adaptive.