### **Product Overview**

The Qorvo QPD1025 is a 1800 W ( $P_{3dB}$ ) discrete GaN on SiC HEMT which operates from 0.96 to 1.215 GHz. Input prematch within the package results in ease of external board match and saves board space. The device is in an industry standard air cavity package and is ideally suited for IFF, avionics and test instrumentation. The device can support both CW and pulsed operations.

RoHS compliant

Evaluation boards are available upon request.

4-lead NI-1230 Package (Earless)

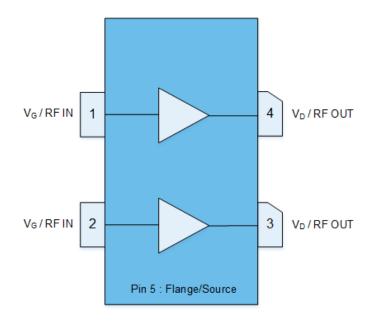

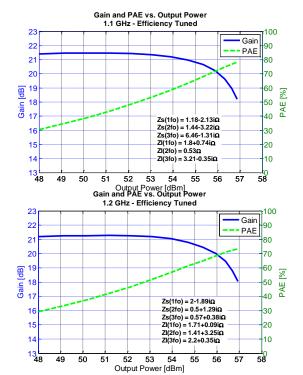

# **Functional Block Diagram**

### **Key Features**

Frequency: 0.96 to 1.215 GHz

Output Power (P3dB)<sup>1</sup>: 1862 W

Linear Gain<sup>1</sup>: 22.5 dB

Typical PAE<sub>3dB</sub><sup>1</sup>: 77.2%

Operating Voltage: 65 V

• CW and Pulse capable

Note 1: @ 1.0 GHz Load Pull

# **Applications**

- IFF Transponders

- DME radar

- Avionics

# Ordering info

| Part No.    | Description                                  |

|-------------|----------------------------------------------|

| QPD1025     | 0.96 – 1.215 GHz Transistor (18 pcs in tray) |

| QPD1025EVB1 | 1.0 – 1.1 GHz Evaluation Board               |

| QPD1025EVB2 | 0.96 – 1.215 GHz Evaluation Board            |

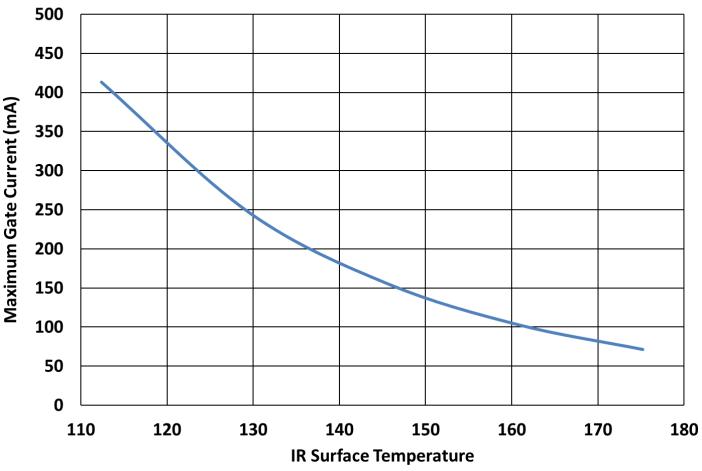

### **Absolute Maximum Ratings** 1,2,3

| Parameter                                     | Rating      | Units |

|-----------------------------------------------|-------------|-------|

| Breakdown Voltage,BVpg                        | 225         | V     |

| Gate Voltage Range, Vo                        | -7 to +2    | V     |

| Drain Current, IDMAX                          | 142         | Α     |

| Gate Current Range, Ig                        | See pg. 12  | mA    |

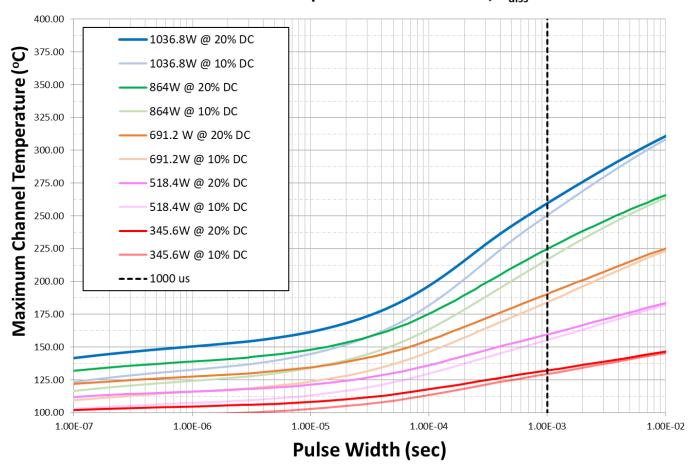

| Power Dissipation, Pulsed, PDISS <sup>2</sup> | 1209        | W     |

| RF Input Power, Pulsed, Pin 3                 | 46.2        | dBm   |

| Mounting Temperature (30 Seconds)             | 320         | °C    |

| Storage Temperature                           | −65 to +150 | °C    |

#### Notes:

- 1. Operation of this device outside the parameter ranges given above may cause permanent damage

- 2. Pulsed, 1000us PW, 20% DC, Package base at 85 °C

- 3. Pulsed, 100us PW, 10% DC, T = 25 °C

### Recommended Operating Conditions 1, 2, 3, 4

| Parameter                                            | Min | Тур  | Max | Units |

|------------------------------------------------------|-----|------|-----|-------|

| Operating Temp. Range                                | -40 | +25  | +85 | °C    |

| Drain Voltage Range, VD                              | _   | +65  | +70 | V     |

| Drain Bias Current, IDQ                              |     | 1.5  |     | Α     |

| Drain Current, In 4                                  | _   | 28   | _   | Α     |

| Gate Voltage, Vg3                                    | _   | -2.8 | _   | V     |

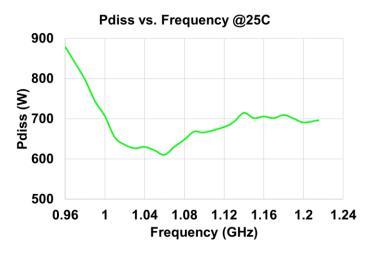

| Power Dissipation (PD) 2,4                           | _   | _    | 685 | W     |

| Power Dissipation (P <sub>D</sub> ), CW <sup>2</sup> | _   | _    | 496 | W     |

#### Notes:

- Electrical performance is measured under conditions noted in the electrical specifications table. Specifications are not guaranteed over all recommended operating conditions

- 2. Package base at 85 °C

- 3. To be adjusted to desired  $I_{DQ}$

- 4. Pulsed, 1000us PW, 20% DC

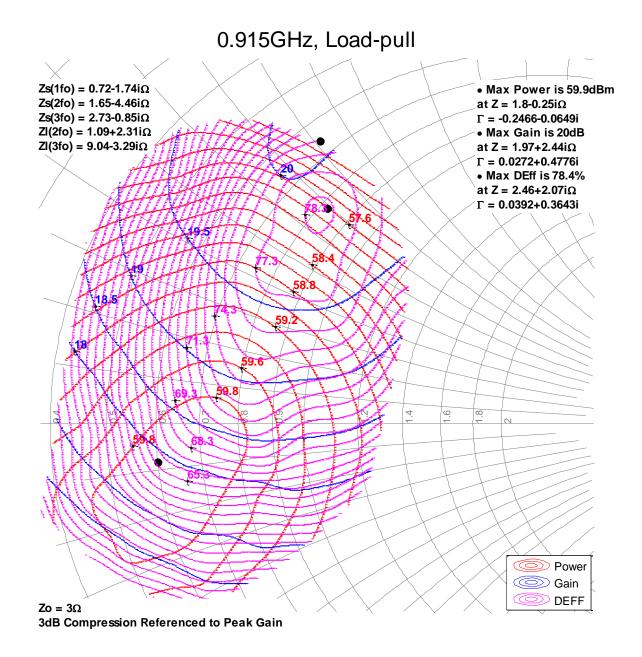

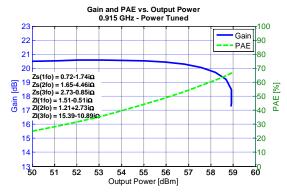

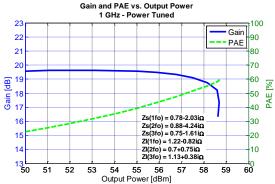

### Measured Load Pull Performance - 65V Power Tuned 1,2

| Parameter                                          |       | Туріса | l Values |      | Units |

|----------------------------------------------------|-------|--------|----------|------|-------|

| Frequency, F                                       | 0.915 | 1.0    | 1.1      | 1.2  | GHz   |

| Output Power at 3dB compression, P3dB              | 59.9  | 59.7   | 59.7     | 59.8 | dBm   |

| Power Added Efficiency at 3dB compression, PAE 3dE | 63.2  | 62.8   | 65.7     | 61.9 | %     |

| Gain at 3dB compression, G <sub>3dB</sub>          | 17.9  | 17.5   | 17.3     | 17.2 | dB    |

#### Notes:

- 1. Test conditions unless otherwise noted: T<sub>A</sub> = 25 °C, V<sub>D</sub> = 65 V, I<sub>DQ</sub> = 750 mA (half device)

- 2. Pulsed, 100 us Pulse Width, 10% Duty Cycle.

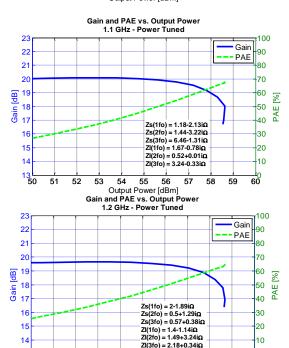

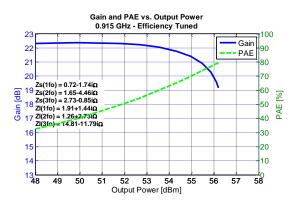

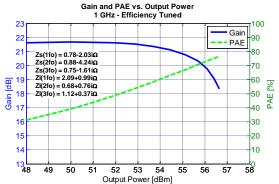

# Measured Load Pull Performance – 65V Efficiency Tuned <sup>1, 2</sup>

| Parameter                                                     |       | Туріса | ıl Values |      | Units |

|---------------------------------------------------------------|-------|--------|-----------|------|-------|

| Frequency, F                                                  | 0.915 | 1.0    | 1.1       | 1.2  | GHz   |

| Output Power at 3dB compression, P <sub>3dB</sub>             | 57.5  | 57.7   | 58.5      | 58.3 | dBm   |

| Power Added Efficiency at 3dB compression, PAE <sub>3dE</sub> | 77.6  | 77.2   | 77.0      | 74.6 | %     |

| Gain at 3dB compression, G <sub>3dB</sub>                     | 19.7  | 19.5   | 18.7      | 19.0 | dB    |

- 1. Test conditions unless otherwise noted: T<sub>A</sub> = 25 °C, V<sub>D</sub> = 65 V, I<sub>DQ</sub> = 750 mA (half device)

- 2. Pulsed, 100 us Pulse Width, 10% Duty Cycle.

# Measured Load Pull Performance – 50V Power Tuned 1,2

| Parameter                                          |       | Typica | al Values |      | Units |

|----------------------------------------------------|-------|--------|-----------|------|-------|

| Frequency, F                                       | 0.915 | 1.0    | 1.1       | 1.2  | GHz   |

| Output Power at 3dB compression, P3dB              | 58.9  | 58.6   | 58.5      | 58.6 | dBm   |

| Power Added Efficiency at 3dB compression, PAE 3dE | 66.8  | 60.1   | 66.1      | 62.6 | %     |

| Gain at 3dB compression, G3dB                      | 17.6  | 17     | 17        | 16.8 | dB    |

#### Notes:

- 1. Test conditions unless otherwise noted: T<sub>A</sub> = 25 °C, V<sub>D</sub> = 50 V, I<sub>DQ</sub> = 750 mA (half device)

- 2. Pulsed, 100 us Pulse Width, 10% Duty Cycle.

# Measured Load Pull Performance - 50V Efficiency Tuned 1,2

| Parameter                                                     |       | Туріса | l Values |      | Units |

|---------------------------------------------------------------|-------|--------|----------|------|-------|

| Frequency, F                                                  | 0.915 | 1.0    | 1.1      | 1.2  | GHz   |

| Output Power at 3dB compression, P3dB                         | 55.2  | 55.6   | 56.5     | 56.8 | dBm   |

| Power Added Efficiency at 3dB compression, PAE <sub>3dE</sub> | 78.2  | 74.7   | 76.6     | 71.8 | %     |

| Gain at 3dB compression, G <sub>3dB</sub>                     | 19.2  | 19     | 18.6     | 18.2 | dB    |

- 1. Test conditions unless otherwise noted:  $T_A = 25$  °C,  $V_D = 50$  V,  $I_{DQ} = 750$  mA (half device)

- 2. Pulsed, 100 us Pulse Width, 10% Duty Cycle.

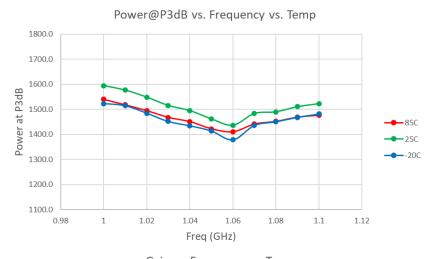

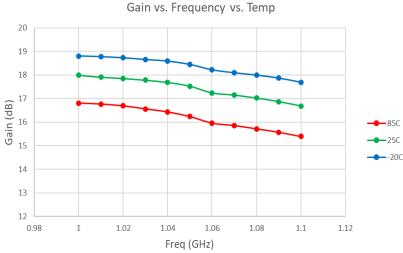

## RF Characterization – 1.0 – 1.1 GHz EVB1 Performance at 1.05 GHz <sup>1</sup>

| Parameter                                          | Min               | Тур  | Max | Units |

|----------------------------------------------------|-------------------|------|-----|-------|

| Linear Gain, GLIN                                  | _                 | 21.2 | _   | dB    |

| Output Power at 3dB compression point, P3dB        | _                 | 1461 | _   | W     |

| Drain Efficiency at 3dB compression point, DEFF3dB | _                 | 73.2 | _   | %     |

| Gain at 3dB compression point, G3dB                | _                 | 18.2 | _   | dB    |

| Gate Leakage VD = +10 V, VG = −3.3 V               | - 25 <sup>2</sup> | _    | _   | mA    |

#### Notes:

- 1.  $V_D = 65 \text{ V}$ ,  $I_{DQ} = 1.5 \text{ A}$  (combined), Temp = +25 °C, Pulse Width = 100 us, Duty Cycle = 10%

- 2. Gate leakage per path

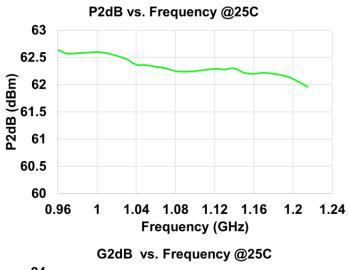

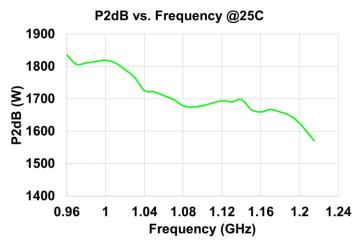

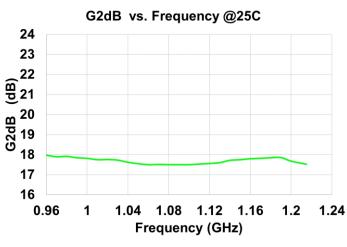

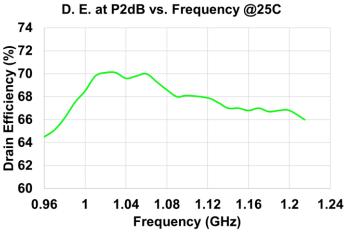

### RF Characterization - 0.96 - 1.215 GHz EVB2 Performance<sup>1</sup>

| Parameter                                          | Typ 0.96 GHz      | Typ 1.08 GHz | Typ 1.2GHz | Units |

|----------------------------------------------------|-------------------|--------------|------------|-------|

| Linear Gain, GLIN                                  | 20                | 19.5         | 19.6       | dB    |

| Output Power at 2dB compression point, P2dB        | 1800              | 1678         | 1570       | W     |

| Drain Efficiency at 2dB compression point, DEFF2dB | 64                | 68           | 66         | %     |

| Gain at 3dB compression point, G2dB                | 18                | 17.5         | 17.6       | dB    |

| Gate Leakage VD = +10 V, VG = −3.3 V               | - 25 <sup>2</sup> | _            | _          | mA    |

#### Notes:

- 1.  $V_D = 65 \text{ V}$ ,  $I_{DQ} = 1.5 \text{ A}$  (combined), Temp = +25 °C, Pulse Width = 100 us, Duty Cycle = 10%

- 2. Gate leackage per path

# RF Characterization – Mismatch Ruggedness at 1.0 GHz 1, 2,3

| Symbol | Parameter                     | dB Compression | Typical |

|--------|-------------------------------|----------------|---------|

| VSWR   | Impedance Mismatch Ruggedness | 3              | 10:1    |

- 1. Test conditions unless otherwise noted:  $T_A = 25 \, ^{\circ}\text{C}$ ,  $V_D = 65 \, \text{V}$ ,  $I_{DQ} = 1.5 \, \text{A}$  (combined)

- 2. Input drive power is determined at pulsed 3dB compression under matched condition at EVB output connector

- 3. Pulse: 100us, 10% Duty cycle

# **Maximum Gate Current vs. IR Surface Temperature**

# Thermal and Reliability Information - Pulsed 1

# Peak IR Surface Temperature vs. Pulse Width Base temperature fixed at 85 °C, P<sub>diss</sub> Varies

| Parameter                                                   | Conditions                              | Values | Units |

|-------------------------------------------------------------|-----------------------------------------|--------|-------|

| Thermal Resistance, IR <sup>1</sup> (θ <sub>JC</sub> )      | 85 °C Case backside Temperature         | 0.10   | °C/W  |

| Peak IR Surface Temperature <sup>1</sup> (T <sub>ch</sub> ) | Pdiss = 518 W, Pulse: 100 us PW, 10% DC | 131    | °C    |

#### Notes

1. Refer to the following document GaN Device Channel Temperature, Thermal Resistance, and Reliability Estimates

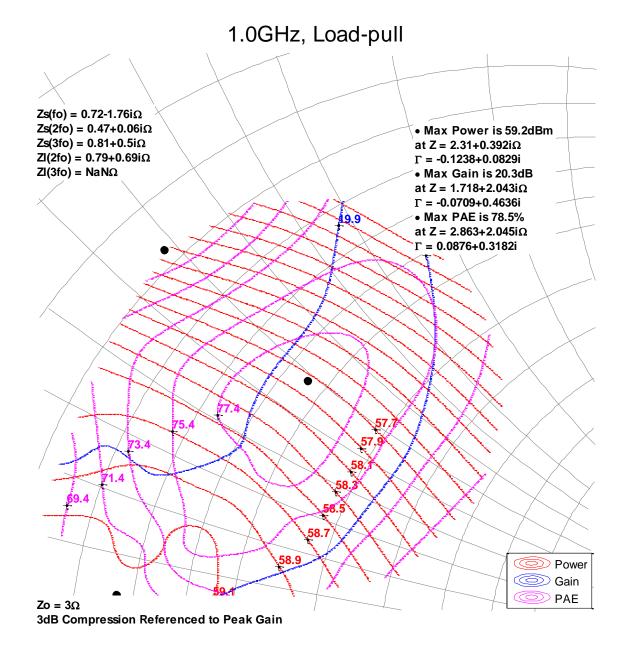

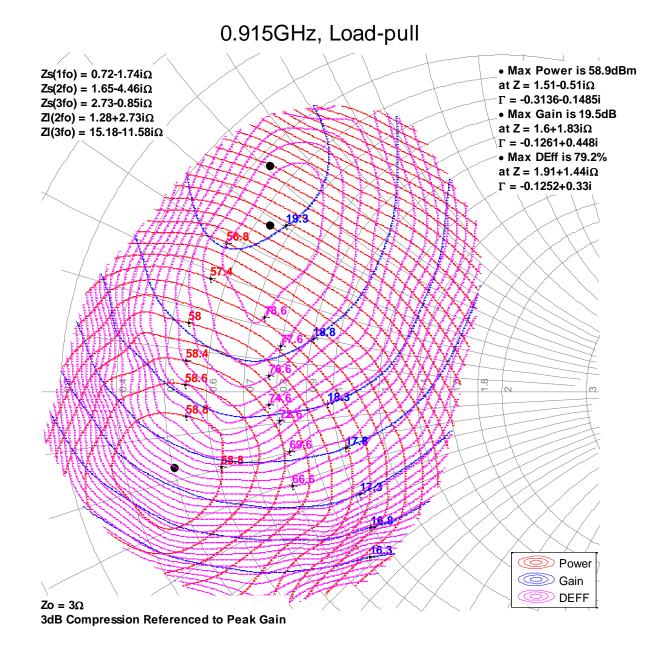

## Measured Load-Pull Smith Charts at 65V 1, 2, 3

- 1. Test Conditions: V<sub>D</sub> = 65 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 2. The performance shown below is for only half of the device out of the two independent amplification paths.

- 3. See page 18 for load pull reference planes where the performance was measured.

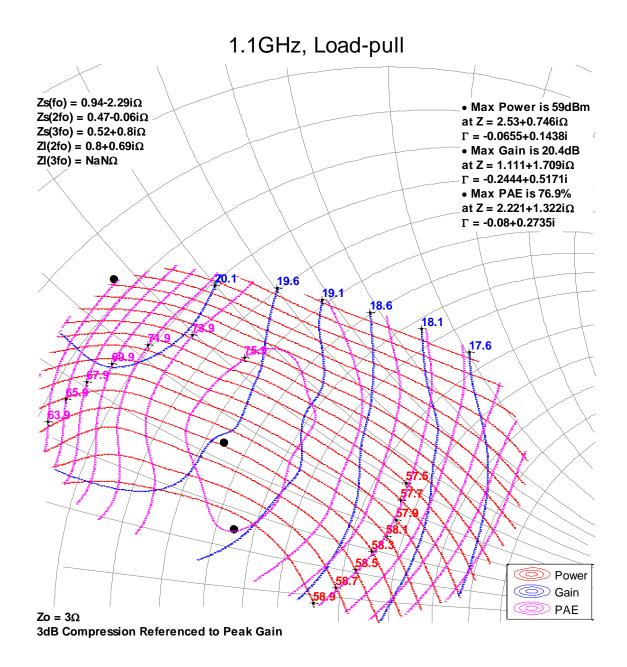

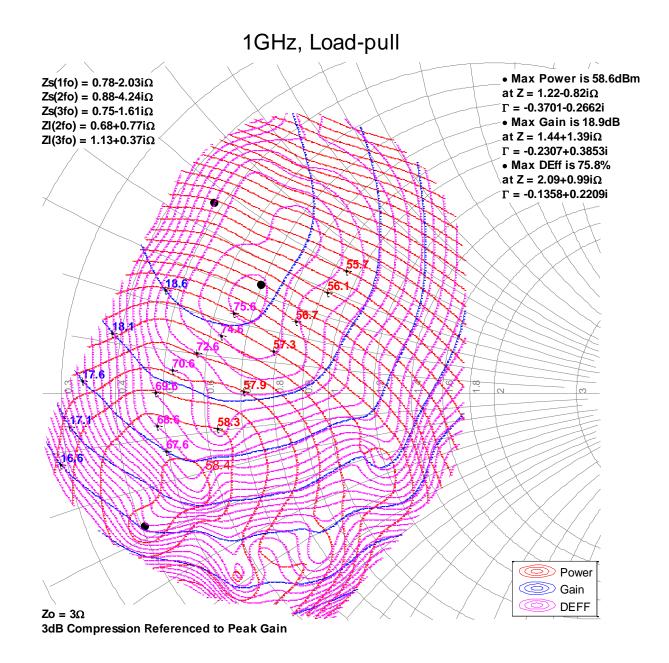

## Measured Load-Pull Smith Charts at 65V 1, 2, 3

- 5. Test Conditions: V<sub>D</sub> = 65 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 6. The performance shown below is for only half of the device out of the two independent amplification paths.

- 7. See page 18 for load pull reference planes where the performance was measured.

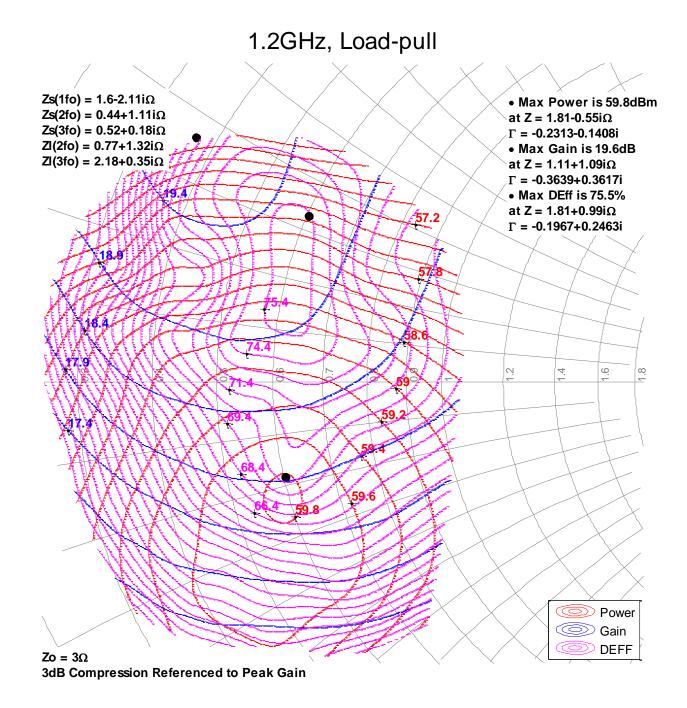

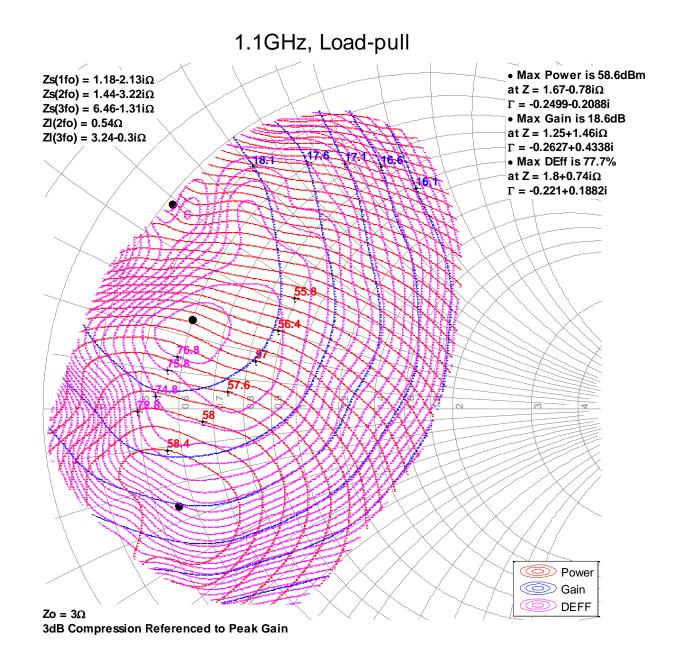

### Measured Load-Pull Smith Charts at 65V 1,2,3

- 1. Test Conditions: V<sub>D</sub> = 65 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 2. The performance shown below is for only half of the device out of the two independent amplification paths.

- 3. See page 18 for load pull reference planes where the performance was measured.

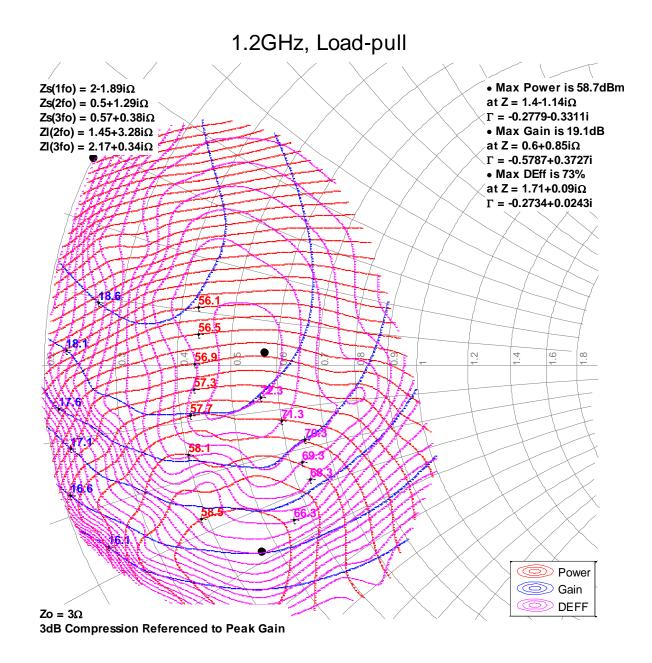

## Measured Load-Pull Smith Charts at 65V 1, 2, 3

- 1. Test Conditions: V<sub>D</sub> = 65 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 2. The performance shown below is for only half of the device out of the two independent amplification paths.

- 3. See page 18 for load pull reference planes where the performance was measured.

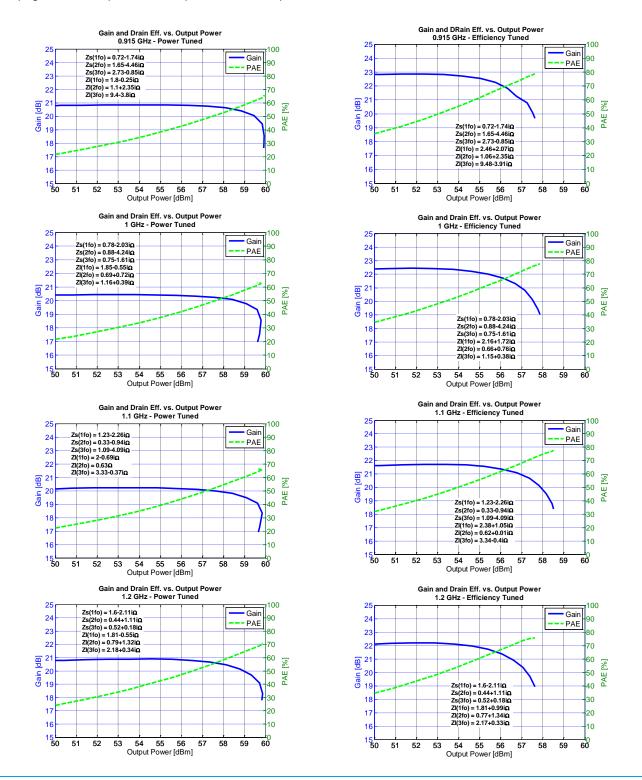

# Typical Measured Performance - Load-Pull Drive-up at 65V 1, 2, 3

- 1. Test Conditions: V<sub>D</sub> = 65 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 2. The performance shown below is for only half of the device out of the two independent amplification paths.

- 3. See page 18 for load pull reference planes where the performance was measured.

## Measured Load-Pull Smith Charts at 50V 1, 2, 3

- 1. Test Conditions: V<sub>D</sub> = 50 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 2. The performance shown below is for only half of the device out of the two independent amplification paths.

- 3. See page 18 for load pull reference planes where the performance was measured.

## Measured Load-Pull Smith Charts at 50V 1, 2, 3

- 5. Test Conditions: V<sub>D</sub> = 50 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 6. The performance shown below is for only half of the device out of the two independent amplification paths.

- 7. See page 18 for load pull reference planes where the performance was measured.

## Measured Load-Pull Smith Charts at 50V 1, 2, 3

- 1. Test Conditions: V<sub>D</sub> = 50 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 2. The performance shown below is for only half of the device out of the two independent amplification paths.

- 3. See page 18 for load pull reference planes where the performance was measured.

## Measured Load-Pull Smith Charts at 50V 1, 2, 3

- 1. Test Conditions: V<sub>D</sub> = 50 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 2. The performance shown below is for only half of the device out of the two independent amplification paths.

- 3. See page 18 for load pull reference planes where the performance was measured.

# Typical Measured Performance - Load-Pull Drive-up at 50V 1, 2, 3

#### Notes:

- 1. Test Conditions: V<sub>D</sub> = 50 V, I<sub>DQ</sub> = 750 mA, 100 us Pulse Width, 10% Duty Cycle, Temp = 25°C.

- 2. The performance shown below is for only half of the device out of the two independent amplification paths.

- 3. See page 18 for load pull reference planes where the performance was measured.

55 56

Output Power [dBm]

57 58 59

60

13 50

51 52 53 54

# Pin Configuration and Description <sup>1</sup>

#### Note:

1- The QPD1025 will be marked with the "QPD1025" designator and a lot code marked below the part designator. The "YY" represents the last two digits of the calendar year the part was manufactured, the "WW" is the work week of the assembly lot start, the "MXXX" is the production lot number, and the "ZZZ" is an auto-generated serial number.

| Pin  | Symbol                  | Description                        |

|------|-------------------------|------------------------------------|

| 1, 2 | RF IN / Vg              | Gate                               |

| 3, 4 | RF OUT / V <sub>D</sub> | Drain                              |

| 5    | Source                  | Source / Ground / Backside of part |

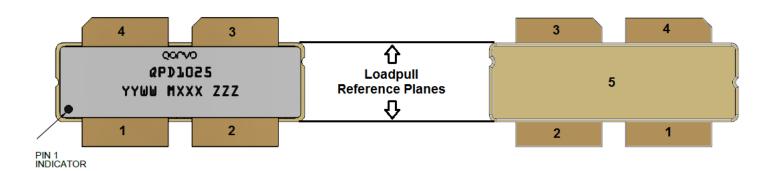

# Mechanical Drawing 1

- 1. All dimensions are in inches.

- 2. Dimension tolerance is  $\pm$  0.005 inches, unless noted otherwise.

- 3. Package base: Ceramic/Metal, Package lid: Ceramic

- 4. Package exposed metalization is gold plated

- 5. Part is epoxy sealed.

- 6. Parts meet industry NI1230 footprint

- 7. Body dimensions do not include runout which can be up to 0.020 inches per side.

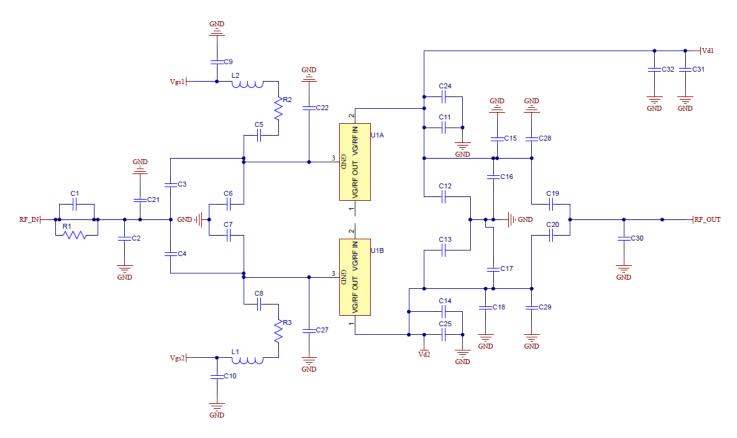

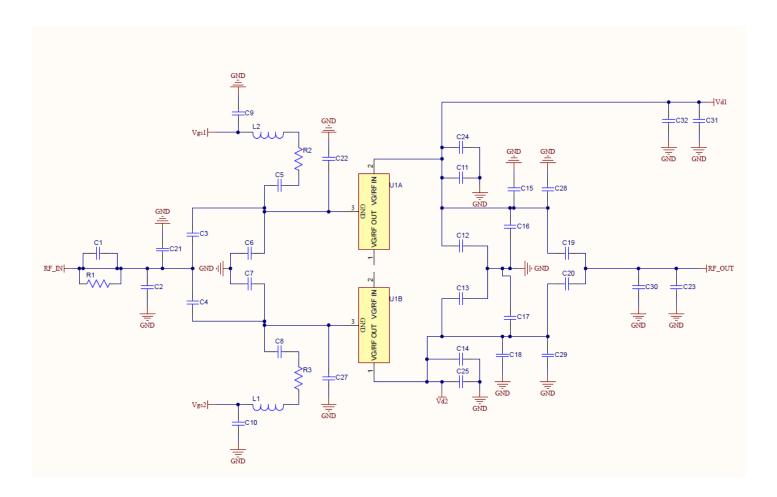

# 1.0 – 1.1 GHz Application Circuit - Schematic

| Bias-up Procedure                                                     | Bias-down Procedure                                      |

|-----------------------------------------------------------------------|----------------------------------------------------------|

| 1. Set V <sub>G</sub> to -5 V.                                        | 1. Turn off RF signal.                                   |

| 2. Set I <sub>D</sub> current limit to 4 A.                           | 2. Turn off V <sub>D</sub>                               |

| 3. Apply 65 V V <sub>D</sub> .                                        | 3. Wait 2 seconds to allow drain capacitor to discharge. |

| 4. Slowly adjust V <sub>G</sub> until I <sub>D</sub> is set to 1.5 A. | 4. Turn off V <sub>G</sub>                               |

| 5. Apply RF.                                                          |                                                          |

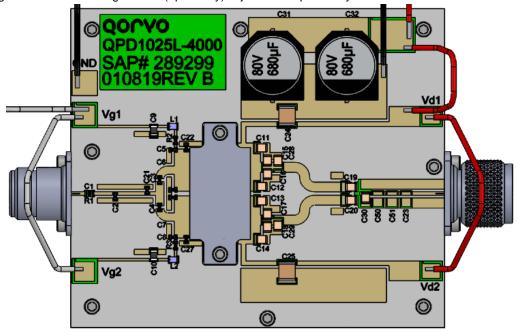

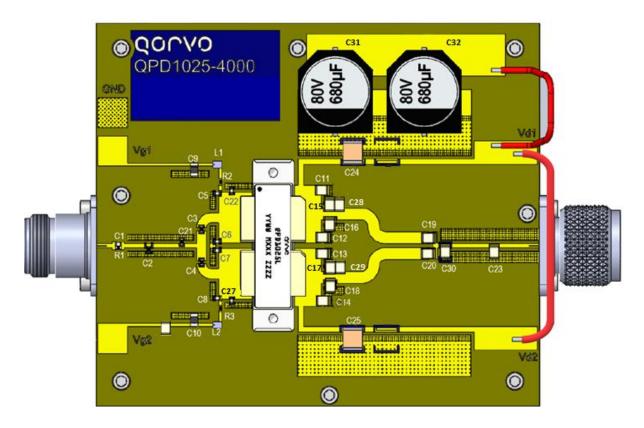

# 1.0 - 1.1 GHz Application Circuit EVB1 - Layout 1,2

#### Notes:

- 1. PCB material is RO4350B 0.020" thick, 2 oz. copper each side.

- 2. The two gates could be tied together or (optionally) adjusted independently.

# 1.0 – 1.1 GHz Application Circuit – Bill of Material EVB1

| Reference Design | Value      | Qty | Manufacturer                 | Part Number         |

|------------------|------------|-----|------------------------------|---------------------|

| U1               |            | 1   | QORVO                        | QPD1025L            |

| C1,C5,C8         | 8.2pF      | 3   | American Technical Ceramics  | 600S8R2BT250XT      |

| C11,C12,C13,C14  | 10pF       | 4   | American Technical Ceramics  | 100B100JW500XT      |

| C15,C18          | 5.6pF      | 2   | American Technical Ceramics  | 100B5R6CT500XT      |

| C16,C17,C28,C29  | 6.8pF      | 4   | American Technical Ceramics  | 800B6R8CT500XT      |

| C19,C20          | 56pF       | 2   | American Technical Ceramics  | 800B560JT500XT      |

| C2               | 0.7pF      | 1   | American Technical Ceramics  | 800B560JT500XT      |

| C21,C22,C27      | 6.8pF      | 3   | American Technical Ceramics  | 100B100JW500XT      |

| C24,C25          | 10uF       | 2   | TDK Signapore PDE LTD        | C5750X7S2A106M230KB |

| C3,C4            | 20pF       | 2   | American Technical Ceramics  | 600S200FT250XT      |

| C30              | 3pF        | 1   | American Technical Ceramics  | 800B3R0BT500XT      |

| C31,C32          | 680uF      | 2   | Vishay Americas Inc          | MAL215099708E3      |

|                  | 5.6pF      | 2   | American Technical Ceramics  | 600S5R6BW250XT      |

| C9,C10           | 4.7uF      | 2   | Murata Electronics           | GRM31CR71H475KA12L  |

| L1,L2            | 110nH      | 2   | Coilcraft, Inc               | 0805CS-111XJBC      |

| R1               | 47         | 1   | Panasonic Industrial Devices | KTR03EZPF47R0       |

| R2,R3            | 10         | 2   | Vishay Dale Electronics      | CRCW060310R0FKEA    |

| Connector        | N type F/M | 1   | Huber+Suhner, Inc            | 23_N-50-0-33/133_NE |

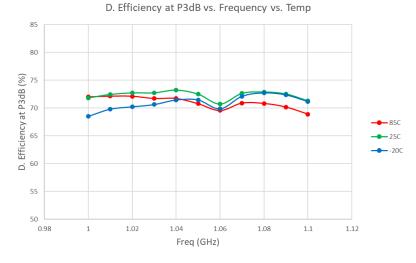

# Power Driveup Performance over Temperatures of 1.0 – 1.1 GHz EVB1 <sup>1</sup>

#### Notes:

1. Test Conditions:  $V_D = 65 \text{ V}$ ,  $I_{DQ} = 1.5 \text{ A}$ , 100 us Pulse Width, 10% Duty Cycle.

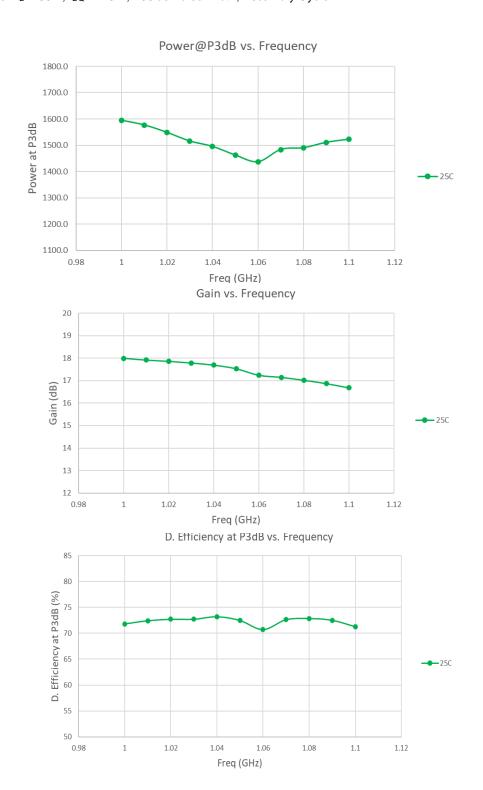

# Power Driveup Performance at 25°C of 1.0 – 1.1 GHz EVB1 <sup>1</sup>

#### Notes:

1. Test Conditions:  $V_D = 65 \text{ V}$ ,  $I_{DQ} = 1.5 \text{ A}$ , 100 us Pulse Width, 10% Duty Cycle.

# 0.96 - 1.215 GHz Application Circuit - Schematic

| Bias-up Procedure                                                     | Bias-down Procedure                                      |

|-----------------------------------------------------------------------|----------------------------------------------------------|

| 2. $Set V_G to -5 V$ .                                                | 3. Turn off RF signal.                                   |

| 4. Set I <sub>D</sub> current limit to 4 A.                           | 4. Turn off V <sub>D</sub>                               |

| 5. Apply 65 V V <sub>D</sub> .                                        | 5. Wait 2 seconds to allow drain capacitor to discharge. |

| 6. Slowly adjust V <sub>G</sub> until I <sub>D</sub> is set to 1.5 A. | 6. Turn off V <sub>G</sub>                               |

| 7. Apply RF.                                                          |                                                          |

# 0.96 - 1.215 GHz Application Circuit EVB2-Layout 1,2

- 1. PCB material is RO4350B 0.020" thick, 2 oz. copper each side.

- 2. The two gates could be tied together or (optionally) adjusted independently.

0.96 - 1.215 GHz Application Circuit - Bill of Material

| Reference Designator    | Value   | Qty | Manufacturer                 | Part Number         |

|-------------------------|---------|-----|------------------------------|---------------------|

| L1,L2                   | 110nH   | 2   | Coilcraft, Inc               | 0805CS-111XJBC      |

| C2                      | 0.7pF   | 1   | American Technical Ceramics  | 600S0R7FT250XT      |

| C3,C4                   | 20pF    | 2   | American Technical Ceramics  | 600S200T250T        |

| C6,C7                   | 5.6pF   | 2   | American Technical Ceramics  | 600S5R6T250T        |

| C21, C22, C27           | 6.8pF   | 3   | American Technical Ceramics  | 600S6R8FT250XT      |

| C1, C5,C8               | 8.2pF   | 3   | American Technical Ceramics  | 600S8R2FT250XT      |

| C19,C20                 | 12pF    | 2   | American Technical Ceramics  | 800B120BC500XT      |

| C23                     | 1.5pF   | 1   | American Technical Ceramics  | 800B1R5BC500XT      |

| C30                     | 1.8pF   | 1   | American Technical Ceramics  | 800B1R8BT500XT      |

| C28,C29                 | 2.4pF   | 2   | American Technical Ceramics  | 800B2R4BC500XT      |

| C12,C13,C15,C16,C17,C18 | 5.6pF   | 6   | American Technical Ceramics  | 800B5R6BC500XT      |

| C11,C14                 | 8.2pF   | 2   | American Technical Ceramics  | 800B8R2BC500XT      |

| C24,C25                 | 10uF    | 2   | TDK Singapore (Pte) Ltd      | C5750X7S2A106M230KB |

| R2,R3                   | 10 Ohms | 2   | Vishay Dale Electronics      | CRCW060310R0FKEA    |

| Connectors              | N type  | 2   | Huber+Suhner, Inc            | CRCW060310R0FKEA    |

| R1                      | 47 Ohms | 1   | Panasonic Industrial Devices | ERJ-3EKF47R0        |

| C9,C10                  | 4.7uF   | 2   | Murata Electronics           | GRM31CR71H475KA12L  |

| C31, C32                | 680uF   | 2   | Vishay Americas Inc          | MAL215099708E3      |

### Performance at 25°C of 0.96 – 1.215 GHz EVB2 1

#### Notes:

1. Test Conditions: VD = 65 V, IDQ = 1.5 A, 100 us Pulse Width, 10% Duty Cycle.

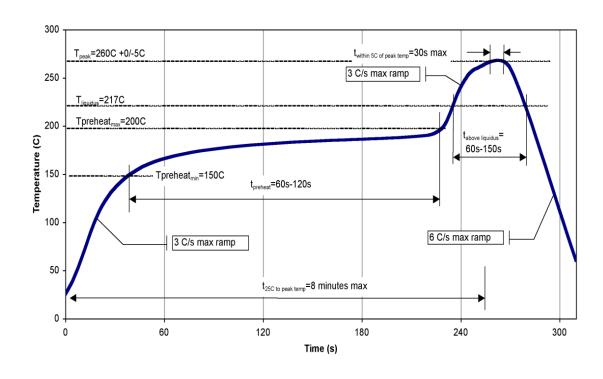

# **Recommended Solder Temperature Profile**

### **Handling Precautions**

| Parameter                        | Rating   | Standard                                    |

|----------------------------------|----------|---------------------------------------------|

| ESD – Human Body Model (HBM)     | Class 1C | JEDEC JS-001                                |

| ESD – Charged Device Model (CDM) | Class C3 | JEDEC JS-002                                |

| MSL – Moisture Sensitivity Level | MSL3     | JESD J-STD-020<br>(260°C Convection reflow) |

Caution! ESD-Sensitive Device

### **Solderability**

Compatible with both lead-free (260°C max. reflow temp.) and tin/lead (245°C max. reflow temp.) soldering processes. Solder profiles available upon request.

Contact plating: NiAu. Au thickness is 100micro-inches

### **RoHS Compliance**

This part is compliant with 2011/65/EU RoHS directive (Restrictions on the Use of Certain Hazardous Substances in Electrical and Electronic Equipment) as amended by Directive 2015/863/EU.

This product also has the following attributes:

- Halogen Free (Chlorine, Bromine)

- Antimony Free

- TBBP-A (C<sub>15</sub>H<sub>12</sub>Br<sub>4</sub>O<sub>2</sub>) Free

- PFOS Free

- SVHC Free

#### **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations, and information about Qorvo:

Web: <u>www.gorvo.com</u> Tel: +1.844.890.8163

Email: info-sales@gorvo.com

For technical questions and application information: Email: info-products@gorvo.com

# **Important Notice**

The information contained herein is believed to be reliable; however, Qorvo makes no warranties regarding the information con tained herein and assumes no responsibility or liability whatsoever for the use of the information contained herein. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for Qorvo products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anythin g described by such information. THIS INFORMATION DOES NOT CONSTITUTE A WARRANTY WITH RESPECT TO THE PRODUCTS DESCRIBED HEREIN, AND QORVO HEREBY DISCLAIMS ANY AND ALL WARRANTIES WITH RESPECT TO SUCH PRODUCTS WHETHER EXPRESS OR IMPLIED BY LAW, COURSE OF DEALING, COURSE OF PERFORMANCE, USAGE OF TRADE OR OTHERWISE. INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Without limiting the generality of the foregoing, Qorvo products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.

Copyright 2017 © Qorvo, Inc. | Qorvo is a registered trademark of Qorvo, Inc.