# High efficiency constant current LED driver for automotive applications

Datasheet - production data

#### **Features**

| Max V <sub>BATT</sub>                              | 40        | V        |

|----------------------------------------------------|-----------|----------|

| Operation supply battery voltage V <sub>BATT</sub> | 5.6 - 24  | <b>V</b> |

| Oscillator frequency range                         | 100 - 500 | kHz      |

- · Automotive qualified

- Constant current operation

- Current LED settable by external sensing resistor and adjustable via SPI

- Converter switching frequency adjustable by external resistor (R<sub>SF</sub>)

- EMC reduction by internal spread spectrum dither oscillator

- Low frequency PWM dimming operation.

- Maximum input current limiter

- Maximum switching duty cycle limiter

- Slope compensation adjustable by external resistor (R9)

- Battery overvoltage shut down protection (ext. R3, R4 resistors required)

- Led chain OV detection (ext. R5, R6)

- Multiplexed output for monitoring and control of LED temperature (external NTC resistor required), voltage of LED chain, and low frequency PWM

- SPI communication serial interface transceiver (SDI, SDO, SCK, CSN)

- Regulated output for micro supply 5 V ± 2 %

-20 mA

- Parameter programming and settings of internal memory registers by the dedicated SPI interface:

- LED current reference adjusting (± 66.7 %)

- Maximum input current limiter reference adjusting (± 55.5 %)

- Random dither frequency sweeping, modulation frequency and deviation percentage

- Power on reset pin output

- ESD protection

# **Applications**

Automotive day time running light, LED HeadLamps

# **Description**

L99LD01 is a precise constant current DC–DC converter LED driver for automotive applications, dedicated to the control of high-brightness LED headlights and housed in a LQFP32<sup>™</sup> package.

The device is designed to be used in Boost, Buck-Boost and Fly back converter topologies. An internal random dither oscillator works in low frequency modulation, allowing the RF spectrum of the switching frequency to spread so to reduce EMC emissions. The slope compensation ensures good converter loop stability whatever is the duty cycle needed by the application.

The converter is able to work either in full power mode or in low frequency dimming mode.

The device includes an internal low drop voltage regulator, that can be used to supply a microcontroller, and a reset pin, that is useful for resetting the microcontroller at the start up and every time that the regulated output voltage falls down below an established voltage threshold.

Contents L99LD01

# **Contents**

| 1 | Block                  | diagra     | m and pin description                        | . 6  |  |  |  |  |  |  |

|---|------------------------|------------|----------------------------------------------|------|--|--|--|--|--|--|

| 2 | Functional description |            |                                              |      |  |  |  |  |  |  |

|   | 2.1                    | Operation  | ng modes                                     | . 8  |  |  |  |  |  |  |

|   |                        | 2.1.1      | Operation with an external microcontroller   | 8    |  |  |  |  |  |  |

|   |                        | 2.1.2      | Stand alone operation                        | 9    |  |  |  |  |  |  |

|   |                        | 2.1.3      | Start-up fail                                | 9    |  |  |  |  |  |  |

|   |                        | 2.1.4      | Normal mode                                  | . 10 |  |  |  |  |  |  |

|   |                        | 2.1.5      | Software limp home                           | . 10 |  |  |  |  |  |  |

|   |                        | 2.1.6      | Limp home mode                               | . 10 |  |  |  |  |  |  |

|   | 2.2                    | Protecti   | ons and functions                            | 16   |  |  |  |  |  |  |

|   |                        | 2.2.1      | LED current adjust and temperature control   | . 16 |  |  |  |  |  |  |

|   |                        | 2.2.2      | Slope compensation                           | . 17 |  |  |  |  |  |  |

|   |                        | 2.2.3      | LED chain overvoltage detection              | . 18 |  |  |  |  |  |  |

|   |                        | 2.2.4      | Battery overvoltage shutdown                 | . 19 |  |  |  |  |  |  |

|   |                        | 2.2.5      | Regulators thermal shut down                 | . 19 |  |  |  |  |  |  |

|   |                        | 2.2.6      | Reset                                        | . 19 |  |  |  |  |  |  |

|   |                        | 2.2.7      | Watchdog                                     | . 20 |  |  |  |  |  |  |

|   |                        | 2.2.8      | Standby and wake up by ENABLE pin            | . 20 |  |  |  |  |  |  |

|   |                        | 2.2.9      | Frequency setting and dither effect          | . 21 |  |  |  |  |  |  |

|   |                        | 2.2.10     | Start up LED overvoltage management          | . 23 |  |  |  |  |  |  |

|   |                        | 2.2.11     | Programming the over/under voltage threshold | . 27 |  |  |  |  |  |  |

|   |                        | 2.2.12     | Input overvoltage programming                | . 29 |  |  |  |  |  |  |

| 3 | SPI fu                 | ınctiona   | al description                               | 31   |  |  |  |  |  |  |

|   | 3.1                    | Serial p   | eripheral interface (ST SPI standard)        | 31   |  |  |  |  |  |  |

|   | 3.2                    | Signal c   | lescription                                  | 32   |  |  |  |  |  |  |

|   | 3.3                    | <b>5</b> 1 |                                              |      |  |  |  |  |  |  |

|   | 0.0                    | 3.3.1      | SDI, SDO format                              |      |  |  |  |  |  |  |

|   |                        | 3.3.2      | Global status byte description               |      |  |  |  |  |  |  |

|   |                        | 3.3.3      | Operating code definition                    |      |  |  |  |  |  |  |

|   | 3.4                    |            | s mapping                                    |      |  |  |  |  |  |  |

|   |                        |            |                                              |      |  |  |  |  |  |  |

|   | 3.5                    |            | registers (RAM)                              |      |  |  |  |  |  |  |

|   | 3.6                    | Status r   | egisters                                     | 41   |  |  |  |  |  |  |

| L99LD01 | Contents |

|---------|----------|

|         |          |

| 4  | <b>Elec</b><br>4.1 | trical specifications                   |

|----|--------------------|-----------------------------------------|

| 5  | Elec               | trical characteristics46                |

| 6  | SPI                | electrical characteristics54            |

|    | 6.1                | DC characteristics 54                   |

|    | 6.2                | AC characteristics 54                   |

|    | 6.3                | Dynamic characteristics                 |

| 7  | App                | lication circuits 59                    |

| 8  | Pack               | rage information                        |

|    | 8.1                | ECOPACK <sup>®</sup> 65                 |

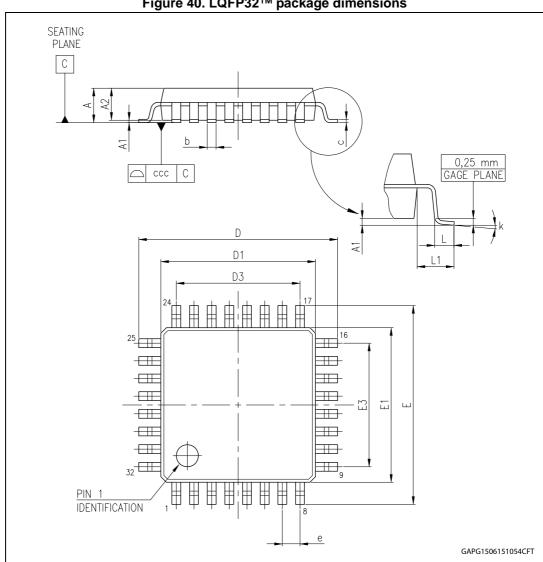

|    | 8.2                | LQFP32 <sup>™</sup> package information |

| 9  | Orde               | er codes 67                             |

| 10 | Revi               | sion history                            |

List of tables L99LD01

# List of tables

| Table 1.  | Pin description                                           |

|-----------|-----------------------------------------------------------|

| Table 2.  | Limp home mode: recovery paths                            |

| Table 3.  | Suggested K <sub>L</sub> value and overvoltage thresholds |

| Table 4.  | Command byte (8 bit)                                      |

| Table 5.  | Input data byte                                           |

| Table 6.  | Global status byte                                        |

| Table 7.  | Output data byte                                          |

| Table 8.  | Global status byte                                        |

| Table 9.  | Operation code definition                                 |

| Table 10. | RAM memory map                                            |

| Table 11. | ROM memory map                                            |

| Table 12. | Internal oscillator frequency deviation settings39        |

| Table 13. | Internal oscillator frequency modulation settings         |

| Table 14. | Watchdog timer status                                     |

| Table 15. | Absolute maximum ratings                                  |

| Table 16. | Thermal data                                              |

| Table 17. | VS and V <sub>CC1</sub> pin characteristics               |

| Table 18. | V <sub>CC2</sub> and C5V pin characteristics47            |

| Table 19. | NRES and LMODE pin characteristics                        |

| Table 20. | G1 driver 1 pin characteristics                           |

| Table 21. | G2 pin characteristics (driver2)48                        |

| Table 22. | Converter oscillator and RSF pin characteristics          |

| Table 23. | PWM_L, PWM, MOUT pin characteristics                      |

| Table 24. | ISENSE+, ISENSE- pin, and O.T.A. characteristics          |

| Table 25. | SC pin characteristics                                    |

| Table 26. | VLED pin characteristics                                  |

| Table 27. | INP_OV pin characteristics (input overvoltage shut down)  |

| Table 28. | NTC pin characteristics52                                 |

| Table 29. | ENABLE, LHM pin characteristics                           |

| Table 30. | Power on reset                                            |

| Table 31. | Watchdog and timers parameters53                          |

| Table 32. | SPI DC characteristics                                    |

| Table 33. | SPI AC characteristics                                    |

| Table 34. | SPI dynamic characteristics                               |

| Table 35. | LQFP32™ mechanical data                                   |

| Table 36. | Device summary                                            |

| Table 37. | Document revision history                                 |

L99LD01 List of figures

# List of figures

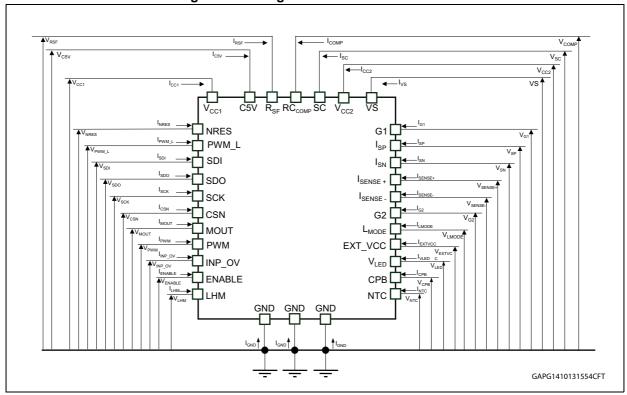

| Figure 1.  | Block diagram                                                                                                   |

|------------|-----------------------------------------------------------------------------------------------------------------|

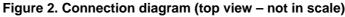

| Figure 2.  | Connection diagram (top view – not in scale)                                                                    |

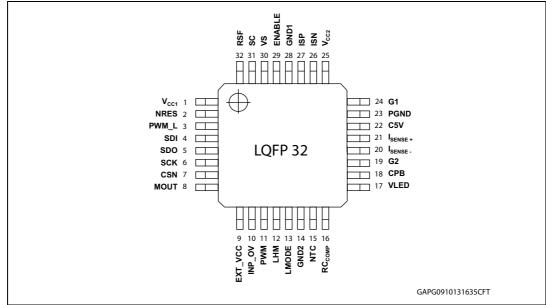

| Figure 3.  | Operating modes, main states                                                                                    |

| Figure 4.  | Normal start up vs V <sub>S</sub> ramp up and V <sub>CC1</sub> voltage dips                                     |

| Figure 5.  | V <sub>CC1 FAIL</sub> or V <sub>CC1</sub> reset under voltage (V <sub>S</sub> > V <sub>SMIN</sub> ) at start up |

| Figure 6.  | $V_{CC1}$ reset under voltage at start up ( $V_S < V_{SMIN}$ ) and fast $V_S$ ramp down                         |

| Figure 7.  | Slow vs ramp down                                                                                               |

| Figure 8.  | Internal structure of the slope compensation circuit                                                            |

| Figure 9.  | Operation with a standalone LIN and ENABLE                                                                      |

| Figure 10. | Operation with PM device and ENABLE (FSO active Low)                                                            |

| Figure 11. | Internal structure of main converter oscillator22                                                               |

| Figure 12. | Converter frequency range vs R <sub>SF</sub> and I <sub>RSF</sub> vs frequency                                  |

| Figure 13. | Correct start UP with no LED overvoltage failure                                                                |

| Figure 14. | LED overvoltage after t <sub>DStart</sub>                                                                       |

| Figure 15. | Device behavior in case the low to high transition of PWM_L signal happens after t <sub>DStart</sub>            |

| J          | expiration                                                                                                      |

| Figure 16. | LED overvoltage event not caused by a VS overvoltage event                                                      |

| Figure 17. | LED overvoltage detection due to a possible battery VS overvoltage                                              |

| Figure 18. | Behavior of LED overvoltage recovery bit with low on-time of PWM_L                                              |

| Figure 19. | LED chain overvoltage thresholds settings. An example for boost and fly back converters28                       |

| Figure 20. | Input overvoltage programming                                                                                   |

| Figure 21. | Clock polarity and clock phase                                                                                  |

| Figure 22. | SPI global error information output                                                                             |

| Figure 23. | SPI write operation                                                                                             |

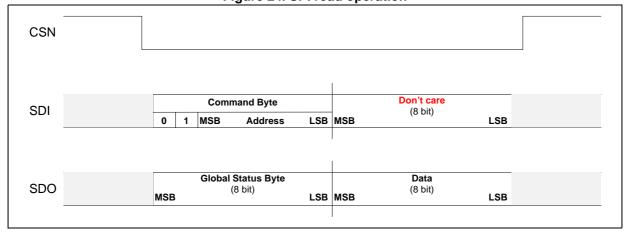

| Figure 24. | SPI read operation                                                                                              |

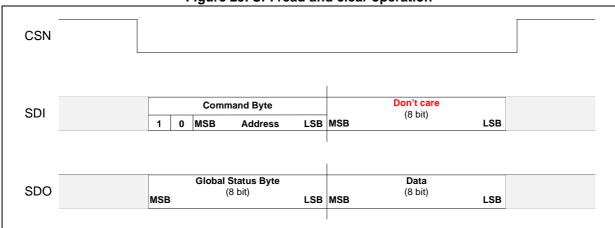

| Figure 25. | SPI read and clear operation                                                                                    |

| Figure 26. | SPI read device information                                                                                     |

| Figure 27. | Principle of the WD_Status bits                                                                                 |

| Figure 28. | Voltage and current conventions                                                                                 |

| Figure 29. | SPI timing parameters                                                                                           |

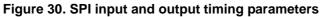

| Figure 30. | SPI input and output timing parameters                                                                          |

| Figure 31. | SPI maximum clock frequency                                                                                     |

| Figure 32. | NRES pin open drain structure                                                                                   |

| Figure 33. | Handshake procedure at start up with microcontroller on board                                                   |

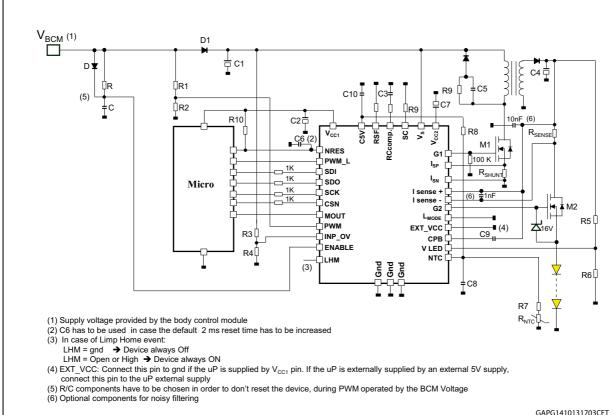

| Figure 34. | Boost application circuit                                                                                       |

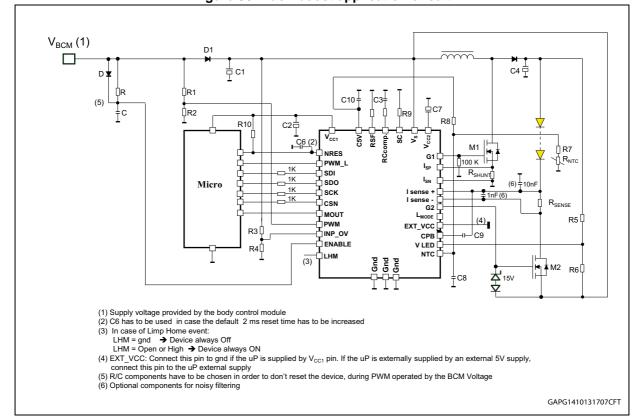

| Figure 35. | Fly back application circuit                                                                                    |

| Figure 36. | Buck-boost application circuit                                                                                  |

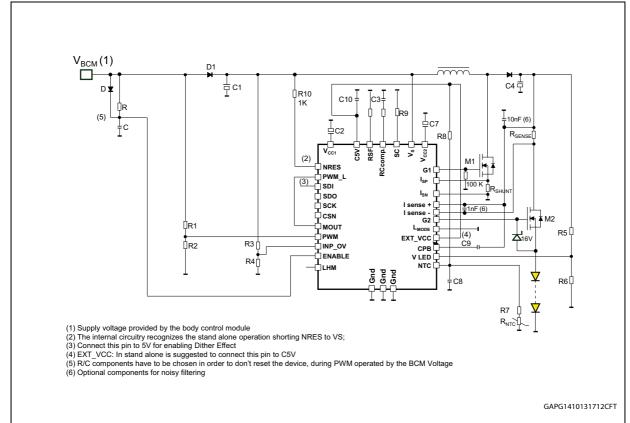

| Figure 37. | Stand alone application example for boost topology                                                              |

| Figure 38. | Reverse battery protection: an example for boost topology                                                       |

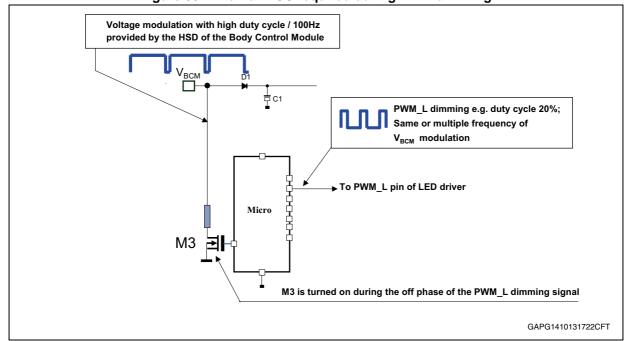

| Figure 39. | External MOS required during PWM dimming64                                                                      |

| Figure 40. | LQFP32™ package dimensions                                                                                      |

#### Block diagram and pin description 1

$V_{CC2}$  $V_{\text{CC1}}$ VS SC Voltage Regulator 2 & Band gap Ref Voltage Regulator 1 Main Oscillato DRIVER1 **☆** G1 FF **Duty Max** OSC\_RAME PWM\_L 📮 C\_Disch SLOPE AD. LH\_ON Randomic Dither ☐ I<sub>SN</sub> NRES [ State Machine For Parameter Settings, Diagnostic & WD V V<sub>LREF</sub> Batt\_OV LED\_OC SDI I<sub>SENSE +</sub> STOP\_CONV / LH\_OFF LED\_OC I<sub>SENSE</sub> -SDO [ MAX INP CURRENT Charge Pump SCK [ 🗅 СРВ LED Current Adjust & NTC Control  $V_{NTC\_TH}$ PWM\_ **□** G2 CSN [ EN\_NTC DRIVER2

□ EXT\_VCC LHM 🗀 V<sub>LED</sub> LED Over INP\_OV 📮 OV Voltage ₽₽ILMODE -EXT\_VCC Detection □ LMODE MOUT 🗀 Analog MUX ☐ NTC PWM [ ₽ĮI<sub>NTC</sub> ☐ GND GND GND ENABLE 📮 Batt\_OV GAPG0910131649CFT

Figure 1. Block diagram

Table 1. Pin description

| Pin<br>number | Pin name             | Function                                                                                                                 |

|---------------|----------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1             | V <sub>CC1</sub>     | 5 V internal voltage regulator 1 output (external capacitor req.)                                                        |

| 2             | NRES                 | Reset I/O pin; active low                                                                                                |

| 3             | PWM_L                | Logic low frequency PWM input                                                                                            |

| 4             | SDI                  | Serial SPI data input                                                                                                    |

| 5             | SDO                  | Serial SPI data output                                                                                                   |

| 6             | SCK                  | SPI clock                                                                                                                |

| 7             | CSN                  | Chip select not                                                                                                          |

| 8             | MOUT                 | Multiplexed data output pin                                                                                              |

| 9             | EXT_VCC              | Internal/external up supply voltage programming pin <sup>(1)</sup>                                                       |

| 10            | INP_OV               | Battery overvoltage programming pin                                                                                      |

| 11            | PWM                  | Low frequency PWM input (battery compatible)                                                                             |

| 12            | LHM                  | Limp home mode input pin                                                                                                 |

| 13            | LMODE                | Switch input pin (connect to GND if LED drop voltage is referred to GND or open (5 V) if LED drop is referred to $V_S$ ) |

| 14            | GND2                 | GND of controller                                                                                                        |

| 15            | NTC                  | Output for external N.T.C. resistor                                                                                      |

| 16            | RC <sub>COMP</sub>   | External R C compensation network                                                                                        |

| 17            | VLED                 | Input for LED chain overvoltage detection                                                                                |

| 18            | СРВ                  | Charge pump buffer capacitor                                                                                             |

| 19            | G2                   | Gate 2 output for external PMOS M2                                                                                       |

| 20            | I <sub>SENSE</sub> - | Negative terminal of the LED sense resistor                                                                              |

| 21            | I <sub>SENSE+</sub>  | Positive terminal of the LED sense resistor                                                                              |

| 22            | C5V                  | Output for 5 V buffer capacitor                                                                                          |

| 23            | PGND                 | Power ground                                                                                                             |

| 24            | G1                   | Gate 1 output for external PMOS M1                                                                                       |

| 25            | V <sub>CC2</sub>     | 10 V voltage regulator 2 output (ext. capacitor required)                                                                |

| 26            | ISN                  | Negative terminal of the shunt resistor                                                                                  |

| 27            | ISP                  | Positive terminal of the shunt resistor                                                                                  |

| 28            | GND1                 | GND of controller                                                                                                        |

| 29            | ENABLE               | Enable pin                                                                                                               |

| 30            | VS                   | Supply voltage input pin                                                                                                 |

| 31            | SC                   | Slope compensation setting resistor                                                                                      |

| 32            | RSF                  | Oscillator frequency setting resistor                                                                                    |

<sup>1.</sup> In case of externally supplied microcontroller, attach this pin to its external supply voltage pin.

# 2 Functional description

# 2.1 Operating modes

The device is able to work both with a microcontroller and without it (stand alone configuration).

## 2.1.1 Operation with an external microcontroller

This way allows parameters to be adjusted and checked by means of the SPI interface.

The adjusted device parameters, stored, i.e., inside the micro EEPROM, can be loaded into device internal registers after the start up phase.

By means of a small 8 pins microcontroller it is possible to implement the following functions:

- Parameters setting:

- LED current level and maximum input current limit can be adjusted according to the application, the LED characteristic and spreads

- Dither oscillator parameters as random, frequency modulation and deviation percentage can be programmed

- Flexible PWM operation with duty cycle and frequency managed by the microcontroller

- Diagnostic feedback:

- Fault condition is sent to the micro when the CSN pin is pulled down

- Advanced LED monitoring:

- LED voltage drop and temperature are multiplexed and sent to the microcontroller through the dedicated MOUT pin in order to monitor the selected parameter with the A/D of the microcontroller. The multiplexer is driven through a SPI command. This function allows a sophisticated control of the LED status. For example, as an alternative to the default overvoltage detection, it is possible to monitor the LED drop voltage, reduced by the external R5/R6 resistor divider. So taking into account the spread and temperature influence on the LED voltage drop, the microcontroller is able to detect if there is one or more LED shorted. Furthermore, it is possible to monitor the LED chain temperature, by means of the voltage feedback through the dedicated NTC pin. The temperature limit control, operated by the device by default, can be disabled via the SPI and the voltage applied on the NTC pin can be sent back to the microcontroller via the multiplexed output, MOUT, so allowing the microcontroller itself to control the LED chain either acting on the internal current LED register or reducing the low frequency PWM duty cycle.

- In case of V<sub>R1</sub> over temperature, its output will be switched off, the device enters in limp home mode and a failsafe bit will be set in the internal status register (see details in the following paragraph). In order to restart the normal operation, so clearing the corresponding status register bit, the V<sub>S</sub> or ENABLE voltage has to be switched off and then on. The mentioned bit can be cleared by the microcontroller only when it is external supplied.

#### 2.1.2 Stand alone operation

The device operates with default parameters. The overall tolerance depends on the internal references precision and the external resistors tolerance. In details:

LED current via external sensing resistor:

$$I_{LED} = 150 \text{ mV/R}_{SENSE}$$

- Maximum input current via an external shunt resistor.

- Oscillator dither effects are set to its default parameters; a low level on the SDI allows disabling the function.

- Low frequency dimming operation is allowed either by PWM pin or by logic level PWM\_L input pin. Connecting the PWM control pin to the supply voltage via a resistor divider, allows the converter to be synchronized to the low frequency PWM generated, i.e., from the smart junction box.

- Connecting the MOUT pin, which by default provides a logic level image of the control

input, to the PWM\_L input, it is possible to drive the LED according to the PWM

frequency and duty cycle of control. (See application circuit of Figure 38).

- In case of V<sub>R1</sub> over temperature, its output will be permanently switched off. The device still continues to work in normal mode but with V<sub>R1</sub> = OFF.

The L99LD01 can operate in 4 different modes:

- Start-up fail

- Normal mode

- Software limp home

- Limp home

After the power on reset, the device stays in start-up phase until  $V_{CC1}$  reaches a specified threshold,  $V_{CC1\_TH}$ . Then the device enters in normal mode either with microcontroller or standalone, depending on the voltage level on the  $N_{reset}$  pin.

Note:

The information about the operation with microcontroller or standalone is latched until a new power on reset.

If  $V_{CC1}$  does not reach both  $V_{CC1}$  fail and  $V_{CC1\_TH}$  thresholds within a given delay or if a  $V_{CC1}$  over temperature event occurs, the device enters in a corresponding state.

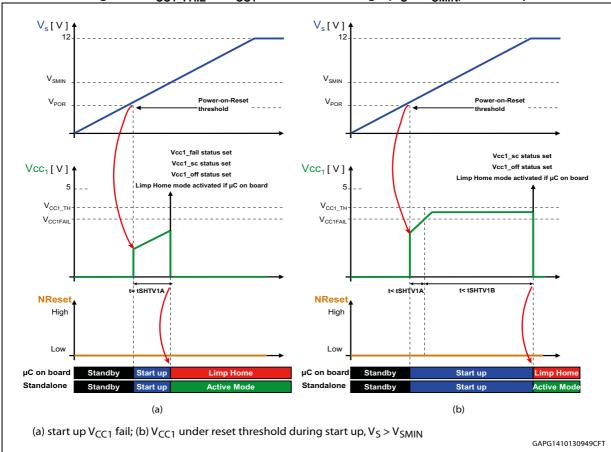

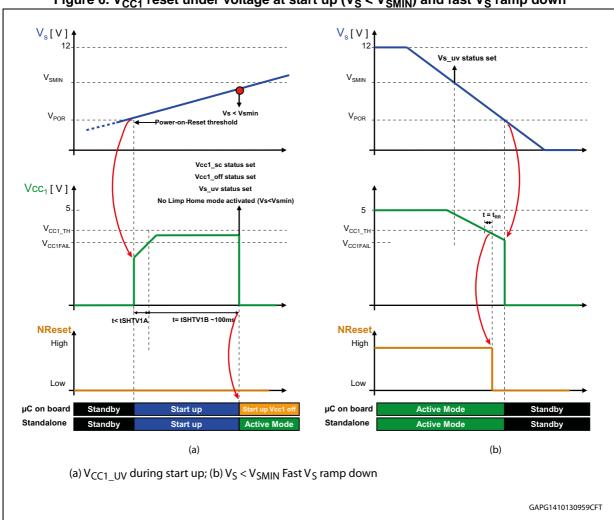

#### 2.1.3 Start-up fail

The device enters this mode in case a  $V_{CC1}$  under voltage event occurs during start-up phase and  $V_S < V_{SMIN}$ , provided that a microcontroller is detected. In this case  $V_{CC1}$  is turned off.

If V<sub>S</sub> remains below V<sub>SMIN</sub>, then the converter is switched off.

If V<sub>S</sub> rises above V<sub>SMIN</sub>, the converter behaves according to the PWM\_L pin.

#### 2.1.4 Normal mode

- Normal mode with microcontroller: the device enters this mode after a successful start up (V<sub>CC1</sub> > V<sub>CC1\_TH</sub>) and a microcontroller is detected. The device keeps this mode as long as the watchdog is retriggered before a timeout event.

- Normal mode in standalone configuration: the device enters this mode if a standalone configuration is detected, independently from V<sub>CC1</sub> errors. The L99LD01 keeps this mode even in case of watchdog timeouts.

In both cases, the converter behaves according to the PWM\_L pin.

#### 2.1.5 Software limp home

This device enters software limp home mode in case the Lh\_Sw bit is set (see Section : Control registers 3).

The control registers are set to their default values, with the exception of the Lh\_Sw bit, which remains unchanged.

The converter behaves according to the signal on the LHM pin:

- Turned on if a high signal is detected at the LHM pin

- Turned off if a low signal is detected at the LHM pin

#### 2.1.6 Limp home mode

The device enters limp home mode, if a microcontroller is detected, in the following cases:

- Watchdog timeout in normal mode

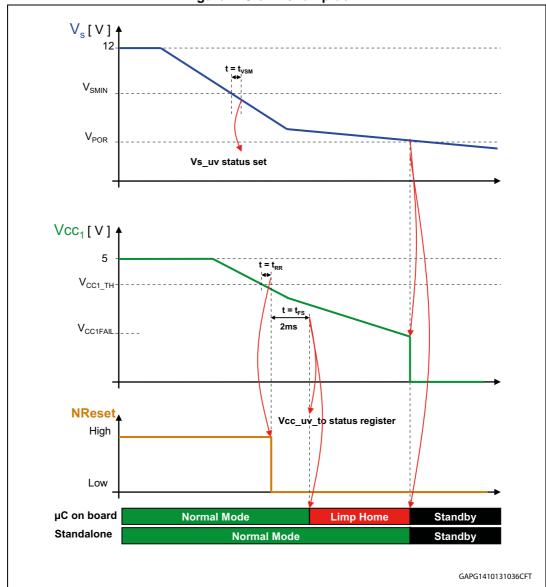

- V<sub>CC1</sub> under voltage (V<sub>CC1</sub> < V<sub>CC1</sub> TH) for more than 2 ms in normal mode

- V<sub>CC1</sub> is below the V<sub>CC1</sub> FAIL threshold for more than 4 ms during start-up

- $V_{CC1}$  is below Vcc1uv for more than 100 ms during start-up and  $V_S$  is above  $V_{SMIN}$  threshold

- Thermal shutdown of V<sub>CC1</sub>

- SDI stuck at 0 or 1

In Limp Home mode, all the control registers are set to their default values, except Lh\_Sw (see Section: Control registers 3), which remains unchanged.

The converter behaves according to the voltage level on the LHM pin:

- Turned on if a High signal is detected at the LHM pin

- Turned off if a Low signal is detected at the LHM pin

Depending on the root cause, the action taken to quit the limp home mode (provided that the limp home condition has disappeared) is different. Some of the recovery paths require the microcontroller to be supplied by external supply.

A power on reset is always possible.

Figure 3. Operating modes, main states

Table 2. Limp home mode: recovery paths

| Transition                                     | Root cause                                                    | Action to get back to normal mode        | Response in the next SPI command        |

|------------------------------------------------|---------------------------------------------------------------|------------------------------------------|-----------------------------------------|

|                                                | WD timeout<br>(1 <sup>st</sup> or 2 <sup>nd</sup> WD timeout) |                                          | Fail Safe bit = 0<br>WD_Fail bit = 0    |

| Normal mode →<br>Limp Home V <sub>CC1</sub> on | V <sub>CC1</sub> < V <sub>CC1_TH</sub> for more than 2 ms     | Read and clear status1<br>AND WD trigger | Fail Safe bit = 0<br>Vcc1_Uv_To bit = 0 |

|                                                | SDI stuck at 0 or 1                                           |                                          | Fail Safe bit = 0<br>SDI_Stuck@ = 0     |

Table 2. Limp home mode: recovery paths (continued)

| Transition                                                              | Root cause                                                                                                                                               | Action to get back to normal mode                                 | Response in the next SPI command                      |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------|

| Limp home V <sub>CC1</sub> on →                                         | 3 consecutive WD timeouts (microcontroller is supplied by V <sub>CC1</sub> )                                                                             | Power on reset OR toggling of EN pin                              | Fail Safe bit = 0<br>WD_Fail bit = 0<br>Reset bit = 1 |

| limp home V <sub>CC1</sub> off                                          | 3 consecutive WD timeouts (microcontroller is supplied by another V <sub>REG</sub> )                                                                     | Read and clear Status1<br>AND WD trigger                          | Fail Safe bit = 0<br>WD_Fail bit = 0                  |

|                                                                         | V <sub>CC1</sub> < V <sub>CC1_FAIL</sub> during start up for more than 4 ms                                                                              | Power on reset                                                    | Failsafe bit = 0<br>Vcc1_Sc bit = 0<br>Reset bit = 1  |

| Start up →limp home                                                     | V <sub>CC1</sub> < V <sub>CC1_FAIL</sub> during start up<br>for more than 4 ms<br>(microcontroller supplied by<br>another V <sub>REG</sub> )             | Read and clear Status1<br>AND WD trigger OR<br>Toggling of EN pin | Failsafe bit = 0<br>Vcc1_Sc bit = 0<br>Vcc1_Fail = 0  |

| V <sub>CC1</sub> off                                                    | $V_{CC1} < V_{CC1\_TH}$ for more than 100 ms during start up AND $V_S > V_{SMIN}$                                                                        | Power on reset OR toggling of EN pin                              | Fail Safe bit = 0<br>Vcc1_Sc bit = 0<br>Reset bit = 1 |

|                                                                         | $V_{\rm CC1} < V_{\rm CC1\_TH}$ for more than 100 ms during start up AND $V_{\rm S} > V_{\rm SMIN}$ (microcontroller supplied by another $V_{\rm REG}$ ) | Read and clear Status1<br>AND WD trigger                          | Fail Safe bit = 0<br>Vcc1_Sc bit = 0                  |

| Any state except normal mode standalone→ limp home V <sub>CC1</sub> off |                                                                                                                                                          | Read and clear Status1<br>AND WD trigger                          | Fail Safe bit = 0<br>Vcc1_Ot bit = 0                  |

| Normal mode → SW limp home                                              | Software limp home is activated                                                                                                                          | Reset Lh_Sw bit AND<br>WD trigger                                 | Fail Safe bit = 0<br>Lh_Sw_St = 0                     |

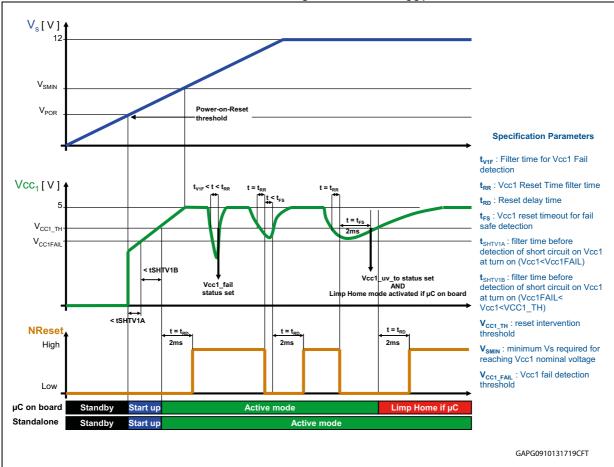

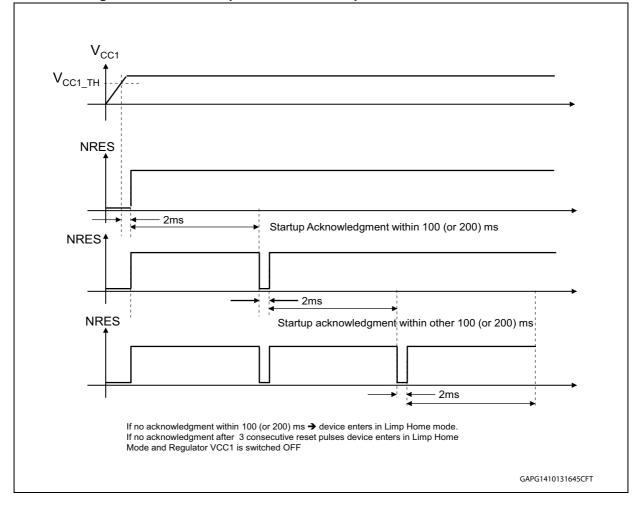

The following Figure 4, Figure 5 (a), (b) and Figure 6 (a) show the behavior of the device and NRES during start-up in case of normal  $V_S$  ramp up or in case of  $V_{CC1}$  failures ( $V_{CC1}$  fail or reset under voltage), both with microcontroller and standalone. Figure 6 (b) and Figure 7 show the behavior at  $V_S$  ramp down fast and slow respectively.

Figure 4. Normal start up vs  $V_S$  ramp up and  $V_{CC1}$  voltage dips

Note: Normal start up with or without microcontroller.

Figure 5.  $V_{CC1\_FAIL}$  or  $V_{CC1}$  reset under voltage ( $V_S > V_{SMIN}$ ) at start up

Figure 6.  $V_{CC1}$  reset under voltage at start up ( $V_S < V_{SMIN}$ ) and fast  $V_S$  ramp down

Figure 7. Slow vs ramp down

#### 2.2 Protections and functions

# 2.2.1 LED current adjust and temperature control

The LED current can be adjusted within a range of  $\pm$  66.7 %, with respect to the default value set by the LED current sense resistor, via the SPI input, so allowing the end of line calibration. The LED chain temperature measurement is achieved by means of an external NTC resistor connected between the NTC pin and GND. The NTC resistor is supplied through a resistor connected to the 5 V internal regulator output. As soon as the voltage on the NTC resistor becomes lower than the internal threshold,  $V_{NTC\_TH}$ , (due to an overtemperature in the LED chain) an internal circuitry is activated and the internal LED current reference voltage decreases proportionally, so that the LED current is progressively

DocID025319 Rev 3

reduced (maximum 50 % of the nominal LED current), not allowing the LED temperature to increase over the programmed limit.

Thermal limit intervention is reported by properly setting a bit inside the internal status register.

#### 2.2.2 Slope compensation

Slope compensation is needed to ensure the stability of the control loop with all possible values of duty cycle

$$D = \frac{T_{ON}}{T}$$

(0 < D < 1)

especially for duty cycle greater than 0.5. The recommended slope  $S_{ADD}$  of the additional ramp is proportional to the inductor current slope during the turn off phase, that is:

$$S_{ADD} = \alpha \cdot S_{I}$$

where S<sub>ADD</sub> is the additional slope introduced by the circuit,

$$S_L = \frac{dI_L}{dt}\Big|_{OFF}$$

is the off-time inductor slope and

$$0.5 < \alpha < 1$$

S<sub>L</sub> is also given by the formula:

$$S_{L} = \frac{G_{LA} \cdot R_{SHUNT} \cdot (V_{OUT} - V_{IN})}{L}$$

Being  $G_{LA}$  the gain of the linear amplifier (see *Chapter 5: Electrical characteristics* for  $G_{LA}$  parameter values) and  $R_{SHUNT}$  is the resistor across pin  $I_{SP}$  and  $I_{SN}$  (see *Chapter 7: Application circuits*).

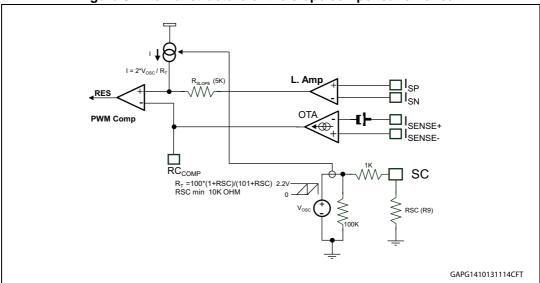

The simplified internal circuit structure for the slope compensation is shown in Figure 8.

The additional slope is obtained from the internal oscillator ramp voltage. A fraction of the oscillator voltage ramp is added to the output voltage of the sensing amplifier, which is proportional to the sense resistor voltage drop, and therefore, to the current flowing through power mosfet M1.

The added ramp voltage is

$$V_{ADD} = I \cdot R_{SLOPE}$$

where

$$I = 2 \cdot \frac{V_{OSC}}{R_{T}}$$

and R<sub>SLOPE</sub> and R<sub>T</sub> are defined in the *Figure 8*, together with their typical values.

Therefore, will result:

$$V_{ADD} = 2 \cdot V_{OSC} \cdot \frac{R_{SLOPE}}{R_{T}}$$

and consequently:

$$S_{ADD} = \frac{V_{ADD}}{T} = \frac{2 \cdot V_{OSC} \cdot R_{SLOPE}}{R_{T} \cdot T}$$

where T is the period of the converter oscillator.

The additional compensating current slope can be simply adjusted by properly setting the value of the external resistor R9 (and consequently  $R_T$ ).

Figure 8. Internal structure of the slope compensation circuit

#### 2.2.3 LED chain overvoltage detection

Via the external resistor divider (R5, R6) it is possible to detect LED overvoltage events, by programming a threshold for the maximum drop voltage of the LED chain for a specific LED board (see Section 2.2.12 for details). In case Boost or Fly back topology is used, the L<sub>MODE</sub> pin must be connected to GND. In this case the voltage at pin V<sub>LED</sub> will be referred to ground. Instead, if Buck Boost topology is used, the L<sub>MODE</sub> pin must be connected to 5 V or left open. An internal pull up current source keep this pin high, and in this case, the voltage applied by the resistor divider R5/R6 at pin V<sub>LED</sub> will be referred to the battery voltage applied at pin V<sub>S</sub>. If a valid overvoltage event occurs, which is detected if the LED drop voltage reaches a value V<sub>LED</sub>  $\geq$  OV\_TH1, the device is switched off immediately forcing the

pins G1 and G2 to zero voltage and the event is registered in the status register of the SPI interface and read by the micro.

In case of LED overvoltage, immediately after stopping the device, an internal resistor is applied between pin I<sub>SENSE+</sub> and GND trough the switch "C\_disch" (see *Figure 1*), in order to discharge capacitors C1 and C4, avoiding LED flashing when the converter restarts. Any LED\_OV event will be written in the GSB (Global Status Byte) bit 7 and also in the SR1 (Status Register 1) bit 18.

## 2.2.4 Battery overvoltage shutdown

In case supply voltage applied to the  $V_S$  pin rises above a maximum voltage threshold, sensed by a resistor divider attached at pin INP\_OV, the converter is switched off immediately, forcing outputs pin G1 and G2, to zero voltage. This prevents a LED over current in case of load-dump.

If, following the input overvoltage event, the battery voltage decreases under a second threshold, lower than the former, the converter starts again.

#### 2.2.5 Regulators thermal shut down

Both voltage regulators inside the chip are provided with over temperature detection circuits.

If  $V_{R1}$  reaches its maximum temperature,  $V_{R1}$  will be switched off. After that, the behavior of the device depends on the application (see Section 2.2.1: LED current adjust and temperature control).

If instead, is  $V_{R2}$  to reach its maximum temperature (typ 175 °C), then the device will be completely switched off ( $V_{CC1}$  and  $V_{CC2} = 0$ ).

Only the internal temperature monitoring of  $V_{CC2}$  remains alive and when the temperature falls down under a second lower temperature threshold (150 °C typ.), the device tries to restart again.

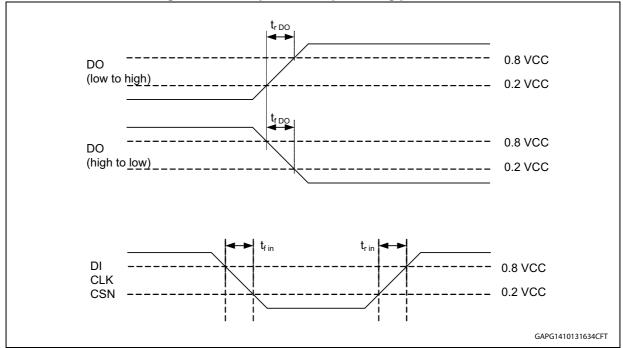

#### 2.2.6 Reset

The NRES pin (active low), generates a reset signal for the microcontroller.

An external pull up resistor (typ. 100 k) maintain normally high the voltage at pin NRES (see *Figure 32*).

Following a power up condition, the NRES pin is forced low while the voltage provided by regulator 1 ( $V_{CC1}$ ) is below an internal fixed threshold  $V_{CC1\_TH}$  of typ 4.5 V. After  $V_{CC1}$  has reached the above mentioned internal threshold, NRES voltage is kept low for a fixed default time of 2 ms; after that, the NRES pin will be released reaching the normal high state. However, this time can be externally extended by an additional capacitance connected between NRES and GND (see C6 in the application circuits), which is charged by the external pull-up. Depending on the reset-input-threshold of the  $\mu P$  ( $U_{TR}$ ), the required capacitance for a typical  $T_{RD}$  can be calculated as follows:

$$C6 = -T_{RD}/(R_{PU} \cdot lg(1 - U_{TR}/V_{CC1}))$$

R<sub>PIJ</sub> is the pull up resistor (value in ohm)

In case  $V_{CC1}$  voltage drops below the internal threshold during the normal functioning, or when the device is put in standby, the NRES pin is forced to low, but after a time interval  $T_{RR}$  has expired and kept low until the  $V_{CC1}$  has gone back again to the internal threshold (see *Figure 4* for more details).

#### 2.2.7 Watchdog

In case the application uses a microcontroller, during the device power-up a reset pulse is generated periodically every 200 ms (default) for 2.0 ms waiting for microcontroller acknowledgment. Timeout window is selectable by SPI (100 ms or 200 ms) and the reset time could be extended by the external capacitor C6.

- Timeout WD is refreshed by bit toggling.

- After the 1<sup>st</sup> WD timeout, a reset pulse is generated and the device enters in Limp Home mode. After the second WD timeout, another reset pulse cycle is generated, waiting for microcontroller response.

- After 3 consecutive reset cycles without WD refresh, which means that microcontroller is not responding, the voltage regulator, V<sub>CC1</sub>, is turned off and the device keeps working in "Limp Home Mode" (see *Figure 33*). Safety critical functions like Low Beam application require the LED Driver to be turned on if the microcontroller fails, while in case of high beam application, it is required the driver to be switched off in case of microcontroller failure. As a consequence, the device operates according to the state of LHM pin which is enabled during the recognition of the microcontroller failure. In particular, if LHM pin is kept low the device will be always OFF. If instead, LHM pin is high or left open, the device will be switched permanently ON, regardless of the status of PWM\_L pin.If the application doesn't use a microcontroller (stand alone operation), the start-up WD control must to be deactivated. This can be done by connecting NRES pin to the battery supply voltage V<sub>S</sub>. In such a case the driver will operate in normal mode as above mentioned (see stand alone operation).

#### 2.2.8 Standby and wake up by ENABLE pin

A low consumption mode is required in case of applications directly connected to the battery.

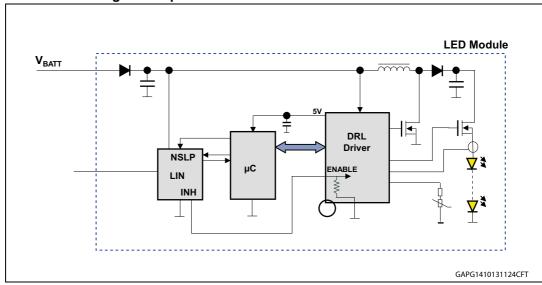

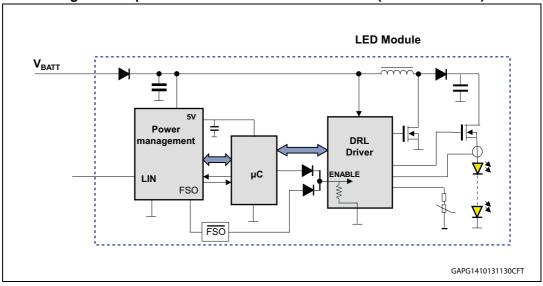

The device enters in standby mode, that is the default operating modes because of an internal pull down, in case of low level signal at the ENABLE pin and it wakes up in case of high level signal. During standby mode,  $V_{CC1}$  and  $V_{CC2}$  are switched off. *Figure 9* and *Figure 10* show two possible application schematics in case of direct connection to the battery.

In case of *Figure 9* the microcontroller of the application goes in standby when the microcontroller sets the LIN transceiver in standby mode: NSLP = Low→INH goes Low→the DRL driver goes in standby.

The application is waken up from the standby when a wake up source is detected by the LIN transceiver. That means INH goes high and so ENABLE, then the DRL driver restarts and consequently V<sub>CC1</sub> is activated and supplies the microcontroller.

In case of *Figure 10*, a power management device is present, which supplies the microcontroller. Normally the inverted FSO signal coming from the power management device is high. This output is inverted by an external logic and applied to one of the two input OR diodes and therefore, at the input of the OR the voltage is normally at logical zero.

So in this case the LED driver goes:

- In stand-by mode with a low level on ENABLE pin operated by the microcontroller

- In normal mode with a high level on ENABLE pin operated by the microcontroller

The inverted FSO signal, coming from the power management device ensures, putting trough the inverter and the external OR diode ENABLE pin high, that the LED driver correctly restarts even if the microcontroller fails.

Figure 9. Operation with a standalone LIN and ENABLE

1. An inverter network is required.

# 2.2.9 Frequency setting and dither effect

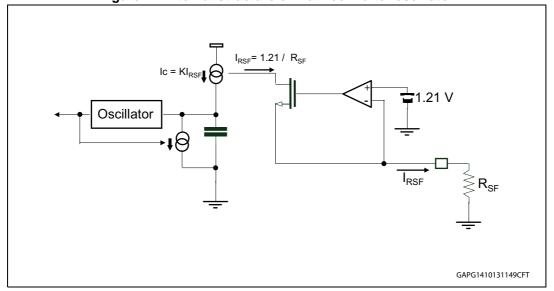

The internal main converter oscillator structure is reported in *Figure 11*.

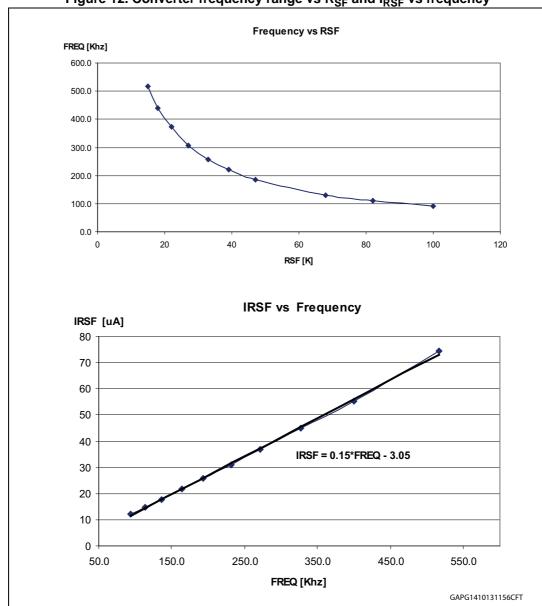

The external resistor applied between pin  $R_{SF}$  and ground is setting the converter working frequency. The voltage applied on pin  $R_{SF}$  is the internal reference reported by the source follower structure which is a constant voltage of 1.21 V. The converter frequency is directly related to the current flowing through the  $R_{SF}$  pin. *Figure 12* reports the behavior of frequency converter as function of the external resistor  $R_{SF}$  and  $I_{RSF}$  as function of converter frequency. As above mentioned the converter oscillator spread parameters (dither effect) are adjustable via SPI.

Dither effect is disabled by default during standalone operation, but it is possible enabling it simply connecting the SDI pin to 5 V voltage.

Figure 11. Internal structure of main converter oscillator

Figure 12. Converter frequency range vs R<sub>SF</sub> and I<sub>RSF</sub> vs frequency

#### 2.2.10 Start up LED overvoltage management

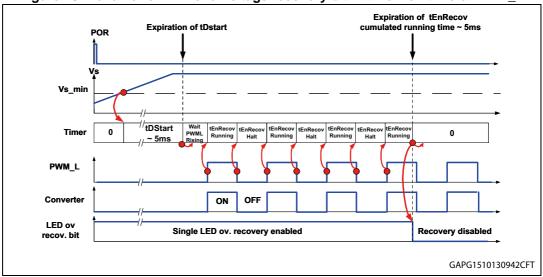

The following diagram shows the purpose of delay time windows "t<sub>DStart</sub>" and "t<sub>EnRecov</sub>".

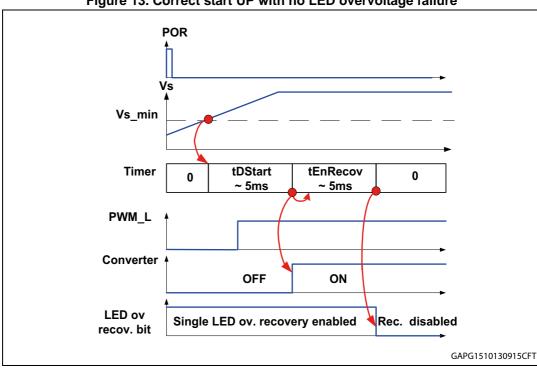

The first delay window  $t_{DStart}$  has been thought to ensure an initial time period for charging the external buffer capacitor of the charge pump C9. When  $V_S$  is below  $V_{SMIN}$ , the LED overvoltage recovery bit is set. During this time interval, triggered as soon as the battery voltage  $V_S$  overcomes  $V_{SMIN}$  threshold, the converter remain in a stop condition, independently from PWM\_L. When the  $t_{DStart}$  is elapsed (typ. 5 ms), the converter is released and behaves according to the PWM\_L signal provided, that no failure occurs.

If no LED overvoltage comes during the  $2^{nd}$  time interval  $t_{EnRecov}$ , LED ov recovery bit is reset.

If a LED overvoltage failure occurs afterwards, the failure will be latched and the converter is stopped until a read and clear of the status register 1.

Note that during t<sub>DStart</sub>, the converter is stopped to enable the buffer capacitor C9 to charge at a sufficient voltage to correctly drive the mosfet M2. This delay prevents the converter to turn on, while M2 stays off, avoiding a LED overvoltage event.

If the application uses a big capacitor<sup>(a)</sup>, it is recommended to keep the PWM\_L signal low after a power on reset or after a  $V_S$  under voltage, until C9 is totally charged, to avoid a LED overvoltage. *Figure 13* shows the device behavior in case of no LED overvoltage failure, after  $t_{DStart}$ .

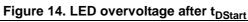

If C9, after t<sub>DStart</sub> time, should be not enough charged to allow correct driving operation, a possible LED overvoltage will appear when, the converter will be released. *Figure 14* shows what happens in this case.

After  $t_{DStart}$ , the converter is released while the C9 capacitor is only partially charged. Consequently,  $V_{LED}$  increases up to LED OV\_TH1 and a LED overvoltage event is detected during the  $t_{EnRecov}$  phase. The LED\_Ov\_Rec bit is not reset at the end of the  $t_{EnRecov}$  phase due to the LED overvoltage event. The discharge path is activated until  $V_{LED}$  crosses LED OV\_TH2. Then, the LED\_Ov\_Rec bit is reset, the converter is released, and the buffer capacitor C9 is now fully charged, enabling the dimming mosfet M2 to turn on.

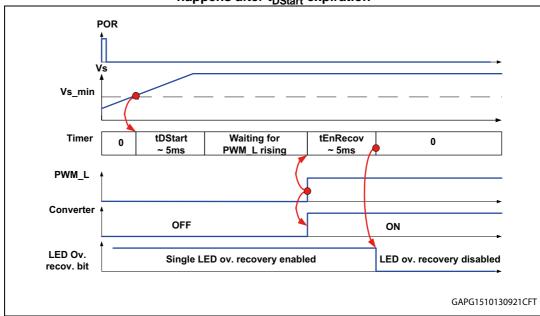

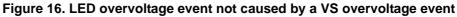

Figure 15 shows the case of LED\_Ov\_Rec bit during a start up with a rising edge on PWM\_L = High after the expiration of t<sub>DStart</sub>. In this case, the t<sub>EnRecov</sub> phase starts only when the PWM\_L signal goes High. Figure 16 shows the case of LED overvoltage event, which could appear during normal functioning.

The LED overvoltage status bit is set (latched) and the discharge path is activated until V<sub>LED</sub> crosses LED OV\_TH2. The converter is stopped, independently from PWM\_L, until a read and clear command of the status register 1 (LED\_Ov\_Rec bit is reset).

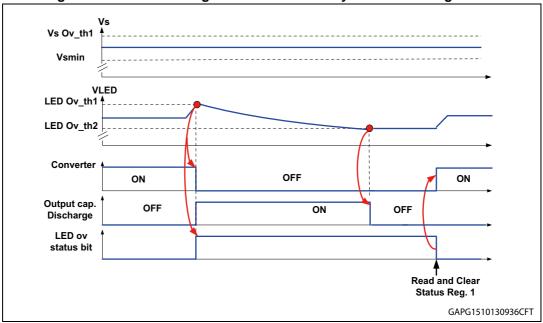

If a LED overvoltage failure event occurs during  $V_S$  overvoltage, (battery OV), the discharge path for the output capacitor is inhibited and the LED overvoltage status bit is not set.

When the  $V_S$  overvoltage event disappears, ( $V_S$  crosses  $V_S$  OV\_TH2), the LED overvoltage status bit is set (latched) and the discharge path is activated until  $V_{LED}$  crosses LED OV\_TH2. The converter is stopped, independently from PWM\_L, until the LED ov status bit is cleared (read and clear of the status register 1). *Figure 17* shows such a case.

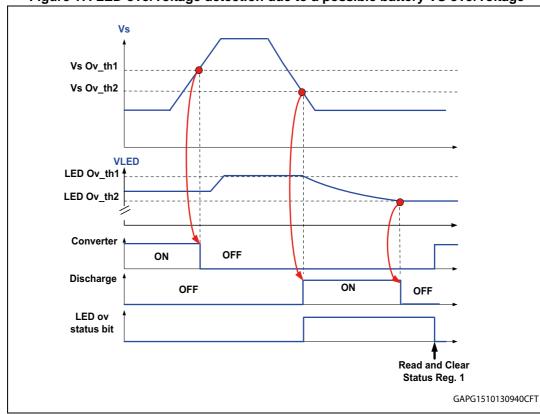

Finally *Figure 18* shows how will be managed the LED\_Ov\_Rec bit in case signal PWM\_L has a low on-time. In this case the LED\_Ov\_Rec bit is reset when the cumulated running time of t<sub>EnRecov</sub> exceeds typ. 5 ms. This feature enables a single recovery of a LED overvoltage event, due to a too fast regulation loop (set by the resistor and capacitor connected to RCCOMP pin), even in PWM operation with low on-time. However, a proper choice of RC network values, avoiding fast transients on the LED string voltage, when the converter is switched ON, it is carefully recommended

a. More than 22 nF

Figure 13. Correct start UP with no LED overvoltage failure

Figure 15. Device behavior in case the low to high transition of PWM\_L signal happens after  $t_{DStart}$  expiration

Figure 17. LED overvoltage detection due to a possible battery VS overvoltage

## 2.2.11 Programming the over/under voltage threshold

The voltage across the LED string is continuously sensed by the external resistor divider R5/R6 and reported inside the chip trough the apposite pin  $V_{LED}$ . Considering negligible the voltage drop due to the sense resistor and the  $V_{DS}$  of external mosfet M2 respect to the LED

voltage string, according to the equation reported below, the LED overvoltage thresholds are given by the following formulas:

$V_{LED\ OV} = OV_{TH1} / K_{L}$ ; being  $K_{L} = R6 / (R5+R6)$ ;

OV\_TH1 is the reference for the OV internal comparator. Typical value for OV\_TH1 is 3.5 V.

LED OV event makes the converter and also mosfet M2 immediately switched OFF, in order to prevent any damage to the LED string or to the driver. Furthermore, following an OV event, the LED\_OV status register is set and an internal load is applied between I<sub>SENSE+</sub> pin and ground in order to fast discharge the voltage across capacitor C4.

In the boost topology application, if a short circuit between the source of external mosfet M2 and GND occurs, an uncontrolled current could flow. In order to avoid this situation, a maximum LED current protection has been inserted, which continuously monitors the voltage across the sense resistor R<sub>SENSE</sub>. If this voltage reaches a value in excess of an internal fixed threshold of (see *Table 24* - LED over current protection threshold parameter), the status bit LED\_OC (led over current) is set and the converter and also mosfet M2 will be immediately switched OFF.

Following a stop of the converter due to an OV event, the device can not be restarted before of C4 discharge (V<sub>LED</sub> is below OV\_TH2).

After an OV event, the converter could restart if a read and clear command of the LED\_OV status bit is done. *Table 3* summarizes the suggested value of K<sub>L</sub> resistor ratio, supposing to have a LED\_OV event, when the voltage across LED string, reaches a value in excess of 50 % of its nominal value.

OV\_COMP OV\_TH<sub>1,2</sub>  $V_{LED} \approx K_L^* V LED_{STRING}$   $V_{LED_OV} = OV_TH 1/K_L$   $K_L = R_6 / (R_5 + R_6)$ GAPG1410131428CFT

Figure 19. LED chain overvoltage thresholds settings. An example for boost and fly back converters

4

| N<br>Number of LED | K <sub>L</sub> | LED CHAIN nominal<br>DROP N*V <sub>F</sub> [V] | overvoltage V <sub>LED_OV</sub> [V] |  |

|--------------------|----------------|------------------------------------------------|-------------------------------------|--|

| 1 <sup>(1)</sup>   | 0.583          | 4                                              | 6                                   |  |

| 2 <sup>(1)</sup>   | 0.292          | 8                                              | 12                                  |  |

| 3 <sup>(1)</sup>   | 0.194          | 12                                             | 18                                  |  |

| 4 <sup>(1)</sup>   | 0.146          | 16                                             | 24                                  |  |

| 5                  | 0.117          | 20                                             | 30                                  |  |

| 6                  | 0.097          | 24                                             | 36                                  |  |

| 7                  | 0.083          | 28                                             | 42                                  |  |

| 8                  | 0.073          | 32                                             | 48                                  |  |

| 9                  | 0.065          | 36                                             | 54 <sup>(2)</sup>                   |  |

| 10                 | 0.0583         | 40                                             | 60 <sup>(2)</sup>                   |  |

Table 3. Suggested K<sub>L</sub> value and overvoltage thresholds

# 2.2.12 Input overvoltage programming

Supply overvoltage is programmed by the external partition ratio  $K_1 = R3/R4$

According to the *Figure 20* input overvoltage thresholds depend on the internal reference voltages  $V_{OVTH1}$  and  $V_{OVTH2}$  (being  $V_{OVTH2} < V_{OVTH1}$ )

Typical values of these internally generated references are 3.5 V and 3 V.

When the Battery voltage reaches a value in excess to  $V_{S\_TH1}$  the converter is immediately stopped. When the battery voltage, going down, reaches a value just lower to  $V_{S\_TH2}$ , the converter restarts again.

VBATT

VS

INP\_OV

VoVTH1,2

Vs\_TH1 = (1+R3/R4)\*VoVTH1

Vs\_TH2 = (1+R3/R4)\*VoVTH2

GAPG1410131443CFT

Figure 20. Input overvoltage programming

Not Applicable on boost converter topology, since the chain LED Drop must be always larger as the maximum battery voltage.

<sup>2.</sup> Theoretical value; effective value will be clamped to 52 V (typ) by the OV protection.

As an example, if we want  $V_{S\_TH1}$  = 20 V, according to the formula of *Figure 20*, R3/R4 will result equal to 4.7 and consequently the deactivation threshold  $V_{S\_TH2}$  will result ~ 17 V.<sup>(b)</sup>

b. Notice that the deactivation threshold must be always greater than the maximum allowed battery value in normal conditions.

# 3 SPI functional description

# 3.1 Serial peripheral interface (ST SPI standard)

The SPI communication is based on a standard ST-SPI 24-bit interface, using CSN, SDI, SDO and SCK signal lines.

Input data are shifted into SDI, MSB first while output data are shifted out on SDO, MSB first.

During active mode, the SPI:

- Triggers the watchdog

- Controls the modes and status of all internal modules (incl. input and output drivers)

- · Provides driver output diagnostic

- Provides device diagnostic (incl. over temperature warning, device operation status)

Note: During standby modes, the SPI is generally deactivated.

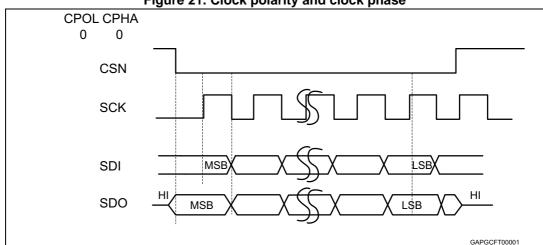

The SPI can be driven by a microcontroller with its SPI peripheral running in following mode:

Figure 21. Clock polarity and clock phase

According to the standard, a generic input bit is sampled by the low to high transition of the clock CLK and a generic output bit changes synchronously to the high to low transition of CLK.

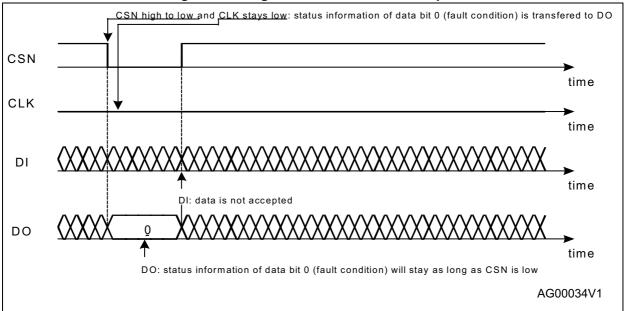

This device is not limited to micro controller through a built-in SPI. Only three CMOS-compatible output pins and one input pin will be needed to communicate with the device. A fault condition can be detected by setting CSN low. If CSN = 0, the DO pin will reflect the global error flag (fault condition) of the device (see *Figure 22*). This operation does not cause a communication error bit in the global status byte to be set.

Figure 22. SPI global error information output

# 3.2 Signal description

- Serial Clock (SCK): this input signal provides the timing of the serial interface. Data

present at Serial Data Input (SDI) is latched on the rising edge of Serial Clock (SCK).

Data on Serial Data Out (SDO) is shifted out at the falling edge of Serial Clock (SCK).

- Serial Data Input (SDI): This input is used to transfer data serially into the device. It receives the data to be written. Values are latched on the rising edge of Serial Clock (SCK).

- Serial Data Output (SDO): this output signal is used to transfer data serially out of the device. Data is shifted out on the falling edge of Serial Clock (SCK). SDO also reflects the status of the <Global Error Flag> (Bit 7 of the <Global Status Register>) while CSN is low and no clock signal is present

- Chip Select Not (CSN): when this input signal is High, the device is deselected and Serial Data Output (SDO) is high impedance. Driving this input Low enables the communication. The communication must start and stop on a Low level of Serial Clock (SCK).

# 3.3 SPI protocol

#### 3.3.1 SDI, SDO format

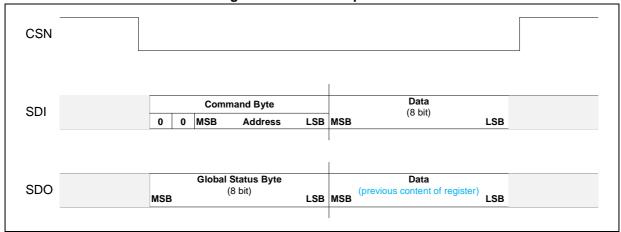

SDI format during each communication frame starts with a command byte.

It begins with two bits of operating code (OC0, OC1) which specify the type of operation (read, write, read and clear status, read device information) and is followed by a 6 bit address (A0:A5). The command byte is followed by an input data byte (D0:D15).

DocID025319 Rev 3

At the beginning of each communication the master device read the contents of the <SPI-frame-ID> register (ROM address 3Eh) of the slave device. This 8 bit register indicates the SPI frame length (24 bit) and the availability of additional features.

Each communication frame consists of a command byte which is followed by 2 data bytes.

The data returned on SDO within the same frame always starts with the <Global Status Byte>. It provides general status information about the device. It is followed by 2 data bytes (i.e. "in-frame-response").

For write cycles the <Global Status Byte> is followed by the previous content of the addressed register.

Table 4. Command byte (8 bit)

| Bit  | 23  | 22  | 21 | 20 | 19 | 18 | 17 | 16 |

|------|-----|-----|----|----|----|----|----|----|

| Name | OC1 | OC0 | A5 | A4 | А3 | A2 | A1 | A0 |

#### Table 5. Input data byte

|      | Data Byte 1 |     |     |     |     |     |    |    |    | Data I | Byte 0 |    |    |    |    |    |

|------|-------------|-----|-----|-----|-----|-----|----|----|----|--------|--------|----|----|----|----|----|

| Bit  | 15          | 14  | 13  | 12  | 11  | 10  | 9  | 8  | 7  | 6      | 5      | 4  | 3  | 2  | 1  | 0  |

| Name | D15         | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6     | D5     | D4 | D3 | D2 | D1 | D0 |

SDO format during each communication frame starts with a specific byte called Global Status Byte (see *Section 3.3.2*). This byte is followed by two output data byte (D0:D7, D8:D15).

#### Table 6. Global status byte

| Bit  | 23  | 22       | 21                             | 20           | 19            | 18          | 17                        | 16        |

|------|-----|----------|--------------------------------|--------------|---------------|-------------|---------------------------|-----------|

| Name | GEF | Comm_Err | Not (chip reset or Comm_Error) | LED overload | Temp. warning | Overvoltage | V <sub>CC1</sub><br>Error | Fail safe |

#### Table 7. Output data byte

|      | Data Byte 1 |     |     |     |     |     |    |    | Data Byte 0 |    |    |    |    |    |    |    |

|------|-------------|-----|-----|-----|-----|-----|----|----|-------------|----|----|----|----|----|----|----|

| Bit  | 15          | 14  | 13  | 12  | 11  | 10  | 9  | 8  | 7           | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Name | D15         | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7          | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

#### 3.3.2 Global status byte description

The data shifted out on SDO during each communication starts with a specific byte called Global Status Byte. This one is used to inform the microcontroller about global faults which can be happened on the channel part (like thermal warning, OVL,...) or on the SPI interface (like communication error,...). This specific register has the following format.

Table 8. Global status byte

| Bit | Name                            | Description                                                                                                                                                                                 |  |  |  |  |  |

|-----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 23  | Global Error<br>Flag (GEF)      | This bit is an OR combination of the remaining bits of the register OR (Vs_uv) OR (Lmode_err)                                                                                               |  |  |  |  |  |

| 22  | Comm_Err                        | The right number of SPI clocks within any valid spi command is 24.  If not, then this bit is set to '1'.  This bit goes to '0' automatically after any valid spi command                    |  |  |  |  |  |

| 21  | Not (Chip reset<br>OR Comm Err) | After a POR phase this bit is active ('0'). It becomes inactive ('1') after the first valid spi command, provided that any communication error occurs.                                      |  |  |  |  |  |

| 20  | LED Overload                    | This bit is set when an LED overcurrent event is detected                                                                                                                                   |  |  |  |  |  |

| 19  | Temp. warning                   | Temperature Warning for the LED                                                                                                                                                             |  |  |  |  |  |

| 18  | Overvoltage                     | LED chain overvoltage or Vs overvoltage via INP_OV (Led_Ov OR Vs_Overvoltage)                                                                                                               |  |  |  |  |  |

| 17  | V <sub>CC1</sub> Error          | This bit is an OR combination of all the errors related to V <sub>CC1</sub>                                                                                                                 |  |  |  |  |  |

| 16  | Fail Safe                       | This bit is set if the device is in a limp home mode (Data In stuck at '0' or '1', watchdog time out, software limp home), V <sub>CC1</sub> undervoltage for more than 2 ms in active mode. |  |  |  |  |  |

## 3.3.3 Operating code definition

The SPI interface features four different addressing modes which are listed in *Table 10*.

**Table 9. Operation code definition**

| OC1 | OC0 | Meaning                         |  |  |  |

|-----|-----|---------------------------------|--|--|--|

| 0   | 0   | Write operation                 |  |  |  |

| 0   | 1   | Read operation                  |  |  |  |

| 1   | 0   | Read and clear status operation |  |  |  |

| 1   | 1   | Read device information         |  |  |  |

The <Write Mode> and <Read Mode> operations allow access to the RAM of the device.

A <Read and Clear Mode> operation is used to read a status register and subsequently clears its content.

The <Read Device Information> allows access to the ROM area which contains device related information such as <ID-Header>, <Product Code>, <Silicon Version> and <SPI-frame-ID>.

#### Write mode

The write mode of the device allows writing the content of the input data byte into the addressed register. Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first.

During the same sequence outgoing data are shifted out MSB first on the falling edge of the CSN pin and subsequent bits on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status Byte and the second to the previous content of the addressed register.

Figure 23. SPI write operation

#### Read mode

The read mode of the device allows to read and to check the state of any register. Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first. Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status Byte and the second to the content of the addressed register. In case of a read mode on an unused address, the 'global status/error' byte on the SDO pin is following by 00H byte.

In order to avoid inconsistency between the Global status byte and the status register, the status register contents are frozen during SPI communication.

Figure 24. SPI read operation

#### Read and clear status command

The read and clear status operation is used to clear the content of the addressed status register (see Section: Status registers 1). A read and clear status operation with address

3Fh clears all status registers simultaneously and reads back the configuration register (GLOBCTR).

Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first. The command byte allows to determine which register content is read then erased while the data byte is 'don't care'.

Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status byte and the second to the content of the addressed register.

In order to avoid inconsistency between the Global status byte and the status register, the status register contents are frozen during SPI communication.

Figure 25. SPI read and clear operation

#### Read device information

Specific information can be read but not modified during this mode.

Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first. The command byte allows to determine which information is read while the data byte is 'don't care'.

Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the Global Status byte and the second to the content of the addressed register.

CSN Don't care **Command Byte** SDI (8 bit) 1 MSB Address LSB MSB LSB Global Status Byte Data SDO (8 bit) (8 bit) MSB LSB MSB LSB

#### Figure 26. SPI read device information

#### **Address mapping** 3.4

Table 10. RAM memory map

| Address | Name               | Access     | Content                                                              |

|---------|--------------------|------------|----------------------------------------------------------------------|

| 00h     | Reserved           | Read/write | Reserved                                                             |

| 01h     | Control register 1 | Read/write | Mux settings, WD period and retrigger                                |

| 02h     | Control register 2 | Read/write | Spread spectrum settings, max input current and LED current settings |

| 03h     | Control register 3 | Read/write | SW Limp Home, OTA/driver and converter delay control                 |

| 04h     | Status register 1  | Read       | Detailed status information                                          |

| 05h     | Status register 2  | Read       | WD status, operation mode and LMode error                            |

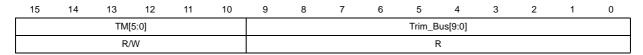

| 3E      | Trimming and test  | Read       | Trimming bus and test mode select                                    |

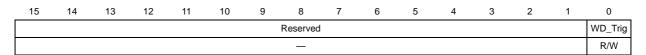

| 3F      | Configuration reg. | Read/write | WD retrigger bit                                                     |

Table 11. ROM memory map

| Address | Name           | Access    | Content                                   |

|---------|----------------|-----------|-------------------------------------------|

| 00h     | ID header      | Read only | 4300h (ASSP ST_SPI)                       |

| 01h     | Version        | Read only | 0100h                                     |

| 02h     | Product code 1 | Read only | 3100h (dec. 49)                           |

| 03h     | Product code 2 | Read only | 5100h (ASCII 'Q')                         |

| 3Eh     | SPI frame ID   | Read only | 4200h (Watchdog available, 24 bit ST-SPI) |

## 3.5 Control registers (RAM)

### **Control registers 1**

| 15 | 14 | 13 | 12 | 11   | 10    | 9 | 8 | 7 | 6 | 5   | 4      | 3      | 2      | 1         | 0       |

|----|----|----|----|------|-------|---|---|---|---|-----|--------|--------|--------|-----------|---------|

|    |    |    |    | Rese | erved |   |   |   |   | Mux | [[1:0] | Mux_En | En_Ntc | WD_Period | WD_trig |

Address: 0x01h Type: R/W

**Reset:** 0000 0000 0000 1110b

Bit [6:15] Reserved

Bit [5:4] Mux[1:0]:

00 (default): the signal on the PWM pin is reflected on Mout pin

01: the signal on the V<sub>LED</sub> is reflected on Mout pin

10: the signal on NTC is selected

11: the signal on Lmode pin is selected

Bit [3] Mux\_En:

0: the Mout pin is inactive (tristate)1: the Mout pin is active (default)

Bit [2] En\_Ntc:

When set, the current fold back feature enabled in case of LED overtemperature conditions.

This bit is ignored in case of any LIMP MODE and the LED temperature monitoring is activated (the NTC control is internal)

Bit [1] WD\_Period:

0: WD timeout = 100 ms

1: WD timeout = 200 ms (default)

Bit [0] WD\_trig:

This bit must be toggled within the WD period to refresh the WD

#### **Control registers 2**

| 15 | 14        | 13 | 12   | 11    | 10      | 9 | 8  | 7         | 6   | 5 | 4 | 3  | 2         | 1   | 0 |

|----|-----------|----|------|-------|---------|---|----|-----------|-----|---|---|----|-----------|-----|---|

| -  | Fdev[2:0] |    | Fmod | [0:1] | Dith_En |   | Le | ed_Curr[4 | :0] |   |   | Ma | ax_Curr[4 | :0] |   |

Address: 0x02h

Type: R/W

**Reset:** 0101 1110 0001 1111b

Bit [15:13] Fdev[2:0]: frequency deviation of the internal oscillator (see Table 12)

Bit [12:11] Fmod[1:0]: frequency modulation of the internal oscillator (see Table 13)

Bit [10] Dith\_En: enable or disable random dither effect.

If this bit is set Dithering is enabled; If the bit is reset, the dithering is disabled

Bit [9:5] Led\_Curr[4:0]: these bits set the LED current.

The LED current is given by:

$0.05 + (0.2 * Led\_Curr[4:0]d) / 31) / (R_{SENSE}) [A] (typ)$

Where Led\_Curr[4:0]d = decimal value of Led\_Curr[4:0]

Bit [4:0] Max\_Curr[4:0]: these bits set the maximum input current.

The internal current limiter voltage threshold is:

1 + (2.5 \* Max\_Curr[4:0]d) / 31 in [V] (typ)

Considering the gain of the amplifier of 10, the current limitation is:

$(1 + 2.5 * Max_Curr[4:0]d / 31) / (10 R_{SHUNT}) (typ);$

Where Max \_Curr[4:0]d = decimal value of Max\_Curr[4:0]

Table 12. Internal oscillator frequency deviation settings

| Fdev[2] | Fdev[1] | Fdev[0] | Frequency deviation |

|---------|---------|---------|---------------------|

| 0       | 0       | 0       | 0 %                 |

| 0       | 0       | 1       | 5 %                 |

| 0       | 1       | 0       | 10 %                |

| 0       | 1       | 1       | 15 %                |

| 1       | 0       | 0       | 20 %                |

| 1       | 0       | 1       | 25 %                |

| 1       | 1       | 0       | 30 %                |

Table 13. Internal oscillator frequency modulation settings

|         | · · · · · · · · · · · · · · · · · · · | <u> </u>             |

|---------|---------------------------------------|----------------------|

| Fmod[1] | Fmod[0]                               | Frequency modulation |

| 0       | 0                                     | 1.95 kHz             |

| 0       | 1                                     | 3.9 kHz              |

| 1       | 0                                     | 7.8 kHz              |

| 1       | 1                                     | 15.6 kHz             |

#### **Control registers 3**

| 15 | 14       | 13 | 12    | 11 | 10     | 9       | 8 | 7 | 6      | 5       | 4 | 3 | 2 | 1 | 0 |   |

|----|----------|----|-------|----|--------|---------|---|---|--------|---------|---|---|---|---|---|---|

|    | Reserved |    | Lh_Sw |    | Ctrl_O | ta[3:0] |   |   | Ctrl_D | rv[3:0] |   |   |   |   |   | l |

Address: 0x03h

Type: R/W

**Reset:** 0000 1000 0000 0000b

Bit [15:13] Reserved

Bit [12] Lh\_Sw:

The device goes in Limp Home mode without WD supervision ( $V_{CC1}$  stays on) when the bit is set

Bit [11:8] Ctrl\_Ota[3:0]: these bits set the delay between a rising edge of the PWM\_L signal and a connection of the output of the operation transconductance amplifier.

The delay is given by Ctrl\_Ota[3:0]d \* 3.3 µs (typ.)

Where Ctrl\_Ota[3:0]d is the decimal value of Ctrl\_Ota[3:0]

The default of these bits are loaded from the corresponding control bus

Bit [7:4] Ctrl\_Drv[3:0]: these bits set the delay between a rising edge of the PWM\_L signal and the activation of the converter

The delay is given by:

Ctrl\_Drv[3:0]d \* 1.67 µs (typ.)

Where Ctrl\_Drv[3:0]d is the decimal value of Ctrl\_Drv[3:0]

The default of these bits are loaded from the corresponding control bus

Bit [3:0] Ctrl\_Sw[3]: these bits set the delay between the falling edge of the PWM\_L signal and the turn off of the dimming mosfet M2.

The delay is given by:

Ctrl\_Sw[3:0]d \* 1.67 µs (typ.)

Where Ctrl\_Sw[3:0]d is the decimal value of Ctrl\_Sw[3:0]

The default of these bits are loaded from the corresponding control bus.

## 3.6 Status registers

### Status registers 1

| 15 | 14       | 13 | 12               | 11    | 10               | 9            | 8                  | 7      | 6        | 5         | 4          | 3       | 2                | 1          | 0       |

|----|----------|----|------------------|-------|------------------|--------------|--------------------|--------|----------|-----------|------------|---------|------------------|------------|---------|

|    | Reserved |    | Lmode_Err        | Vs_Ov | Vs_Uv            | Led_Temp_War | Led_Oc             | Led_Ov | Vcc1_Off | Vcc1_Fail | Vcc1_Uv_To | Vcc1_Ot | Vcc1_Sc          | SDI_stuck@ | WD_fail |

|    | _        |    | R <sup>(1)</sup> | R     | R <sup>(1)</sup> |              | R/C <sup>(2)</sup> |        | R        |           |            | R/0     | C <sup>(2)</sup> |            |         |

- 1. "Read only", real time bit.

- 2. These bits are latched until a "Read and Clear" access.

Address: 0x04h

Type: R/C

Bit [15:13] Reserved

Bit [12] Lmode\_Err: this bit is set if a mismatch between the signal on LMODE pin and VLED pin is detected.

Bit [11] Vs\_Ov: is set if an overvoltage event at the supply line is detected

Bit [10] Vs\_Uv: is set if an under voltage event at the supply line is detected

Bit [9] Led\_Temp\_Warn: temperature warning for the LED