#### SYNCHRONOUS MOSFET CONTROLLER IN SO-8

#### Description

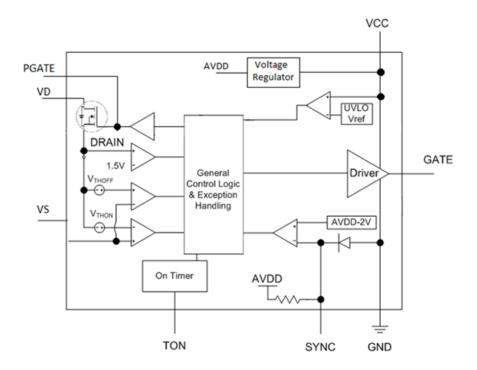

The ZXGD3110N8 is intended to drive a MOSFET configured as an ideal diode replacement. The device is comprised of a high voltage detector stage and gate driver. The detector monitors the voltage between the drain and the source of the MOSFET and if this voltage is less than the turn on threshold voltage of the controller a positive voltage is applied to the MOSFET's Gate Pin. As the load current decays to zero and the voltage between the drain and source of the MOSFET increases beyond the turn-off threshold value MOSFET is rapidly turned off.

Intelligent features of this IC are the Minimum Off-Time (T<sub>OFF</sub>) and Minimum On-Time (T<sub>ON</sub>), these features blanket the noise generated during the turn-on and turn-off instances of the power FET. Also Light Load Detection (LLD) for improved efficiency at light and no load, where synchronous rectification is no more beneficial. Other features include Undervoltage Lockout (UVLO), SYNC feature for CCM operation and low turn-off threshold voltage for improved efficiency.

#### **Applications**

Flyback Converters in:

- Power Adaptors

- Auxiliary Power Supplies

- PoE Power Devices

#### Resonant Converters in:

- High Power Adaptors

- 85+/90+ Compliant ATX and Server Power Supplies

#### **Features**

- · Frequency of Operation up to 500kHz

- Suitable for Discontinuous Conduction Mode (DCM),

Continuous Conduction Mode (CCM) and Critical (CrCM)

Conduction Mode

- Minimum On-Time and Off-Time to Reduce Turn-On/Off Oscillations

- Intelligent Light Load Detection and Sleep Mode

- Turn-Off Propagation Delay Time 30ns

- Drain Voltage Rating of 200V

- Recommended Operating Voltage from 4.5V up to 12V

- Source and Sink Current of 2A and 4A Respectively

- Low Component Count

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony free. "Green" Device (Note 3)

#### **Mechanical Data**

- Case: SO-8

- Case Material: Molded Plastic. "Green" Molding Compound.

UL Flammability Classification Rating 94V-0

- Moisture Sensitivity: Level 1 per J-STD-020

- Terminals: Finish Matte Tin Plated Leads, Solderable per MIL-STD-202, Method 208 (§3)

- Weight: 0.074 grams (Approximate)

#### **Ordering Information** (Note 4)

| Product      | Marking  | Reel Size (inches) | Tape Width (mm) | Quantity per Reel |

|--------------|----------|--------------------|-----------------|-------------------|

| ZXGD3110N8TC | ZXGD3110 | 13                 | 12              | 2,500             |

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- 2. See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen and Antimony free, "Green" and Lead-Free

- 3. Halogen and Antimony free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

- 4. For packaging details, go to our website at http://www.diodes.com/products/packages.html.

# **Marking Information**

ZXGD = Product Type Marking Code, Line 1 3110 = Product Type Marking Code, Line 2 YY = Year (ex: 15 = 2015) WW = Week (01 - 53)

# **Functional Block Diagram**

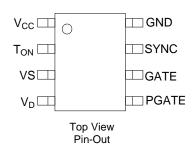

# **Pin Descriptions**

| Pin Number | Pin Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Vcc             | Power Supply Pin $V_{CC}$ supplies all the internal circuitry of the device. A DC supply is required to be connected to this pin. A $10\mu F$ or larger capacitor must be connected between this pin and GND Pin as close as possible. The device will not function until the $V_{CC}$ has risen above the UVLO threshold. The device can safely be turned off by bringing $V_{CC}$ below the UVLO threshold (minus the UVLO threshold hysteresis). If $V_{CC}$ drops below the UVLO threshold (minus UVLO threshold hysteresis), the MOSFET is turned off and the $T_{OFF/ON}$ Pin is internally connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2          | T <sub>ON</sub> | Minimum On-Time Minimum on-time setting pin. Connect this pin to Ground via R <sub>TON</sub> resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3          | Vs              | Source Voltage Connect this pin to the source of the synchronous MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4          | V <sub>D</sub>  | Drain Voltage This pin needs to be connected as closely as possible to the transformer used in the application, to minimize the effects of parasitic inductance on the performance of the device. The device requires that V <sub>D</sub> has a voltage greater than 1.5V and that the T <sub>OFF</sub> timer has expired before the MOSFET is able to be activated. Once these conditions are met and the voltage sensed on the V <sub>D</sub> Pin is 150mV lower than the V <sub>S</sub> Pin, the gate output to the sync MOSFET will go high and the T <sub>ON</sub> (minimum on-time) period is started. The MOSFET will remain on for at least the length of the minimum on-time. After the T <sub>ON</sub> period, the MOSFET will remain on until the V <sub>D</sub> to V <sub>S</sub> voltage has reached to the V <sub>THOFF</sub> threshold, at which point the gate output will go low. If the V <sub>THOFF</sub> threshold is reached before the T <sub>ON</sub> period has expired, the device will enter the Light Load Mode. Under this mode, the MOSFET will not be turned on the next switching cycle. The device will come out of light load, once the on-time of the synchronous MOSFET exceeds the set minimum on-time. |

| 5          | PGATE           | Protection MOSFET Gate A 100nF capacitor should be connected between this pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6          | GATE            | Gate Connect GATE to the gate of the controlled MOSFET through a small series resistor using short PC board tracks to achieve optimal switching performance. The gate output can source >2A peak source current while turning on the sync MOSFET and can sink >4A peak current while turning on the sync MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7          | SYNC            | Gate Turn-Off Synchronization If a falling edge is sensed on this pin, the gate output is pulled low, irrespective of the sensed drain to source voltage or the state of the Ton timer. This characteristic allows the device to be easily used in a Continuous Conduction Mode (CCM) system. The SYNC Pin needs to be connected to a suitable control signal on the primary side of the convertor, using a high voltage isolation cap, transformer or other suitable means.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8          | GND             | Ground This is the reference potential for all internal comparators and thresholds. A 10μF decoupling capacitor is required to place as close as possible between V <sub>CC</sub> and GND Pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### Absolute Maximum Ratings (@TA = +25°C, unless otherwise specified.)

| Characteristic                                   | Symbol            | Value      | Unit |

|--------------------------------------------------|-------------------|------------|------|

| Supply Voltage, Relative to GND                  | Vcc               | -0.3 to 15 | V    |

| Drain Pin Voltage                                | $V_D$             | -1 to +200 | V    |

| Gate Output Voltage                              | V <sub>G</sub>    | 12         | V    |

| Minimum Off-Time (T <sub>OFF</sub> ) Pin Voltage | SYNC              | -0.3 to 6  | V    |

| Minimum On-Time (T <sub>ON</sub> ) Pin Voltage   | $V_{TON}$         | -0.3 to 6  | V    |

| Gate Driver Peak Source Current                  | Isource           | 5          | Α    |

| Gate Driver Peak Sink Current                    | I <sub>SINK</sub> | 5          | Α    |

| Input Voltage Range V <sub>S</sub>               | Vs                | -1 to 1    | V    |

### **Thermal Characteristics**

| Characteristic                          |           | Symbol           | Value       | Unit  |  |

|-----------------------------------------|-----------|------------------|-------------|-------|--|

|                                         | (Note 5)  |                  | 490         |       |  |

|                                         | (Note 5)  |                  | 3.92        |       |  |

|                                         | (Note 6)  |                  | 655         |       |  |

| Power Dissipation                       | (11010-0) | $P_D$            | 5.24        | mW    |  |

| Linear Derating Factor                  | (Note 7)  | י ט              | 720         | mW/°C |  |

|                                         | (Note 1)  |                  | 5.76        |       |  |

|                                         | (Note 8)  |                  | 785         |       |  |

|                                         | ` ,       |                  | 6.28        |       |  |

|                                         | (Note 5)  |                  | 255         |       |  |

| Thermal Resistance, Junction to Ambient | (Note 6)  | $R_{	heta JA}$   | 191         | °C/W  |  |

| Thermal Resistance, Sundion to Ambient  | (Note 7)  | NejA             | 173         | O/ VV |  |

|                                         | (Note 8)  |                  | 159         |       |  |

| Thermal Resistance, Junction to Lead    | (Note 9)  | $R_{	heta JL}$   | 55          | °C/W  |  |

| Thermal Resistance, Junction to Case    | (Note 10) | $R_{	heta JC}$   | 45          | °C/W  |  |

| Maximum Junction Temperature            |           | $T_J$            | +150        | °C    |  |

| Storage Temperature Range               |           | T <sub>STG</sub> | -65 to +150 | C     |  |

### ESD Ratings (Note 11)

| Characteristic                             | Symbol  | Value | Unit | JEDEC Class |

|--------------------------------------------|---------|-------|------|-------------|

| Electrostatic Discharge – Human Body Model | ESD HBM | 2,000 | V    | 1C          |

| Electrostatic Discharge – Machine Model    | ESD MM  | 500   | V    | С           |

Notes:

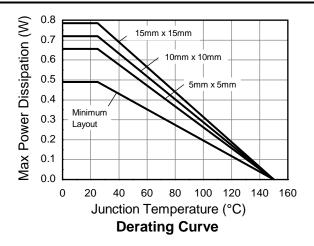

- 5. For a device surface mounted on minimum recommended pad layout FR4 PCB with high coverage of single sided 1oz copper, in still air conditions; the device is measured when operating in a steady-state condition.

- 6. Same as Note (5), except Pin 1 (V<sub>CC</sub>) and Pin 8 (GND) are both connected to separate 5mm x 5mm 1oz copper heatsinks.

- 7. Same as Note (6), except both heatsinks are 10mm x 10mm.

- 8. Same as Note (6), except both heatsinks are 15mm x 15mm.

- 9. Thermal resistance from junction to solder-point at the end of each lead on Pin 1 (VCC) and Pin 8 (GND).

- 10. Thermal resistance from junction to top of the case.

- 11. Refer to JEDEC specification JESD22-A114 and JESD22-A115.

# Recommended Operating Conditions (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol             | Parameter                            | Min  | Max  | Unit |

|--------------------|--------------------------------------|------|------|------|

| Vcc                | Supply Voltage Range                 | 4.5  | 12   | V    |

| V <sub>DS</sub>    | Voltage Cross Drain and Source       | -1   | 200  | V    |

| F <sub>SW</sub>    | Switching Frequency                  | 20   | 600  | kHz  |

| TJ                 | Operating Junction Temperature Range | -40  | +125 | °C   |

| R <sub>TON</sub>   | T <sub>ON</sub> Resistor Value       | 8.25 | 100  | kΩ   |

| C <sub>VCC</sub>   | V <sub>CC</sub> Bypass Capacitor     | 10   | _    | μF   |

| TW <sub>sync</sub> | Sync Pulse Width                     | 20   | _    | ns   |

# **Thermal Derating Curve**

# **Electrical Characteristics** (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol               | Parameter                                                    | Conditions                                                                       | Min                    | Тур                    | Max                    | Unit |

|----------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------|------------------------|------------------------|------|

| .,                   | lateral Bandata Ostant                                       | V <sub>CC</sub> = 5.5V                                                           | _                      | 4.5                    | _                      | V    |

| V <sub>AVDD</sub>    | Internal Regulator Output                                    | V <sub>CC</sub> = 12V                                                            | _                      | 4.7                    | _                      | V    |

| ICCSTART             | Supply Current (Undervoltage)                                | V <sub>CC</sub> = 2.6V                                                           | _                      | 160                    | 220                    | μA   |

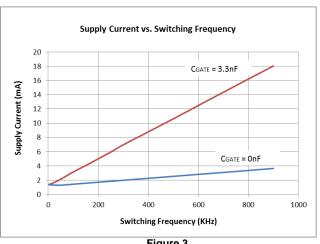

|                      |                                                              | $V_{CC} = 5.5V$ , $F_{SW} = 100$ kHz $C_{GATE} = 0$ pF                           | _                      | 1.5                    | 1.8                    |      |

| 100                  |                                                              | $V_{CC} = 12V, F_{SW} = 100kHz$ $C_{GATE} = 0pF$                                 | _                      | 1.8                    | 2.2                    | A    |

| ICCON                | Supply Current (Enabled)                                     | $V_{CC}$ = 5.5V, $F_{SW}$ = 100kHz $C_{GATE}$ = 3,300pF                          | _                      | 3.2                    | 4                      | mA   |

|                      |                                                              | $V_{CC}$ = 12V, $F_{SW}$ = 100kHz $C_{GATE}$ = 3,300pF                           | _                      | 5                      | 7                      |      |

| Undervoltage Loc     | kout (UVLO)                                                  |                                                                                  |                        |                        |                        |      |

| UVLO <sub>TH</sub>   | V <sub>CC</sub> Undervoltage Lockout Threshold Rising        |                                                                                  | 2.8                    | 3.0                    | 3.20                   | V    |

| UVLO <sub>HYS</sub>  | V <sub>CC</sub> Undervoltage Lockout Threshold<br>Hysteresis | _                                                                                | _                      | 200                    | _                      | mV   |

| MOSFET Voltage       | Sensing                                                      |                                                                                  |                        |                        |                        |      |

| V <sub>THARM</sub>   | Gate Re-Arming Threshold                                     | V <sub>D</sub> to GND, Rising                                                    | -1.3                   | -1.5                   | -1.7                   | V    |

| $V_{THON}$           | Gate Turn-On Threshold                                       | $(V_D-V_S)$ Falling, $V_S = 0V$                                                  | -220                   | -150                   | -80                    | mV   |

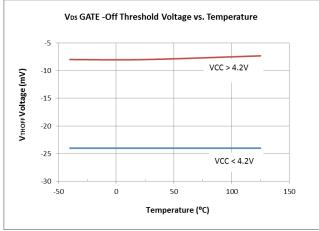

| V <sub>THOFFLV</sub> | Gate Turn-Off Threshold                                      | $(V_D-V_S)$ Rising, $V_S = 0V$ , $V_{CC} < 4.3V$                                 | -30                    | -20                    | -10                    | mV   |

| Vтноггнv             | Gate Turn-Off Threshold                                      | $(V_D-V_S)$ Rising, $V_S = 0V$ , $V_{CC} > 4.3V$                                 | -10                    | -4                     | -1                     | mV   |

| T <sub>D(ON)</sub>   | Gate Turn-On Propagation Delay                               | From V <sub>THON</sub> to Gate > 1V                                              | _                      | 30                     | 52                     | ns   |

| T <sub>D(OFF)</sub>  | Gate Turn-Off Propagation Delay                              | From V <sub>THOFF</sub> to Gate < 4V                                             | _                      | 30                     | 62                     | ns   |

| Minimum On-Time      | 9                                                            |                                                                                  |                        |                        |                        |      |

| T <sub>ON-LR</sub>   | Minimum On-Time Low Resistance                               | $R_{TON} = 8.25 k\Omega$                                                         | 0.26                   | 0.34                   | 0.42                   | μs   |

| T <sub>ON-HR</sub>   | Minimum On-Time High Resistance                              | $R_{TON} = 100k\Omega$                                                           | 2.2                    | 3                      | 3.8                    | μs   |

| Synchronization      |                                                              |                                                                                  |                        |                        |                        |      |

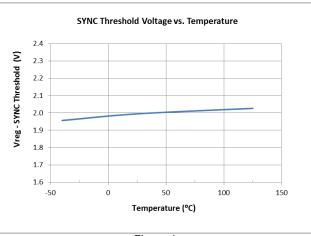

| VTHSYNC              | SYNC Falling Threshold                                       | Gate Output from High to Low                                                     | V <sub>AVDD</sub> -2.4 | V <sub>AVDD</sub> -2.0 | V <sub>AVDD</sub> -1.6 | V    |

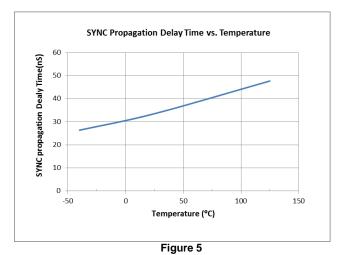

| T <sub>SDLY</sub>    | SYNC Propagation Delay (Note 8)                              | SYNC Falling to Gate Falling 10%, 4.5V < V <sub>CC</sub> < 5.5V                  | _                      | 40                     | _                      | ns   |

| R <sub>SYNC</sub>    | SYNC Pull Up Resistance (Note 8)                             | Internal Resistance from SYNC to V <sub>CC</sub> , 4.5V < V <sub>CC</sub> < 5.5V | _                      | 2.0                    | _                      | kΩ   |

# Electrical Characteristics (Continued) (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Gate Driver          | Gate Driver                                              |                                                              |     |      |     |     |

|----------------------|----------------------------------------------------------|--------------------------------------------------------------|-----|------|-----|-----|

| R <sub>GUP</sub>     | Gate Pull-Up Resistance Enabled                          | I <sub>GATE</sub> = -100mA                                   | _   | 2.3  | _   | Ω   |

| R <sub>GDN</sub>     | Gate Pull-Down Resistance Enabled                        | I <sub>GATE</sub> = 100mA                                    | _   | 1.1  | _   |     |

| Isource              | Peak Gate Source Current                                 | C <sub>GATE</sub> = 22nF                                     | _   | 3    | _   | Α   |

| I <sub>SINK</sub>    | Peak Gate Sink Current                                   | C <sub>GATE</sub> = 22nF                                     | _   | 4    | _   | _ ^ |

| V                    | Gate Output High Voltage                                 | V <sub>CC</sub> = 5V                                         | 4.7 | _    | _   |     |

| Vонg                 | Gate Output High Voltage                                 | V <sub>CC</sub> = 12V                                        | 9   | _    | _   | V   |

| V <sub>OLG</sub>     | Gate Output Low Voltage                                  | V <sub>CC</sub> = 5V                                         | _   | _    | 0.3 |     |

|                      |                                                          | 4V to 1V, C <sub>GATE</sub> = 3,300pF, V <sub>CC</sub> = 5V  | _   | 14   | 42  |     |

| T <sub>FGATE</sub>   | Gate Fall Time                                           | 9V to 1V, C <sub>GATE</sub> = 3,300pF, V <sub>CC</sub> = 12V | _   | 20   | 42  | ns  |

|                      |                                                          | 1V to 4V, C <sub>GATE</sub> = 3,300pF, V <sub>CC</sub> = 5V  | _   | 16   | 42  | 113 |

| T <sub>RGATE</sub>   | Gate Rise Time                                           | 1V to 9V, C <sub>GATE</sub> = 3,300pF, V <sub>CC</sub> = 12V | _   | 20   | 42  |     |

| Exception Handlin    | Exception Handling                                       |                                                              |     |      |     |     |

| T <sub>OVER</sub>    | Overtemperature                                          | _                                                            | _   | +150 | _   | °C  |

| T <sub>RECOVER</sub> | Temperature to Recover from<br>Overtemperature Exception | _                                                            | _   | +125 | _   | °C  |

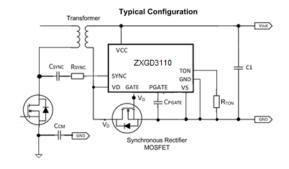

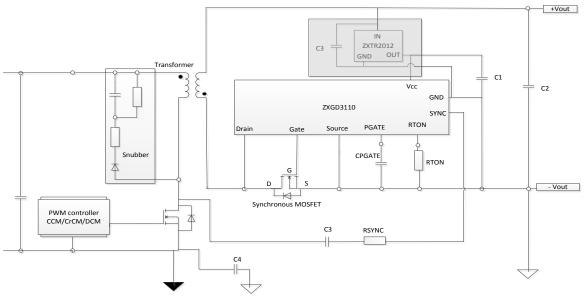

# **Typical Application Circuit**

Less than 12V rails can be directly connected to the Vcc. For more than 12V operation, a regulator arrangement is suggested in the figure.

C3 of  $1\mu F$  must be connected

CPGATE of 0.1µF must be connected

C1 of >10 $\mu F$  must be connected as close as possible to Vcc and ground with minimum track length

### **Typical Performance Characteristics**

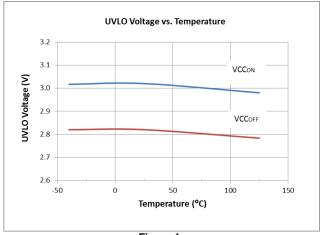

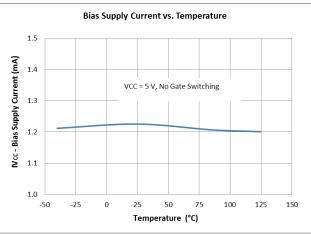

Figure 1

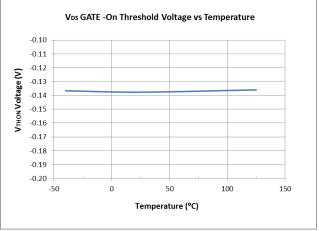

Figure 3

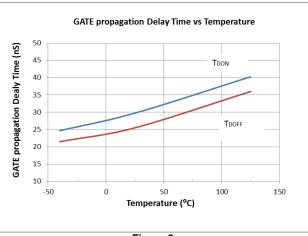

Figure 4

Figure 6

### **Typical Performance Characteristics (Continued)**

Figure 7

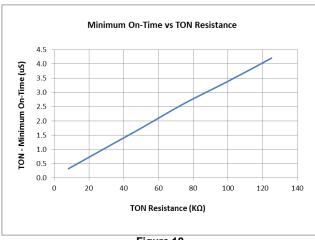

Figure 10

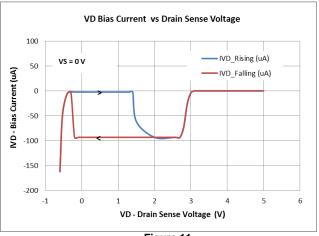

Figure 11

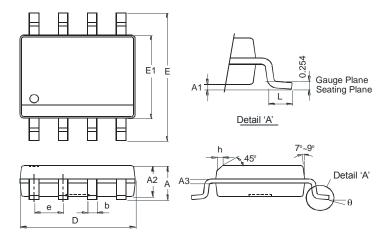

# **Package Outline Dimensions**

Please see AP02002 at http://www.diodes.com/datasheets/ap02002.pdf for the latest version.

#### SO-8

| SO-8   |          |         |

|--------|----------|---------|

| Dim    | Min      | Max     |

| Α      | 1        | 1.75    |

| A1     | 0.10     | 0.20    |

| A2     | 1.30     | 1.50    |

| A3     | 0.15     | 0.25    |

| b      | 0.3      | 0.5     |

| D      | 4.85     | 4.95    |

| E      | 5.90     | 6.10    |

| E1     | 3.85     | 3.95    |

| е      | 1.27     | Тур     |

| h      | 1        | 0.35    |

| L      | 0.62     | 0.82    |

| θ      | 0°       | 8°      |

| All Di | nensions | s in mm |

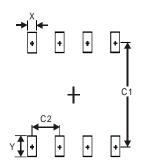

### **Suggested Pad Layout**

Please see AP02001 at http://www.diodes.com/datasheets/ap02001.pdf for the latest version.

SO-8

| Dimensions | Value (in mm) |

|------------|---------------|

| Х          | 0.60          |

| Υ          | 1.55          |

| C1         | 5.4           |

| C2         | 1 27          |

Note: For high voltage applications, the appropriate industry sector guidelines should be considered with regards to creepage and clearance distances between device Terminals and PCB tracking.

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2015, Diodes Incorporated

www.diodes.com