# SURFACE MOUNT SILICON DUAL P-CHANNEL ENHANCEMENT-MODE MOSFETS

\* Device is *Halogen Free* by design

#### **APPLICATIONS:**

- Load/Power Switches

- · Power Supply Converter Circuits

- Battery Powered Portable Equipment

# Central semiconductor corp.

www.centralsemi.com

## **DESCRIPTION:**

These CENTRAL SEMICONDUCTOR devices are dual chip P-Channel enhancement-mode MOSFETs, manufactured by the P-Channel DMOS Process, designed for high speed pulsed amplifier and driver applications. The CMLDM8002A utilizes the USA pinout configuration, while the CMLDM8002AJ, utilizing the Japanese pinout configuration, is available as a special order. These special dual dransistor devices offer low rDS(on) and low VDS(on).

MARKING CODES: CMLDM8002A: C08

CMLDM8002AG\*: CG8 CMLDM8002AJ: CJ8

#### **FEATURES:**

- Dual Chip Device

- · Fast Switching

- Low rDS(on)

- Logic Level CompatibleSmall SOT-563 package

- · Low V<sub>DS(on)</sub>

- Low Threshold Voltage

| MAXIMUM RATINGS: (T <sub>A</sub> =25°C)    | SYMBOL                            |             | UNITS |

|--------------------------------------------|-----------------------------------|-------------|-------|

| Drain-Source Voltage                       | $V_{DS}$                          | 50          | V     |

| Drain-Gate Voltage                         | $V_{DG}$                          | 50          | V     |

| Gate-Source Voltage                        | $V_{GS}$                          | 20          | V     |

| Continuous Drain Current                   | ΙD                                | 280         | mA    |

| Continuous Source Current (Body Diode)     | IS                                | 280         | mA    |

| Maximum Pulsed Drain Current               | $I_{DM}$                          | 1.5         | Α     |

| Maximum Pulsed Source Current              | I <sub>SM</sub>                   | 1.5         | Α     |

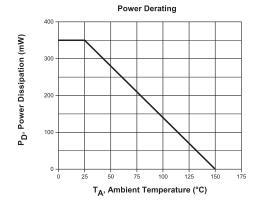

| Power Dissipation (Note 1)                 | $P_{D}$                           | 350         | mW    |

| Power Dissipation (Note 2)                 | $P_{D}$                           | 300         | mW    |

| Power Dissipation (Note 3)                 | $P_{D}$                           | 150         | mW    |

| Operating and Storage Junction Temperature | T <sub>J</sub> , T <sub>stg</sub> | -65 to +150 | °C    |

| Thermal Resistance                         | $\Theta_{JA}$                     | 357         | °C/W  |

## **ELECTRICAL CHARACTERISTICS PER TRANSISTOR:** (TA=25°C unless otherwise noted)

| SYMBOL                                | TEST CONDITIONS                           | MIN | MAX  | UNITS |

|---------------------------------------|-------------------------------------------|-----|------|-------|

| I <sub>GSSF</sub> , I <sub>GSSR</sub> | $V_{GS}$ =20V, $V_{DS}$ =0                |     | 100  | nA    |

| IDSS                                  | $V_{DS}$ =50V, $V_{GS}$ =0                |     | 1.0  | μΑ    |

| IDSS                                  | $V_{DS}$ =50V, $V_{GS}$ =0, $T_J$ =125°C  |     | 500  | μΑ    |

| I <sub>D(ON)</sub>                    | $V_{GS}$ =10V, $V_{DS}$ =10V              | 500 |      | mA    |

| BVDSS                                 | $V_{GS}$ =0, $I_D$ =10 $\mu$ A            | 50  |      | V     |

| V <sub>GS(th)</sub>                   | $V_{DS}=V_{GS}$ , $I_{D}=250\mu A$        | 1.0 | 2.5  | V     |

| V <sub>DS(ON)</sub>                   | $V_{GS}$ =10V, $I_D$ =500mA               |     | 1.5  | V     |

| V <sub>DS(ON)</sub>                   | $V_{GS}$ =5.0V, $I_D$ =50mA               |     | 0.15 | V     |

| V <sub>SD</sub>                       | V <sub>GS</sub> =0, I <sub>S</sub> =115mA |     | 1.3  | V     |

|                                       |                                           |     |      |       |

Notes: (1) Ceramic or aluminum core PC Board with copper mounting pad area of 4.0mm<sup>2</sup>

(2) FR-4 Epoxy PC Board with copper mounting pad area of 4.0mm2 (3) FR-4 Epoxy PC Board with copper mounting pad area of 1.4mm<sup>2</sup>

# SURFACE MOUNT SILICON DUAL P-CHANNEL ENHANCEMENT-MODE MOSFETS

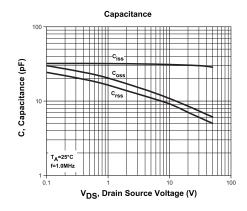

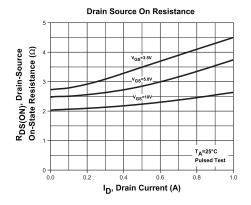

$\textbf{ELECTRICAL CHARACTERISTICS PER TRANSISTOR - Continued:} \ (T_A = 25^{\circ}\text{C unless otherwise noted})$ **TEST CONDITIONS** UNITS **SYMBOL** MIN TÝP MAX 2.5  $V_{GS}$ =10V,  $I_D$ =500mA Ω rDS(ON)  $V_{GS}$ =10V,  $I_D$ =500mA,  $T_J$ =125°C 4.0 Ω r<sub>DS(ON)</sub> 3.0 Ω  $V_{GS}$ =5.0V,  $I_D$ =50mA rDS(ON)  $V_{GS}$ =5.0V,  $I_D$ =50mA,  $T_J$ =125°C 5.0 Ω rDS(ON)  $V_{DS}$  =10V,  $I_{D}$ =200mA 200 mS g<sub>FS</sub>  $\mathsf{C}_{\mathsf{rss}}$  $V_{DS}$ =25V,  $V_{GS}$ =0, f=1.0MHz 7.0 рF  $\mathsf{C}_{\mathsf{iss}}$  $V_{DS}$ =25V,  $V_{GS}$ =0, f=1.0MHz 70 рF  $V_{DS}$ =25V,  $V_{GS}$ =0, f=1.0MHz рF 15 Coss  $V_{DS}$ =25V,  $V_{GS}$ =4.5V,  $I_{D}$ =100mA 0.72 nC Q<sub>g(tot)</sub>  $V_{DS}$ =25V,  $V_{GS}$ =4.5V,  $I_{D}$ =100mA 0.25 Qgs nC  $V_{DS}$ =25V,  $V_{GS}$ =4.5V,  $I_{D}$ =100mA 0.16 nC  $Q_{gd}$  $V_{DD}$ =30V,  $V_{GS}$ =10V,  $I_D$ =200mA ton, toff  $R_G=25\Omega$ ,  $R_I=150\Omega$ 20 ns

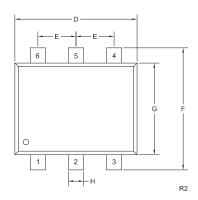

## **SOT-563 CASE - MECHANICAL OUTLINE**

| DIMENSIONS        |        |       |             |      |  |  |  |

|-------------------|--------|-------|-------------|------|--|--|--|

|                   | INCHES |       | MILLIMETERS |      |  |  |  |

| SYMBOL            | MIN    | MAX   | MIN         | MAX  |  |  |  |

| Α                 | 0.0027 | 0.007 | 0.07        | 0.18 |  |  |  |

| В                 | 0.008  |       | 0.20        |      |  |  |  |

| C                 | 0.017  | 0.024 | 0.45        | 0.60 |  |  |  |

| D                 | 0.059  | 0.067 | 1.50        | 1.70 |  |  |  |

| Е                 | 0.020  |       | 0.50        |      |  |  |  |

| F                 | 0.059  | 0.067 | 1.50        | 1.70 |  |  |  |

| G                 | 0.043  | 0.051 | 1.10        | 1.30 |  |  |  |

| H                 | 0.006  | 0.012 | 0.15        | 0.30 |  |  |  |

| SOT-563 (REV: R2) |        |       |             |      |  |  |  |

| G<br>H            |        | 0.012 | 0.15        | 0.30 |  |  |  |

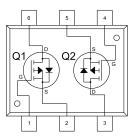

#### CMLDM8002A (USA Pinout) CMLDM8002AG\*

## **LEAD CODE:**

- 1) Gate Q1

- 2) Source Q1

- 3) Drain Q2

- 4) Gate Q2

- 5) Source Q2

- 6) Drain Q1

MARKING CODES:

CMLDM8002A: C08

CMLDM8002AG\*: CG8

\* Device is *Halogen Free* by design

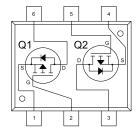

## CMLDM8002AJ (Japanese Pinout)

## LEAD CODE:

- 1) Source Q1

- 2) Gate Q1

- 3) Drain Q2

- 4) Source Q2

- 5) Gate Q2

- 6) Drain Q1

**MARKING CODE: CJ8**

SURFACE MOUNT SILICON DUAL P-CHANNEL ENHANCEMENT-MODE MOSFETS

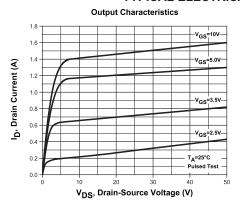

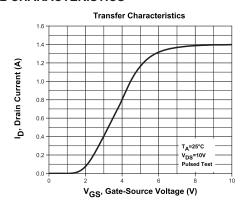

# TYPICAL ELECTRICAL CHARACTERISTICS

# SURFACE MOUNT SILICON DUAL P-CHANNEL ENHANCEMENT-MODE MOSFETS

#### **SERVICES**

- · Bonded Inventory

- · Custom Electrical Screening

- Custom Electrical Characteristic Curves

- SPICE Models

- Custom Packaging

- Package Base Options

- Custom Device Development/Multi Discrete Modules (MDM™)

- · Bare Die Available for Hybrid Applications

**LIMITATIONS AND DAMAGES DISCLAIMER:** In no event shall Central be liable for any collateral, indirect, punitive, incidental, consequential, or exemplary damages in connection with or arising out of a purchase order or contract or the use of products provided hereunder, regardless of whether Central has been advised of the possibility of such damages. Excluded damages shall include, but not be restricted to: cost of removal or reinstallation, rework, ancillary costs to the procurement of substitute products, loss of profits, loss of savings, loss of use, loss of data, or business interruption. No claim, suit, or action shall be brought against Central more than two (2) years after the related cause of action has occurred.

In no event shall Central's aggregate liability from any warranty, indemnity, or other obligation arising out of or in connection with a purchase order or contract, or any use of any Central product provided hereunder, exceed the total amount paid to Central for the specific products sold under a purchase order or contract with respect to which losses or damages are claimed. The existence of more than one (1) claim against the specific products sold to Buyer under a purchase order or contract shall not enlarge or extend this limit.

Buyer understands and agrees that the foregoing liability limitations are essential elements of a purchase order or contract and that in the absence of such limitations, the material and economic terms of the purchase order or contract would be substantially different.