## **Features & Benefits**

- Two independent Active Light measurement channels for proximity sensing and/or gesture recognition

- Integrated DC light cancellation circuitry

- Two logarithmic ambient light channels with two different sensitivities

- Minimum amount of external components

- Stand-by and sleep modes for low power consumption

- Integrated LED drivers

- Integrated battery voltage monitor

- Integrated LED temperature sensing circuitry

- Integrated 16bit ADC for high resolution A2D conversion

- Integrated temperature sensor

- Integrated watchdog timer

- Easy digital communication interface via SPI

- High input capacitance tolerant input current terminals

- High safety design by several diagnostic and monitoring functions

## **Ordering Information**

# Product Code Temperature Code Package Code Option Code MLX75031 R (-40°C to 105°C) LQ (QFN24 4x4) B MLX75031 C (0°C to 70°C) LQ (QFN24 4x4) B

## **General Description**

The MLX75031 Optical Gesture & Proximity Sensing IC actively controls up to 2 independent Active Light measurement channels. Each channel consists out of one or multiple LEDs, of any type, combined with one or more photodiodes, of any type. Additional Active Light channels can be added through multiplexing. Integrated DC light suppression makes the sensors highly tolerant to background light interference. Primary function is complemented with two integrated ambient light channels. Internal control logic, configurable user registers and SPI communication enable intuitive & programmable operation. Extra features include a watchdog timer, on-board temperature sensor and self-diagnostics are built-in to facilitate robust product design.

The digital output from the Active Light and ambient light channels can be used for proximity and ambient light detection. Gestures such as swipe, zoom, scroll can be recognized by software algorithms that can run on the customer's microcontroller. Reliable communication is assured via an SPI interface.

## Applications

- Robust Proximity Sensing

- Smart Touch Displays & Panels

- Simple Gesture Detection

- Driver-Passenger Discrimination

- Ambient Light Sensing & Display Dimming

## **Functional Diagram**

## **Table of Contents**

| Features & Benefits                                   | 1  |

|-------------------------------------------------------|----|

| Applications                                          | 1  |

| Functional Diagram                                    | 1  |

| Ordering Information                                  | 1  |

| General Description                                   | 1  |

| Table of Contents                                     |    |

| 1. Functional Block Diagram                           |    |

| 2. Device Overview                                    |    |

|                                                       |    |

| 3. Glossary of Terms                                  | 5  |

| 4. Absolute Maximum Ratings                           | 6  |

| 5. Pin Definitions & Descriptions                     | 7  |

| 6. General Electrical Specifications                  | 9  |

| 7. Sensor Interface Specific Specifications           | 10 |

| 8. Detailed General Description                       | 15 |

| 8.1 Active Light Channels A & B                       |    |

| 8.1.1 Transimpedance Amplifier (TIA)                  | 15 |

| 8.1.2 Active Light Channel DC Light Measurement       |    |

| 8.2 Ambient Light Sensor                              | 17 |

| 8.2.1 Normal Operation                                |    |

| 8.2.2 Logarithmic Transfer Function                   |    |

| 8.2.3 Calibration & Temperaure Compensaion            |    |

| 8.2.4 Response Time                                   |    |

| 8.2.5 Diagnostics Mode Operation                      |    |

| 8.3 Temperature Sensor                                |    |

| 8.4 Analog to Digital Conversion                      |    |

| 8.5 Output Stage                                      |    |

| 8.5.1 DAC                                             |    |

| 8.5.2 LED Driver                                      |    |

| 8.5.3 LED Forward Voltage Measurement                 |    |

| 8.5.4 Battery Supply Voltage Measurement & Monitoring |    |

| 8.6 Power-On Reset                                    |    |

| 8.7 Oscillator (RC)                                   |    |

| 8.8 ADC MUX                                           |    |

| 8.9 Vstab Analog +Bandgap<br>8.10 Digital Control     |    |

| 8.10 Digital Control                                  |    |

| 0.11 JF1                                              |    |

Datasheet

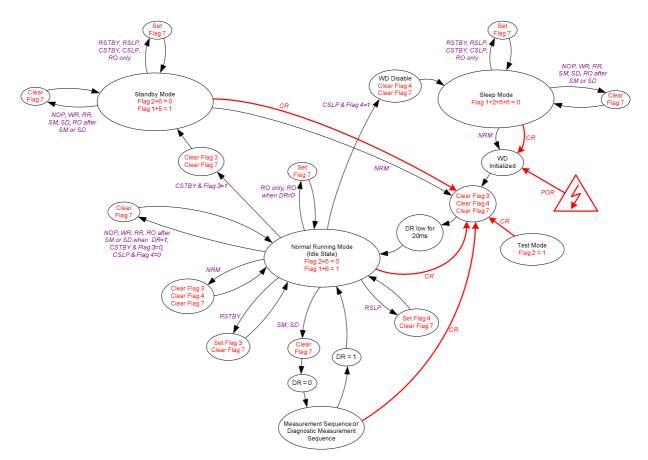

| 8.11.1 General Description of the SPI Interface                                         | 26         |

|-----------------------------------------------------------------------------------------|------------|

| 8.11.2 Operation Modes                                                                  | 29         |

| 8.11.3 Detailed Explanation of SPI Instruction Words                                    | 30         |

| 8.11.3.1 NOP – Idle Command                                                             |            |

| 8.11.3.2 CR – Chip Reset Command                                                        |            |

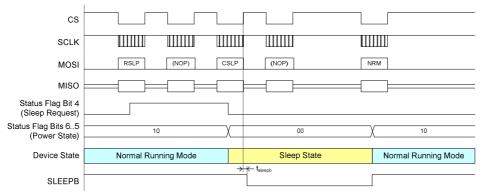

| 8.11.3.3 RSLP/CSLP – Request Sleep/Confirm Sleep                                        |            |

| 8.11.3.4 RSTBY/CSTBY - Request Standby/Confirm Standby                                  |            |

| 8.11.3.5 NRM – Normal Running Mode                                                      |            |

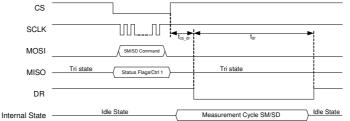

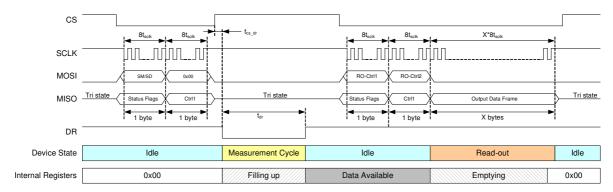

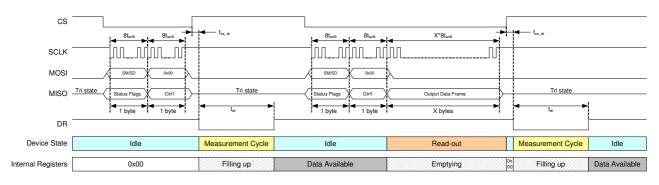

| 8.11.4 SM – Start Measurement                                                           |            |

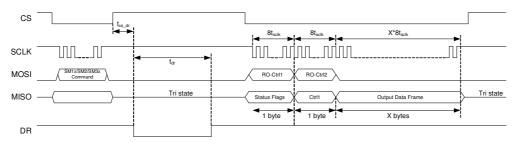

| 8.11.5 RO – Start Read-Out                                                              |            |

| 8.11.6 DM+RO - Start Measurement combined with Read-Out                                 |            |

| 8.11.7 WR/RR - Write/Read Register                                                      |            |

| 8.11.8 SD – Start Diagnostics                                                           |            |

| 8.12 Internal Status Flags                                                              |            |

| 8.13 User Registers Overview                                                            |            |

| 8.13.0 SetAna register                                                                  |            |

| 8.13.1 SetAH register                                                                   |            |

| 8.13.2 SetAL register                                                                   |            |

| 8.13.3 SetBH register                                                                   |            |

| 8.13.4 SetBL register                                                                   |            |

| 8.13.5 SetTP register                                                                   |            |

| 8.13.6 Err register                                                                     |            |

| 8.13.7 Rst register                                                                     |            |

| 8.13.8 Version register                                                                 |            |

| 8.10.9 Reserved register                                                                |            |

| 8.10.10 GainBuf register                                                                |            |

| 8.13.11/12 Calib1/Calib2 register                                                       |            |

| 8.13.13 EnChan register                                                                 |            |

| 8.13.14 Tamb register                                                                   |            |

| 8.13.15 SetPLS register                                                                 |            |

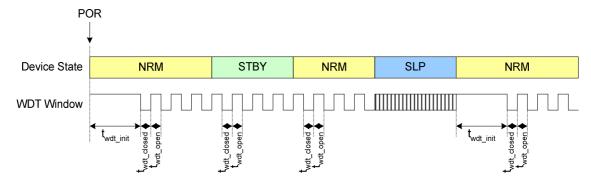

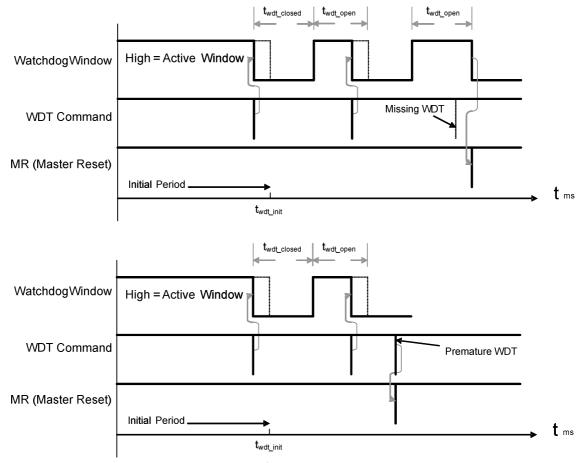

| 8.14 Window Watchdog Timer                                                              |            |

| 8.15 Reset Behaviour                                                                    |            |

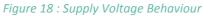

| 8.16 Supply Voltage Behaviour                                                           |            |

| 8.17 Wake-up from Sleep or Standby                                                      |            |

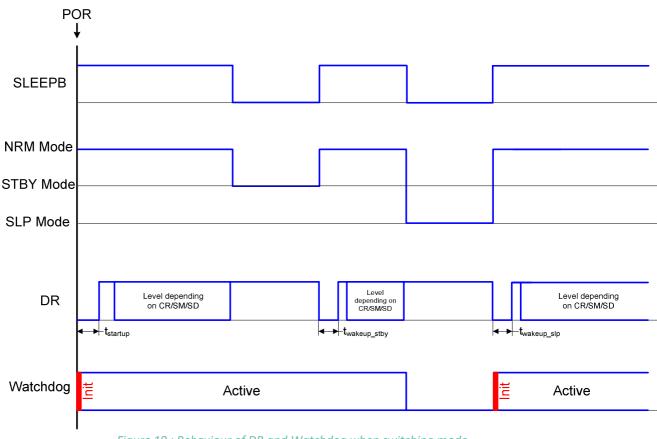

| 8.18 CRC Calculation                                                                    |            |

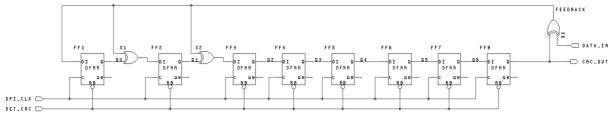

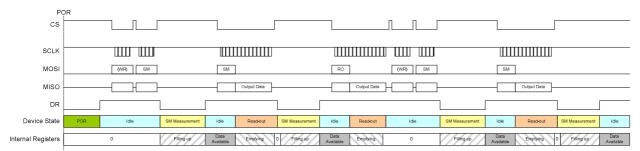

| 8.19 Global Timing Diagrams                                                             |            |

| 9. Application Information                                                              |            |

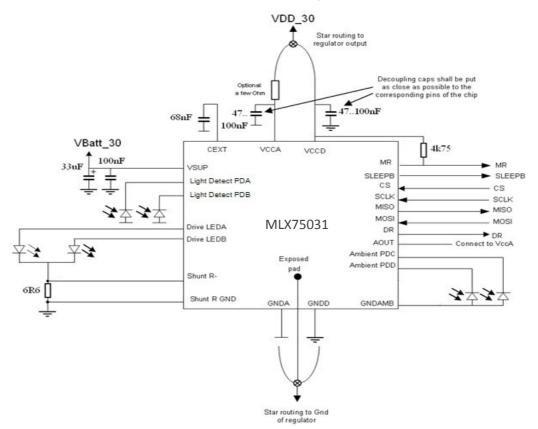

| 9.1 Application circuit                                                                 | 63         |

| 10. Standard information regarding manufacturability of Melexis products with different | <i>c</i> . |

| soldering processes                                                                     |            |

| 11. General Recommendations - ESD/EMC Precautions                                       |            |

| 12. Package Information                                                                 | 66         |

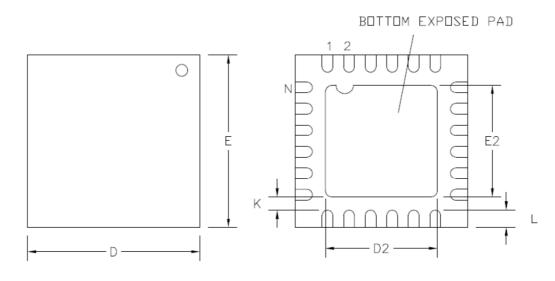

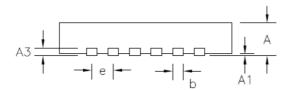

| 12.1 QFN 4x4 (24 pins): Quad Flat No-lead with exposed pad                              | 66         |

| 13. Disclaimer                                                                          | 67         |

Datasheet

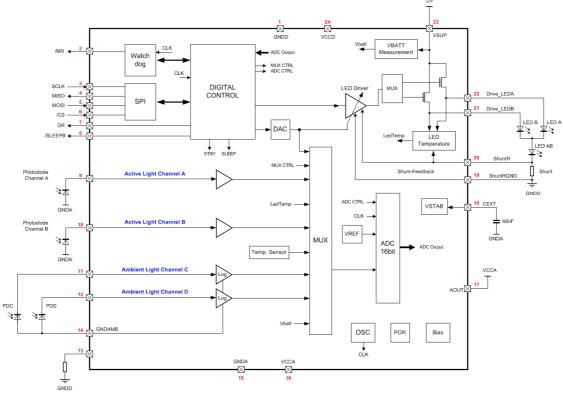

## **1. Functional Block Diagram**

Figure 1 : MLX75031 Functional Block Diagram

## **2. Device Overview**

The MLX75031 Optical Gesture & Proximity Sensing IC independently controls up to 2 Active Light channels. Both channels, A and B, have externally connected photodiodes. External LEDs can be driven up to 150 mA by the built-in LED driver. This current drive capability can also be used to drive a low cost bipolar transistor to increase the peak LED current. The chip synchronizes the pulsing of the LEDs and the exposure time of the Active Light channel photodiodes whereby ambient light and reflected LED light are detected separately. Any spurious light source is subtracted from the Active Light signal. See Section 8.1.

The two logarithmic current sensing channels C and D can be used to measure ambient light over a very wide intensity range. See Section 8.2 for more details.

As auxiliary features, the sensor integrates a watchdog timer, can measure its own temperature, the LED temperature, monitor voltage supply level and perform self diagnostics. All of this information is available via the SPI interface. See Section 8.14, 8.3, 8.5.3, 8.5.4 or 8.11.8 for detailed information.

The sensor features sleep and standby modes to save on current consumption. (Section 8.11.2) The SPI interface is used for data transfer and control of the IC. The timing characteristics are explained in Section 8.11.1 and the interface commands and programmable options in Section 8.11.3 & 8.13. The sensor is available in both consumer and automotive temperature grades.

Datasheet

## **3. Glossary of Terms**

| CRCCyclic Redundancy CheckCSChip SelectCSLPConfirm SleepCSTBYConfirm StandbyDACDigital to Analog ConverterDCDirect CurrentDRDevice ReadyEMCElectromagnetic CompatibilityGNDAGround for analog blocks of MLX75031GNDDGround for digital blocks of MLX75031IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Quital blocks of MLX75031MRMaster Quital blockMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORRead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest SleepRSTBYSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite RegisterUCMicrocontroller | CR    | Chip Reset                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------|

| CSLPConfirm SleepCSTBYConfirm StandbyDACDigital to Analog ConverterDCDirect CurrentDRDevice ReadyEMCElectromagnetic CompatibilityGNDAGround for analog blocks of MLX75031GNDDGround for digital blocks of MLX75031GNDDGround for digital blocks of MLX75031IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster Out Slave InMRMaster Qut Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORead-OutRRead RegisterRSLPRequest SleepRSTBYRequest SleepRSTBYSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                               | CRC   | Cyclic Redundancy Check               |

| CSTBYConfirm StandbyDACDigital to Analog ConverterDCDirect CurrentDRDevice ReadyEMCElectromagnetic CompatibilityGNDAGround for analog blocks of MLX75031GNDDGround for digital blocks of MLX75031GNDDGround for digital blocks of MLX75031IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest SleepRSTBYSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                             | CS    | Chip Select                           |

| DACDigital to Analog ConverterDCDirect CurrentDRDevice ReadyEMCElectromagnetic CompatibilityGNDAGround for analog blocks of MLX75031GNDDGround for digital blocks of MLX75031IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORRead-OutRCORead-OutRRRead RegisterRSLPRequest SleepRSTBYSignal-to-Noise RatioSPISignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                               | CSLP  | Confirm Sleep                         |

| DCDirect CurrentDRDevice ReadyEMCElectromagnetic CompatibilityGNDAGround for analog blocks of MLX75031GNDDGround for digital blocks of MLX75031IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORc-OscillatorRORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest SleepRSTBYSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                         | CSTBY | Confirm Standby                       |

| DRDevice ReadyEMCElectromagnetic CompatibilityGNDAGround for analog blocks of MLX75031GNDDGround for digital blocks of MLX75031IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Cut Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORRead-OutRCORead-OutRRRequest SleepRSTBYRequest SleepRSTBYSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                   | DAC   | Digital to Analog Converter           |

| EMCElectromagnetic CompatibilityGNDAGround for analog blocks of MLX75031GNDDGround for digital blocks of MLX75031IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORRead-OutRCORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                      | DC    | Direct Current                        |

| GNDAGround for analog blocks of MLX75031GNDDGround for digital blocks of MLX75031IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRequest SleepRSLPRequest SleepRSTBYSerial Peripheral InterfaceSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                           | DR    | Device Ready                          |

| GNDDGround for digital blocks of MLX75031IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRequest SleepRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                         | EMC   | Electromagnetic Compatibility         |

| IRInfraredLPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRequest SleepRSLPRequest SleepRSTBYSignal-to-Noise RatioSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                  | GNDA  | Ground for analog blocks of MLX75031  |

| LPFLow-pass filterLSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRRRead-OutRRRequest SleepRSTBYRequest SleepSSTBYSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                   | GNDD  | Ground for digital blocks of MLX75031 |

| LSBLeast Significant BitMISOMaster In Slave OutMOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRQRead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                              | IR    | Infrared                              |

| MISOMaster In Slave OutMOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRCRead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                               | LPF   | Low-pass filter                       |

| MOSIMaster Out Slave InMRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRQRead-OutRRRequest SleepRSLPRequest SleepRSTBYSignal-to-Noise RatioSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                      | LSB   | Least Significant Bit                 |

| MRMaster ResetMSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRequest SleepRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                             | MISO  | Master In Slave Out                   |

| MSBMost Significant BitMUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest SleepSCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                             | MOSI  | Master Out Slave In                   |

| MUXMultiplexerNOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MR    | Master Reset                          |

| NOPNo OperationNRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MSB   | Most Significant Bit                  |

| NRMNormal Running ModeOSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MUX   | Multiplexer                           |

| OSCOscillatorOTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NOP   | No Operation                          |

| OTROptical transfer ratioPORPower on resetRCORC-OscillatorRORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NRM   | Normal Running Mode                   |

| PORPower on resetRCORC-OscillatorRORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OSC   | Oscillator                            |

| RCORC-OscillatorRORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OTR   | Optical transfer ratio                |

| RORead-OutRRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | POR   | Power on reset                        |

| RRRead RegisterRSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RCO   | RC-Oscillator                         |

| RSLPRequest SleepRSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RO    | Read-Out                              |

| RSTBYRequest StandbySCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RR    | Read Register                         |

| SCLKSPI Shift ClockSMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RSLP  | Request Sleep                         |

| SMStart MeasurementSNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RSTBY | Request Standby                       |

| SNRSignal-to-Noise RatioSPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SCLK  | SPI Shift Clock                       |

| SPISerial Peripheral InterfaceTIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SM    | Start Measurement                     |

| TIATransimpedance AmplifierVCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SNR   | Signal-to-Noise Ratio                 |

| VCCASupply Voltage for the analog blocksVCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SPI   | Serial Peripheral Interface           |

| VCCDSupply Voltage for the digital blocksVSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TIA   | Transimpedance Amplifier              |

| VSENSEVoltage across the shunt resistorWDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VCCA  | Supply Voltage for the analog blocks  |

| WDTWatchdog TimerWRWrite Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VCCD  | Supply Voltage for the digital blocks |

| WR Write Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | -                                     |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WDT   | 0                                     |

| uC Microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | WR    | -                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | uC    | Microcontroller                       |

## **4. Absolute Maximum Ratings**

| Parameter                                                                       | Symbol     | Conditions                                                                                                                     | Min          | Мах                        | Units  |

|---------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------|--------|

| Supply Voltage range                                                            | VCCD, VCCA |                                                                                                                                | -0.3         | 5.0                        | V      |

| Battery Supply Voltage range                                                    | VSUP       | t<400ms, no<br>functionality, only<br>during load dump<br>t<2min, functional, not<br>guaranteed to be<br>within specifications | -0.3<br>-0.3 | 40<br>28                   | V<br>V |

| Voltage range Drive_LEDA and Drive_LEDB                                         |            |                                                                                                                                | -0.3         | 5.5                        | V      |

| Voltage range on all pins except<br>VCCD, VCCA, VSUP, Drive_LEDA,<br>Drive_LEDB |            |                                                                                                                                | -0.3         | V(VCCD)+0.3<br>V(VCCA)+0.3 | V      |

| Terminal current                                                                | Iterminal  | per bondpad                                                                                                                    | -20          | +20                        | mA     |

|                                                                                 | ILED       | Battery connection                                                                                                             | -20          | +155                       | mA     |

| Storage temperature                                                             | Tstg       |                                                                                                                                | -40          | +150                       | °C     |

| Junction temperature                                                            | Tj         |                                                                                                                                |              | +150                       | °C     |

| ESD capability of any pin<br>(Human Body Model)                                 | ESDHBM     | Human body model,<br>acc. to<br>AEC-Q100-002 Rev D                                                                             | -2           | +2                         | kV     |

| ESD capability of any pin<br>(Charge device model)                              | ESDCDM     | Charge device model<br>acc. to<br>AEC- Q100-011 Rev B                                                                          | -500         | +500                       | V      |

| Maximum latch–up free<br>current at any pin                                     | ILATCH     | JEDEC- Standard EIA /<br>JESD78                                                                                                | -100         | +100                       | mA     |

Table 1 : Absolute maximum ratings

<u>Note</u> : Exceeding the absolute maximum ratings may cause permanent damage.

Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

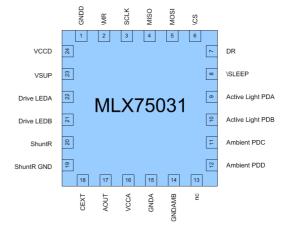

## **5. Pin Definitions & Descriptions**

| Pin № | Name Functional Schematic |      | Туре                                       | Function                                      |

|-------|---------------------------|------|--------------------------------------------|-----------------------------------------------|

| 1     | GNDD                      |      | Ground                                     | Ground                                        |

| 2     | \MR                       |      | Digital Open DActive<br>Light Output       | Master Reset                                  |

| 3     | SCLK                      |      | Digital Input with<br>pull-up              | SPI Shift Clock                               |

| 4     | MISO                      |      | Digital push-pull<br>Output with Tri-state | SPI Data Output                               |

| 5     | MOSI                      |      | Digital Input with<br>pull-down            | SPI Data Input                                |

| 6     | \CS                       |      | Digital Input with<br>pull-up              | Chip Select                                   |

| 7     | DR                        |      | Digital push-pull<br>Output                | Device Ready                                  |

| 8     | \SLEEPB                   |      | Digital push-pull<br>Output                | Sleep Detect                                  |

| 9     | Active Light PDA          |      | Analog Input                               | IR Photo Diode A                              |

| 10    | Active Light PDB          |      | Analog Input                               | IR Photo Diode B                              |

| 11    | Ambient Light PDC         |      | Analog Input                               | Ambient Light Photo Diode C                   |

| 12    | Ambient Light PDD         |      | Analog Input                               | Ambient Light Photo Diode D                   |

| 13    | n.c                       | vec. | Analog Input                               | Test Pin, connect to ground via<br>a resistor |

Datasheet

| 14 | GNDAMB     |                                              | Analog I/O    | Ground Ambient Light<br>Channels         |

|----|------------|----------------------------------------------|---------------|------------------------------------------|

| 15 | GNDA       |                                              | Ground        | Ground                                   |

| 16 | VCCA       |                                              | Supply        | Regulated Power Supply                   |

| 17 | AOUT       |                                              | Analog I/O    | Test Pin, connect to VCCA                |

| 18 | CEXT       |                                              | Analog Input  | External blocking Cap, connected to GNDA |

| 19 | ShuntRGND  |                                              | Analog Input  | Shunt resistor feedback to<br>Ground     |

| 20 | ShuntR     |                                              | Analog Input  | Shunt resistor feedback                  |

| 21 | Drive_LEDB | 740<br>• • • • • • • • • • • • • • • • • • • | Analog Output | IR LED Emitter B                         |

| 22 | Drive_LEDA | PAD                                          | Analog Output | IR LED Emitter A                         |

| 23 | VSUP       |                                              | Supply        | LED driver supply                        |

| 24 | VCCD       |                                              | Supply        | Regulated Power Supply                   |

Table 2 : Pin definitions and descriptions

<u>Note</u> : Pins of measurement channels that are not used, can be left unconnected.

However, this can lead to an error indicated by the corresponding error flags in the Error register.

## **6. General Electrical Specifications**

| Parameter                               | Symbol     | Test Conditions                                                               | Min    | Тур | Max        | Units    |

|-----------------------------------------|------------|-------------------------------------------------------------------------------|--------|-----|------------|----------|

| Supply voltage range                    | VDD        | VCCD and VCCA pin                                                             | 3.135  | 3.3 | 3.465      | V        |

| Supply current (active mode)            | IDD        | I(VCCD)+I(VCCA)<br>without photodiode DC<br>current                           |        |     | 6          | mA       |

| Supply current<br>(standby mode)        | IDD_STBY   | I(VCCD)+I(VCCA)                                                               |        |     | 350        | uA       |

| Supply current (sleep mode)             | IDD_SLP    | I(VCCD)+I(VCCA)<br>without SPI<br>communication                               |        |     | 30         | uA       |

| Battery supply voltage range            | VSUP       | VSUP pin                                                                      | 6      |     | 18         | V        |

| Battery supply current<br>(active mode) | IVSUP      | I(VSUP) with<br>Active Light pulses<br>I(VSUP) without<br>Active Light pulses | 0<br>0 |     | 155<br>0.1 | mA<br>mA |

| Battery supply current (standby mode)   | IVSUP_STBY | I(VSUP)                                                                       | 0      |     | 10         | uA       |

| Battery supply current (sleep mode)     | IVSUP_SLP  | I(VSUP)                                                                       | 0      |     | 10         | uA       |

| Operation Temperature                   | TA         |                                                                               | -40    |     | 105        | °C       |

Table 3 : Electrical specifications

## 7. Sensor Interface Specific Specifications

The following characteristics are valid over the full temperature range of  $T_A = -40$  °C to +105 °C and a supply range of VSUP = 6.18V and VCCD = VCCA = 3.135..3.465V unless otherwise noted.

| Active Light Channels (Photodiode A & B)                                        |                                      |                                                                                                                                                                      |         |            |        |          |  |  |

|---------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--------|----------|--|--|

| Parameter                                                                       | Symbol                               | Test Conditions                                                                                                                                                      | Min     | Тур        | Max    | Units    |  |  |

| Optical transfer ratio                                                          | $OTR = \frac{I_{LED}}{I_{PD}}$       |                                                                                                                                                                      | 30      |            | 12000  |          |  |  |

| DC sunlight current in the photodiode                                           | I <sub>sun</sub>                     |                                                                                                                                                                      | 0       |            | 900    | μΑ       |  |  |

| Fast full scale transition at $I_{\mbox{sunmax}}$                               | t <sub>sunrise</sub>                 |                                                                                                                                                                      | 3.5     |            |        | ms       |  |  |

| Min. relative active light<br>modulation<br>(referred to received IR signal)    | $\frac{\Delta I_{PD\_\min}}{I_{PD}}$ | <ul> <li>- 20 μs LED pulse</li> <li>- PD pulsed current</li> <li>≥ 20μA, - 25°C</li> <li>- DC sun constant</li> <li>- response per</li> <li>channel 2.5ms</li> </ul> |         | 1          | 5 (*)  | %        |  |  |

| Dynamic range of active light events (referred to received IR signal)           | $\Delta I_{\text{ActiveLight}}$      |                                                                                                                                                                      |         |            | 80     | %        |  |  |

| Active light repetition time<br>Acive light measurement<br>channel A, channel B | $t_{rep\_activelight}$               |                                                                                                                                                                      |         | 2.5<br>2.5 |        | ms<br>ms |  |  |

| LED pulse duration range                                                        | t <sub>o</sub>                       | selectable via register                                                                                                                                              | 15-8%   |            | 30+8%  | μs       |  |  |

| Max. input capacitance PDA & PDB                                                | C <sub>PDA</sub> , C <sub>PDB</sub>  |                                                                                                                                                                      |         |            | 80     | рF       |  |  |

| DC light measurement range                                                      | I <sub>DC</sub> range                |                                                                                                                                                                      | 0       |            | 900    | μΑ       |  |  |

| DC light measurement offset                                                     | I <sub>DC</sub> offset               | I <sub>DC</sub> = 0uA & VDD=3.3V                                                                                                                                     | 1360    | 1960       | 2460   | LSB      |  |  |

| DC light measurement slope                                                      | I <sub>DC</sub> sens                 |                                                                                                                                                                      | 28      | 35         | 44     | LSB/µA   |  |  |

| DC light measurement inearity error                                             |                                      | I <sub>DC</sub> range: OuA -><br>900uA                                                                                                                               |         | 5          | 8      | %        |  |  |

| DC light measurement word length                                                |                                      |                                                                                                                                                                      |         | 16         |        | Bit      |  |  |

| DC light measurement noise                                                      |                                      | for averaging of<br>8 measurements                                                                                                                                   |         | 3          |        | Bit      |  |  |

|                                                                                 | Error o                              | ondition Err_TIA                                                                                                                                                     |         |            |        |          |  |  |

| Critical error detected                                                         | on TIA outpu                         | t, if TIA output outside                                                                                                                                             | 1.1V+/- | (0.65      | 0.75V) |          |  |  |

Table 4 : Active Light Channels Specification

(\*) The 5% is really worst case condition, i.e. with OTR = 30 and Rshunt = 10hm, this condition is not realistic and should be avoided in a the application

Datasheet

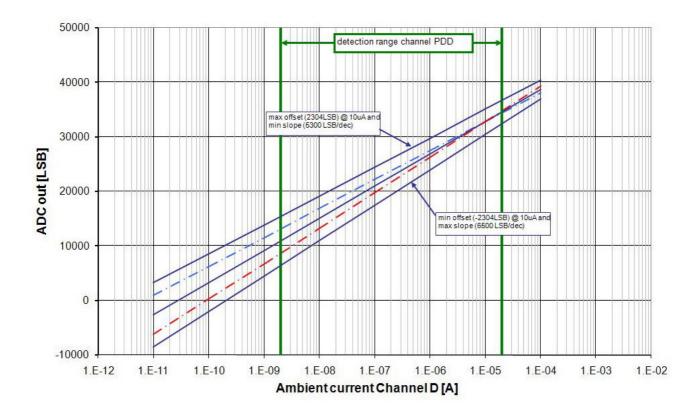

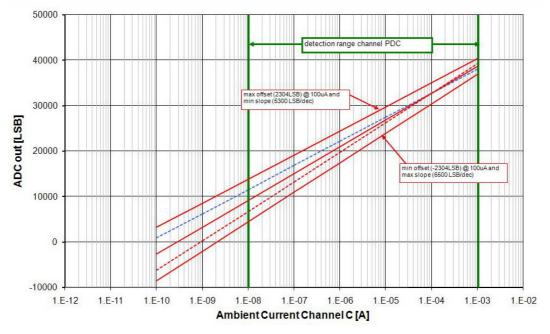

#### Table 5 : Ambient Light Channels Specifications

| Ambient Light Channels (Photodiode C & D)       |              |                                                                                                 |           |       |            |         |  |  |  |

|-------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------|-----------|-------|------------|---------|--|--|--|

| Parameter                                       | Symbol       | Test Conditions                                                                                 | Min       | Тур   | Max        | Units   |  |  |  |

| Input current range<br>for detector C           | Iambc        | Detector C                                                                                      | 0.01      |       | 1040       | uA      |  |  |  |

| Input current<br>threshold level                | lambc_detect | Detector C                                                                                      | 333       |       |            | nA      |  |  |  |

| Input capacity on<br>ambient PDC                | Cambc        | at 1V, Detector C                                                                               |           |       | 1          | nF      |  |  |  |

| Input current range<br>for detector D           | lambd        | Detector D                                                                                      | 0.002     |       | 20         | uA      |  |  |  |

| Input current<br>threshold level                | lambd_detect | Detector D                                                                                      | 22        |       |            | nA      |  |  |  |

| Input capacity on<br>ambient PDD                | Cambd        | at 1V, Detector D                                                                               |           |       | 100        | pF      |  |  |  |

| Transfer function<br>logarithmic                | Vamb         | See                                                                                             | Section 8 | 3.2.2 |            |         |  |  |  |

| Output Ambient<br>Channel C                     |              | At VDD=3.3V, lin=100uA                                                                          | 30464     | 32768 | 37376      | LSB     |  |  |  |

| Output Ambient<br>Channel D                     |              | At VDD=3.3V, lin=10uA                                                                           | 30464     | 32768 | 37376      | LSB     |  |  |  |

| Slope Ambient Channel C                         |              | At VDD=3.3V and 105°C                                                                           | 5300      | 5900  | 6500       | LSB/dec |  |  |  |

| Slope Ambient Channel D                         |              | At VDD=3.3V and 105°C                                                                           | 5300      | 5900  | 6500       | LSB/dec |  |  |  |

| Ambient Channels<br>Linearity Error             |              | for lin $\geq$ lambx_detect                                                                     |           | 3     | 5          | %       |  |  |  |

| Ambient light word length                       |              |                                                                                                 |           | 16    |            | bits    |  |  |  |

| Ambient light<br>channel accuracy               |              | for averaging of 16<br>measurements                                                             |           | 13    |            | bits    |  |  |  |

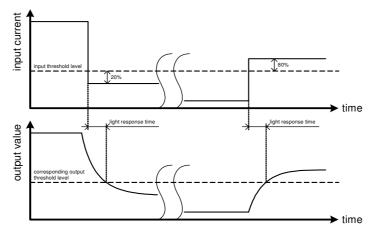

| Ambient light<br>response time                  |              | See Section 8.2.4 for a<br>detailed explanation of<br>this parameter.<br>for lin ≥ lambx_detect |           |       | 3          | ms      |  |  |  |

| Ambient light<br>measurement<br>repetition rate |              |                                                                                                 | 10        |       |            | ms      |  |  |  |

|                                                 |              | or condition Err_Amb                                                                            |           |       |            |         |  |  |  |

| _                                               |              | on mode of one ambient cha<br>CCA for each of the differen                                      |           |       | out of rai | nge     |  |  |  |

Datasheet

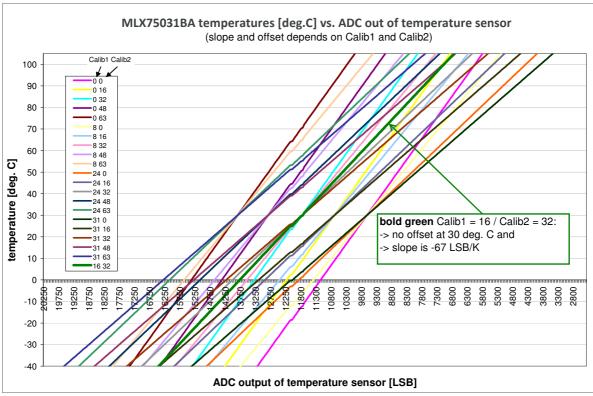

#### Table 6 : Temperature Sensor Specification

| Die Temperature Sensor             |                    |                                          |      |      |       |       |  |  |  |

|------------------------------------|--------------------|------------------------------------------|------|------|-------|-------|--|--|--|

| Parameter                          | Symbol             | Test Conditions                          | Min  | Тур  | Max   | Units |  |  |  |

| Temp. sensor range                 | ϑ                  |                                          | -40  |      | 105   | °C    |  |  |  |

| Temp. sensor transfer function (*) | Vϑ                 | At VDD=3.3V                              | -82  | -67  | -51   | LSB/K |  |  |  |

| Temp. sensor output                | V@85°C             | At VDD=3.3V and full<br>Calib 1/2 ranges | 5990 | 8096 | 10203 | LSB   |  |  |  |

| Temp. sensor error                 | verror@30℃         | At VDD=3.3V                              |      |      | ±3    | °C    |  |  |  |

| Temp. response time                | tresp_ $\vartheta$ |                                          |      |      | 1     | S     |  |  |  |

| Temp. sensor word length           |                    |                                          |      | 16   |       | bits  |  |  |  |

| Temp. sensor noise                 |                    | for averaging of 16<br>measurements      |      | 3    |       | bits  |  |  |  |

(\*) This value will be stored in the Calib1 Register.

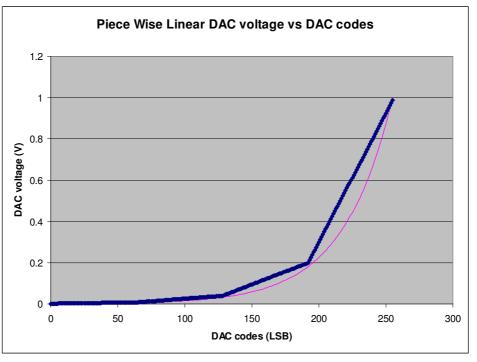

| LED Driver                                                                                                                                                     |                                                                          |                                                                                  |     |     |     |       |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|-----|-----|-------|--|

| Parameter                                                                                                                                                      | Symbol                                                                   | Test Conditions                                                                  | Min | Тур | Max | Units |  |

| LED pulse current                                                                                                                                              |                                                                          | Shunt=1 Ω                                                                        | 1   |     | 150 | mA    |  |

| Shunt resistor values                                                                                                                                          |                                                                          | The minimum VSUP voltage is<br>affected by the drop across the<br>shunt resistor | 1   |     | 6.6 | Ohm   |  |

| Shunt voltage                                                                                                                                                  |                                                                          |                                                                                  | 1   |     | 993 | mV    |  |

| Rising and falling time                                                                                                                                        |                                                                          | 1tau settling time,<br>programmable via Rise<1:0>                                |     | 17  |     | us    |  |

| DC offset level                                                                                                                                                |                                                                          | Shunt bias voltage before transmitting the current pulse                         |     | 1   |     | mV    |  |

| Time before pulseTdc_pulseBiasing time of the LED driver<br>(Shunt voltage = DC offset level)<br>before pulse transmission.<br>See Section 8.13.0 for details. |                                                                          |                                                                                  | 200 |     | us  |       |  |

| Error condition Err_Drv                                                                                                                                        |                                                                          |                                                                                  |     |     |     |       |  |

| Err_                                                                                                                                                           | Err_Drv difference between Vdac and Vsense. Detection level larger 200mV |                                                                                  |     |     |     |       |  |

Table 7 : LED Driver specification

Datasheet

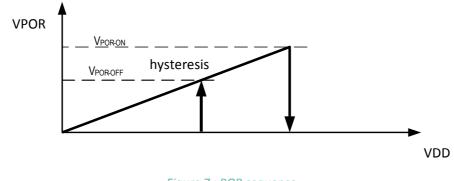

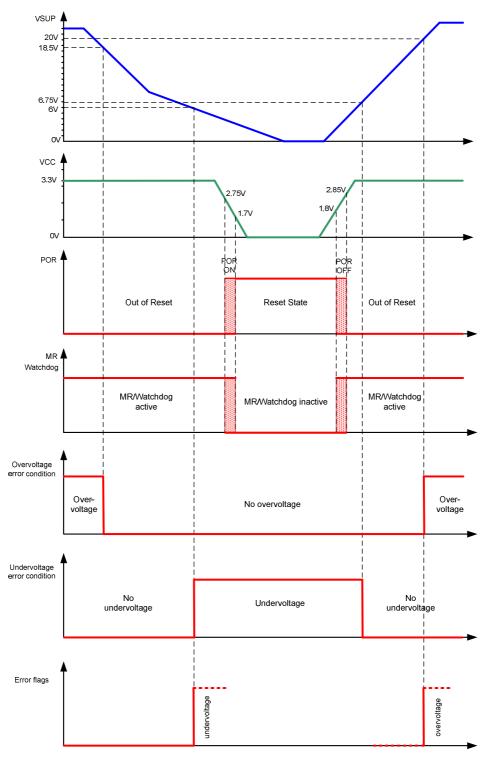

#### Table 8 : Power on Reset specification

| POR                       |          |                 |     |     |      |       |  |

|---------------------------|----------|-----------------|-----|-----|------|-------|--|

| Parameter                 | Symbol   | Test Conditions | Min | Тур | Max  | Units |  |

| POR off threshold voltage | VPOR-ON  |                 | 1.8 |     | 2.85 | V     |  |

| POR on threshold voltage  | VPOR-OFF |                 | 1.7 |     | 2.75 | V     |  |

| POR hysteresis voltage    | VHYS     |                 |     | 150 |      | mV    |  |

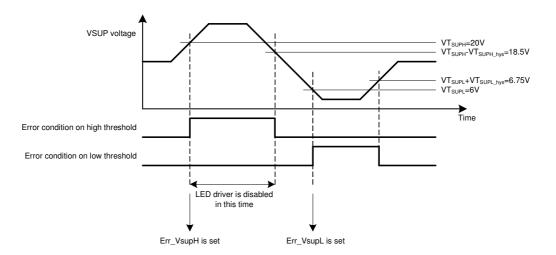

| VSup Voltage Monitor        |              |                                     |     |     |       |       |  |

|-----------------------------|--------------|-------------------------------------|-----|-----|-------|-------|--|

| Parameter                   | Symbol       | Test Conditions                     | Min | Тур | Max   | Units |  |

| VSUP Measurement Range      |              |                                     | 5   |     | 20    | V     |  |

| VSup Low threshold voltage  | VTSUPL       | Default VSUPLOW<1:0>                |     | 6   |       | V     |  |

| VSup Low hysteresis         | VTSUPL_hys   |                                     |     | 1   |       | V     |  |

| VSup High threshold voltage | VTSUPH       |                                     |     | 20  |       | V     |  |

| VSup High hysteresis        | VTSUPH_hys   |                                     |     | 1.8 |       | V     |  |

| Gain error                  | VTgain_err   |                                     |     |     | +/-2  | %     |  |

| Offset error                | VToffset_err |                                     |     |     | +/-50 | LSB   |  |

| Voltage Monitor Noise       |              | for averaging of 16<br>measurements |     | 3   |       | bits  |  |

Table 9 : VSup Voltage Monitor specification

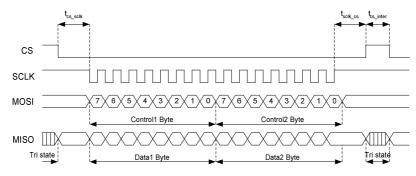

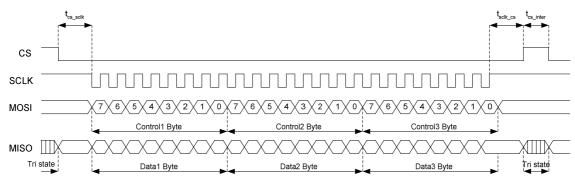

|                                           | SPI    |                                                                             |        |      |        |       |  |

|-------------------------------------------|--------|-----------------------------------------------------------------------------|--------|------|--------|-------|--|

| Parameter                                 | Symbol | Test Conditions                                                             | Min    | Тур  | Max    | Units |  |

| SPI word length                           |        |                                                                             |        |      | 8      | bit   |  |

| High-level input voltage                  | VIH    |                                                                             | 0.7VDD |      | VDD    | V     |  |

| Low-level input voltage                   | VIL    |                                                                             | 0      |      | 0.3VDD | V     |  |

| Hysteresis on digital inputs              | VHYST  |                                                                             |        | 0.28 |        | V     |  |

| High output voltage<br>(not on pin MR)    | VOH    | CL=30pF                                                                     | 0.8VDD |      | VDD    | V     |  |

| Low output voltage<br>(not on pin MR)     | VOL    | CL=30pF                                                                     | 0      |      | 0.2VDD | V     |  |