# RENESAS

## ISL1550 Single Port, VDSL2 Differential Line Driver

## DATASHEET

FN6795 Rev 0.00 March 16, 2012

The ISL1550 is a dual operational amplifier intended to be used as a differential line driver. ISL1550's high bandwidth and low distortion performance enables the support of VDSL2 8b, 17a and 30a modem applications.

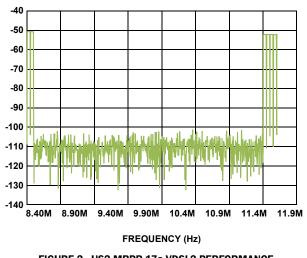

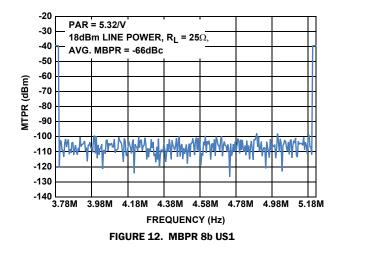

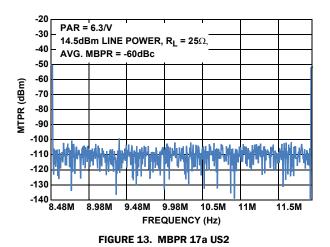

This device features a high current drive capability of  $\pm 750$ mA required to drive large voltage peaks into heavy loads. In Central Office (CO) applications, the driver achieves a typical Missing Band Power Ratio (MBPR) of -66dBc in VDSL2 8b upstream (US) 1 band and MBPR's of -61dBc and -60dBc in VDSL2 17a US1 and US2 respectively.

The ISL1550 has two bias current control pins (C0, C1) to allow for four power settings (disable, low, medium, high). The VDSL modem DSP configures the line driver's power setting based on the desired mode of operation. The line driver operates on a nominal single +12V or a dual ±6V supplies with bias current in active mode between 15mA to 32mA, depending on its power setting. The ISL1550's gain setting is configurable at the application level by setting the Rf and Rg resistor values. The surge current handling of ISL1550 has been enhanced to allow ITU-T K.20 and GR1089 compliance with minimal external surge protection circuitry.

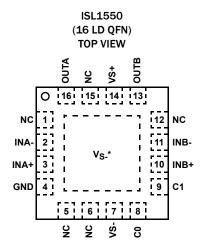

The ISL1550 is available in the thermally-enhanced, Pb-free RoHS compliant 16 Ld QFN package and is specified for operation over the full -40  $^{\circ}$ C to +85  $^{\circ}$ C temperature range.

### **Features**

- 20dBm output power capability

- + Drives up to  $\pm 750$ mA from a +12V supply

- + 18V<sub>P-P</sub> differential output drive into 20 $\Omega$

- -89dBc typical driver output distortion at full output at 200kHz,  $12V_{P\!\!\!\!\!P}$  differential

- -61dBc US1, -60dBc US2 avg. MBPR 17a

- Supply range: ±4.0V to ±6.6V, +8.0V to +13.2V

- Thermal shutdown

- K.20, GR-1089 Surge Robustness Validated

## **Applications**

• VDSL2 Profiles: 8MHz, 17MHz, and 30MHz

## **Related Literature**

• AN1325 "Choosing and Using Bypass Capacitors"

#### TABLE 1. ALTERNATE SOLUTIONS

| PART #   | NOMINAL ±V <sub>CC</sub><br>(V) | BANDWIDTH<br>(MHz) | APPLICATIONS |

|----------|---------------------------------|--------------------|--------------|

| ISL1557  | ±6,+12                          | 200                | VDSL2        |

| ISL1539A | ±12,+24                         | 240                | VDSL2        |

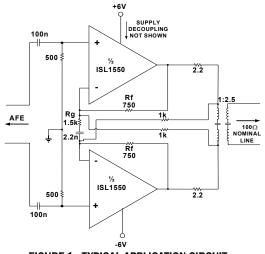

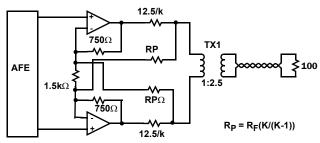

FIGURE 1. TYPICAL APPLICATION CIRCUIT

## **Connection Diagram**

## **Pin Configuration**

\*THERMAL PAD CONNECTS TO MOST NEGATIVE SUPPLY

## **Pin Descriptions**

| PIN NUMBER | PIN NAME | FUNCTION                        |

|------------|----------|---------------------------------|

| 1          | NC       | No Connect                      |

| 2          | INA-     | Amplifier A Inverting Input     |

| 3          | INA+     | Amplifier A Non-Inverting Input |

| 4          | GND      | Ground                          |

| 5          | NC       | No Connect                      |

| 6          | NC       | No Connect                      |

| 7          | VS-      | Negative Supply Voltage         |

| 8          | CO       | Digital Control Pin             |

| 9          | C1       | Digital Control Pin             |

| 10         | INB+     | Amplifier B Non-Inverting Input |

| 11         | INB-     | Amplifier B Inverting Input     |

| 12         | NC       | No Connect                      |

| 13         | OUTB     | Amplifier B Output              |

| 14         | VS+      | Positive Supply Voltage         |

| 15         | NC       | No Connect                      |

| 16         | OUTA     | Amplifier A Output              |

## **Ordering Information**

| PART<br>NUMBER<br>(Notes 2, 3) | PART<br>MARKING  | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|--------------------------------|------------------|--------------------|----------------------|----------------|

| ISL1550IRZ                     | 155 OIRZ         | -40 to +85         | 16 Ld QFN            | L16.4x4H       |

| ISL1550IRZ-T7 (Note 1)         | 155 OIRZ         | -40 to +85         | 16 Ld QFN            | L16.4x4H       |

| ISL1550IRZ-T13 (Note 1)        | 155 0IRZ         | -40 to +85         | 16 Ld QFN            | L16.4x4H       |

| ISL1550IRZ-EVALZ               | Evaluation Board |                    |                      | ·              |

NOTES:

1. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for ISL1550. For more information on MSL please see tech brief TB363.

### Absolute Maximum Ratings ( $T_A = +25^{\circ}C$ )

| V <sub>S</sub> + Voltage to GND0.3V to +13.2V                         |

|-----------------------------------------------------------------------|

| Driver V <sub>IN</sub> + VoltageGND to +V <sub>S</sub>                |

| C <sub>0</sub> , C <sub>1</sub> Voltage to GND0.3V to +V <sub>S</sub> |

| Current into any Input 8mA                                            |

| Continuous Output Current for Long Term Reliability50mA               |

| ESD Rating                                                            |

| Human Body Model (Tested per JESD22-A114F)                            |

| Machine Model (Tested per JESD22-A115C)                               |

| Charge Device Model (Tested per JESD22-C101E)1.5kV                    |

|                                                                       |

#### **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|-------------------------------------------|----------------------|------------------------|

| 16 Ld QFN Package (Notes 4, 5)            | 53                   | 16.5                   |

| Maximum Junction Temperature (Plastic Pac | kage)                | +150°C                 |

| Storage Temperature Range                 | 4                    | 40°C to +150°C         |

| Pb-Free Reflow Profile                    |                      | . see link below       |

| http://www.intersil.com/pbfree/Pb-FreeRe  | eflow.asp            |                        |

#### **Operating Conditions**

| Ambient Temperature Range  | 40°C to +85°C  |

|----------------------------|----------------|

| Junction Temperature Range | 40°C to +150°C |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>TB379</u>.

- 5. For  $\theta_{\text{JC}}$  the "case temp" location is the center of the exposed metal pad on the package underside.

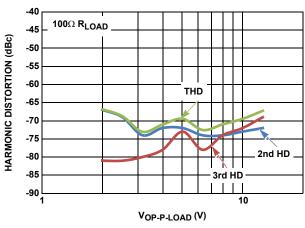

### **Electrical Specifications** $V_S = \pm 6V$ , see Figure 1, $T_A = +25$ °C, unless otherwise specified.

| PARAMETER                                           | DESCRIPTION                                         | CONDITIONS                                                            | MIN<br>(Note 6) | ТҮР  | MAX<br>(Note 6) | UNIT  |

|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|-----------------|------|-----------------|-------|

| AC PERFORMANCE                                      |                                                     |                                                                       |                 |      | 1               |       |

| BW                                                  | -3dB Bandwidth                                      | See Figure 1                                                          |                 | 105  |                 | MHz   |

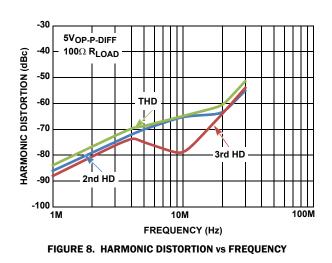

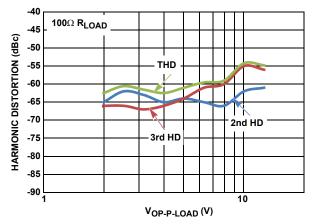

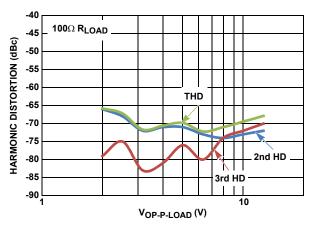

| THD                                                 | Total Harmonic Distortion, Differential             | f = 200kHz, $V_0$ = 12 $V_{P-P \text{ output}}$ , $R_L$ = 20 $\Omega$ |                 | -89  |                 | dBc   |

|                                                     |                                                     | f = 4MHz, $V_0$ = 12 $V_{P-P \text{ output}}$ , $R_L$ = 100Ω          |                 | -67  |                 | dBc   |

|                                                     |                                                     | f = 10MHz, $V_0$ = 12 $V_{P-P \text{ output}}$ , $R_L$ = 100 $\Omega$ |                 | -61  |                 | dBc   |

| SR                                                  | Slew Rate (20% to 80%)                              | V <sub>OUT</sub> from -6V to +6V (differential)                       | 1500            | 2400 |                 | V/µs  |

| DC PERFORMANCE                                      |                                                     |                                                                       |                 | L    |                 |       |

| V <sub>OS_CM</sub>                                  | Input Offset Voltage Common Mode                    |                                                                       | -45             |      | +45             | mV    |

| V <sub>OS_DM</sub>                                  | Input Offset Voltage Differential Mode              |                                                                       | -7.5            |      | +7.5            | mV    |

| INPUT CHARACTERI                                    | STICS                                               |                                                                       |                 | I    |                 |       |

| I <sub>B</sub> +                                    | Non-Inverting Input Bias Current                    |                                                                       | -7.0            | -3.0 | +7.0            | μA    |

| IB- DM                                              | Inverting Input Bias Current Differential<br>Mode   |                                                                       | -45             | ±7   | +45             | μA    |

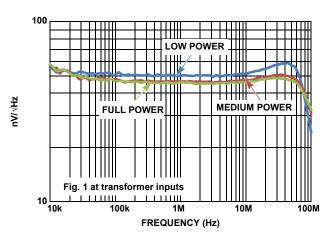

| e <sub>0</sub>                                      | Differential Output Noise                           | See Figure 1 [at transformer input]                                   |                 | 45   |                 | nV√Hz |

| OUTPUT CHARACTE                                     | RISTICS                                             |                                                                       |                 | 1    | 1               |       |

| V <sub>OUT</sub>                                    | Loaded Output Swing (single-ended)                  | $V_S = \pm 6V, R_{L \text{ DIFF}} = 100\Omega$                        | ±4.7            | ±5.0 |                 | V     |

|                                                     |                                                     | $V_S = \pm 6V$ , $R_{L DIFF} = 20\Omega$                              |                 | ±4.5 |                 | V     |

| SUPPLY                                              |                                                     |                                                                       |                 | I    |                 |       |

| +V <sub>S</sub>                                     | Supply Voltage                                      | Single supply (-V <sub>S</sub> = GND)                                 | 8.0             | 12   | 13.2            | V     |

| I <sub>S</sub> + (Full Bias)                        | Positive Supply Current                             | All outputs at OV, $C_0 = C_1 = OV$                                   | 27              | 32   | 37              | mA    |

| I <sub>S</sub> + (Medium Bias)                      | Positive Supply Current                             | All outputs at OV, $C_0 = 5V$ , $C_1 = 0V$                            | 19              | 23   | 26              | mA    |

| I <sub>S</sub> + (Low Bias)                         | Positive Supply Current                             | All outputs at OV, $C_0 = OV$ , $C_1 = 5V$                            | 12              | 15   | 18              | mA    |

| I <sub>S</sub> + (Power down)                       | Positive Supply Current                             | All outputs at OV, $C_0 = C_1 = 5V$                                   | 1.3             | 1.6  | 2.5             | mA    |

| I <sub>INH</sub> , C <sub>O</sub> or C <sub>1</sub> | C <sub>0</sub> , C <sub>1</sub> Input Current, High | C <sub>0</sub> , C <sub>1</sub> = 6V                                  | 100             | 165  | 224             | μA    |

| I <sub>INL</sub> , C <sub>0</sub> or C <sub>1</sub> | C <sub>0</sub> , C <sub>1</sub> Input Current, Low  | C <sub>0</sub> , C <sub>1</sub> = 0V                                  | -1.5            | -1.0 | +1.5            | μA    |

| V <sub>INH</sub> , C <sub>O</sub> or C <sub>1</sub> | C <sub>0</sub> , C <sub>1</sub> Input Voltage, High |                                                                       | 2.0             |      |                 | v     |

| V <sub>INL</sub> , C <sub>0</sub> or C <sub>1</sub> | C <sub>0</sub> , C <sub>1</sub> Input Voltage, Low  |                                                                       |                 |      | 0.8             | V     |

NOTE:

6. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

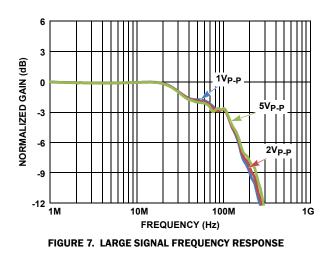

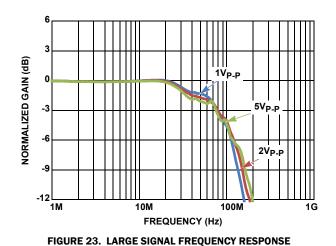

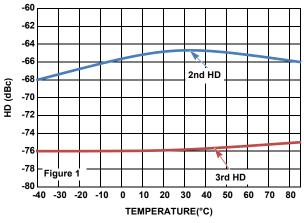

# Typical Performance Curves noted.

$V_{CC} = \pm 6V$ , See Figure 1,  $T_A = +25 \degree C$ , C0 = C1 = 0V (Full power), Unless otherwise

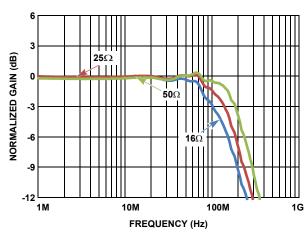

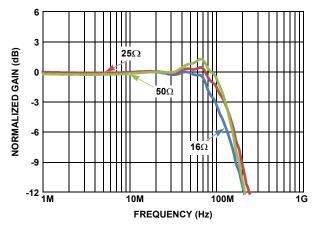

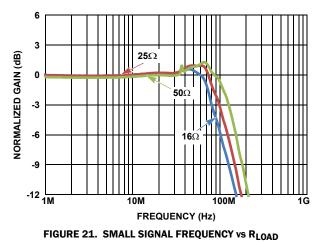

FIGURE 4. SMALL SIGNAL FREQUENCY RESPONSE vs RLOAD

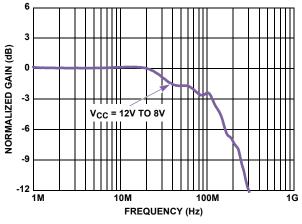

FIGURE 6. SMALL SIGNAL BANDWIDTH vs SUPPLY VOLTAGE

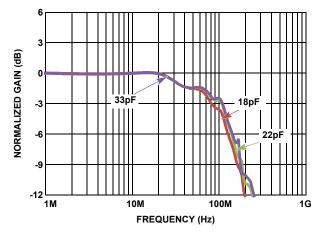

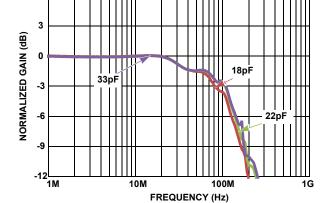

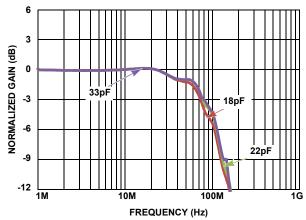

FIGURE 5. SMALL SIGNAL FREQUENCY RESPONSE vs CLOAD

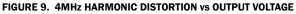

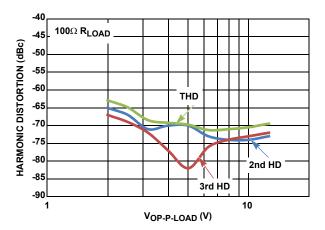

### **Typical Performance Curves**

$V_{CC} = \pm 6V$ , See Figure 1,  $T_A = +25 \degree C$ , CO = C1 = OV (Full power), Unless otherwise

noted. (Continued)

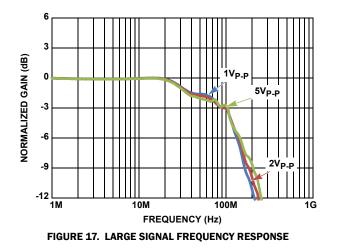

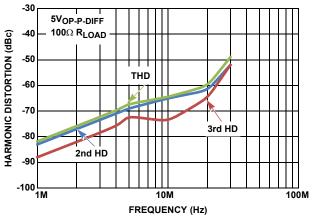

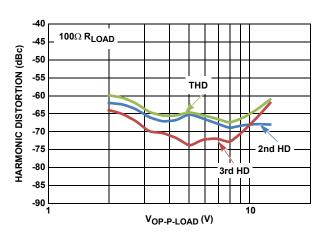

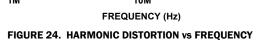

FIGURE 10. 10MHz HARMONIC DISTORTION vs OUTPUT VOLTAGE

FIGURE 11. 20MHz HARMONIC DISTORTION vs OUTPUT VOLTAGE

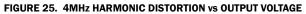

## **Typical Performance Curves**

otherwise noted.

FIGURE 15. SMALL SIGNAL FREQUENCY RESPONSE vs  $\mathsf{R}_{\mathsf{LOAD}}$

$V_{CC} = \pm 6V$ , See Figure 1,  $T_A = +25$  °C, C0 = 3.3V, C1 = 0V (Medium power), Unless

6

FIGURE 16. SMALL SIGNAL FREQUENCY RESPONSE vs CLOAD

FIGURE 19. 4MHz HARMONIC DISTORTION vs OUTPUT VOLTAGE

FIGURE 18. HARMONIC DISTORTION vs FREQUENCY

FN6795 Rev 0.00 March 16, 2012

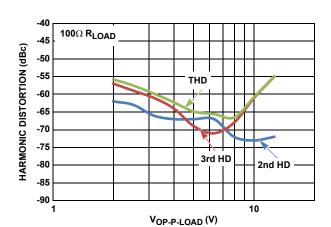

## **Typical Performance Curves**

otherwise noted.

$V_{CC} = \pm 6V$ , See Figure 1,  $T_A = +25 \degree C$ , C0 = 0V, C1 = 3.3V (Low power), unless

FIGURE 26. 10MHz HARMONIC DISTORTION vs OUTPUT VOLTAGE

-30 5V<sub>OP-P-DIFF</sub>

RENESAS

#### ISL1550 **Typical Performance Curves** VCC = ±6V, See Figure 3, Gain = 5V/V (Differential), Rf = 1.5k $\Omega$ , R<sub>LOAD</sub> = 100 $\Omega$ , $T_A = +25$ °C, CO and C1 Varied, unless otherwise noted. -30 13.5 V<sub>S</sub> = ±6V $V_S = \pm 6V$ 12.5 -40 AV = 5 **RF = 750**Ω 11.5 -50 **RF = 750**Ω **R<sub>G</sub> = 374**Ω 10.5 $R_{LOAD}$ = 100 $\Omega$ G R<sub>L</sub> = 100Ω DIFF -60 DIFFERENTIAL V<sub>IN</sub> = 1V<sub>P-P</sub> DIFF GAIN (dB) 9.5 -70 FULL POWER 8.5 I I TTTI -80 7.5 MEDIUM POWER -90 +++++6.5 -100 LOW POWER 5.5 -110 4.5 -120 3.5 100k 100M 100k 1M 10M 1G 1M 10M 100M FREQUENCY (Hz) FREQUENCY (Hz) FIGURE 27. OFF-ISOLATION FIGURE 28. DIFFERENTIAL OUTPUT IMPEDANCE T = 0s T = 1.60000µs C0, C1 PIN 2V/DIV CO, C1 PIN 2V/DIV Output Sine Wave OUTPUT PIN n **OUTPUT PIN** 300ns Ch1 2.00 V Ch2 5.00 V M 100ns A Ch1 L 3.12 V Ch2 5.00 V M 40.0µs A Ch1 J 3.12 V Ch1 2.00 V FIGURE 29. POWER ON FIGURE 30. POWER OFF 40 Ū T = 242.800ns FULL POWER(mA) 35 QUIESCENT CURRENT (mA) 30 OUTPUT A 25 2V/DIV MEDIUM POWER 20 OUTPUT B 15 LOW POWER 10 5 Figure 1 0 -40 -30 -20 -10 10 20 30 50 60 70 80 Ó 40 Ch1 2.00 V Ch2 2.00 V M 100ns A Ch1 J 40.0mV

FIGURE 31. OVERDRIVE RECOVERY

**TEMPERATURE (°C)**

FIGURE 32. QUIESCENT CURRENT vs TEMPERATURE

### **Typical Performance Curves** $vcc = T_A = +25^{\circ}C$ , C0 and C1 Varied, unless otherwise noted. (Continued) VCC = ±6V, See Figure 3, Gain = 5V/V (Differential), Rf = 1.5k\Omega, R<sub>LOAD</sub> = 100\Omega,

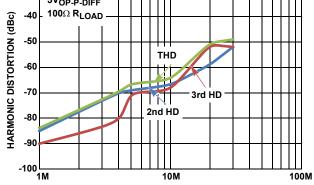

FIGURE 33. 200kHz DISTORTION vs TEMPERATURE

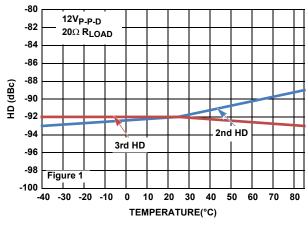

FIGURE 34. 4MHz DISTORTION vs TEMPERATURE

## **Applications Information**

#### **Product Description**

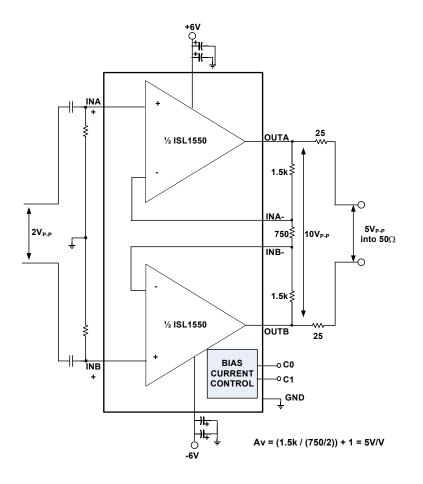

The ISL1550 is a dual operational amplifier designed for line driving in DMT VDSL2 8MHz, 12MHz, 17MHz and 30MHz bandplans solutions. It is a current mode feedback amplifier with low distortion drawing moderately low supply current. Due to the current feedback architecture, the ISL1550 closed-loop 3dB bandwidth is dependent on the value of the feedback resistor. First, the desired bandwidth is selected by choosing the feedback resistor,  $R_{\rm F}$ , and then the gain is set by picking the gain resistor,  $R_{\rm G}$  (Figure 3).

#### **VDSL CO Applications**

The ISL1550 is designed as a VDSL line driver for CO. At an output current of  $\pm 450$ mA, the typical supply voltage headroom is 1.5V on each side of the differential output.

The average line power requirement for the VDSL CO application is 20dBm (100mW) into a 100 $\Omega$  line. The average line voltage is 3.16V<sub>RMS</sub>. The VDSL DMT peak-to-average ratio (crest factor) of 5.3 implies peak voltage of 16.8V<sub>P</sub> into the line. Using a differential drive configuration and transformer coupling with standard back termination, a transformer ratio of 1:2.5 is selected. The active termination technique provides better power efficiency by reducing the backmatch resistor by a factor of K = 5. Positive feedback resistors, RP, can be sized to make the effective backmatch impedance larger. The circuit configuration is shown in Figure 35.

FIGURE 35. CIRCUIT CONFIGURATION

# Power Supply Bypassing and Printed Circuit Board Layout

As with any high frequency device, good printed circuit board layout is necessary for optimum performance. Ground plane construction is highly recommended. Lead lengths should be as short as possible (below 0.25"). The power supply pins must be well bypassed to reduce the risk of oscillation. A 4.7µF tantalum capacitor in parallel with a 0.1µF ceramic capacitor is adequate for each supply pin. During power-up, it is necessary to limit the slew rate of the rising power supply to less than 1V/µs. If the power supply rising time is undetermined, a series  $10\Omega$  resistor on the power supply line before the decoupling caps can be used to ensure the proper power supply rise time.

For good AC performance, parasitic capacitances should be kept to a minimum, especially at the inverting input. This implies keeping the ground plane away from this pin. Carbon or metal film resistors are acceptable, while use of wire-wound resistors should be avoided because of their parasitic inductance. Similarly, capacitors should be low inductance for best performance.

#### **Capacitance at the Inverting Input**

Due to the topology of the current feedback amplifier, stray capacitance at the inverting input will affect the AC and transient performance of the ISL1550 when operating in the non-inverting configuration.

#### **Feedback Resistor Values**

The ISL1550 has been designed and specified with R<sub>F</sub> =  $1.5k\Omega$  for A<sub>V</sub> = +5 (Figure 3). As is the case with all current feedback amplifiers, wider bandwidth at the expense of slight peaking, can be obtained by reducing the value of the feedback resistor. Inversely, larger values of the feedback resistor will cause rolloff to occur at a lower frequency.

#### **Quiescent Current vs Temperature**

The ISL1550 was designed to slightly increase quiescent current with temperature to maintain good distortion performance at high temperatures. Refer to "Typical Performance Curves" beginning on page 5.

#### **Supply Voltage Range**

The ISL1550 has been designed to operate with supply voltages from  $\pm 4.0V$  to  $\pm 6.6V$  nominal. Optimum bandwidth, slew rate, and video characteristics are obtained at higher supply voltages.

#### **Single Supply Operation**

If a single supply is desired, values from +8.0V to +13.2V nominal can be used as long as the input common mode range is not exceeded. When using a single supply, be sure to either,

- 1. DC bias the inputs at an appropriate common mode voltage and AC-couple the signal, or

- 2. Ensure the driving signal is within the common mode range of the ISL1550.

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

|   | DATE           | REVISION | CHANGE           |

|---|----------------|----------|------------------|

|   | March 16, 2012 | FN6795.0 | Initial release. |

| L |                |          | k                |

## **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <u>www.intersil.com/products</u> for a complete list of Intersil product families.

For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: <u>ISL1550</u>

To report errors or suggestions for this datasheet, please go to: www.intersil.com/askourstaff

© Copyright Intersil Americas LLC 2012. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <u>www.intersil.com/en/support/qualandreliability.html</u>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN6795 Rev 0.00 March 16, 2012

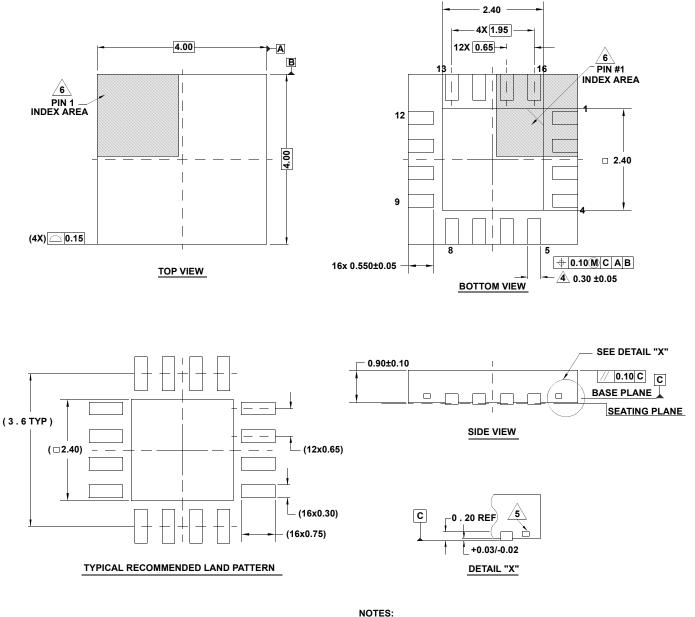

## Package Outline Drawing

#### L16.4x4H

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 0, 1/12

1. Dimensions are in millimeters.

- Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm\,0.05$

- <u>/4.</u> Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

$\sqrt{5.}$  Tiebar shown (if present) is a non-functional feature.

6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.