#### 1. Introduction

With the new UHF transmitter ATA5749 Atmel® offers an optimized solution for unidirectional access systems. The transmitter is primarily designed for automotive applications such as Tire Pressure Monitoring Systems (TPMS), Remote Key-less Entry (RKE) and Passive Entry Go (PEG). In addition the ATA5749 can also be used for any access and remote control system in industrial applications. This application note provides technical background information which helps to quickly understand and apply the device.

# 2. General Description

The ATA5749 is an integrated fractional-N-PLL transmitter that operates in the Industrial Scientific and Medical (ISM) frequency band. The IC transmits signals with Amplitude Shift Keying (ASK) and Frequency Shift Keying (FSK) modulation with a data rate of up to 40 kBits/s in Manchester coding. Several features can be set by using the SPI interface, for example, the operating frequency in the range of 300 MHz to 450 MHz and the transmit power in the range of –0.5 dBm to +12.5 dBm. To ensure maximum battery lifetime the transmitter features low current consumption, for example, just 7.3 mA at 5.5 dBm output power (typical). Due to the small-sized TSSOP10 package only few external elements are needed to realize an end application with minimum board space consumption (please refer to Figure 3-1 on page 3).

# **UHF Transmitter IC ATA5749**

# **Application Note**

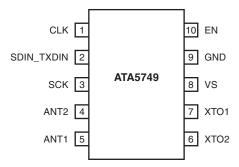

Figure 2-1 shows the Pinning of the ATA5749, whereas the pin description is listed in Table 2-1.

Figure 2-1. ATA5749 Pinning

Table 2-1.ATA5749 Pin Description

| Pin | Symbol     | Function                                |

|-----|------------|-----------------------------------------|

| 1   | CLK        | CLK output                              |

| 2   | SDIN_TXDIN | Serial bus data input and TX data input |

| 3   | SCK        | Serial bus clock input                  |

| 4   | ANT2       | Antenna interface                       |

| 5   | ANT1       | Antenna interface                       |

| 6   | XTO2       | Crystal/C <sub>LOAD2</sub> connection   |

| 7   | XTO1       | Crystal/C <sub>LOAD1</sub> connection   |

| 8   | VS         | Supply Input                            |

| 9   | GND        | Supply GND                              |

| 10  | EN         | Enable input                            |

# 3. Circuit Block Descriptions

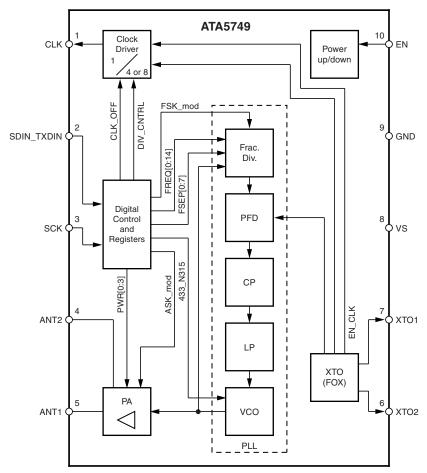

This section describes the individual circuit blocks, providing more detailed information than in the ATA5749 datasheet. Figure 3-1 illustrates the transmitter's system block diagram.

Figure 3-1. System Block Diagram

## 3.1 Crystal Oscillator (XTO)

This block is based on the Pierce oscillator circuit with an amplitude regulation. The definition of the crystal oscillator's features and functionality is fixed. To start the crystal oscillator, pin EN must be set. The amplitude detector, which is implemented in the crystal oscillator block, monitors the oscillation amplitude. If the defined amplitude is reached, an internal signal bit XTO\_RDY will be set (see Figure 3-1) and the clock output (pin CLK) will be switched on.

This method has two benefits. First it guarantees a stable PLL reference frequency and an optimum clock frequency accuracy. Second, the parasitic coupling from the clock output signal to the crystal oscillator pins (XTO1 and XTO2) - which may disturb the start-up process of the crystal oscillator - will not be critical since the clock output signal will be generated only if the oscillation amplitude is high enough. Nevertheless, the board layout must be designed properly to minimize parasitic coupling between the CMOS output of the pin CLK and the crystal oscillator.

The time period between the activation of the IC (EN='HIGH') and the output of the clock signal is defined as the crystal oscillator's start-up time, which mainly depends on the crystal's motional capacitance (Cm). The typical value of 200  $\mu$ s can be obtained using a crystal with a motional capacitance (Cm) of 4 fF and a shunt capacitance (C0) of 1.5 pF. The higher the motional capacitance (Cm) the faster the crystal oscillator's start-up.

The ATA5749's crystal oscillator features a high oscillation margin (negative resistance) of typically  $R_{\rm XTO12\_START} > 1500$ . This helps to reduce the failure rates caused by sleeping crystal phenomena. The external load capacitors must be selected so that the XTO oscillates on the loaded resonance frequency of the specified crystal. To ensure the specified start-up behavior and a low XTO current consumption it is recommended to choose a crystal with a load capacitance (CL) of 9 pF.

# 3.2 Fractional-N PLL (Phase-locked Loop)

The Table 5-1 and Table 5-2 in Section 5. "ANNEX" on page 27 show the ATA5749's register configuration. The configuration of FREQ[0:14], FSEP[0:7] and S434\_N315 influences the frequency generated by the PLL block (please refer to Figure 3-1 on page 3). The ATA5749 provides two different VCO tuning ranges: 300 MHz to 368 MHz, and 367 MHz to 450 MHz. As can be seen in Table 3-1, the bit S434\_N315 in the register sets the VCO's RC oscillator and the fractional divider of the PLL.

**Table 3-1.** Bit *S434\_N315* Configuration

| S434_N315 | ATA5749 Frequency Range |

|-----------|-------------------------|

| LOW       | 300 MHz to 368 MHz      |

| HIGH      | 367 MHz to 450 MHz      |

In case of FSK modulation the carrier frequency will be internally modulated by FSK\_mod Signal, which is identical to the available signal on the pin SDIN\_TXDIN.

Table 3-2 shows the calculation of the RF output frequency based on the setting of FREQ[0:14], FSEP[0:7], *S434\_N315* and the value of FSK\_mod (*SDIN\_TXDIN*).

**Table 3-2.** RF Output Frequencies' Calculation Based on the Register Setting

|                                | S434_N315 = 'LOW'                                                                         | S434_N315 = 'HIGH'                                                                              |

|--------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| f <sub>TX_FSK_mod='LOW'</sub>  | $\left[24 + \frac{(FREQ + 0.5)}{16384}\right] \times f_{XTO}$                             | $\left[32.5 + \frac{(FREQ + 0.5)}{16384}\right] \times f_{XTO}$                                 |

| f <sub>TX_FSK_mod='HIGH</sub>  | $\left[24 + \frac{(FREQ + FSEP + 0.5)}{16384}\right] \times f_{XTO}$                      | $[32.5 + \frac{(FREQ + FSEP + 0.5)}{16384}] \times f_{XTO}$                                     |

| f <sub>DEV_FSK</sub>           | $\frac{\text{FSEP}}{32768} \times f_{\text{XTO}}$                                         | $\frac{\text{FSEP}}{32768} \times f_{\text{XTO}}$                                               |

| f <sub>RF</sub> <sup>(1)</sup> | $\left[24 + \frac{\left(\frac{FREQ + FSEP}{2} + 0.5\right)}{16384}\right] \times f_{XTO}$ | $ \left[ 32.5 + \frac{\left(\frac{FREQ + FSEP}{2} + 0.5\right)}{16384} \right] \times f_{XTO} $ |

Note: 1. The ASK carrier is corrected by adding FSEP/2 to FREQ for ASK transmission. If FSEP is an odd number, the FSEP/2 value is rounded to the lower next integer value, therefore, the ASK center frequency may differ to the FSK center frequency by 396 Hz.

#### **Definition:**

- In ASK modulation f<sub>RF</sub> is the center frequency of the transmitted signal.

- In FSK modulation f<sub>RF</sub> is the virtual carrier that is defined using the Mark and Space Frequencies,

$$f_{RF} = \frac{f_{Mark} + f_{Space}}{2}$$

- F<sub>Space</sub> = f<sub>TX FSK mod='0'</sub>

- f<sub>Mark</sub> = f<sub>TX FSK mod='1'</sub>

The values to be used for FSEP are in the range of 1 to 255. Based on a crystal frequency ( $f_{XTAL} = f_{XTO}$ ) of 13.0 MHz the frequency deviation ( $f_{DEV\_FSK}$ ) is programmable within a range of ±396 Hz to ±101.16 kHz with a resolution of ±396 Hz. For example, an FSK spectrum with a frequency deviation ( $f_{DEV\_FSK}$ ) of ±39.6 kHz can be generated using FSEP = 100 and  $f_{XTO} = 13.0$  MHz as reference.

For proper system operation, the frequency setting of the fractional N-PLL must be well considered due to the fractional spurious emissions. With regard to the ATA5749, the FREQ values setting must be chosen in a range of 2500 to 22000.

The device can be operated at two standard operating frequencies in the ISM band, 315 MHz and 433.92 MHz, using one single crystal frequency of 13.0 MHz (please refer to Table 3-2).

**Table 3-3.** Calculation of the Operating Frequencies in the 315 MHz and the 433.92 MHz Band Using 13.0 MHz Crystal Frequency

| 315.0 MHz - Transmitter Application                                                                      | 433.92 MHz - Transmitter Application                                                |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| FREQ[0:14] = 3730<br>FSEP[0:7] = 100<br>S434_N315 = 0                                                    | FREQ[0:14] = 14342<br>FSEP[0:7] = 100<br>S434_N315 = 1                              |

| > f <sub>RF</sub> = 24.2307434 × f <sub>XTO</sub> = 24.2307434 × 13 MHz> f <sub>RF</sub> = 314.99966 MHz | > $f_{RF}$ = 33.3784485 × $f_{XTO}$ = 33.3784485 × 13 MHz> $f_{RF}$ = 433.91983 MHz |

| The frequency resolution is 793 Hz                                                                       |                                                                                     |

The locking time of the PLL is defined, as follows

$$T_{PLL} = \frac{1280}{f_{XTO}}$$

The crystal frequency ( $f_{XTAL} = f_{XTO}$ ) of 13.0 MHz results in a PLL locking time ( $T_{PLL}$ ) of 98.46 µs. The PLL starts with the clock output activation (please refer to Figure 3-8 on page 15). The power amplifier and thus the data transmission can be started 98.46 µs after the clock output activation. The typical start-up time of the crystal oscillator (XTO) is 200 µs (DT<sub>XTO</sub>). The reduced start-up time of PLL plus XTO (approximately 300 µs) allows a short time delay between switching the transmitter on (EN = "HIGH") and the beginning of the data transmission, which is important when designing a transmitter with low current consumption.

Notes: 1. The PLL will be started when the internal signal XTO\_RDY is set and the programming of the 32-bit register (see Figure 3-8 on page 15 and Figure 3-9 on page 16) has been completed successfully.

In case the register programming by the microprocessor takes longer than the XTO start-up time (DTXTO), the PLL will start after the last bit has been programmed into the 32-bit register (see Figure 3-9 on page 16 and Figure 5-1 on page 28).

This programmable feature using the control bit *FREQ[0:14]* enables the correction of crystal tolerances and the application of frequency channeling.

# 3.3 Clock Output Driver (CLK\_DRV)

6

The bit *DIV\_CNTRL* determines the clock frequency generated by the transmitter. If bit *DIV\_CNTRL* is set, the generated clock frequency is the crystal oscillator's frequency (f<sub>XTO</sub>) divided by 4, whereas the division factor for the clock frequency is 8 if bit *DIV\_CNTRL* has been cleared. Using a 13.0-MHz crystal, the clock frequencies of 1.625 MHz or 3.25 MHz will be generated according to the setting of DIV\_CNTRL. The generated clock signal (pin CLK) is CMOS compatible and can drive load capacitances of up to 20 pF at a frequency of 1.625 MHz, and up to 10 pF at a frequency of 3.25 MHz.

Bit CLK\_ON controls the activation of both the clock output and the internal signal XTO\_RDY (please refer to Section 3.1 "Crystal Oscillator (XTO)" on page 4). If CLK\_ON is cleared the IC does not generate any clock signal at pin CLK, resulting in a lower current consumption. During power-down mode the pin CLK remains on low level. The low level on the pin CLK will change if the amplitude of the crystal oscillator is sufficiently large (XTO\_RDY is set). Hence the clock output and the internal XTO\_RDY signal are always synchronized. With this synchronization spikes during the activation of the clock output will be avoided, because the clock signal always starts with a full period.

The transmitter ATA5749 offers a clock-only mode where only the crystal oscillator and the clock driver are active. Setting the CLK\_Only bit will cause the transmitter to switch to clock-only mode.

## 3.4 Power Amplifier (PA)

To activate the power amplifier, the PLL needs to be locked and the internal signal XTO\_RDY must be set (please refer to Section 3.2 "Fractional-N PLL (Phase-locked Loop)" on page 4). The PA's output power can be programmed in a range of -0.5 dBm to 12.5 dBm by setting the PWR[0:3] bits in the register (please refer to Table 3-1 on page 4 and Table 3-2 on page 5). In ASK mode the transmitter frequency will be corrected to the center of the FSK, see Table 3-2 on page 5 and the PA will be modulated by the internal ASK\_mod signal, which is equal to the data (signal) on the pin SDIN TXDIN.

#### 3.4.1 Class-C Power Amplifier

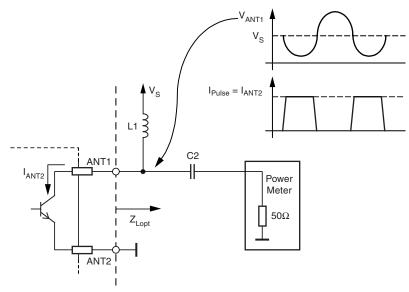

The power amplifier is designed as a class-C amplifier. This kind of circuit delivers current pulses at the open-collector output which is almost independent from the load impedance, supply voltage and temperature. Another advantage of this architecture is a relatively simple matching to an antenna or to a  $50\Omega$  load. Figure 3-2 on page 8 shows how the class-C PA basically works.

The required output power can be chosen by setting the PWR[0:3] bits in the register (see Table 5-1 and Table 5-2 on page 27). This setting adjusts the peak value of the current pulses (I<sub>Pulse</sub>), delivered by the PA. That way the current consumption for pre-specified RF output power can be optimized to obtain the best possible PA efficiency.

During production the peak value of  $I_{Pulse}$  is calibrated to guarantee that variations due to production tolerances do not exceed  $\pm 10\%$ . This results in a tight tolerance of the PA current and thus of the ATA5749's output power. For each power setting an output power variation of  $\pm 1.5$  dB (including production tolerance) can be expected.

Figure 3-2. Operating Principle of Class-C PA

Since the PA's efficiency depends on the PA's load impedance, the matching elements must be optimized for every power setting to achieve the optimum load impedance ( $Z_{LOPT}$ ), see Figure 3-2 on page 8.

#### For example:

Load impedance  $Z_{LOPT} = (180+j300)\Omega$  at 315 MHz operating frequency

Power supply  $V_S = 3V$

Output power setting PWR[0:3]=8, which defines the output power of 5.5 dBm at  $50\Omega$

In this example, the PA's current consumption will be typically 3.6 mA and thus 7.3 mA for the entire transmitter. This results in an power amplifier efficiency (PAE) of 32%.

In case of an optimum load, an efficiency of  $\eta_A$  = 26% can be achieved with a 1.2-dBm power setting (PWR[0:3]=4), and  $\eta_A$  = 36% with a maximum output power setting of 12.5 dBm (PWR[0:3]=15).

The load impedance is defined as the impedance of the matching network, or more specifically, the ratio between the RF voltage peak and the RF current peak at the power amplifier output (see Figure 3-2 on page 8). If the optimum load impedance ( $Z_{LOPT}$ ) is obtained, the RF voltage amplitude will almost reach the supply voltage (please refer to Figure 3-2 on page 8). The  $50\Omega$  load matching method will be addressed in more detail in Section 3.4.2 "Output Matching to  $50\Omega$  Load" on page 9.

The ATA5749 is designed as a class-C power amplifier since this architecture provides significant advantages compared to other architectures such a class-E power amplifier, for example. Thanks to the class-C architecture the PA output is almost independent from the load impedance variation, which could increase the supply current and hence overload the battery of the transmitter module. In worst case, if the battery capacity is already at its limit, the transmitter's supply volt-age drops drastically due to overload, which leads to a malfunction of the module. Please note that a hand approaching the antenna's area may also cause load impedance variations.

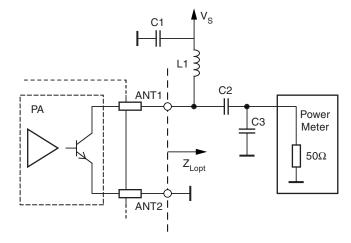

#### 3.4.2 Output Matching to $50\Omega$ Load

Figure 3-3 illustrates the basic measurement assembly of the output power matching to a  $50\Omega$  load. Table 3-1 on page 4 and Table 3-2 on page 5 show the power setting, the optimum achieved output power and the optimized values of the matching elements for each programmed output power. The matching element terms refer to Figure 3-3.

Figure 3-3. Principle of the Output Power Measurement Assembly

As mentioned in the last section an optimum power can be achieved if the peak amplitude value of the RF output voltage is close to the power supply ( $V_S$ ). To this end, a low resistive path from the collector output of the PA to  $V_S$  supplies the necessary DC current. The inductor L1 is used as RF choke, connecting pin Ant1 to VS. To prevent coupling between the PA and the supply voltage, which may disturb PLL operation, the 1-nF decoupling capacitor C1 (X7R) must be placed as close as possible to the RF chokes and the power amplifier.

In case of an optimum load impedance ( $Z_{Lopt}$ ), the PA's output capacitance (approximately 0.7 pF) and the board's parasitic capacitance will be absorbed, and the PA delivers the RF current to a pure resistive load ( $R_{load}$ ). In practice, the  $R_{load}$  value can be measured between pins ANT1 and ANT2. During  $R_{load}$  measurement the ATA5749 must be kept in OFF\_Mode and must also remain soldered on the board.

It must be taken into account that the RF choke (L1) consists of a resistive part which causes a matching loss. This loss can be calculated using the following equation:

• Parallel equivalent resistance of an inductor

$$R_{Loss} = 2 \times \pi \times f_{RF} \times L_1 \times Q_{L1}$$

Equation 3-1

Mismatch loss

$$10 \times log \bigg(1 + \frac{R_{Lopt}}{R_{Loss}}\bigg)$$

Equation 3-2

Example how to calculate the matching loss:

- f<sub>RF</sub> = 315 MHz

- power setting PWR[0:3]=4

- $R_{Load} = 1600\Omega$

- L<sub>1</sub> = 100 nH (0805CS) with a Q factor of 45

- --> The estimated matching loss will be 0.72 dB.

**Table 3-4.** Measured PA Matching at 315 MHz with Typical Samples (50Ω, CLK\_ON = 'Low')

| Register | P <sub>target</sub> / |       |       |       |                   |                              | Assumption           | Meas  |

|----------|-----------------------|-------|-------|-------|-------------------|------------------------------|----------------------|-------|

| PWR[0:3] | dBm                   | L1/nH | C1/pF | C2/pF | $R_{lopt}/\Omega$ | $\mathbf{Z}_{lopt}\!/\Omega$ | C <sub>par</sub> /pF | P/dBm |

| 3        | -0.5                  | 110   | 1.2   | 1.6   | 2950              | 110+540j                     | 0.9                  | -0.37 |

| 4        | 1                     | 100   | 1.5   |       | 1940              | 150+520j                     | 0.9                  | 1.12  |

| 5        | 2.5                   | 100   | 1.5   |       | 1550              | 190+520j                     | 0.9                  | 2.11  |

| 6        | 3.5                   | 100   | 1.5   |       | 1250              | 220+480j                     | 0.9                  | 3.23  |

| 7        | 4.5                   | 82    | 1.8   |       | 1000              | 240+430j                     | 0.9                  | 4.38  |

| 8        | 5.5                   | 82    | 2.2   |       | 730               | 280+360j                     | 0.9                  | 5.42  |

| 9        | 6.5                   | 68    | 2.7   |       | 580               | 290+300j                     | 0.9                  | 7.14  |

| 10       | 7.5                   | 68    | 2.7   |       | 460               | 290+290j                     | 0.9                  | 8.22  |

| 11       | 8.5                   | 68    | 3.3   |       | 350               | 280+225j                     | 0.9                  | 8.63  |

| 12       | 9.5                   | 56    | 3.6   |       | 320               | 250+150j                     | 0.9                  | 9.79  |

| 13       | 10.5                  | 47    | 4.7   |       | 250               | 215+85j                      | 0.9                  | 10.52 |

| 14       | 11.5                  | 47    | 5.6   |       | 190               | 180+50j                      | 0.9                  | 11.67 |

| 15       | 12.5                  | 47    | 5.6   |       | 160               | 160+45j                      | 0.9                  | 13    |

**Table 3-5.** Measured PA Matching at 433.92 MHz with Typical Samples  $(50\Omega, CLK, ON = 'Low')$

|          | (0015, 011, 011 - 1011) |       |           |       |                   |                              |                      |       |  |  |

|----------|-------------------------|-------|-----------|-------|-------------------|------------------------------|----------------------|-------|--|--|

| Register | P <sub>target</sub> /   |       |           |       |                   |                              | Assumption           | Meas  |  |  |

| PWR[0:3] | dBm                     | L1/nH | C1/pF     | C2/pF | $R_{lopt}/\Omega$ | $\mathbf{Z}_{lopt}\!/\Omega$ | C <sub>par</sub> /pF | P/dBm |  |  |

| 3        | -0,5                    | 68    | 0.9       | 1.5   | 2800              | 60+400j                      | 0.9                  | -0.62 |  |  |

| 4        | 1                       | 56    | 2.7 + 2.2 |       | 1850              | 90+390j                      | 0.9                  | 1.3   |  |  |

| 5        | 2.5                     | 56    | 1.2       |       | 1450              | 110+380j                     | 0.9                  | 2.73  |  |  |

| 6        | 3.5                     | 47    | 1.8       | 5.6   | 1150              | 130+370j                     | 0.9                  | 3.03  |  |  |

| 7        | 4.5                     | 47    | 1.6       |       | 950               | 150+350j                     | 0.9                  | 4.63  |  |  |

| 8        | 5.5                     | 47    | 1.8       |       | 680               | 180+300j                     | 0.9                  | 6.18  |  |  |

| 9        | 6.5                     | 43    | 2.2       | 1     | 560               | 200+270j                     | 0.9                  | 6.66  |  |  |

| 10       | 7.5                     | 36    | 2.4       |       | 450               | 210+230j                     | 0.9                  | 7.91  |  |  |

| 11       | 8.5                     | 33    | 3         |       | 340               | 200+170j                     | 0.9                  | 8.68  |  |  |

| 12       | 9.5                     | 36    | 2.7       |       | 310               | 195+150j                     | 0.9                  | 9.8   |  |  |

| 13       | 10.5                    | 36    | 3.6       |       | 230               | 175+100j                     | 0.9                  | 10.49 |  |  |

| 14       | 11.5                    | 27    | 4.7       |       | 180               | 150+70j                      | 0.9                  | 11.6  |  |  |

| 15       | 12.5                    | 27    | 4.7       |       | 150               | 130+50j                      | 0.9                  | 12.5  |  |  |

Notes to the Table 3-4 on page 10 and Table 3-5:

• The measured values in Table 3-5 are verified using Atmel's demo board ATAB5749.

Used inductors: COILCRAFT 0805CS

Used capacitors: AVX ACCU-P 0402

#### 3.4.3 Harmonics Rejection

In some cases the matching as explained in Section 3.4.1 "Class-C Power Amplifier" on page 7 and Section 3.4.2 "Output Matching to  $50\Omega$  Load" on page 9 does not result in sufficient harmonic suppression, so that an additional low-pass filter needs to be implemented. This chapter describes how the harmonics rejection can be improved by the  $50\Omega$  load matching.

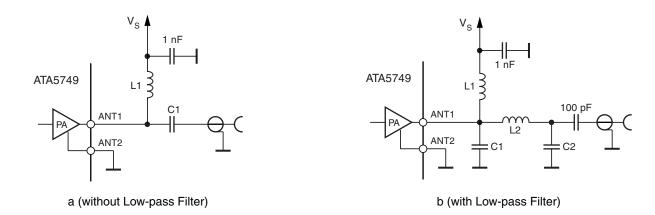

Figure 3-4 on page 12 illustrates PA matching - section b with an additional low-pass filter, section a without low-pass filter. All values in this chapter refer to an ATA5749 application with a 12.5-dBm power setting at a transmit frequency of 433.92 MHz. Table 3-3 on page 6 lists the different matching constellation referring to the circuit as shown in Figure 3-5b. The measurement results as listed in Table 3-4 on page 10 show a different harmonic rejection performance due to the different matching constellation (see Table 3-3 on page 6).

**Figure 3-4.** PA Matching to a  $50\Omega$  Load

Table 3-6. Matching Elements

|          | L1 (0603CS) | C1/pF  | C2/pF  | L2 (0603CS) |

|----------|-------------|--------|--------|-------------|

| Original | 27 nH       | 4.7 pF | n.m.   | n.m.        |

| M1       | 39 nH       | 5.6 pF | 1.5 pF | 27 nH       |

| M2       | 18 nH       | 10 pF  | 1.5 pF | 39 nH       |

| M3       | 18 nH       | 9.1 pF | 1.5 pF | 39 nH       |

| M4       | 18 nH       | 8.2 pF | 1.5 pF | 39 nH       |

Table 3-7.Harmonics Rejection

|          | -                |           |           |           |           |

|----------|------------------|-----------|-----------|-----------|-----------|

|          | P <sub>out</sub> | Hs1       | Hs2       | Hs3       | Hs4       |

| Original | 12.58 dBm        | –19.99 dB | –18.43 dB | –24.17 dB | –23.16 dB |

| M1       | 11.43 dBm        | –32.08 dB | -43.27 dB | > -50 dB  | > -50 dB  |

| M2       | 9.37 dBm         | –36.83 dB | > -50 dB  | > -50 dB  | > -50 dB  |

| М3       | 10.47 dBm        | –37.93 dB | –47.05 dB | > -50 dB  | > -50 dB  |

| M4       | 11.48 dBm        | -40.25 dB | –47 dB    | > -50 dB  | > -50 dB  |

Notes to Table 3-3 on page 6 and Table 3-4 on page 10:

- Original matching structure without low-pass filter

- M1 = first matching constellation, M2 = second matching constellation, etc.

- P<sub>out</sub> = measured transmit power at 433.92 MHz

- Hs1 = suppression of the 1<sup>st</sup> harmonic, Hs2 = suppression of the 2<sup>nd</sup> harmonic, etc.

#### 3.4.4 ATA5749 Frequency Pulling Effect in ASK Mode

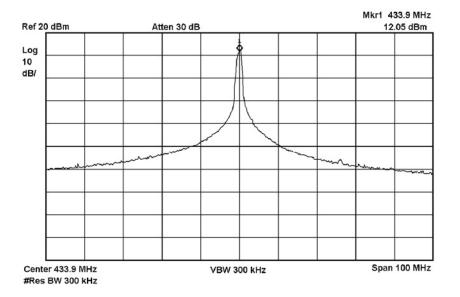

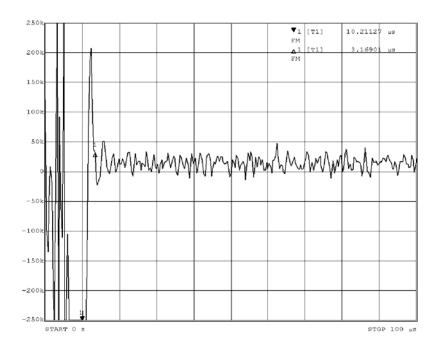

Generally, ASK modulation is performed by switching the power amplifier according to the data rate. When using this method, the decoupling between the power amplifier and the VCO needs to be taken into account in the application. The decoupling measures must be performed internally as well as on the board layout. Otherwise, VCO frequency pulling, affected by the switching of the power amplifier, may occur. Nevertheless, the basic rules of PCB layout design must be observed. Figure 3-5 and Figure 3-6 on page 14 show that the ATA5749 on the Atmel demo board does not exhibit any frequency pulling, even if the maximum transmit power is +12.5 dBm.

**Figure 3-5.** Spectrum of 40 kHz ASK Modulation at  $P_{out} = 12.5 \text{ dBm}$

**Figure 3-6.** Demodulated RF Frequency during PA Switching at  $P_{out} = 12.5 \text{ dBm}$

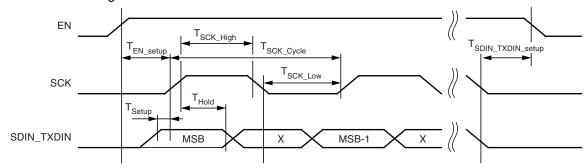

# 3.5 Timing of the Serial Peripheral Interface (SPI) Bus

The UHF transmitter ATA5749 incorporates an SPI bus for the configuration of the transmitter. This bus interface includes the following lines,

- Enable line (EN)

- Data line (SDIN TXDIN)

- SPI bus clock (SCK)

SPI bus timing is illustrated in Figure 3-7 on page 15. The data applied on the SDIN\_TXDIN will be transferred to the positive edge of the SPI clock. In addition to the programming functionality, pin SDIN\_TXDIN also serves as modulating data input for ASK and FSK. The applied data on pin SDIN\_TXDIN will be passed directly as an internal signal (either as ASK\_mod or as FSK\_mod, depending on the chosen modulation type, please refer to Figure 3-1 on page 3). The register bit ASK\_NFSK set the modulation type (please see Table 5-1 and Table 5-2 on page 27). Pin SDIN\_TXDIN will be released as data input if the programming of the 32-bit register has been completed. The timing of the register programming can be seen in Figure 3-8 on page 15 and Figure 3-9 on page 16.

More information on the SPI bus timing conditions can be found in the ATA5749 datasheet (section "Timing Characteristics"). If these conditions are met a maximum SPI bus clock speed of 2 MHz can be achieved.

Note: During OFF\_MODE pin SDIN\_TXDIN and pin SCK must set to the ground.

Figure 3-7. SPI Bus Timing

## 3.5.1 Timing of Register Programming and Data Transmission

#### 3.5.1.1 Timing if the Register Programming Sequence is <u>Faster</u> than XTO Start-up Time

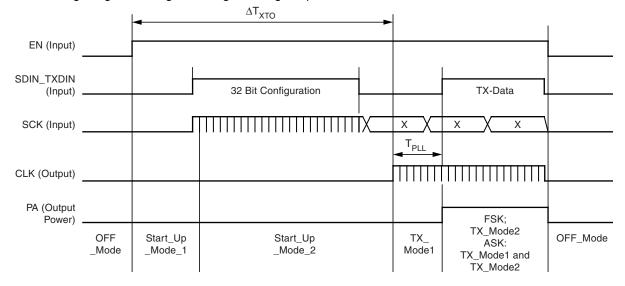

If pin EN is set, the XTO starts immediately. During the start-up process the microprocessor sends the programming sequence (32 configuration bits) via the SPI interface. This programming sequence also needs to be synchronized to the clock frequency on pin SCK, which is usually generated by microprocessor's internal RC oscillator. Figure 3-8 illustrates the programming sequence if the XTO start-up lags behind the programming speed. As mentioned in Section 3.1 "Crystal Oscillator (XTO)" on page 4 the transmitter ATA5749 will generate the clock signal with a crystal tolerance of 200  $\mu$ s typically ( $\Delta$ TXTO) at pin CLK after switching on. That way the clock signal frequency is stable and can be used by the microprocessor as reference to generate the data rate. After a further delay of 98.46  $\mu$ s (T<sub>PLL</sub>) the power amplifier will be activated automatically, and any telegram available at pin SDIN\_TXDIN will be transmitted immediately.

During data transmission the microprocessor clock at pin SCK does not impact the transmitter's functionality. To extend the battery lifetime the ATA5749 must be disabled after each data transmission. For this purpose the SPI interface needs to be cleared (EN = 0, SCK = 0 and SDIN TXDIN = 0).

Note: This timing condition allows short data transmissions as the register programming sequences will be completed during the XTO's start-up time.

Figure 3-8. Timing Diagram if Register Programming Sequence is Faster than ΔΤΧΤΟ

#### 3.5.1.2 Timing if Register Programming Sequence is Slower than XTO Start-up Time

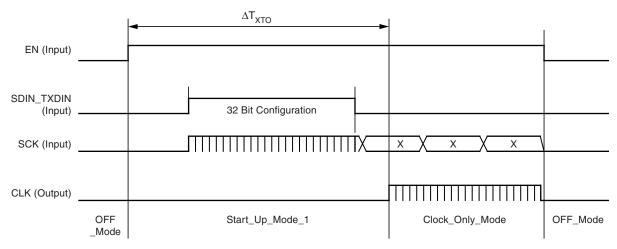

As described in Section 3.5.1.1 "Timing if the Register Programming Sequence is Faster than XTO Start-up Time" on page 15 the microprocessor sends the programming sequence (32 configuration bits) via the SPI interface. This programming sequence also needs to be synchronized to the clock frequency on pin SCK, which is usually generated by microprocessor's internal RC oscillator.

If the SPI programming takes remarkably more time than the XTO start-up, the internal crystal oscillator signal reaches a stable condition earlier than the register programming sequence. In this case the clock signal at pin CLK will be generated exactly after the completion of the register programming progress. The next steps (PA activation, data transmission and switching-off the transmitter) are identical to those described in the previous section. Figure 3-9 illustrates the programming sequence if the XTO start-up is faster than the programming.

This method ensures exact timing for the microprocessor, regardless of the fact that the register programming takes longer than the XTO start-up.

$\Delta T_{XTO}$ EN (Input) SDIN\_TXDIN (Input) 32 Bit Configuration TX-Data X Х SCK (Input)  $\mathsf{T}_{\mathsf{P}\underline{\mathsf{LL}}}$ CLK (Output) PA (Output FSK; Power) TX Mode2 OFF Start Up Start\_Up TX OFF Mode ASK: \_Mode\_2 Mode1 Mode \_Mode\_1 TX\_Mode1 and TX\_Mode2

**Figure 3-9.** Control Timing if Programming is Slower than  $T_{XTO}$

Note: The register is programmed with the negative SCK edge of programming LSB

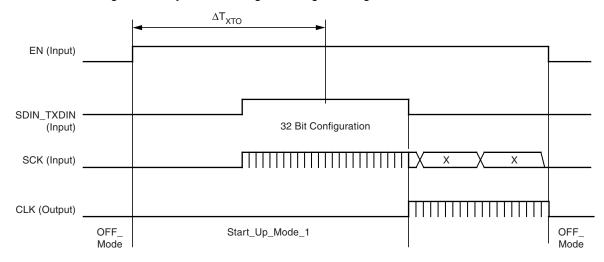

# 3.6 Clock Only Mode

This mode might be useful for specific applications where the clock frequency is still needed for the microprocessor as a reference while the other functional transmitter blocks are deactivated. This mode is controlled by the register bit CLK\_Only, and only the XTO and the clock driver are active. The generated clock frequency depends on the division ratio controlled by the register bit DIV\_CNTRL. For the clock functionality, bit CLK\_ON must always be set, of course. The register contents are listed in Table 5-1 and Table 5-2 on page 27.

Figure 3-10. Control Timing CLK\_Only\_Mode if Register Programming is Faster than ΔΤΧΤΟ

Figure 3-11. Control Timing CLK\_Only\_Mode if Register Programming is Slower than ΔΤΧΤΟ

# 4. Application

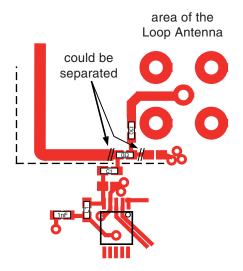

## 4.1 Loop Antenna Design

The matching of the Power Amplifier to the  $50\Omega$  load is described in Section 3.4.2 "Output Matching to  $50\Omega$  Load" on page 9. This section focuses on applications using an antenna, especially a loop antenna. Different applications and operating frequencies need different antenna considerations. Short-range devices in the ISM (Industrial, Scientific and Medical, 315 MHz, 433.92 MHz and 868 MHz) bands mainly use quarter-wave monopoles, helical antennas or printed small-loop antennas. The antenna characteristics such as directivity, gain, polarization, impedance, and bandwidth determine the application's system performance. In addition to the technical requirements the cost is the most significant issue for mass production. Therefore, the decision on the antenna type to be used is always a compromise between cost, package dimension and technical considerations. Typically printed "small" loop antennas are used in hand-held devices of wireless control systems since they are - apart from board space - for free, and they are smaller than a whip or helical antenna. The performance of a loop antenna is sufficient for most system requirements where hand or body approach is not involved. When selecting the antenna type for a transmitter module, potential hand or body approach must always be considered.

# 4.2 Loop Antenna Design Theory

This application note addresses the basic technical information required when applying a "small" loop antenna as used on Atmel's demo board. Any loop antenna with a total circumference of less than a fifth of the wavelength ( $\lambda/5$ ) can be defined as a "small" loop antenna. Several antenna design books even define loop antennas with a circumference of approximately a tenth of the wavelength ( $\lambda/10$ ) as small loop antennas.

A loop antenna is a magnetic antenna that needs a current flow through the loop to generate the required magnetic field for the radiation. The radiation of an antenna can be expressed as radiation resistance ( $R_{\text{Rad}}$ ):

$$R_{Rad} \approx 31.2 \times 10^3 \left(\frac{A^2}{\lambda^4}\right)$$

Equation 4-1

Notes: 1. A = loop area in square meters

2.  $\lambda$  = wavelength in meter

The second essential parameter is the loss of the printed loop antenna. This can be derived from the theory of the skin depth under the assumption that the trace width is remarkably greater than the trace thickness. The loss resistance for a copper trace can be calculated using the following equation:

$$R_{loss\_loop} \approx \frac{1}{2w} \times (2.59 \times 10^{-7}) \times \sqrt{f}$$

Equation 4-2

Notes: 1. L = the total perimeter of the antenna in meter referring to the trace's centre

2. W = trace width in meter

18

In order to calculate the transmit power using the loop antenna it is necessary to determine the efficiency of the antenna. This is given by:

$$\eta = \frac{R_{Rad}}{R_{Rad} + R_{loss\ loop} + R_{loss\ cap}}$$

Equation 4-3

Notes: 1.  $R_{Rad}$  = radiation resistance of the antenna

2. R<sub>loss loop</sub> = loss resistance of the loop's trace

3.  $R_{loss cap} = loss of the capacitors for the matching$

The radiated power can be calculated, as follows

$$P_{Rad} = I_{loop}^2 \times R_{Rad}$$

Equation 4-4

Note:  $I_{loop}$  = current flow through the loop antenna

The relation between the effective radiated power (ERP) and the transmitter output power  $(P_{out \mid C})$  driving the antenna:

$$ERP = \eta \times P_{out,IC}$$

Equation 4-5

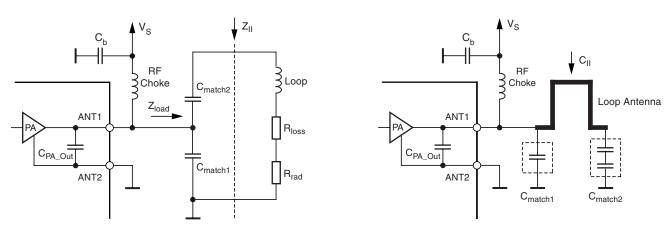

The equivalent circuit for the loop antenna is useful during the matching progress (see Figure 4-1. The first step of the matching procedure is to determine the loop inductance. This value can be calculated using the formula for polygon inductance of a general shape (equation 4-6). The formula results in a relatively good accuracy of approximately ±5%. After that the Q factor of the antenna can be calculated using equation 4-7.

Figure 4-1. Equivalent Circuit of a Loop Antenna

$$L = 2 \times 10^{-7} \times I \times ln \left(\frac{8A}{lw}\right)$$

Equation 4-6

Notes: 1. L = loop perimeter

2. A = loop area

3. W = trace width of the loop antenna

$$Q_{loop} = \frac{\omega L_{loop}}{R_{loss}}$$

Equation 4-7

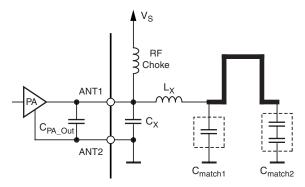

Figure 4-2a shows the principle of the loop antenna matching to the power amplifier of the ATA5749. The two matching capacitors,  $C_{\text{match1}}$  and  $C_{\text{match2}}$ , form the antenna resonance and provide by transformation the optimal load impedance ( $Z_{\text{LOPT}}$ ) required by the power amplifier. To reduce the tolerance influence two serial capacitors can replace  $C_{\text{match1}}$  and  $C_{\text{match2}}$ . As mentioned in Section 3.4.2 "Output Matching to  $50\Omega$  Load" on page 9 the decoupling capacitor (Cb) is necessary for the PA supply blocking and must be placed as close as possible to both the RF choke and pin ANT1. The recommended capacitor Cb value is 1 nF (X7R). The RF choke should provide a low resistive path from the PA's output to VS. Please note that this matching procedure targets to deliver the entire RF current from the PA to the antenna.

The antenna Q-factor must be well chosen to properly handle the tolerances of the elements during the matching progress as well as during mass production later on. The Q-factor should not be too large, and thus the trace width of the printed antenna must be less than 1.5 mm.

Figure 4-2. The Principle Matching of the Loop Antenna to the Power Amplifier

a (with Equivalent Loop Antenna Circuit)

b (Standard Schematic without Equivalent Loop Antenna Circuit

Equations 4-8 to 4-13 help to calculate the start values of the matching elements during the tuning process. The calculation refers to the circuit in Figure 4-2a. First, the parallel resonance impedance  $(Z_{II})$  can be calculated by formula 4-8.

$$Z_{||} = Q_{|oop} \times 2\pi f L_{|oop}$$

Equation 4-8

$Z_{||} = r^2 \times Z_{|oad}$  Equation 4-9

Note: r = transformation ratio of the matching structure (C<sub>match1,2</sub>)

$$C_{II} = \frac{1}{\omega^2 L_{loop}} = \frac{(C_{match1} + C_{PA\_Out}) \times C_{match2}}{(C_{match1} + C_{PA\_Out}) + C_{match2}}$$

Equation 4-10

$$r = \frac{(C_{\text{match1}} + C_{\text{PA\_Out}}) + C_{\text{match2}}}{C_{\text{match2}}}$$

Equation 4-11

The C<sub>match1</sub> and C<sub>match2</sub> can be given as,

$$C_{\text{match1}} = r \times C_{\text{II}} - C_{\text{PA OUT}}$$

Equation 4-12

$$C_{\text{match2}} = \frac{(C_{\text{match1}} + C_{\text{PA\_Out}})}{r - 1}$$

Equation 4-13

<u>Caution</u>: The calculated  $C_{match1}$  and  $C_{match2}$  values are only the theoretical start values for the tuning process.

With regard to the 1<sup>st</sup> harmonic suppression, Cmatch1 must be placed as close as possible to the power amplifier. If a higher harmonic rejection is needed an additional low-pass filter has to be inserted in the matching circuit. Figure 4-3 shows the principle schematic using an additional low-pass filter to improve the harmonics suppression. The capacitor  $C_X$  must be placed as close as possible to the power amplifier output and properly fixed to both pin ANT2 and the ground plate.

Figure 4-3. Matching Structure of the Loop Antenna with an Additional Low Pass Filter

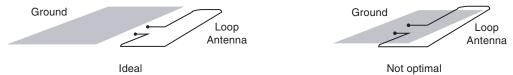

The following rules must be observed when designing a loop antenna:

- In case of a small loop antenna, the area enclosed by the loop has to be designed as large as possible

- The ground area within the loop must be small

- As the field density increases at the loop edges, sufficient space must be provided near the loop edges

Figure 4-4. Comparison of an Ideal and a Poor Loop Antenna Layout Design

# 4.3 Application Circuit and Layout Design Hints

The following rules must be adhered to achieve optimum module performance:

- The connection of pin ANT2 to ground must be designed properly. The best practical way is

to place several vias directly to the board's ground plate. This rule is also valid for the

ground connection of the matching elements.

- The conductive trace for the clock signal from the ATA5749 to the microprocessor must be designed very carefully and as short as possible.

- Each blocking capacitor (especially the decoupling capacitor for the ATA5749's supply

voltage) must be placed as close as possible to the power supply pin to be decoupled. The

recommended value for the decoupling capacitor is 68 nF (X7R).

- The crystal must be placed as close as possible to the IC.

## 4.4 Developing an Application-specific ATA5749 Design using Atmel's Demo Boards

For developing purposes, Atmel offers 2 different boards, the demo board ATAB5749-x and ATA5749-EKx. The ATA5749-EKx is a stand-alone board, where the pre-defined board settings can not be changed unless the software is changed. In case the transmitter settings need to be modified, engineers should use the demo board ATAB5749-x (changes of the software, however, can not be done with this board). Certain settings of the ATAB5749-x can be modified using software installed in the Windows® operating system.

#### 4.4.1 Short Information on ATAB5749-x

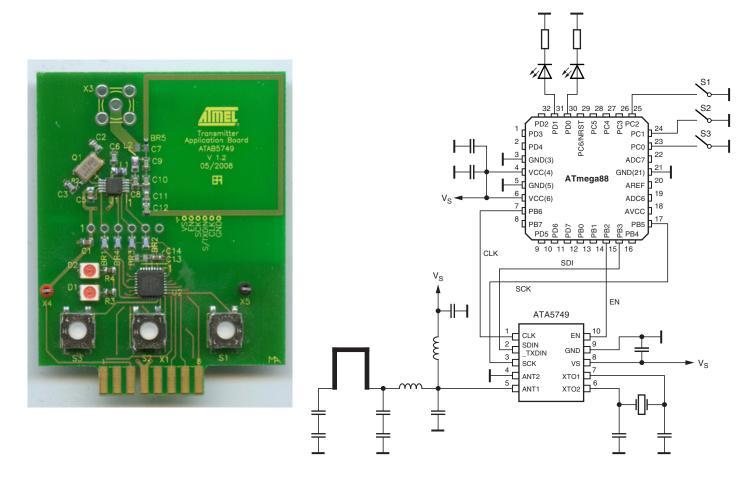

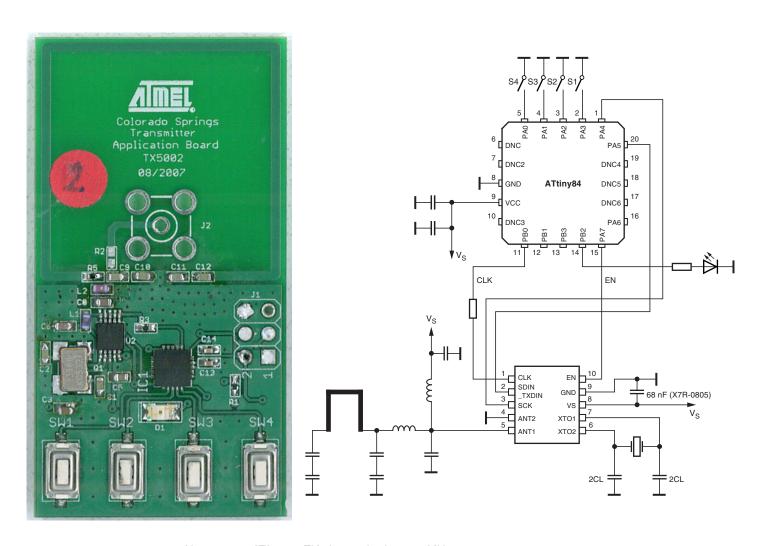

Figure 4-5. ATAB5749-x: Simplified Schematic and Demo Board Picture

The microprocessor board ATAB-RFMB and the "RF Design Kit Software" are needed to start the verification. The application note "Getting Started with ATAB5749 Using RF Design Kit Software" explains how to operate the demo kit. This document is available online on Atmel's website at http://www.atmel.com/dyn/resources/prod\_documents/doc9138.pdf).

Notes: 1. ATAB5749-3 is matched to 315 MHz

- 2. ATAB5749-4 is matched to 433.92 MHz

- 3. For IC verification:

- ATAB-RFMB, (including the Software RF Design Kit

- ATAB5749-3/4

#### 4.4.1.1 Short Description of the Demo Software

The main issue is how to generate an accurate data rate to modulate the transmitter. To this end the ATA5749's clock signal can be used as an external reference to calibrate the internal RC oscillator. The data rate tolerance of the transmitter module will be much tighter than the tolerance of the internal RC oscillator - even if only one crystal is used for the transmitter and the microprocessor. For this purpose the "external" clock, provided by the ATA5749, must be connected to the microprocessor's timer/counter pin (please refer to Figure 4-5 on page 23).

Touching a button causes the following events:

- 1. Start of the microprocessor with its internal RC oscillator

- 2. Configuration of the 32-bit control register via SPI interface

- 3. Waiting for the clock signal generated by the transmitter

- Calibration start of the internal RC oscillator once the ATA5749's clock signal is available

- 5. Shifting the telegram to ATA5749

Note: The RC oscillator's calibration must be performed for each telegram transmission.

To minimize the current consumption on the demo board the ATmega88 always remains in power-down mode until an event occurs. The activation of a button wakes up the microprocessor using a pin change interrupt. To further reduce the current consumption the watchdog timer and brown-out detection are disabled. As the microprocessor's ADC is not used it is also switched off (please refer to the Power Reduction Register (PRR) of ATmega48/88).

#### 4.4.1.2 Measurement with $50\Omega$ Interface

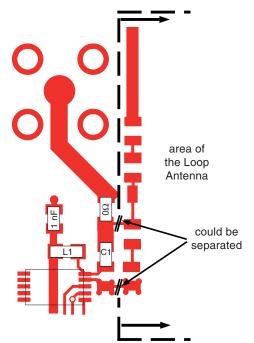

The ATAB5749-x board enables to use an SMB or SMA connector for measurement purposes. Figure 4-6 shows a detail of the board layout with the IC and the  $50\Omega$  output. It illustrates how the connector and the matching elements can be mounted. The inductor L1 and capacitor C1 values can be taken from Table 3-1 on page 4 and Table 3-2 on page 5.

**Figure 4-6.** Section of ATAB5749-x for  $50\Omega$  Measurement

#### 4.4.2 Short Information on ATA5749-EKx

Figure 4-7. ATA5749-EKx: Simplified Schematic and Demo Board Picture

Notes: 1. ATA5749-EK1 is matched to 315 MHz

2. ATA5749-EK2 is matched to 433.92 MHz

#### 4.4.2.1 Measurement with $50\Omega$ Interface

Same as the ATAB5749-x demo board, the ATA5749-EKx enables to use an SMB or SMA connector for measurement purposes. Figure 4-8 shows a detail of the board layout with the IC and the  $50\Omega$  output. It illustrates how the connector and the matching elements can be mounted.

**Figure 4-8.** Section of ATAB5749-x for  $50\Omega$  Measurement

# 4.4.2.2 Approval Test

The boards ATA5749-EK1 and ATA5749-EK2 were tested by an authorized test house according to the FCC (part 15) and ETSI (EN 300 220-1 V2.1.1) regulations. These tests demonstrate that the ATA5749 on the ATA5749-EKx demo boards is able to achieve the common type approval for automotive applications.

# 5. ANNEX

Table 5-1.

Organization of the 32 Bit Control Register

| MSB  |       |         |           |        |        |          |        |           |        |        |         |         |        |      |      |

|------|-------|---------|-----------|--------|--------|----------|--------|-----------|--------|--------|---------|---------|--------|------|------|

| 31   | 30    | 29      | 28        | 27     | 26     | 25       | 24     | 23        | 22     | 21     | 20      | 19      | 18     | 17   | 16   |

| CLK_ | S434_ | FREQ    | FREQ      | FREQ   | FREQ   | FREQ     | FREQ   | FREQ      | FREQ   | FREQ   | FREQ    | FREQ    | FREQ   | FREQ | FREQ |

| Only | N315  | [14]    | [13]      | [12]   | [11]   | [10]     | [9]    | [8]       | [7]    | [6]    | [5]     | [4]     | [3]    | [2]  | [1]  |

|      |       | Frequen | ıcy Adjus | t FREQ | = FREQ | [0] + 2× | FREQ[1 | ] + 4 × F | REQ[2] | + + FF | REQ[14] | × 16384 | = 0 32 | 2767 |      |

|      |                                                     |      |      |      |      |      |      |      |                    |     |     |     |     |      | LSB  |

|------|-----------------------------------------------------|------|------|------|------|------|------|------|--------------------|-----|-----|-----|-----|------|------|

| 15   | 14                                                  | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6                  | 5   | 4   | 3   | 2   | 1    | 0    |

| FREQ | FSEP                                                | FSEP | FSEP | FSEP | FSEP | FSEP | FSEP | FSEP | DIV_               | PWR | PWR | PWR | PWR | ASK_ | CLK_ |

| [0]  | [7]                                                 | [6]  | [5]  | [4]  | [3]  | [2]  | [1]  | [0]  | CNTRL              | [3] | [2] | [1] | [0] | NFSK | ON   |

|      | FSK Shift  FSEP = FSEP[0] + + FSEP[7] × 128 = 0 255 |      |      |      |      |      |      |      | Power P'<br>PWR[3] |     |     |     |     |      |      |

Table 5-2.

Register Description

| Name       | Bit Number | Bit Count | Remarks                                                                                                                                                                               |

|------------|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_Only   | 31         | 1         | Activates / deactivates CLK_Only Mode CLK_only = "Low" normal Mode CLK_only = "High" CLK_Only Mode in Figure 3-10 on page 17                                                          |

| S434_N315  | 30         | 1         | VCO Band Selection and divider control "High": 367 450 MHz "Low": 300 368 MHz                                                                                                         |

| FREQ[0:14] | 15 29      | 15        | Values 0 32767<br>PLL frequency adjust                                                                                                                                                |

| FSEP[0:7]  | 7 14       | 8         | Values 0 255<br>FSK Deviation setting                                                                                                                                                 |

| DIV_CNTRL  | 6          | 1         | CLK output Divider Ratio  "Low": $f_{CLK} = f_{XTO}/8$ "High": $f_{CLK} = f_{XTO}/4$                                                                                                  |

| PWR[0:3]   | 2 5        | 4         | Values 0 15 see Table 3-1 on page 4.  PA Output Power Adjustment  PWR = 3 15> Pout = -0.5 dBm 12.5 dBm  in approximately 1 dB steps see Table 3-4 on page 10 and Table 3-5 on page 11 |

| ASK_NFSK   | 1          | 1         | Modulation Type "Low": FSK "High": ASK                                                                                                                                                |

| CLK_ON     | 0          | 1         | CLK_DRV port de-/activation "High": CLK port is ON "Low": CLK port is OFF                                                                                                             |

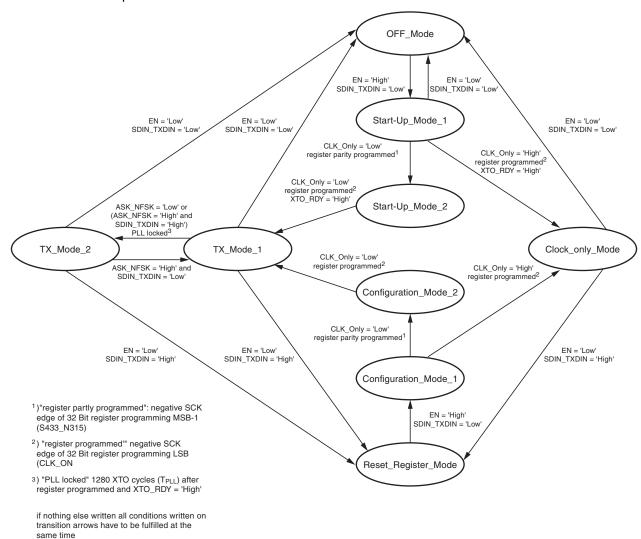

Figure 5-1. Flowchart Operation Modes

#### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia

Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon

Hong Kong

Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud

BP 309 78054

Saint-Quentin-en-Yvelines Cedex

France

Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

Atmel Japan

9F, Tonetsu Shinkawa Bldg.

1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033

Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site

www.atmel.com

**Technical Support**

auto\_control@atmel.com

Sales Contact

www.atmel.com/contacts

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2010 Atmel Corporation. All rights reserved. Atmel logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Windows® is a registered trademark of Microsoft Corporation in the United States and other countries. Other terms and product names may be trademarks of others.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Atmel:

ATA5749-EK1 ATA5749-EK2