# Analog Devices Welcomes Hittite Microwave Corporation

NO CONTENT ON THE ATTACHED DOCUMENT HAS CHANGED

#### Typical Applications

The HMC6590 is ideal for:

- 40 GbE-FR

- 40 GBps VSR / SFF

- Short, intermediate, and long-haul optical receivers

#### **Features**

- Supports data rates up to 43 Gbps

- Internal DCA feedback with external adjustment option

- 4 Kohm differential transimpedance gain

- Low-power dissipation < 300 mW</li>

- -10.5 dBm optical input sensitivity

- +5 dBm optical overload

- Small die size: 1.15 mm x 1.21 mm x 0.15 mm

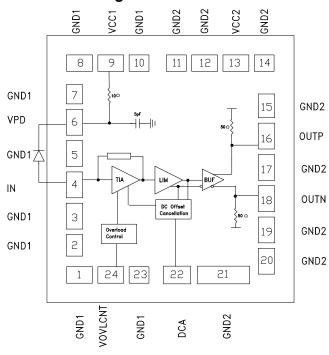

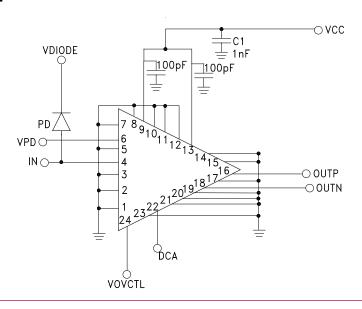

#### **Functional Diagram**

#### **General Description**

The HMC6590 is a high-speed, high gain, low-power limiting transimpedance amplifier (TIA) used in optical receivers with data rates up to 43 Gbps. It features low input referred noise, 36 GHz bandwidth, 4 kohm differential small signal transimpedance and output cross point adjustment. HMC6590 exhibits an optical input dynamic range between -10 dBm and +5 dBm while maintaining 10e-12 BER at 43 Gbps operation.

The HMC6590 is available in die form, includes an on-chip VCC bypass capacitor. It requires only supply decoupling capacitor as external component.

The HMC6590 requires a single 3.3V  $\pm 5\%$  supply and it typically dissipates less than 300 mW. The device is characterized for operation from -5 °C to +85 °C temperature.

v02 1014

# 43 Gbps TRANSIMPEDANCE AMPLIFIER

## Electrical Specifications, $T_{A} = +25^{\circ}\text{C}$ , Vcc = 3.3V

| Parameter                                      | Conditions                        | Min. | Тур.  | Max. | Units  |

|------------------------------------------------|-----------------------------------|------|-------|------|--------|

| Max Data Rate                                  | NRZ                               | 43   |       |      | Gbps   |

| Z21 Small Signal Bandwidth[3]                  | 3 dB cut off                      |      | 39    |      | GHz    |

| Z21 3 dB Low Cutoff Frequency                  |                                   |      | 50    |      | KHz    |

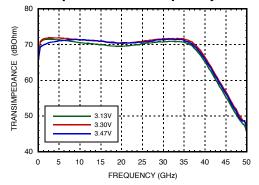

| Transimpedance (Z21)                           | Differential @ 100 MHz            |      | 4     |      | KOhm   |

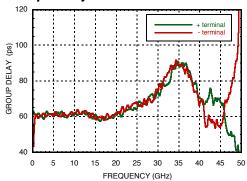

| Group Delay Variation                          | Up to 40 GHz                      |      | ± 15  |      | psec   |

| Differential Output Swing                      | @ 43 Gbps (saturated)             |      | 450   |      | mVp-p  |

| Input Referred RMS Noise                       | Up to 35 GHz                      |      | 3.3   |      | uA     |

| Input Referred Noise Densitiy.                 | RMS noise per 35 GHz              |      | 20    |      | pA/√Hz |

| Optical Input Sensitivity <sup>[1]</sup> (OMA) | Responsivity = 0.65A/W, ER = 9 dB |      | -10.5 |      | dBm    |

| Optical Overload Power <sup>[2]</sup> (OMA)    | Responsivity = 0.65 A/W, ER = 9dB |      | +5    |      | dBm    |

| Input Overload Current                         |                                   |      | 4     |      | mAp-p  |

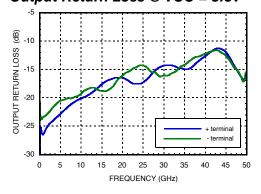

| Output Return Loss (S22)                       | Up to 40 Ω GHz                    |      |       | -10  | dB     |

| Additive RMS Jitter                            | 40 Gbps 1010 stream               |      |       | 0.5  | ps     |

| Input DC Voltage                               | Internally generated              |      | 1.2   |      | V      |

| Operational Supply Voltage Range               | ± 5%                              | 3.15 | 3.3   | 3.45 | V      |

| Supply Current                                 | Vcc = 3.3V                        |      | 94    |      | mA     |

| Operating Temperature Range (Die backside)     |                                   | -5   |       | +85  | °C     |

<sup>[1]</sup> Sensitivity depends on photo diode, packaging, BERT sensitivity, input eye quality and optical coupling.

#### Output Return Loss @ VCC = 3.3V[1]

#### **Group Delay @ VCC = 3.3V**[1]

#### Transimpedance vs Frequency over Supply<sup>[2]</sup>

<sup>[1] 50</sup>  $\Omega$  on wafer measurement results .

<sup>[2]</sup> Vovlcnt= 1.7V

<sup>[3] 50</sup>  $\Omega$  on wafer measurement results.

<sup>[2]</sup> Assumes photo diode and assembly model on page 3.

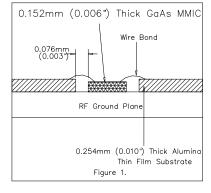

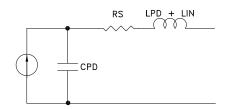

#### Photo Diode Model and Assembly Assumptions

Photo diode and assembly diagram model used in Z21 and input referred noise density calculations:

- $C_{PD} = 50 \text{ fF}$

- $R_s = 15 \Omega$

- $L_{PD} + L_{IN} = 0.35 \text{ nH}$

- $L_{OUT} = 0.25 \text{ nH}$

- $L_{GND}^{GND} = 0.25 \text{ nH}$

- $L_{VDD}^{GIID} = 0.25 \text{ nH}$

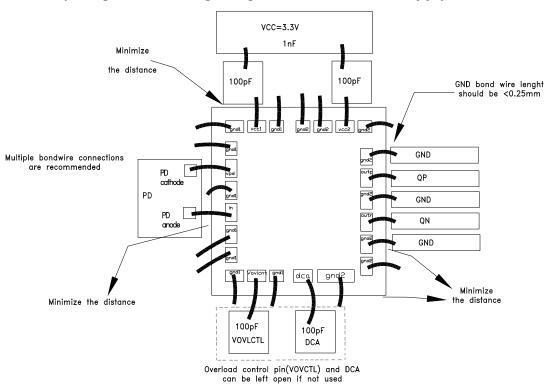

#### Assembly Diagram for Using Integrated Photo Diode Supply VPD

Suggested assembly configuration for using internal supply for photo-diode. Suggested bond-wire length for optimum performance is as follows:

- $\bullet \qquad L_{PD} + L_{IN} < 0.35 \; mm$

- L<sub>out</sub> < 0.25 mm (double-bond is recommended)

- L<sub>GND</sub> < 0.25 mm (double-bond for larger pads)

- L<sub>VCC</sub> < 0.25 mm (double-bond is recommended)

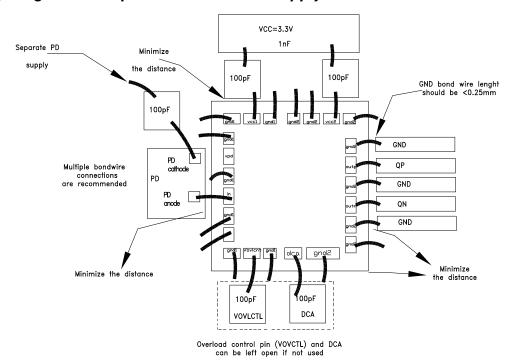

#### Assembly Diagram for Separate Photo Diode Supply

Suggested assembly configuration for separate photo diode supply. Suggested bond-wire length for optimum performance is as follows:

- $L_{PD} + L_{IN} < 0.35 \text{ mm}$

- $L_{\text{OUT}}^{-2} < 0.25 \text{ mm}$  (double-bond is recommended)

- $L_{GND}$  < 0.25 mm (double-bond for larger pads)

- L<sub>vcc</sub> < 0.25 mm (double-bond is recommended)

#### **Application Circuit**

#### Absolute Maximum Ratings

| Voltage level at the RF input (Vin)                          | -0.6V to 2.5V   |  |

|--------------------------------------------------------------|-----------------|--|

| Current level at the RF input (In)                           | 0 to 10 mA      |  |

| Voltage level at the RF output                               | VCC-1 to VCC+1  |  |

| Supply Voltage (VCC)                                         | -0.6V to 3.75V  |  |

| Max. Junction Temperature                                    | 125 °C          |  |

| Continuous Pdiss (T=85°C)<br>(Derate 30.23 mW/°C above 85°C) | 1.21 W          |  |

| Thermal Resistance R <sub>th</sub> (Junction to die bottom)  | 33.08 °C/W      |  |

| Storage Temperature                                          | -55 to +125 °C  |  |

| Operating Temperature (Die backside)                         | -5 to +85 °C    |  |

| ESD Sensitivity Level (HBM)                                  | Class 0 (>150V) |  |

ELECTROSTATIC SENSITIVE DEVICE **OBSERVE HANDLING PRECAUTIONS**

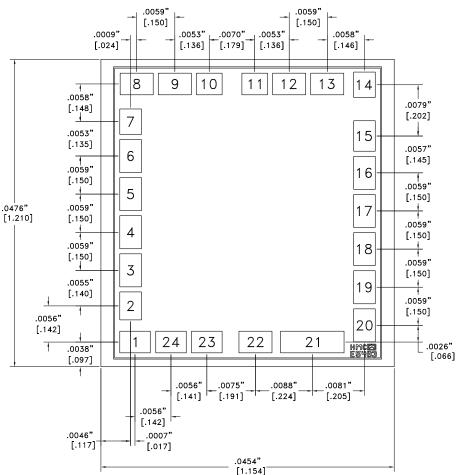

#### Die Packaging Drawing [1]

| Standard        | Alternate |  |

|-----------------|-----------|--|

| GP-1 (Gel Pack) | [2]       |  |

[1] For more information refer to the "Packaging Information" Document in the Product Support Section of our website .

[2] For alternate packaging information contact Hittite Microwave Corporation.

#### Die Pads Dimensions

| Pads         | Pad Size                      |

|--------------|-------------------------------|

| 1,23,24      | 0.0047[0.120] X 0.0033[0.085] |

| 2            | 0.0033[0.085] X 0.0043[0.110] |

| 3-6,16-20    | 0.0033[0.085] X 0.0051[0.130] |

| 7            | 0.0033[0.085] X 0.0039[0.100] |

| 8,9,12,13,22 | 0.0051[0.130] X 0.0033[0.085] |

| 10,11        | 0.0040[0.101] X 0.0033[0.085] |

| 14           | 0.0033[0.085] X 0.0093[0.100] |

| 15           | 0.0033[0.085] X 0.0047[0.120] |

| 21           | 0.0098[0.250] X 0.0033[.085]  |

#### **Outline Drawing**

NOTES:

- 1. ALL DIMENSIONS ARE IN INCHES [MM]

2. DIE THICKNESS IS .006"

3. BOND PAD METALIZATION: ALUMINUM

- 4. NO BACKSIDE METAL

5. OVERALL DIE SIZE ±.002'

## **Pad Descriptions**

| Pad Number                 | Function | Description                                                                                                                                                                                                                                                                  | Interface Schematic                          |

|----------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1,2,3,5,7,8,10<br>23,26    | GND1     | Ground connection for TIA.                                                                                                                                                                                                                                                   | GND<br>=                                     |

| 4                          | IN       | TIA input.                                                                                                                                                                                                                                                                   | IN R                                         |

| 6                          | VPD      | Provides bias voltage for photo-diode (PD) through a 50 $\Omega$ resistor/capacitor network from VCC1.                                                                                                                                                                       | VCC1 500 VPD                                 |

| 9                          | VCC1     | Power supply for input stage and PD.                                                                                                                                                                                                                                         | GND1                                         |

| 11,12,14,15,17<br>19-22,25 | GND2     | Ground connection for TIA.                                                                                                                                                                                                                                                   | Ģ GND<br><u>=</u>                            |

| 13                         | VCC2     | Power supply for output buffers.                                                                                                                                                                                                                                             | VCC2                                         |

| 16                         | OUTP     | Non-inverted data output with 50 $\Omega$ back termination.                                                                                                                                                                                                                  | 50n 50n 00UTN                                |

| 18                         | OUTN     | Inverted data output with 50 $\Omega$ back termination.                                                                                                                                                                                                                      | =                                            |

| 22                         | DCA      | DC offset control. Voltage at this pad sets output DC offset. When it is floating, DC offset is at 0V.                                                                                                                                                                       | VCC2<br>DCA 91ko<br>91ko<br>GND2             |

| 24                         | VOVLCNT  | Overload current compensation control. Voltage at this pad sets the strength of the input overload current control. When it is floating, overload control is set to nominal(VCC1/2). Overload performance can be optimized by adjusting VOVLCNT voltage between 1.6V - 3.3V. | VCC1<br>VOVLCNT 20kn<br>120n<br>22kn<br>GND1 |

#### **Mounting & Bonding Techniques for MMICs**

The die should be attached directly to the ground plane with epoxy (see HMC general Handling, Mounting, Bonding Note).

50  $\Omega$  Microstrip transmission lines on 0.254 mm (10 mil) thick alumina thin film substrates are recommended for bringing high speed differential signal from the chip RF to and from the chip (Figure 1).

Microstrip substrates should be placed as close to the die as possible in order to minimize bond wire length. Typical die-to-substrate spacing is 0.076 mm to 0.152 mm (3 to 6 mils).

#### **Handling Precautions**

Follow these precautions to avoid permanent damage.

Storage: All bare die are placed in either Waffle or Gel based ESD protective containers, and then sealed in an ESD protective bag for shipment. Once the

sealed ESD protective bag has been opened, all die should be stored in a dry nitrogen environment.

Cleanliness: Handle the chips in a clean environment. DO NOT attempt to clean the chip using liquid cleaning systems.

Static Sensitivity: Follow ESD precautions to protect against ESD strikes.

**Transients:** Suppress instrument and bias supply transients while bias is applied. Use shielded signal and bias cables to minimize inductive pick-up.

General Handling: The chip may be handled by a vacuum collet or with a pair of sharp tweezers.

#### **Mounting**

Epoxy Die Attach: Apply a minimum amount of epoxy to the mounting surface so that a thin epoxy fillet is observed around the perimeter of the chip once it is placed into position. Cure epoxy per the manufacturer's schedule.