## Quad Channel Ultrasound Echo Multiplexer with T/R Switch

#### **Features**

- Quad channel analog echo signal MUX switches

- ▶ ±130V 20ns T/R switch built-in for each channel

- $\triangleright$  17 $\Omega$  total on-resistance for low insertion loss

- 0.8nV/rt.Hz low RF input noise at 5MHz

- ▶ DC to 100MHz small signal bandwidth

- ▶ -65dB off-Isolation and -55dB crosstalk

- ► Single +5V power supply

- ► Low power consumption

- ▶ 20MHz serial interface 3.3V CMOS logic

- -55dB HD2 very low echo signal distortions

#### **Applications**

- Medical imaging ultrasound beamforming receiver

- Software programmable echo multiplex switching

- High resolution phase array ultrasound NDT

- Ultrasonic phase array receiver focusing

- Array PZT transducer echo phase processing

#### **General Description**

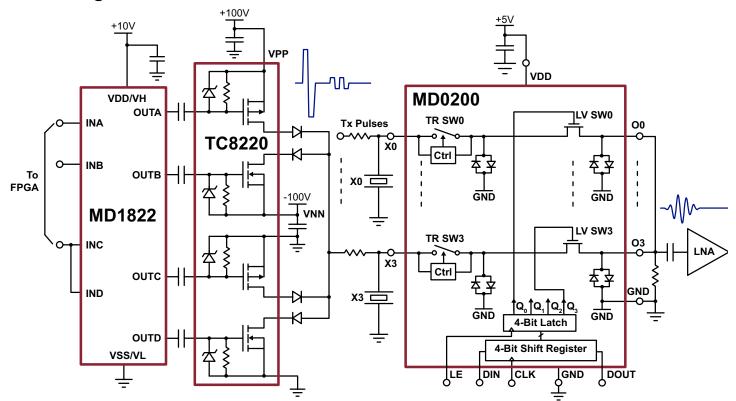

The MD0200 is a multi-channel, low voltage, analog multiplex switch with a high voltage T/R switch and diode voltage limiter circuit. It is designed for medical ultrasound image system receive beamforming applications. It also can be used in NDT and other ultrasound applications.

The MD0200 circuit consists of a low voltage CMOS analog switch and digital logic serial interface circuits. This analog switch not only has very low insertion loss and noise and wide frequency response, it also has high isolation and low channel to channel crosstalk. The inputs of the analog switch are connected to the output of the two terminal type of ultrasound T/R switch, and two back-to-back diode voltage limiter circuits.

The shift-register and latch-register serial interface has allowed the IC maximum flexibility to connect a large number of channels together to form the echo multiplexing dynamic-focusing circuit for ultrasound image receive beamforming.

### **Block Diagram**

#### **Ordering Information**

| Part Number     | Package Options   | Packing   |  |  |

|-----------------|-------------------|-----------|--|--|

| MD0200K6-G      | 18-Lead DFN (5x5) | 490/Tray  |  |  |

| MD0200K6-G M932 | 18-Lead DFN (5x5) | 2500/Reel |  |  |

<sup>-</sup>G denotes a lead (Pb)-free / RoHS compliant package

### Absolute Maximum Ratings<sup>1</sup>

| Parameter                       | Value          |

|---------------------------------|----------------|

| GND reference voltage           | 0V             |

| X0~X3 input pins to GND voltage | 0 to ±140V     |

| V <sub>DD</sub> positive supply | -0.5V to +6.5V |

| All logic input pins            | -0.5V to +6.5V |

| Maximum junction temperature    | +125°C         |

| Storage temperature range       | -65°C to 150°C |

#### Note

#### **Typical Thermal Resistance**

| Package     | $oldsymbol{	heta_{ja}}$ |

|-------------|-------------------------|

| 18-Lead DFN | 30°C/W                  |

#### **Pin Configuration**

18-Lead DFN (top view)

## **Product Marking**

L = Lot Number

YY = Last Digit of Year Sealed

WW = Code for Week Sealed

A = Assembler ID

C = Country of Origin

—— = "Green" Packaging

18-Lead DFN

Package may or may not include the following marks: Si or

## Operating Supply Voltages (Over operating conditions unless otherwise specified, $V_{np}$ = +5V, $T_{i}$ = 25°C)

| Sym                   | Parameter                                               | Min    | Тур  | Max   | Unit  | Conditions                                                 |

|-----------------------|---------------------------------------------------------|--------|------|-------|-------|------------------------------------------------------------|

| Sylli                 | Parameter                                               | IVIIII | тур  | IVIAX | Ullit | Conditions                                                 |

| V <sub>SIG</sub>      | Signal input range (p-p)                                | -      | ±400 | -     | mV    |                                                            |

| V <sub>DD</sub>       | Positive voltage power supply                           | 4.75   | 5.00 | 5.25  | V     | T <sub>A</sub> = 0 to 70°C                                 |

| R <sub>on</sub>       | Total switch ON-resistance $X_{0\sim3}$ to $O_{0\sim3}$ | -      | 17.5 | -     | Ω     | $I_X = \pm 5.0 \text{mA}, V_{X0\sim3} = \pm 300 \text{mV}$ |

| $\Delta R_{_{ m ON}}$ | Ch to Ch R <sub>ON</sub> difference                     | -      | ±5   | -     | %     |                                                            |

| W                     | Diada farward valtaga                                   | -      | 0.8  | 1.0   | V     | 1mA                                                        |

| V <sub>F</sub>        | Diode forward voltage                                   | -      | 1.25 | 1.50  | V     | 100mA                                                      |

| I <sub>FM</sub>       | Diode forward continuous current                        | -      | 100  | -     | mA    |                                                            |

| I <sub>DDQ</sub>      | V <sub>DD</sub> supply current 0MHz                     | -      | 0.1  | 0.2   | mA    | f <sub>CLK</sub> = 0Hz                                     |

| I <sub>DD20</sub>     | V <sub>DD</sub> supply current 20MHz                    | -      | 8.0  | 10    | mA    | f <sub>CLK</sub> = 20Hz                                    |

| HD2                   | Second harmonic distortion                              | -      | -55  | -     | dB    | 5MHz sine wave,<br>±300mV p-p input                        |

<sup>1.</sup> Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

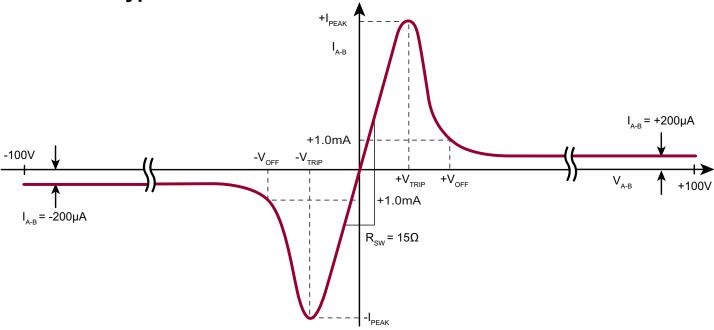

## T/R Switch Characteristics (Over operating conditions unless otherwise specified, $V_{DD}$ = +5V, $T_j$ = 25°C)

| Sym                  | Parameter                                                          | Min  | Тур  | Max  | Unit | Conditions                                              |

|----------------------|--------------------------------------------------------------------|------|------|------|------|---------------------------------------------------------|

| V <sub>x</sub>       | Max X <sub>0∼3</sub> to GND input voltage                          | ±130 | -    | -    | V    | I <sub>χ</sub> = ±500μA                                 |

| R <sub>TRSW</sub>    | Switch ON-resistance of T/R SWX <sub>0~3</sub> to O <sub>0~3</sub> | -    | 15   | -    | Ω    | $I_X = \pm 5.0 \text{mA}, V_{X0-3} = \pm 300 \text{mV}$ |

| V <sub>TRIP</sub>    | VX <sub>0~3</sub> trip point to turn off                           | -    | ±1.0 | ±2.0 | V    |                                                         |

| V <sub>OFF</sub>     | T/R switch turn off voltage                                        | -    | ±2.0 | -    | V    | $I_{A-B} = \pm 1.0 \text{mA}$                           |

| I <sub>PEAK</sub>    | Peak T/R switch current                                            | -    | ±60  | -    | mA   |                                                         |

| T <sub>OFF</sub>     | Turn-OFF time                                                      | -    | -    | 20   | ns   |                                                         |

| T <sub>on</sub>      | Turn-ON time                                                       | -    | -    | 20   | ns   |                                                         |

| C <sub>SW(ON)</sub>  | Switch ON-capacitance                                              | -    | 15   | -    | pF   | T/R SW = ON                                             |

| C <sub>SW(OFF)</sub> | Switch OFF-capacitance                                             | -    | 9.0  | -    | pF   | V <sub>(X0~3)</sub> = ±25V                              |

| BW                   | Small signal bandwidth                                             | -    | 100  | -    | MHz  | $R_{LOAD} = 50\Omega$                                   |

## Clock and Logic I/O Characteristics (Over operating conditions unless otherwise specified, $V_{DD}$ = +5V, $T_j$ = 25°C)

| V <sub>IH</sub> | Input logic high voltage  | 2.5  | 3.3 | 5.0  | V  | Design for 2 2V/Logic   |

|-----------------|---------------------------|------|-----|------|----|-------------------------|

| V <sub>IL</sub> | Input logic low voltage   | 0    | -   | 0.6  | V  | Design for 3.3V Logic   |

| I <sub>IH</sub> | Input logic high current  | -    | -   | 1.0  | μA |                         |

| I               | Input logic low current   | -1.0 | -   | -    | μA |                         |

| C <sub>IN</sub> | Input capacitance         | -    | 10  | 12   | pF |                         |

| I <sub>OH</sub> | Output logic high current | -    | -   | -2.0 | mA |                         |

| I <sub>OL</sub> | Output logic low current  | -    | -   | 2.0  | mA |                         |

| V <sub>OH</sub> | Output logic high voltage | 4.5  | -   | -    | V  | I <sub>OH</sub> =-2.0mA |

| V <sub>OL</sub> | Output logic low voltage  | -    | -   | 0.35 | V  | I <sub>OL</sub> =-2.0mA |

## AC Electrical Characteristics (Over operating conditions unless otherwise specified, $V_{DD}$ = +5V, $T_j$ = 25°C)

| Q <sub>C</sub>                 | LV SW charge injection        | -  | 3.0 | 7.0 | pC  | V <sub>(X0~3)</sub> = 0V,<br>O3~1 to GND 1nF load |

|--------------------------------|-------------------------------|----|-----|-----|-----|---------------------------------------------------|

| BW                             | Small signal bandwidth        | -  | 100 | -   | MHz | $R_{LOAD}$ =50 $\Omega$                           |

| K <sub>o</sub>                 | OFF-Isolation                 |    | -60 | -   | dB  | At 10MHz,                                         |

| K <sub>CR</sub>                | On-channel crosstalk          | -  | -55 | -   | dB  | $R_{LOAD} = 50\Omega$ , ±300mVp-p                 |

| C <sub>(ON)</sub>              | On-capacitance output to GND  | -  | 42  | 45  | pF  | From O0~O3 to GND                                 |

| C <sub>(OFF)</sub>             | OFF-capacitance output to GND | -  | 22  | 25  | pF  |                                                   |

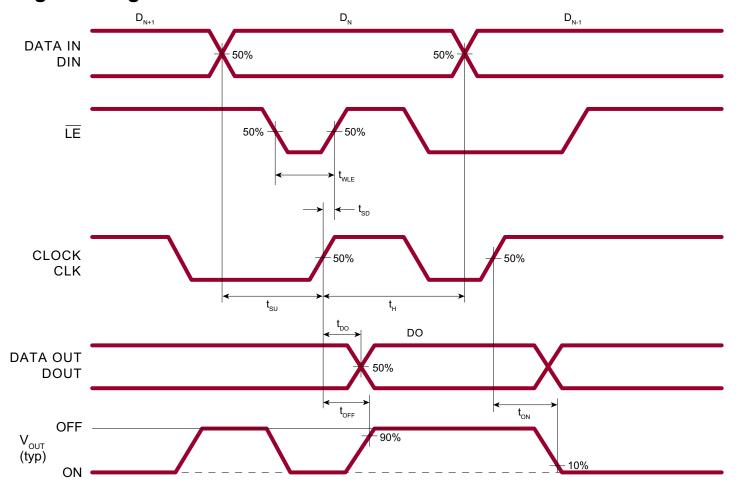

| f <sub>CLK</sub>               | Clock frequency               | 20 | 25  | -   | MHz |                                                   |

| t <sub>sd</sub>                | Setup time before LE rises    | 10 | -   | -   | ns  |                                                   |

| t <sub>H</sub>                 | Data hold time                | 10 | -   | -   | ns  |                                                   |

| t <sub>r</sub> /t <sub>f</sub> | CLK rise or fall time         | -  | -   | 5.0 | ns  |                                                   |

## AC Electrical Characteristics (cont.) (Over operating conditions unless otherwise specified, $V_{DD}$ = +5V, $T_j$ = 25°C)

| Sym              | Parameter                        |    | Тур | Max       | Unit | Conditions                                         |

|------------------|----------------------------------|----|-----|-----------|------|----------------------------------------------------|

| t <sub>wle</sub> | Time width of LE                 | 10 | -   |           | ns   |                                                    |

| t <sub>su</sub>  | Data setup time                  | 10 | -   |           | ns   |                                                    |

| t <sub>DO</sub>  | CLK delay time to data out       | -  | -   |           | ns   |                                                    |

| dv/dt            | Maximum V <sub>x</sub> slew rate | -  | -   |           | V/ns |                                                    |

| t <sub>on</sub>  | ON time delay                    | -  | 3.0 | 5.0       | μs   | From CLK rise 50% to the                           |

| t <sub>OFF</sub> | OFF time delay                   | -  | 3.0 | 5.0       | μs   | switch full on or off time, at $\overline{LE} = 0$ |

| V                | Spike of LV SW turning ON        | -  | 5.0 | 5.0 10 mV |      | 50Ω on O0~3 to GND                                 |

| V <sub>SPK</sub> | Spike of LV SW turning OFF       | -  | 5.0 | 10        | IIIV | 1kΩ on X0~3 to GND                                 |

# **Logic Timing Waveforms**

# T/R Switch Typical I-V Curve

## **Pin Description**

| Pin | Name | Description                                                                                                                             |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 00   | Low voltage analog switch channel 0 output                                                                                              |

| 2   | 01   | Low voltage analog switch channel 1 output                                                                                              |

| 3   | DIN  | Serial Data Input                                                                                                                       |

| 4   | CLK  | Shift register clock input                                                                                                              |

| 5   | VDD  | Positive voltage power supply +5V                                                                                                       |

| 6   | ĪĒ   | Latch-Enable input - the switch status latched at the rising edge of LE. When LE is low the shift registers data flow through the latch |

| 7   | DOUT | Serial Data Output                                                                                                                      |

| 8   | O2   | Low voltage analog switch channel 2 output                                                                                              |

| 9   | О3   | Low voltage analog switch channel 3 output                                                                                              |

| 10  | NC   | No internal connection                                                                                                                  |

| 11  | Х3   | T/R switch channel 3 high voltage input                                                                                                 |

| 12  | NC   | No internal connection                                                                                                                  |

| 13  | X2   | T/R switch channel 2 high voltage input                                                                                                 |

| 14  | NC   | No internal connection                                                                                                                  |

| 15  | X1   | T/R switch channel 1 high voltage input                                                                                                 |

| 16  | NC   | No internal connection                                                                                                                  |

| 17  | X0   | T/R switch channel 0 high voltage input                                                                                                 |

| 18  | NC   | No internal connection                                                                                                                  |

| DAP | GND  | The bottom thermal pad of DFN-18, Ground (0V)                                                                                           |

Note: DAP must be connected to the ground on the PCB.

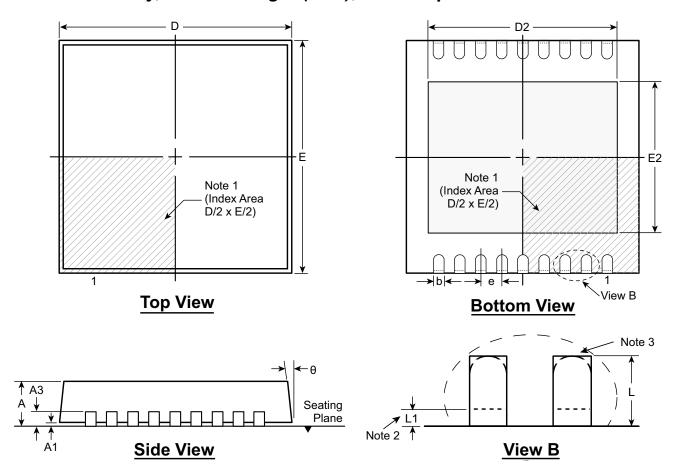

## 18-Lead DFN Package Outline (K6)

#### 5.00x5.00mm body, 1.00mm height (max), 0.50mm pitch

#### Notes:

- A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- 3. The inner tip of the lead may be either rounded or square.

| Symb           | ol  | Α    | A1   | А3          | b    | D     | D2                | E     | E2                | е           | L                 | L1    | θ          |

|----------------|-----|------|------|-------------|------|-------|-------------------|-------|-------------------|-------------|-------------------|-------|------------|

|                | MIN | 0.80 | 0.00 |             | 0.18 | 4.85* | 4.20 <sup>†</sup> | 4.85* | 3.50 <sup>†</sup> |             | 0.30 <sup>†</sup> | 0.00* | <b>0</b> o |

| Dimension (mm) | NOM | 0.90 | 0.02 | 0.20<br>REF | 0.25 | 5.00  | 4.35 <sup>†</sup> | 5.00  | 3.65 <sup>†</sup> | 0.50<br>BSC | 0.40†             | -     | -          |

| (111111)       | MAX | 1.00 | 0.05 |             | 0.30 | 5.15* | 4.45 <sup>†</sup> | 5.15* | 3.75 <sup>†</sup> |             | 0.50 <sup>†</sup> | 0.15  | 14°        |

JEDEC Registration MO-229, Variation VJJD-2, Issue C, Aug 2003.

Drawings not to scale.

Supertex Doc. #: DSPD-18DFNK65X5P050, Version A013111.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2014 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.

<sup>†</sup> This dimension differs from the JEDEC drawing.