# AB1 PROTOTYPING BOARD USER'S GUIDE

## 1. Summary

The AB1 prototyping board provides a 3 x 3.75" prototyping area (0.1" center through-hole) with access to all MCU I/O signals. Access to I/O signals is provided by a 96-pin, high density connector that mates directly to the expansion connector of C8051F020-TB, C8051F040-TB, C8051F060-TB, and C8051F120-TB target boards. A 128 kB SRAM is installed on the board which can be connected to the MCU's External Memory Interface by installing a single 2-pin jumper (included).

### 2. Features

- 96 pin 3 row connector

- 128 kB SRAM Part number IDT71V124

- SRAM disable jumper J1(open = disabled, closed = enabled)

- Duplicate of connector pins for easy access to signals

- Digital and analog supply and ground rails

## 3. SRAM Details

The IDT71V124SA12PH is a high-speed with 12 nanosecond access and cycle time static SRAM. For more further information on access and cycle times for this SRAM please refer to the IDT71V124 data sheet available at <a href="http://www.idt.com/docs/71V124SA\_DS\_30147.pdf">http://www.idt.com/docs/71V124SA\_DS\_30147.pdf</a>. To enable the SRAM jumper J1 must be installed and the /CS Chip Select pin must be pulled low. The SRAM utilizes the External Memory Interface from F02X and later devices, more information on using this interface can be found in Section 16 of the C8051F02x Data Sheet. When enabled the SRAM uses ports 5, 6, and 7 and the upper nibble of port 4. The pin-out is as follows:

| Signal Name | SRAM Pin(s)             | C8051F02XTB<br>Connection | Description           |

|-------------|-------------------------|---------------------------|-----------------------|

| /WE         | 12                      | P4.7                      | Write Enable          |

| /CS         | 5                       | P4.4(J1 closed)           | Chip Select           |

| /OE         | 28                      | P4.6                      | Output Enable         |

| VDD         | 8,24                    | +3 VD                     | Digital Power         |

| GND         | 9,25                    | GND                       | Digital Ground        |

| I/O0I/O7    | 6,7,10,11,22,23,26,27   | P7.0P7.7                  | Data Bus              |

| A0A7        | 1,2,3,4,13,14,15,16     | P6.0P6.7                  | Address Bus Low Byte  |

| A8A15       | 17,18,19,20,21,29,30,31 | P5.0P5.7                  | Address Bus High Byte |

| A16         | 32                      | P4.5                      | Bank Select           |

# 4. Hardware Setup

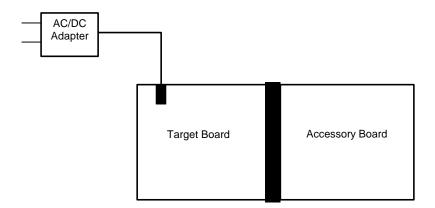

A compatible target board is connected to the accessory board as shown in Figure 1.

Figure 1. Hardware Setup

loT Portfolio www.silabs.com/loT

**SW/HW** <u>www.sila</u>bs.com/simplicity

Quality www.silabs.com/quality

Support and Community community.silabs.com

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadio®, EZRadio®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701