# Low Power 1.8V Dual Pixel FPD-Link (LVDS) Serializer

Check for Samples: DS90C187

# **FEATURES**

- 100 mW typical power consumption at 185 MHz (SIDO mode)

- Drives QXGA and WQXGA class displays

- Three operating modes:

- Single Pixel In, Single Pixel Out (SISO), 105MHz max

- Single Pixel In, Dual Pixel Out (SIDO), 185MHz

- Dual Pixel In, Dual Pixel Out (DIDO), 105MHz

- Supports 24 bit RGB, 48 bit RGB

- Optional low power mode supports 18 bit RGB, 36 bit RGB

- Supports 3D+C, 4D+C, 6D+C, 6D+2C, 8D+C, and 8D+2C LVDS configurations

- Compatible with FPD-Link, and FlatLink Deserializers

- 1.8V VDDIO and Core Supply

- Interfaces directly with 1.8V LVCMOS .

- Less than 1mW power consumption in Sleep Mode

- Spread Spectrum Clock Compatible

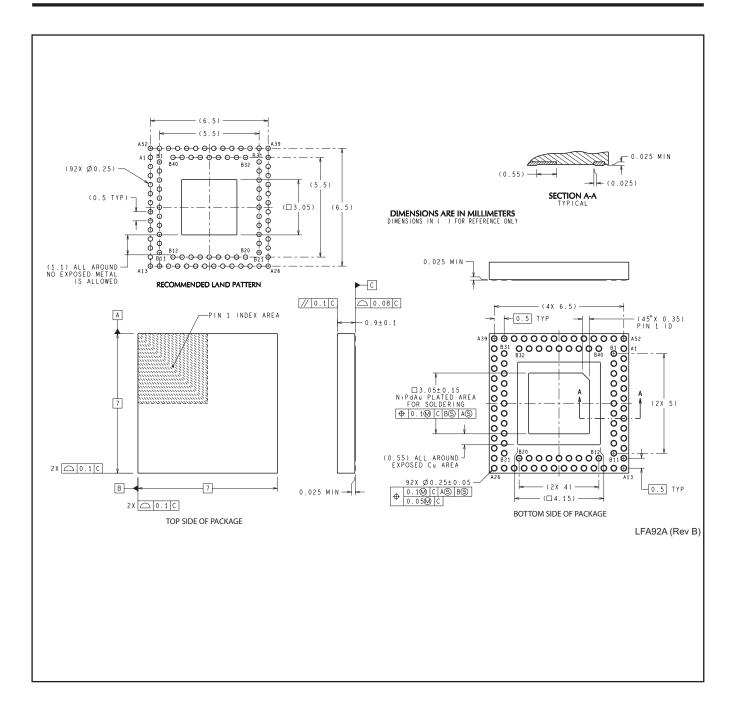

- Small 7mm x 7mm x 0.9 mm 92-pin dual row VQFN package

# APPLICATIONS

- **Media Tablet Devices**

- eBook, Notebooks, Laptops

- **Portable Display Monitors**

# DESCRIPTION

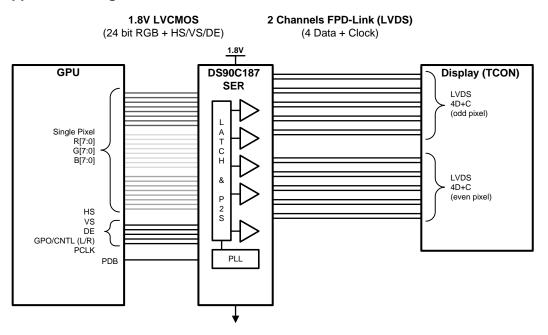

The DS90C187 is a Low Power Serializer for portable battery powered application that reduces the size of the RGB interface between the host GPU and the Display.

The DS90C187 Serializer is designed to support dual pixel data transmission between Host and Flat Panel Display up to QXGA 2048x1536 at 60Hz resolutions. The transmitter converts up to 48 bits (Dual Pixel 24 bit color) of 1.8V LVCMOS data into two channels of 4 data + clock (4D+C) reduced width interface LVDS compatible data streams.

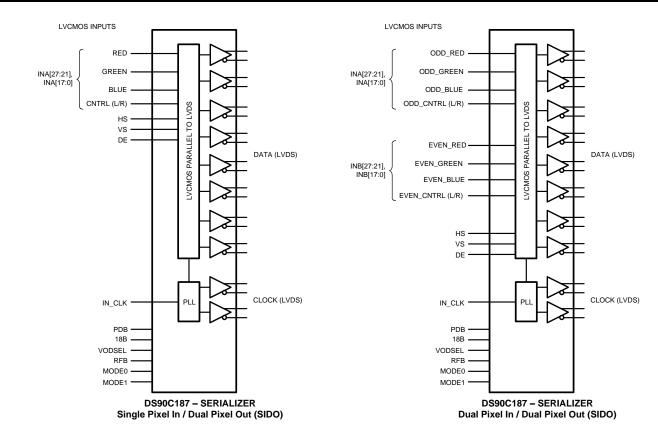

DS90C187 supports 3 modes of operation. In single pixel mode in/out mode, the device can drive up to SXGA+ 1400x1050 at 60Hz. In this mode, the device converts one bank of 24 bit RGB data to one channel of 4D+C LVDS data stream. In single pixel in / dual pixel out mode, the device can drive up to WUXGA+ 1920x1440 at 60Hz. In this configuration, the device provides single-to-dual pixel conversion and converts one bank of 24 bit RGB data into two channels of 4D+C LVDS streams at half the pixel clock rate. In dual pixel in / dual pixel out mode, the device can drive up to QXGA 2048x1536 at 60Hz or up to QSXGA 2560x2048 at 30Hz. In this mode, the device converts 2 channels of 24 bit RGB data into 2 channels of 4D+C LVDS streams. For all the modes, the device supports 18bpp and 24bpp color.

The DS90C187 is offered in a small 92 pin dual row VQFN package and features single 1.8V supply for minimal power dissipation.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

SNLS401A - FEBRUARY 2012 - REVISED APRIL 2012

www.ti.com

### **Typical Application Diagram**

Figure 1. Single Pixel In Dual Pixel Out (SIDO) Mode

### **Functional Block Diagrams**

#### SNLS401A - FEBRUARY 2012 - REVISED APRIL 2012

TEXAS INSTRUMENTS

www.ti.com

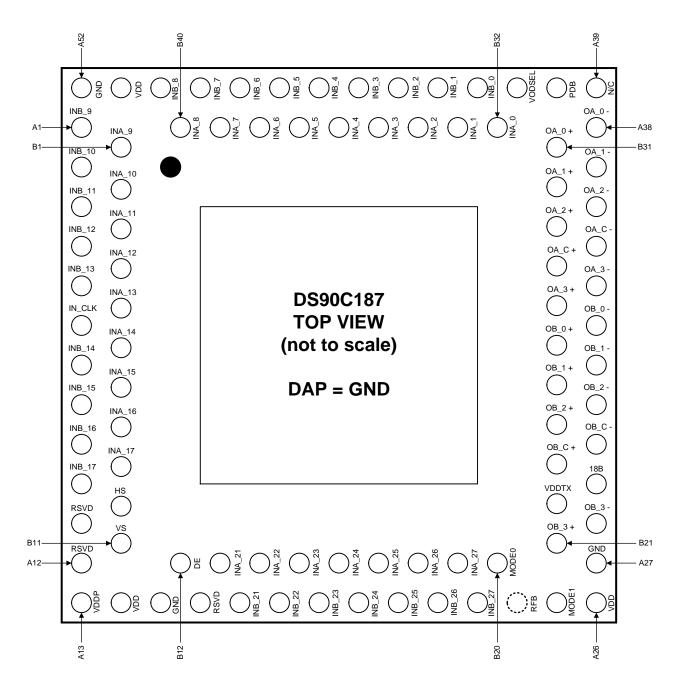

### CONNECTION DIAGRAM

### DS90C187 Pin Descriptions — Serializer

| Pin Name                                                 | I/O                      | No.                                      | Description                                                                                                                               |  |  |  |  |  |

|----------------------------------------------------------|--------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1.8V LVCMOS VID                                          | 1.8V LVCMOS VIDEO INPUTS |                                          |                                                                                                                                           |  |  |  |  |  |

| INA_[27:21],<br>INA_[17:9],<br>INA_[8:0]                 | I                        | B19-B13,<br>B9-B1,<br>B40-B32            | Channel A Data Inputs<br>Typically consists of 8 Red, 8 Green, 8 Blue and a general purpose or L/R control<br>bit.<br>Includes pull down. |  |  |  |  |  |

| INB_[27:21],<br>INB_[17:14],<br>INB_[13:9],<br>INB_[8:0] | I                        | A23-A17,<br>A10-A7,<br>A5-A1,<br>A50-A42 | Channel B Data Inputs<br>Typically consists of 8 Red, 8 Green, 8 Blue and a general purpose or L/R control<br>bit.<br>Includes pull down. |  |  |  |  |  |

### SNLS401A - FEBRUARY 2012 - REVISED APRIL 2012

# DS90C187 Pin Descriptions — Serializer (continued)

| Pin Name                                    | I/O         | No.                           | Description                                                                                                                                                              |

|---------------------------------------------|-------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS (INA_18),<br>VS (INA_19),<br>DE (INA_20) | I           | B10,<br>B11,<br>B12           | Video Control Signal Inputs -<br>HS = Horizontal Sync, VS = Vertical SYNC, and DE = Data Enable                                                                          |

| IN_CLK                                      | I           | A6                            | Pixel Input Clock<br>Includes pull down.                                                                                                                                 |

| 1.8V LVCMOS CO                              | NTROL INPUT | ſS                            |                                                                                                                                                                          |

| MODE0,<br>MODE1                             | I           | B20,<br>A25                   | Mode Control Inputs (MODE1, MODE0)<br>00 = Single In / Single Out<br>01 = Single In / Dual Out<br>10 = Dual In / Dual Out<br>11 = <b>Reserved</b><br>Includes pull down. |

| RFB                                         | I           | A24                           | Rising / Falling Clock Edge Select Input -<br>0 = Falling Edge, 1 = Rising Edge<br>Includes pull down.                                                                   |

| PDB                                         | I           | A40                           | Power Down (Sleep) Control Input -<br>0 = Sleep (Power Down mode), 1 = device active (enabled)<br>Includes pull down.                                                    |

| 18B                                         | I           | A29                           | 18 bit / 24 bit Control Input -<br>0 = 24 bit mode, 1 = 18 bit mode<br>Includes pull down.                                                                               |

| VODSEL                                      | I           | A41                           | VOD Level Select Input -<br>0 = Low swing, 1 = Normal swing<br>Includes pull down.                                                                                       |

| N/C                                         | I           | A39                           | no connect pin — leave open                                                                                                                                              |

| RSVD                                        | I           | A11, A12, A16                 | Reserved - Tie to Ground.                                                                                                                                                |

| LVDS OUTPUTS                                |             |                               |                                                                                                                                                                          |

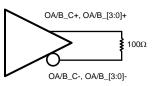

| OA_C+,<br>OA_C-                             | 0           | B28,<br>A35                   | Channel A LVDS Output Clock — Expects 100 $\Omega$ DC load.                                                                                                              |

| OA_[3:0]+,<br>OA_[3:0]-                     | 0           | B27, B29-B31<br>A34, A36-A38  | Channel A LVDS Output Data — Expects 100 $\Omega$ DC load.                                                                                                               |

| OB_C+,<br>OB_C-                             | 0           | B23,<br>A30                   | Channel B LVDS Output Clock — Expects 100 $\Omega$ DC load.                                                                                                              |

| OB_[3:0]+,<br>OB_[3:0]-                     | 0           | B21, B24-B26,<br>A28, A31-A33 | Channel B LVDS Output Data — Expects 100 $\Omega$ DC load.                                                                                                               |

| POWER and GRO                               | UND         |                               |                                                                                                                                                                          |

| V <sub>DDTX</sub>                           | Р           | B22                           | Power supply for LVDS Drivers, 1.8V.                                                                                                                                     |

| V <sub>DD</sub>                             | Р           | A14, A26, A51                 | Power supply pin for core, 1.8V.                                                                                                                                         |

| V <sub>DDP</sub>                            | Р           | A13                           | Power supply pin for PLL, 1.8V.                                                                                                                                          |

| GND                                         | G           | A15, A27, A52                 | Ground pins.                                                                                                                                                             |

| DAP                                         | G           | DAP                           | Connect DAP to Ground plane.                                                                                                                                             |

# DS90C187

### SNLS401A - FEBRUARY 2012 - REVISED APRIL 2012

Texas Instruments

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### Absolute Maximum Ratings <sup>(1)</sup>

| Supply Voltage (V <sub>CC</sub> )  | -0.3V to +2.5V      |                      |

|------------------------------------|---------------------|----------------------|

| LVCMOS Input Voltage               | -0.3V to VDD + 0.3V |                      |

| LVDS Driver Output Voltage         | -0.3V to +3.6V      |                      |

| LVDS Output Short Circuit Duration |                     | Continuous           |

| Junction Temperature               | +150°C              |                      |

| Storage Temperature                | -65°C to +150°C     |                      |

| Package Derating: θ <sub>JA</sub>  |                     | 35.1°C/W above +22°C |

|                                    | НВМ                 | > ±8 kV              |

| ESD Ratings                        | CDM                 | > ±1.25 kV           |

|                                    | MM                  | >±250 V              |

(1) "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

### **Recommended Operating Conditions**

|                                                 | Min  | Nom  | Max  | Unit              |

|-------------------------------------------------|------|------|------|-------------------|

| Supply Voltage                                  | 1.71 | 1.80 | 1.89 | V                 |

| Operating Free Air Temperature (T <sub>A)</sub> | -10  | +25  | +70  | °C                |

| Differential Load Impedance                     | 80   | 100  | 120  | Ω                 |

| Supply Noise Voltage                            |      |      | <90  | mV <sub>p-p</sub> |

## **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol          | Parameter                                                        | Con                                                                                    | ditions                                  | Min          | Тур          | Max                 | Unit                       |

|-----------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------|--------------|--------------|---------------------|----------------------------|

| LVCMOS          | DC SPECIFICATIONS                                                |                                                                                        |                                          | -            |              |                     |                            |

| VIH             | High Level Input Voltage                                         |                                                                                        |                                          | $0.65V_{DD}$ |              | V <sub>DD</sub>     | V                          |

| V <sub>IL</sub> | Low Level Input Voltage                                          |                                                                                        |                                          | GND          |              | 0.35V <sub>DD</sub> | V                          |

| I <sub>IN</sub> | Input Current                                                    | V <sub>IN</sub> = 0V or V <sub>DD</sub> =<br>1.71 V to 1.89 V                          |                                          | - 10         | ±1           | +10                 | μA                         |

| LVDS DRI        | VER DC SPECIFICATIONS                                            |                                                                                        |                                          |              |              |                     |                            |

| V <sub>OD</sub> | Differential Output Voltage                                      | R <sub>L</sub> = 100Ω<br>Figure 4                                                      | VODSEL = V <sub>IH</sub>                 | 160<br>(320) | 300<br>(600) | 450<br>(900)        | mV<br>(mV <sub>P-P</sub> ) |

|                 |                                                                  |                                                                                        | VODSEL = V <sub>IL</sub>                 | 110<br>(220) | 180<br>(360) | 300<br>(600)        | mV<br>(mV <sub>P-P</sub> ) |

| $\Delta V_{OD}$ | Change in V <sub>OD</sub> between<br>Complimentary Output States |                                                                                        |                                          |              |              | 50                  | mV                         |

| V <sub>OS</sub> | Offset Voltage                                                   |                                                                                        |                                          | 0.8          | 0.9          | 1.0                 | V                          |

| $\Delta V_{OS}$ | Change in V <sub>OS</sub> between<br>Complimentary Output States |                                                                                        |                                          |              |              | 50                  | mV                         |

| l <sub>os</sub> | Output Short Circuit Current                                     | V <sub>OUT</sub> = GND, VODS                                                           | SEL = V <sub>DD</sub>                    | -45          | -35          | -25                 | mA                         |

| SUPPLY C        | URRENT                                                           |                                                                                        |                                          | · · · ·      |              |                     |                            |

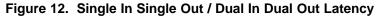

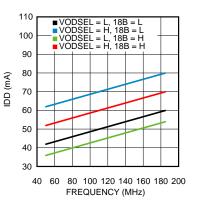

| IDDT1           | Serializer Worst Case Supply<br>Current (includes load current)  | Checkerboard pattern,<br>$R_L = 100 \Omega$ ,                                          | f = 105 MHz,<br>MODE[1:0] = 00<br>(SISO) |              | 60           | 85                  | mA                         |

| IDDT2           | _                                                                | $18B = V_{IL},$<br>VODSEL = V <sub>IH</sub> ,<br>V <sub>DD</sub> = 1.89 V,<br>Figure 2 | f = 185 MHz,<br>MODE[1:0] = 01<br>(SIDO) |              | 95           | 140                 | mA                         |

| IDDT3           |                                                                  |                                                                                        | f = 105 MHz,<br>MODE[1:0] = 10<br>(DIDO) |              | 100          | 150                 | mA                         |

#### SNLS401A-FEBRUARY 2012-REVISED APRIL 2012

### **Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol          | Parameter Conditions                      |                                                     | Min                                                                                                                          | Тур | Max | Unit |    |

|-----------------|-------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|----|

| IDDTP Serialize | Serializer Supply Current PRBS-7          | MODE[1:0] = 01<br>(SIDO),<br>f = 150 MHz,           | $18B = V_{IL},$<br>VODSEL = V <sub>IL</sub> ,<br>VDD = 1.8                                                                   |     | 55  |      | mA |

|                 |                                           | $R_L = 100 \Omega$ ,<br>PRBS-7 Pattern<br>Figure 13 | $\begin{array}{l} 18\text{B} = \text{V}_{\text{IL}},\\ \text{VODSEL} = \text{V}_{\text{IH}},\\ \text{VDD} = 1.8 \end{array}$ |     | 75  |      | mA |

|                 |                                           |                                                     | $\begin{array}{l} 18\text{B} = \text{V}_{\text{IH}},\\ \text{VODSEL} = \text{V}_{\text{IL}},\\ \text{VDD} = 1.8 \end{array}$ |     | 49  |      | mA |

|                 |                                           |                                                     | $18B = V_{IH},$<br>VODSEL = $V_{IH},$<br>VDD = 1.8                                                                           |     | 65  |      | mA |

| IDDTG           | Serializer Supply Current 16<br>Grayscale | MODE[1:0] = 01<br>(SIDO),<br>f = 150 MHz,           | $18B = V_{IL},$<br>VODSEL = $V_{IL},$<br>VDD = 1.8                                                                           |     | 53  |      | mA |

|                 |                                           | R <sub>L</sub> = 100 Ω,<br>16 Grayscale<br>Pattern  | $18B = V_{IL},$<br>VODSEL = V <sub>IH</sub> ,<br>VDD = 1.8                                                                   |     | 71  |      | mA |

|                 |                                           | $18B = V_{IH},$<br>VODSEL = $V_{IL},$<br>VDD = 1.8  |                                                                                                                              | 48  |     | mA   |    |

|                 |                                           |                                                     | $18B = V_{IH},$<br>VODSEL = V <sub>IH</sub> ,<br>VDD = 1.8                                                                   |     | 63  |      | mA |

| IDDZ            | Power Down Supply Current                 | PDB = GND                                           |                                                                                                                              |     | 18  | 200  | μA |

### **Recommended Input Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol   | Parameter                     |                      | Min   | Тур  | Max   | Unit |

|----------|-------------------------------|----------------------|-------|------|-------|------|

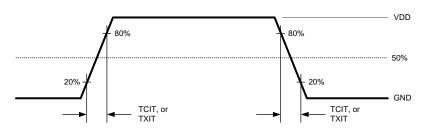

| TCIT     | IN_CLK Transition Time        | MODE[1:0] = 00 or 10 | 1.0   | Т    | 4.0   | ns   |

| Figure 6 |                               | MODE[1:0] = 01       | 1.0   |      | 2.0   | ns   |

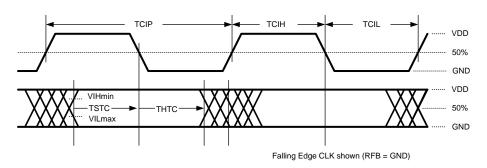

| TCIP     | IN_CLK Period                 | MODE[1:0] = 00 or 10 | 9.53  | Т    | 40    | ns   |

|          | Figure 7                      | MODE[1:0] = 01       | 5.40  | Т    | 20    | ns   |

| TCIH     | IN_CLK High Time              | Figure 7             | 0.35T | 0.5T | 0.65T | ns   |

| TCIL     | IN_CLK Low Time               |                      | 0.35T | 0.5T | 0.65T | ns   |

| TXIT     | INA_x & INB_x Transition Time | Figure 6             | 1.5   |      | 0.3T  | ns   |

## **Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                                                   |                       | Min | Тур      | Max | Unit |

|--------|-------------------------------------------------------------|-----------------------|-----|----------|-----|------|

| TSTC   | INn_x Setup to IN_CLK                                       | Figure 7              | 0   |          |     | ns   |

| THTC   | INn_x Hold from IN_CLK                                      |                       | 2.5 |          |     | ns   |

| LLHT   | LVDS Low-to-High Transition Time<br>Figure 5 <sup>(1)</sup> |                       |     | 0.18     | 0.5 | ns   |

| LHLT   | LVDS High-to-Low Transition Time<br>Figure 5 <sup>(1)</sup> |                       |     | 0.18     | 0.5 | ns   |

| TBIT   | LVDS Output Bit Width                                       | MODE[1:0] = 00, or 10 |     | 1/7 TCIP |     | ns   |

|        |                                                             | MODE[1:0] = 01        |     | 2/7 TCIP |     | ns   |

(1) Parameter is guaranteed by characterization and is not tested at final test.

SNLS401A - FEBRUARY 2012 - REVISED APRIL 2012

**EXAS** ISTRUMENTS

www.ti.com

# **Switching Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                                                  |                                                  | Min | Тур               | Max               | Unit |

|--------|------------------------------------------------------------|--------------------------------------------------|-----|-------------------|-------------------|------|

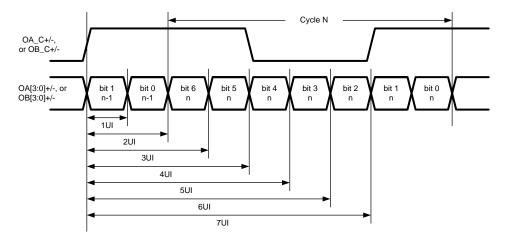

| TPPOS0 | Transmitter Output Pulse Positions Normalized for Bit 0    | Figure 10                                        |     | 1                 |                   | UI   |

| TPPOS1 | Transmitter Output Pulse Positions Normalized for Bit 1    |                                                  |     | 2                 |                   | UI   |

| TPPOS2 | Transmitter Output Pulse Positions Normalized for Bit 2    |                                                  |     | 3                 |                   | UI   |

| TPPOS3 | Transmitter Output Pulse Positions Normalized for Bit 3    |                                                  |     | 4                 |                   | UI   |

| TPPOS4 | Transmitter Output Pulse Positions Normalized for Bit 4    |                                                  |     | 5                 |                   | UI   |

| TPPOS5 | Transmitter Output Pulse Positions Normalized for Bit 5    |                                                  |     | 6                 |                   | UI   |

| TPPOS6 | Transmitter Output Pulse Positions Normalized<br>for Bit 6 |                                                  |     | 7                 |                   | UI   |

| ΔTPPOS | Variation in Transmitter Pulse Position (Bit 6 — Bit 0)    |                                                  |     | ±0.06             |                   | UI   |

| TCCS   | LVDS Channel to Channel Skew                               |                                                  |     | 110               |                   | ps   |

| TJCC   | Jitter Cycle-to-Cycle                                      | MODE0, MODE1 = 0,<br>f = 105 MHz,<br>(1)         |     | 0.028             | 0.035             | UI   |

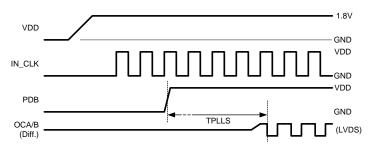

| TPLLS  | Phase Lock Loop Set (Enable Time)                          | Figure 8                                         |     |                   | 1                 | ms   |

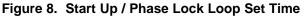

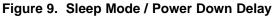

| TPDD   | Powerdown Delay                                            | Figure 9<br>(2)                                  |     |                   | 100               | ns   |

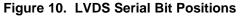

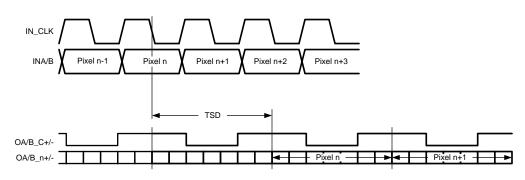

| TSD    | Latency Delay                                              | MODE0 = 0,<br>MODE1 = 1 or 0<br>Figure 11<br>(3) |     | 2*TCIP +<br>10.54 | 2*TCIP +<br>13.96 | ns   |

| TLAT   | Latency Delay for Single Pixel In / Dual Pixel Out<br>Mode | MODE0 = 1,<br>MODE1 = 0<br>Figure 11<br>(3)      |     | 9*TCIP +<br>4.19  | 9*TCIP +<br>6.36  | ns   |

|        |                                                            |                                                  |     |                   |                   |      |

(2) Parameter is guaranteed by design and is not tested at final test.(3) Parameter is guaranteed by characterization and is not tested at final test.

SNLS401A-FEBRUARY 2012-REVISED APRIL 2012

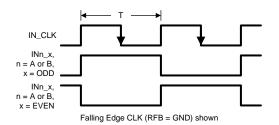

### AC Timing Diagrams

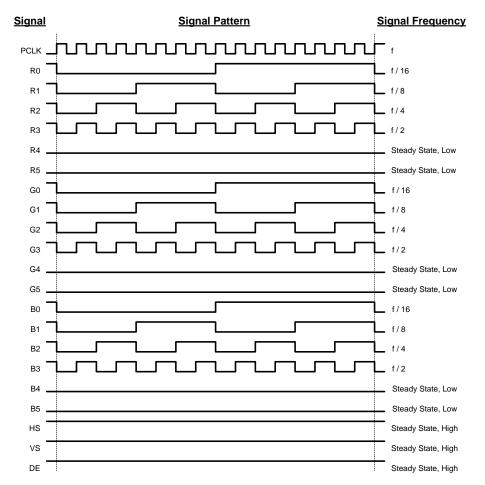

- A. The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and LVCMOS/ I/O.

- B. Figure 2 and Figure 3 show a falling edge data strobe (IN\_CLK).

Figure 2. Checker Board Test Pattern

- A. The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and LVCMOS/ I/O.

- B. Recommended pin to signal mapping for 18 bits per pixel, customer may choose to define differently. The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

- C. Figure 2 and Figure 3 show a falling edge data strobe (IN\_CLK).

### Figure 3. "16 Gray Scale" Test Pattern (Falling Edge Clock shown)

# **AC Timing Diagrams (continued)**

Figure 4. DS90C187 (Transmitter) LVDS Output Load

Figure 5. LVDS Output Transition Times

Figure 6. LVCMOS Input Transition Times

Figure 7. LVCMOS Input Setup/Hold and Clock High/Low Times (Falling Edge Strobe)

#### SNLS401A-FEBRUARY 2012-REVISED APRIL 2012

Figure 11. Single In Dual Out Mode Timing and Latency

SNLS401A - FEBRUARY 2012 - REVISED APRIL 2012

AC Timing Diagrams (continued)

Figure 13. Typ Current Draw — Single In/Dual Out Mode — PRBS-7 Data Pattern

Figure 14. Typ Current Draw — Single In/Single Out Mode — PRBS-7 Data Pattern

## LVDS INTERFACE / TFT COLOR DATA RECOMMENDED MAPPING

Different color mapping options exist. Check with the color mapping of the Deserializer / TCON device that is used to ensure compatible mapping for the application. The DS90C187 supports three modes of operation for single and dual pixel applications supporting either 24bpp or 18bpp color depths.

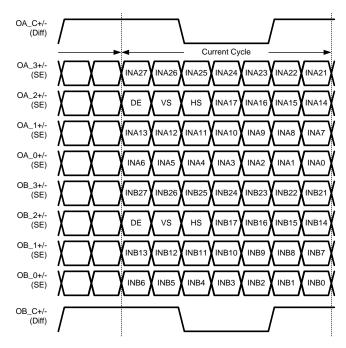

In the Dual Pixel / 24bpp mode, eight LVDS data lines are provided along with two LVDS clock lines (8D+2C). The Deserializer may utilize one or two clock lines. The 53 bit interface typically assigns 24 bits to RGB for the odd pixel, 24 bits to RGB for the even pixel, 3 bits for the video control signals (HS, VS and DE), 1 bit for odd pixel and 1 bit for even pixel which can be ignored or used for general purpose data, control or L/R signaling.

A reduced width input interface is also supported with a Single-to-Dual Pixel conversion where the data is presented at double rate (same clock edge, 2X speed, see Figure 11) and the DE transition is used is flag the first pixel. Also note in both 8D+2C configurations, the three video control signals are sent over **both** the A and B outputs. The DES / TCON may recover one set, or both depending upon its implementation. The Dual Pixel / 24bpp 8D+2C LVDS Interface Mapping is shown in Figure 15.

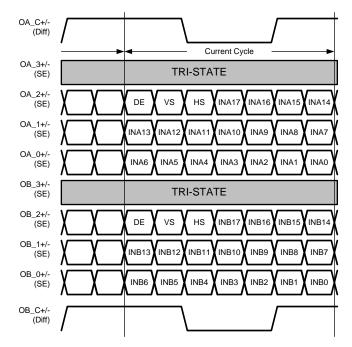

A Dual Pixel / 18bpp mode is also supported. In this configuration OA3 and OB3 LVDS output channels are placed in TRI-STATE® to save power. Their respective inputs are ignored. (Figure 16)

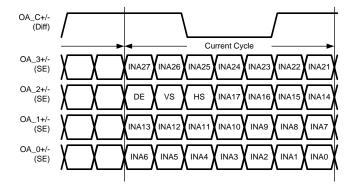

In the Single Pixel / 24bpp mode, four LVDS data lines are provided along with a LVDS clock line (4D+C). The 28 bit interface typically assigns 24 bits to RGB color data, 3 bits to video control (HS, VS and DE) and one spare bit can be ignored, used for L/R signaling or function as a general purpose bit. The Single Pixel / 24bpp 4D+C LVDS Interface Mapping is shown in Figure 17.

12 Submit Documentation Feedback

SNLS401A - FEBRUARY 2012 - REVISED APRIL 2012

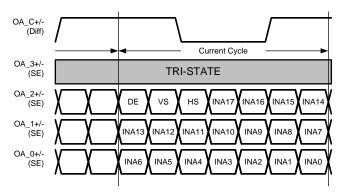

A Single Pixel / 18bpp mode is also supported. In this configuration the OA3 LVDS output channel is placed in TRI-STATE® to save power. Its respective inputs are ignored. (Figure 18)

Figure 15. Dual Pixel / 24bpp LVDS Mapping

Figure 16. Dual Pixel / 18bpp LVDS Mapping

SNLS401A-FEBRUARY 2012-REVISED APRIL 2012

Figure 17. Single Pixel / 24bpp LVDS Mapping

Figure 18. Single Pixel / 18bpp LVDS Mapping

#### **COLOR MAPPING INFORMATION**

A defacto color mapping is shown next. Different color mapping options exist. Check with the color mapping of the Deserializer / TCON device that is used to ensure compatible mapping for the application.

| DS90C187 Input | Color Mapping | Note |

|----------------|---------------|------|

| INA_22         | R7            | MSB  |

| INA_21         | R6            |      |

| INA_5          | R5            |      |

| INA_4          | R4            |      |

| INA_3          | R3            |      |

| INA_2          | R2            |      |

| INA_1          | R1            |      |

| INA_0          | R0            | LSB  |

| INA_24         | G7            | MSB  |

| INA_23         | G6            |      |

| INA_11         | G5            |      |

| INA_10         | G4            |      |

| INA_9          | G3            |      |

| INA_8          | G2            |      |

| INA_7          | G1            |      |

| INA_6          | G0            | LSB  |

| INA_26         | B7            | MSB  |

#### Table 1. Single Pixel Input / 24bpp / MSB on CH3

# SNLS401A-FEBRUARY 2012-REVISED APRIL 2012

## Table 1. Single Pixel Input / 24bpp / MSB on CH3 (continued)

| DS90C187 Input | Color Mapping | Note            |

|----------------|---------------|-----------------|

| INA_25         | B6            |                 |

| INA_17         | B5            |                 |

| INA_16         | B4            |                 |

| INA_15         | B3            |                 |

| INA_14         | B2            |                 |

| INA_13         | B1            |                 |

| INA_12         | B0            |                 |

| DE             | DE            | Data Enable*    |

| VS             | VS            | Vertical Sync   |

| HS             | HS            | Horizontal Sync |

| INA_27         | GP            | General Purpose |

# Table 2. Single Pixel Input / 24bpp / LSB on CH3

| DS90C187 Input | Color Mapping | Note            |

|----------------|---------------|-----------------|

| INA_5          | R7            | MSB             |

| INA_4          | R6            |                 |

| INA_3          | R5            |                 |

| INA_2          | R4            |                 |

| INA_1          | R3            |                 |

| INA_0          | R2            |                 |

| INA_22         | R1            |                 |

| INA_21         | R0            | LSB             |

| INA_11         | G7            | MSB             |

| INA_10         | G6            |                 |

| INA_9          | G5            |                 |

| INA_8          | G4            |                 |

| INA_7          | G3            |                 |

| INA_6          | G2            |                 |

| INA_24         | G1            |                 |

| INA_23         | G0            | LSB             |

| INA_17         | B7            | MSB             |

| INA_16         | B6            |                 |

| INA_15         | B5            |                 |

| INA_14         | B4            |                 |

| INA_13         | B3            |                 |

| INA_12         | B2            |                 |

| INA_26         | B1            |                 |

| INA_25         | B0            |                 |

| DE             | DE            | Data Enable*    |

| VS             | VS            | Vertical Sync   |

| HS             | HS            | Horizontal Sync |

| INA_27         | GP            | General Purpose |

SNLS401A - FEBRUARY 2012 - REVISED APRIL 2012

www.ti.com

| DS90C187 Input | Color Mapping | Note            |

|----------------|---------------|-----------------|

| INA_5          | R5            | MSB             |

| INA_4          | R4            |                 |

| INA_3          | R3            |                 |

| INA_2          | R2            |                 |

| INA_1          | R1            |                 |

| INA_0          | R0            | LSB             |

| INA_11         | G5            | MSB             |

| INA_10         | G4            |                 |

| INA_9          | G3            |                 |

| INA_8          | G2            |                 |

| INA_7          | G1            |                 |

| INA_6          | G0            | LSB             |

| INA_17         | B5            | MSB             |

| INA_16         | B4            |                 |

| INA_15         | B3            |                 |

| INA_14         | B2            |                 |

| INA_13         | B1            |                 |

| INA_12         | B0            |                 |

| DE             | DE            | Data Enable*    |

| VS             | VS            | Vertical Sync   |

| HS             | HS            | Horizontal Sync |

# Table 3. Single Pixel Input / 18bpp

### Table 4. Dual Pixel Input / 24bpp

| DS90C187 Input | Color Mapping | Note |

|----------------|---------------|------|

| INA 22         | O R7          | MSB  |

| INA 21         | 0_R6          |      |

| INA 5          | 0 R5          |      |

| INA 4          | 0_R4          |      |

| INA 3          | <br>O_R3      |      |

| INA 2          | 0 R2          |      |

| INA_1          | <br>O_R1      |      |

| INA_0          | O_R0          | LSB  |

| INA_24         | O_G7          | MSB  |

| INA_23         | O_G6          |      |

| INA_11         | O_G5          |      |

| INA_10         | O_G4          |      |

| INA_9          | O_G3          |      |

| INA_8          | O_G2          |      |

| INA_7          | 0_G1          |      |

| INA_6          | O_G0          | LSB  |

| INA_26         | O_B7          | MSB  |

| INA_25         | O_B6          |      |

| INA_17         | O_B5          |      |

| INA_16         | O_B4          |      |

| INA_15         | O_B3          |      |

| INA_14         | O_B2          |      |

| INA_13         | O_B1          |      |

SNLS401A-FEBRUARY 2012-REVISED APRIL 2012

#### www.ti.com

| DS90C187 Input | Color Mapping | Note            |

|----------------|---------------|-----------------|

| INA_12         | O_B0          |                 |

| INB_22         | E_R7          |                 |

| INB_21         | E_R6          |                 |

| INB_5          | E_R5          |                 |

| INB_4          | E_R4          |                 |

| INB_3          | E_R3          |                 |

| INB_2          | E_R2          |                 |

| INB_1          | E_R1          |                 |

| INB_0          | E_R0          |                 |

| INB_24         | E_G7          |                 |

| INB_23         | E_G6          |                 |

| INB_11         | E_G5          |                 |

| INB_10         | E_G4          |                 |

| INB_9          | E_G3          |                 |

| INB_8          | E_G2          |                 |

| INB_7          | E_G1          |                 |

| INB_6          | E_G0          |                 |

| INB_26         | E_B7          |                 |

| INB_25         | E_B6          |                 |

| INB_17         | E_B5          |                 |

| INB_16         | E_B4          |                 |

| INB_15         | E_B3          |                 |

| INB_14         | E_B2          |                 |

| INB_13         | E_B1          |                 |

| INB_12         | E_B0          |                 |

| DE             | DE            | Data Enable*    |

| VS             | VS            | Vertical Sync   |

| HS             | HS            | Horizontal Sync |

| INA_27         | GP            | General Purpose |

| INB_27         | GP            | General Purpose |

# Table 4. Dual Pixel Input / 24bpp (continued)

## FUNCTIONAL DESCRIPTION

DS90C187 converts a wide parallel LVCMOS input bus into banks of FPD-Link LVDS data. The device can be configured to support RGB-888 (24 bit color) or RGB-666 (18 bit color) in three main configurations: single pixel in / single pixel out; single pixel out; dual pixel out; dual pixel in / dual pixel out. The DS90C187 has several power saving features including: selectable VOD, 18 bit / 24 bit mode select, and a power down pin control.

### **Device Configuration**

The MODE0 and MODE1 pins are used to configure the DS90C187 into the three main operation modes as shown in the table below.

| MODE1 | MODE0 | CONFIGURATION                                  |

|-------|-------|------------------------------------------------|

| 0     | 0     | Single Pixel Input, Single Pixel Output (SISO) |

| 0     | 1     | Single Pixel Input, Dual Pixel Output (SIDO)   |

| 1     | 0     | Dual Pixel Input, Dual Pixel Output (DIDO)     |

| 1     | 1     | RESERVED                                       |

| Table 5  | Mode | Configurations |

|----------|------|----------------|

| Table J. | woue | Connyurations  |

SNLS401A - FEBRUARY 2012 - REVISED APRIL 2012

www.ti.com

# Single Pixel Input / Single Pixel Output

When MODE0 and MODE1 are both set to low, data from INA\_[27:0], HS, VS and DE is serialized and driven out on OA\_[3:0]+/- with OA\_C+/-. If 18B\_MODE is LOW, then OA\_3+/- is powered down and the corresponding LVCMOS input signals are ignored.

In this configuration IN\_CLK can range from 25 MHz to 105 MHz, resulting in a total maximum payload of 700 Mbps (28 bits \* 25MHz) to 2.94 Gbps (28 bits \* 105 MHz). Each LVDS driver will operate at a speed of 7 bits per input clock cycle, resulting in a serial line rate of 175 Mbps to 735 Mbps. OA\_C+/- will operate at the same rate as IN\_CLK with a duty cycle ratio of 57:43.

## Single Pixel Input / Dual Pixel Output

When MODE0 is HIGH and MODE1 is LOW, data from INA\_[27:0], HS, VS and DE is serialized and driven out on OA\_[3:0]+/- and OB\_[3:0]+/- with OA\_C+/- and OB\_C+/-. If 18B\_MODE is LOW, then OA\_3+/- and OB\_3+/are powered down and the corresponding LVCMOS input signals are ignored. The input LVCMOS data is split into odd and even pixels starting with the odd (first) pixel outputs OA\_[3:0]+/- and then the even (second) pixel outputs OB\_[3:0]+/-. The splitting of the data signals starts with DE (data enable) transitioning from logic LOW to HIGH indicating active data (see Figure 11). **The number of clock cycles during blanking must be an EVEN number.** This configuration will allow the user to interface with two FPD-Link receivers or other dual pixel inputs.

In this configuration IN\_CLK can range from 50 MHz to 185 MHz, resulting in a total maximum payload of 1.4 Gbps (28 bits \* 50 MHz) to 5.18 Gbps (28 bits \* 185 MHz). Each LVDS driver will operate at a speed of 7 bits per 2 input clock cycles, resulting in a serial line rate of 175 Mbps to 647.5 Mbps. OA\_C+/- and OA\_B+/- will operate at ½ the rate as IN\_CLK with a duty cycle ratio of 57:43.

### Dual Pixel Input / Dual Pixel Output

When MODE0 is LOW and MODE1 is set to HIGH, data from INA\_[27:0], HS, VS and DE is serialized and driven out on OA\_[3:0]+/- with OA\_C+/-, while data from INB\_[27:0], HS, VS and DE is serializer and driven out on OB\_[3:0]+/- with OB\_C+/-. If 18B\_MODE is LOW, then OA\_3+/- and OB\_3+/- is powered down and the corresponding LVCMOS input signals are ignored.

In this configuration IN\_CLK can range from 25 MHz to 105 MHz, resulting in a total maximum payload of 1.325 Gbps (53 bits \* 25 MHz) to 5.565 Gbps (53 bits \* 105 MHz). Each LVDS driver will operate at a speed of 7 bits per input clock cycle, resulting in a serial line rate of 175 Mbps to 735 Mbps. OA\_C+/- and OB\_C+/- will operate at the same rate as IN\_CLK with a duty cycle ratio of 57:43.

### Pixel Clock Edge Select (RFB)

The RFB pin determines the edge that the input LVCMOS data is latched on. If RFB is HIGH, input data is latched on the RISING EDGE of the pixel clock (IN\_CLK). If RFB is LOW, the input data is latched on the FALLING EDGE of the pixel clock. Note: This can be set independently of receiver's output clock strobe.

| RFB | Result       |

|-----|--------------|

| 0   | FALLING edge |

| 1   | RISING edge  |

### Table 6. Pixel Clock Edge

### Power Management

The DS90C187 has several features to assist with managing power consumption. The device can be configured through the MODE0 and MODE1 control pins to enable only the required number of LVDS drivers for each application. The 18B\_MODE pin allows the DS90C187 to power down the unused LVDS driver(s) for RGB-666 (18 bit color) applications for an additional level of power management. If no clock is applied to the IN\_CLK pin, the DS90C187 will enter a low power state. To place the DS90C187 in its lowest power state, the device can be powered down by driving the PDB pin to LOW.

### Sleep Mode (PDB)

The DS90C187 provides a power down feature. When the device has been powered down, current draw through the supply pins is minimized and the PLL is shut down. The LVDS drivers are also powered down with their outputs pulled to GND through  $100\Omega$  resistors (not TRI-STATE®).

# SNLS401A-FEBRUARY 2012-REVISED APRIL 2012

#### Table 7. Power Down Select

| PDB | Result               |

|-----|----------------------|

| 0   | SLEEP Mode (default) |

| 1   | ACTIVE (enabled)     |

### LVDS Outputs

The DS90C187's LVDS drivers are compatible with ANSI/TIA/EIA-644-A LVDS receivers. The LVDS drivers can output a power saving low  $V_{OD}$ , or a high  $V_{OD}$  to enable longer trace and cable lengths by configuring the VODSEL pin.

Table 8 VOD Select

| Table 0. VOD Select |                    |  |  |  |  |  |  |

|---------------------|--------------------|--|--|--|--|--|--|

| VODSEL              | Result             |  |  |  |  |  |  |

| 0                   | ±180 mV (360 mVpp) |  |  |  |  |  |  |

| 1                   | ±300 mV (600 mVpp) |  |  |  |  |  |  |

Any unused LVDS outputs that are not powered down or put into TRI-STATE® due to the MODE0, MODE1, or 18B pins should be externally terminated differentially with a 100 ohm resistor. For example, when driving a timing controller (TCON) that only requires an 8D + C LVDS interface, rather than 8D + 2C, the unused clock line should be terminated near the package of the DS90C187. For more information regarding the output state of unused LVDS drivers, refer to the next section, 18 bit / 24 bit Color Mode (18B). For more information regarding the electrical characteristics of the LVDS outputs, refer to the LVDS DC Characteristics and LVDS Switching Specifications.

### 18 bit / 24 bit Color Mode (18B)

The 18B pin can be used to further save power by powering down the 4th LVDS driver in each used bank when the application requires only 18 bit color or 3D+C LVDS. Set the 18B pin to logic HIGH to TRI-STATE® OA\_3+/- and OB\_3+/- (if the device is configured for dual pixel output). For 24 bit color applications this pin should be set to logic LOW. Note that the power down function takes priority over the TRI-STATE® function. So if the device is configured for 18 bit color Single Pixel In/Single Pixel Out, LVDS channel OB\_3+/- will be powered down and not TRI-STATE®. If an LVDS driver is powered down, each output terminal is pulled low by a 100 ohm resistor to ground.

#### Table 9. Color DepthConfigurations

| 18B | Result                    |

|-----|---------------------------|

| 0   | 24bpp, LVDS 4D+C or 8D+2C |

| 1   | 18bpp, LVDS 3D+C or 6D+2C |

### **LVCMOS Inputs**

The DS90C187 has two banks of 24 data inputs, one set of video control signal (HS, VS and DE) inputs and several device configuration LVCMOS pins. All LVCMOS input pins are designed for 1.8V LVCMOS logic. All LVCMOS inputs, including clock, data and configuration pins, have an internal pull down resistor to set a default state. If any inputs are unused, they can be left as no connect (NC) or connected to ground.

# **APPLICATIONS INFORMATION**

### **Power Up Sequence**

The  $V_{DD}$  power supply pins do not require a specific power on sequence and can be powered on in any order. However, the PDB pin should only be set to logic HIGH once the power sent to all supply pins is stable. Active clock and data inputs should not be applied to the DS90C187 until all of the input power pins have been powered on, settled to the recommended operating voltage and the PDB pin has be set to logic HIGH.

The user experience can be impacted by the way a system powers up and powers down an LCD screen. The following sequence is recommended:

Power up sequence (DS90C187 PDB input initially LOW):

- 1. Ramp up LCD power (maybe 0.5ms to 10ms) but keep backlight turned off.

- 2. Wait for additional 0-200ms to ensure display noise won't occur.

- 3. Toggle DS90C187 power down pin to PDB =  $V_{IH}$ .

- 4. Enable video source output; start sending black video data.

- 5. Send >1ms of black video data; this allows the DS90C187 to be phase locked, and the display to show black data first.

- 6. Start sending true image data.

- 7. Enable backlight.

Power Down sequence (DS90C187 PDB input initially HIGH):

- 1. Disable LCD backlight; wait for the minimum time specified in the LCD data sheet for the backlight to go low.

- 2. Video source output data switch from active video data to black image data (all visible pixel turn black); drive this for >2 frame times.

- 3. Set DS90C187 power down pin to PDB = GND.

- 4. Disable the video output of the video source.

- 5. Remove power from the LCD panel for lowest system power.

## Power Supply Filtering

The DS90C187 has several power supply pins at 1.8V. It is important that these pins all be connected and properly bypassed. Bypassing should consist of at least one  $0.1\mu$ F capacitor placed on each pin, with an additional  $4.7\mu$ F -  $22\mu$ F capacitor placed on the PLL supply pin (VDDPLL).  $0.01\mu$ F capacitors are typically recommended for each pin. Additional filtering including ferrite beads may be necessary for noisy systems. It is recommended to place a 0 ohm resistor at the bypass capacitors that connect to each power pin to allow for additional filtering if needed. A large bulk capacitor is recommended at the point of power entry. This is typically in the  $50\mu$ F —  $100\mu$ F range.

### Layout Guidelines

Circuit board layout and stack-up for the LVDS serializer devices should be designed to provide low-noise power feed to the device. Good layout practice will also separate high frequency or high-level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. Power system performance may be greatly improved by using thin dielectrics (2 to 4 mils) for power / ground sandwiches. This arrangement provides plane capacitance for the PCB power system with low-inductance parasitics, which has proven especially effective at high frequencies, and makes the value and placement of external bypass capacitors less critical. This practice is easier to implement in dense pcbs with many layers and may not be practical in simpler boards. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range of 0.01 uF to 0.1 uF. Tantalum capacitors may be in the 2.2 uF to 10 uF range. Voltage rating of the tantalum capacitors should be at least 5X the power supply voltage being used.

Surface mount capacitors are recommended due to their smaller parasitics. When using multiple capacitors per supply pin, locate the smaller value closer to the pin. It is recommended to connect power and ground pins directly to the power and ground planes with bypass capacitors connected to the plane with vias on both ends of the capacitor.

20 Submit Documentation Feedback

#### SNLS401A-FEBRUARY 2012-REVISED APRIL 2012

A small body size X7R chip capacitor, such as 0603, is recommended for external bypass. Its small body size reduces the parasitic inductance of the capacitor. The user must pay attention to the resonance frequency of these external bypass capacitors, usually in the range of 20-30 MHz. To provide effective bypassing, multiple capacitors are often used to achieve low impedance between the supply rails over the frequency of interest. At high frequency, it is also a common practice to use two vias from power and ground pins to the planes, reducing the impedance at high frequency. Some devices provide separate power and ground pins for different portions of the circuit. This is done to isolate switching noise effects between different sections of the circuit. Separate planes on the PCB are typically not required. Pin Description tables typically provide guidance on which circuit blocks are connected to which power pin pairs. In some cases, an external filter many be used to provide clean power to sensitive circuits such as PLLs.

Use at least a four layer board with a power and ground plane. Locate LVCMOS signals away from the LVDS lines to prevent coupling from the LVCMOS lines to the LVDS lines. Closely coupled differential lines of 100 Ohms are typically recommended for LVDS interconnect. The closely coupled lines help to ensure that coupled noise will appear as common mode and thus is rejected by the receivers. The tightly coupled lines will also radiate less.

Information on the VQFN package is provided in Application Note: AN-1187.

### LVDS Interconnect Guidelines

See AN-1108 and AN-905 for full details.

- Use 100Ω coupled differential pairs

- Use differential connectors when above 500Mbps

- Minimize skew within the pair

- Use the S/2S/3S rule in spacings

- S = space between the pairs

- 2S = space between pairs

- 3S = space to LVCMOS signals

- Place ground vias next to signal vias when changing between layers

- When a signal changes reference planes, place a bypass cap and vias between the new and old reference plane

For more tips and detailed suggestions regarding high speed board layout principles, please consult the LVDS Owner's Manual at: http://www.ti.com/lvds

9-Feb-2013

# PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|-------------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      |             | (2)                        |                  | (3)                 |              | (4)               |         |

| DS90C187LF/NOPB  | ACTIVE | VQFN         | NLA     | 92   | 1000        | Green (RoHS<br>& no Sb/Br) |                  | Level-3-260C-168 HR | -10 to 70    | 90C187LF          | Samples |

| DS90C187LFE/NOPB | ACTIVE | VQFN         | NLA     | 92   | 250         | Green (RoHS<br>& no Sb/Br) |                  | Level-3-260C-168 HR | -10 to 70    | 90C187LF          | Samples |

| DS90C187LFX/NOPB | ACTIVE | VQFN         | NLA     | 92   | 2500        | Green (RoHS<br>& no Sb/Br) |                  | Level-3-260C-168 HR | -10 to 70    | 90C187LF          | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

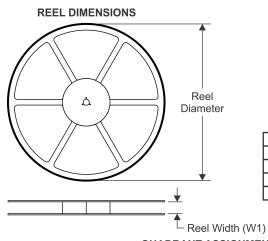

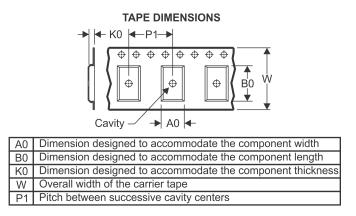

# TAPE AND REEL INFORMATION

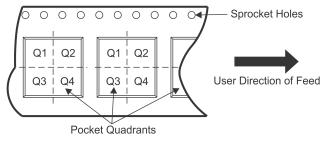

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All di | imensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|---------|-----------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

|         | Device                | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| D       | S90C187LF/NOPB        | VQFN            | NLA                | 92 | 1000 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.3        | 12.0       | 16.0      | Q1               |

| DS      | 90C187LFE/NOPB        | VQFN            | NLA                | 92 | 250  | 178.0                    | 16.4                     | 7.3        | 7.3        | 1.3        | 12.0       | 16.0      | Q1               |

| DS      | 90C187LFX/NOPB        | VQFN            | NLA                | 92 | 2500 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.3        | 12.0       | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

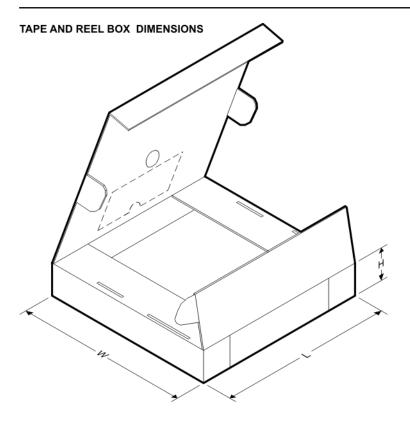

# PACKAGE MATERIALS INFORMATION

26-Mar-2013

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DS90C187LF/NOPB  | VQFN         | NLA             | 92   | 1000 | 367.0       | 367.0      | 38.0        |

| DS90C187LFE/NOPB | VQFN         | NLA             | 92   | 250  | 213.0       | 191.0      | 55.0        |

| DS90C187LFX/NOPB | VQFN         | NLA             | 92   | 2500 | 367.0       | 367.0      | 38.0        |

# **MECHANICAL DATA**

# NLA0092A

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated