FXP1500/1800 front-ends have a backplane-mounted AC input.

### **Applications**

- Telecommunications

- Data communications

- Servers

- Distributed power

# FXR-3-48G Power Shelf

The FXR-3-48G shelf provides up to 5400 watts in a 19" rack. (See the Rack section for power shelf details.)

#### **Features**

- RoHS compliant for all six substances

- High density front-ends 15.2 to 18.3 W/in<sup>3</sup>

- Wide input voltage range 85 to 264 VAC

- 12 V standby voltage, 1A per front-end

- Highly efficient topology reduces operating costs

- I<sup>2</sup>C interface status and control

- I<sup>2</sup>C voltage and current limit setting

- Analog output voltage setting

- Overtemperature, output overvoltage, and output overcurrent protection

- ORing circuits for true redundant operation:  $V_{01}$ : ORing FETs;  $V_{02}$ : ORing Diodes

- Status LEDs: AC OK, DC OK, and Fan Fail/Overtemperature Fail

#### **Description**

The FXP1500/1800 front-ends are power-factor-corrected (PFC) and provide a 48 VDC (1500 or 1800 watt) output, and can be used in hot-swap redundant systems. Their very small dimensions allow configuration of up to three units in a 1U rack. The FXP front-ends have a rear-mounted AC connector. The highly efficient thermal design with internal-fan cooling permits their use over wide temperature ranges and provides very high reliability.

Status information is provided with front panel LEDs, logic signals, and via an I<sup>2</sup>C management interface. In addition, the I<sup>2</sup>C bus can enable the power supply, set high fan speed, adjust the output voltage, and set the output current limit. The FXP1500/1800's meet international safety standards and display the CE-Mark for the European Low Voltage Directive (LVD).

FXR-3-48G power-shelf solutions provide rectification, system management, and power distribution, while maintaining high reliability and offering flexibility for future expansion. The power shelves can be configured with up to three hot-swappable 1500 or 1800-watt AC-DC front-ends.

#### **Model Selection**

|             | Input voltage                      | Output 1                   |                            | Output 2                   |                            | Poted newer          | Compatible                       |

|-------------|------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------|----------------------------------|

| Model       | VAC<br>auto selected <sup>1</sup>  | V <sub>o1 nom</sub><br>VDC | I <sub>o1 max</sub><br>ADC | V <sub>o2 nom</sub><br>VDC | I <sub>o2 max</sub><br>ADC | Rated power<br>W     | Compatible<br>Shelf <sup>2</sup> |

| FXP1500-48G | 105 – 264<br>85 – 105              | 48<br>48                   | 32.2<br>25.4               | 12<br>12                   | 1<br>1                     | 1512<br>1212         | FXR-3-48G                        |

| FXP1800-48G | 180 – 264<br>105 – 180<br>85 – 105 | 48<br>48<br>48             | 39.2<br>32.2<br>25.4       | 12<br>12<br>12             | 1<br>1<br>1                | 1812<br>1512<br>1212 | FXR-3-48G                        |

#### **Absolute Maximum Ratings**

Stress in excess of the absolute maximum ratings may cause performance degradation, adversely effect long-term reliability, or cause permanent damage to the converter.

| Parameter                     | Conditions/Description                                                                                               |   | Max        | Unit       |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------|---|------------|------------|

| Input voltage                 | Continuous<br>Transient, 60 ms max.                                                                                  |   | 264<br>300 | VAC<br>VAC |

| Operating ambient temperature | V <sub>i min</sub> -V <sub>i max</sub> , I <sub>o nom</sub> , cooling by internal fan<br>@ 100 % load<br>@ 50 % load | 0 | 50<br>70   | ů<br>Ĉ     |

| Storage temperature           | Non-Operating                                                                                                        |   | 85         | °C         |

#### **Environmental, Mechanical, & Reliability Specifications**

| Parameter                         | Conditions/Description                                                                     | Min               | Nom           | Max          | Unit                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------|-------------------|---------------|--------------|-------------------------------------------|

| Altitude                          | Operating Non-Operating                                                                    |                   |               | 10 k<br>40 k | ASL Ft.<br>ASL Ft.                        |

| Relative humidity, non-condensing | Operating                                                                                  | 10                |               | 90           | % RH                                      |

|                                   | Storage                                                                                    | 5                 |               | 95           | % RH                                      |

| Temperature coefficient           | 0 °C to 70 °C (after 15 min warm-up)                                                       |                   |               | 0.02         | %/K                                       |

| Shock                             | IEC/EN 60068-2-27, 11 ms                                                                   |                   |               | 40           | $g_{pk}$                                  |

| Sinusoidal vibration              | IEC/EN 60068-2-6<br>2-8 Hz<br>8-200 Hz<br>200-500 Hz                                       |                   | 7.5<br>2<br>4 |              | mil<br>9 <sub>pk</sub><br>9 <sub>pk</sub> |

| Random vibration                  | 10-2000 Hz                                                                                 |                   | 6.15          |              | g <sub>rms</sub>                          |

| MTBF                              | Calculated per Bellcore (SR-332, Issue 1):  GB 25 °C  GB 25 °C (FNP1500-12G)  Demonstrated | 230<br>TBD<br>250 |               |              | kh<br>kh<br>kh                            |

The available output power is automatically adjusted depending on the input voltage.

1U standard racks are available from Power-One. See the Rack (Power Shelf) section of this data sheet for configurations and details.

#### **Safety Specifications**

Maximum electric strength testing is performed in the factory according to EN 550116, IEC/EN60950-1 2<sup>nd</sup> ed. and UL/CSA60950-1 2<sup>nd</sup> ed. Input-to-output electric strength tests should not be repeated in the field. Power-One will not honor any warranty claims resulting from electric strength field tests.

| Parameter                      | Conditions/description                                                                                            | Min | Nom                               | Max | Unit                         |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------|-----|------------------------------|

| Agency approvals               | UL/CSA60950-1 2 <sup>nd</sup> ed., EN60950-1 2 <sup>nd</sup> ed., IEC60950-1 2 <sup>nd</sup> ed., CE Mark for LVD |     |                                   |     |                              |

| Insulation safety rating       | Input to case<br>Input to output<br>Output to case                                                                |     | Basic<br>Reinforced<br>Functional |     |                              |

| Electric strength test voltage | voltage Input to case Input to output Output to case Output 1 to output 2                                         |     |                                   |     | kVDC<br>kVDC<br>kVDC<br>kVDC |

<sup>&</sup>lt;sup>1</sup> Subassemblies are pre-tested with 4.2 kVDC in accordance with EN50116 and IEC/EN60950-1 2<sup>nd</sup> ed.

#### **EMC Specifications**

| Parameter                        | Description                    | Criterion                                         |

|----------------------------------|--------------------------------|---------------------------------------------------|

| Electrostatic discharge          | IEC/EN 61000-4-2, level 4      | Performance criterion B                           |

| Electromagnetic field            | IEC/EN 61000-4-3, level 3      | Performance criterion A                           |

| Electrical fast transients/burst | IEC/EN 61000-4-4, level 3      | Performance criterion B                           |

| Surge                            | IEC/EN 61000-4-5, level 3      | Performance criterion B                           |

| Voltage dips and interruptions   | IEC/EN 61000-4-11              | Performance criterion B or better                 |

| RF conducted immunity            | IEC/EN 61000-4-6               | 10 VAC, AM 80 %, 1 kHz<br>Performance criterion A |

| Emissions conducted              | CISPR 22/EN 55022/EN 61204     | Class B                                           |

| Emissions radiated               | CISPR 22/EN 55022/EN 61204     | Class A                                           |

| Harmonics                        | IEC/EN 61000-3-2               | Class B                                           |

| Voltage fluctuation and flicker  | IEC/EN 61000-3-3               | Pass                                              |

| Voltage sag                      | SEMI F47-0200 (High Line 230V) | Pass                                              |

#### **Input Specifications**

Specification is valid for input voltage, load, and temperature ranges, unless otherwise stated.

| Parameter                 | Conditions/description                                         | Min  | Nom   | Max | Unit             |

|---------------------------|----------------------------------------------------------------|------|-------|-----|------------------|

| Input voltage             |                                                                | 85   | 230   | 264 | VAC              |

| Input frequency           |                                                                | 47   | 50/60 | 63  | Hz               |

| Turn-on input voltage     | Ramping up                                                     | 79   | -     | 85  | VAC              |

| Turn-off input voltage    | Ramping down                                                   | 70   | -     | 78  | VAC              |

| Inrush current limitation | 115/230 VAC acc. ETS 300 132-1<br>< 100 ms                     |      |       | 50  | $A_pk$           |

| Hold-up time              | After last AC line peak, $V_i$ = 230 VAC, $P_{o \text{ nom}}$  | 20   |       |     | ms               |

| Power factor              | V <sub>i nom</sub> , J <sub>o nom</sub>                        | 0.95 |       |     | W/VA             |

| Efficiency                | $V_{\rm i}$ = 230 VAC, $I_{\rm o \ nom}$ , $T_{\rm C}$ = 25 °C | 89   | 90    |     | %                |

| Max input current         |                                                                |      |       | 20  | A <sub>rms</sub> |

| Input connector           | 16A – 20 A / 250 VAC; according to IEC320 C19                  |      |       |     |                  |

Output Specifications, 48Vout Models

Specification is valid for input voltage, load, and temperature ranges, unless otherwise stated.

|                                               | Parameter                          | Conditions/Description                                                                                                                                                                          | Min   | Nom                  | Max        | Units                         |

|-----------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------|------------|-------------------------------|

| Nominal outp                                  | ut voltage Vo1                     | I <sub>o</sub> = 16.1 A                                                                                                                                                                         |       | 48                   |            | VDC                           |

| Nominal outp                                  | ut voltage Vo2                     | <i>I</i> <sub>o</sub> = 0.5 A                                                                                                                                                                   |       | 12                   |            | VDC                           |

| Output voltag                                 | e set point accuracy               | $V_{\rm i}$ = 230 VAC, $I_{\rm o1}$ =16.1 A, $T_{\rm C}$ = 25 °C (47.8 - 48.2 VDC)                                                                                                              | -0.5  |                      | +0.5       | % V <sub>o1 nom</sub>         |

| Output voltag<br>(via I <sup>2</sup> C or wit | e trimming<br>h external resistor) | Adjustable (44.16 to 51.84 VDC)                                                                                                                                                                 | -8    |                      | +8         | % V <sub>o1 nom</sub>         |

| Nominal<br>current                            | FXP1500-48G                        | $I_{o1 \text{ nom}}$ @ $V_i = 105 \text{ VAC} - 264 \text{ VAC}, P_o 1.5 \text{ kW}$<br>$I_{o1 \text{ nom}}$ @ $V_i = 85 \text{ VAC} - 105 \text{ VAC}, P_o 1.2 \text{ kW}$                     |       | 32.2<br>25.4         |            | ADC<br>ADC                    |

| output 1                                      | FXP1800-48G                        | $I_{o1 \text{ nom}}$ @ $V_i$ =180 VAC - 264 VAC, $P_o$ 1.8 kW<br>$I_{o1 \text{ nom}}$ @ $V_i$ =105 VAC - 180 VAC, $P_o$ 1.5 kW<br>$I_{o1 \text{ nom}}$ @ $V_i$ = 85 VAC - 105 VAC, $P_o$ 1.2 kW |       | 39.2<br>32.2<br>25.4 | 39.2       | ADC<br>ADC<br>ADC             |

| Current                                       | FXP1500-48G                        | $I_{\text{01 max}}$ @ $V_{\text{i}}$ = 105 VAC - 264 VAC droop hiccup $I_{\text{01 max}}$ @ $V_{\text{i}}$ = 85 VAC - 105 VAC droop hiccup                                                      |       | 36.8<br>30           |            | ADC<br>ADC                    |

| limit<br>output 1                             | FXP1800-48G                        | $I_{01 \text{ max}}$ @ $V_i$ = 180 VAC - 264 VAC droop hiccup<br>$I_{01 \text{ max}}$ @ $V_i$ = 105 VAC - 180 VAC droop hiccup<br>$I_{01 \text{ max}}$ @ $V_i$ = 85 VAC - 105 VAC droop hiccup  |       | 43.8<br>36.8<br>30   |            | ADC<br>ADC<br>ADC             |

| Nominal curre                                 | ent output 2                       | $I_{o2 \text{ nom}}$ @ Vi = 85 VAC – 264 VAC, $P_o$ 12 W                                                                                                                                        |       | 1.0                  | 1.0        | ADC                           |

| Current limit of                              | output 2                           | $I_{o2 \text{ max}} \otimes V_i = 85 \text{ VAC} - 264 \text{ VAC}$                                                                                                                             |       | 1.5                  |            | ADC                           |

| Static line reg                               | julation output 1                  | $V_{\rm imin}$ - $V_{\rm imax}$ , 50 % $I_{\rm onom}$                                                                                                                                           | -0.5  |                      | 0.5        | % V <sub>o nom</sub>          |

| Static load regulation                        | FXP1500-48G                        | $V_{\rm i}$ = 230 V, 5-100 % $I_{\rm o nom}$ $V_{\rm o}$ : full load (32.2 ADC) to no load                                                                                                      | 46.65 | 83.5<br>48           | 49.34      | mV/A<br>VDC                   |

| output 1<br>(droop<br>characteristic          | FXP1800-48G                        | V <sub>i</sub> = 230 V, 5-100 % I <sub>o nom</sub><br>V <sub>o</sub> : full load (32.2 ADC) to no load                                                                                          | 46.07 | 83.5<br>48           | 49.34      | mV/A<br>VDC                   |

| Static load reg                               | gulation<br>op characteristic)     | $V_i$ = 230 V, 5-100 % $I_{o \text{ nom}}$<br>$V_o$ : full load (32.2 ADC) to no load                                                                                                           |       | 0.4                  |            | VDC                           |

| Dynamic                                       |                                    | Load change 50% <-> 100% I <sub>o nom</sub> , dI <sub>o</sub> /dt =1 A/μs<br>Voltage deviation (droop + over- or undershoot)                                                                    |       |                      |            | % V <sub>o nom</sub>          |

| load                                          | FXP1500-48G                        |                                                                                                                                                                                                 | -5    |                      | 5          | % V <sub>o nom</sub>          |

| regulation                                    | FXP1800-48G                        |                                                                                                                                                                                                 | -5.7  |                      | 5.7        | % V <sub>o nom</sub>          |

|                                               | All models                         | Max. recovery time to within 1 % of $V_{\text{o1 nom}}$                                                                                                                                         |       |                      | 400        | μS                            |

| Current                                       |                                    | Difference in current between two units for $V_{o1}$ above 10 % load.                                                                                                                           |       |                      |            |                               |

| Share                                         | FXP1500-48G                        |                                                                                                                                                                                                 |       |                      | 3.2        | ADC                           |

|                                               | FXP1800-48G                        |                                                                                                                                                                                                 |       |                      | 3.9        | ADC                           |

| Start-up time                                 |                                    | Time required for output within regulation after initial application of AC-input $(V_{\text{i nom}}, I_{\text{o nom}})$ after removal of inhibit $(V_{\text{i nom}}, I_{\text{o nom}})$         |       | 100                  | 1.5        | s<br>ms                       |

| Output voltag<br>(Filter 10 nF/1              | e ripple and noise<br>10 μF)       | $V_{	ext{i nom}}$ , $I_{	ext{o nom}}$ , 20 MHz bandwidth $V_{	ext{o1}}$ $V_{	ext{o2}}$                                                                                                          |       |                      | 480<br>120 | ${ m mV_{pp}} \ { m mV_{pp}}$ |

| Remote sens                                   | e                                  | Total compensation for cable losses                                                                                                                                                             |       |                      | 500        | mV                            |

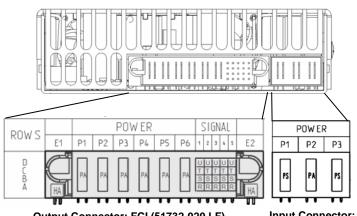

## **Controls and Indicators**

Specification is valid for input voltage, load, and temperature ranges, unless otherwise stated.

| Parameter                                     | Type <sup>1</sup>            | Conditions/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Visual Status<br>Indication                   | FP                           | DC OK (green)     AC OK (green)     Fan fail & Over-temperature (amber)                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| I <sup>2</sup> C communication bus            | OC[S1, S2]                   | <ul> <li>Monitors alarm functions and allows control of specific parameters.</li> <li>Uses standard Philips two wire bus (SCL and SDA signal lines)</li> </ul>                                                                                                                                                                                                                                                                                                                                      |  |

| I <sup>2</sup> C communication bus addressing | OC[T1-T5]                    | Five lines provide up to 32 separate PSU I <sup>2</sup> C addresses                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| PS present pin                                | OC[U3]                       | <ul> <li>Used by system to indicate a PSU is installed in a system shelf</li> <li>Contact closure to logic ground (internal pull-down resistor of 1 kΩ)</li> </ul>                                                                                                                                                                                                                                                                                                                                  |  |

| PS main output                                | OC[R1]                       | <ul> <li>TTL compatible signal, inhibited when open contact, high or at TTL logic "1"</li> <li>Signal referenced to logic return (LRTN)</li> </ul>                                                                                                                                                                                                                                                                                                                                                  |  |

| remote shutdown                               | FP                           | Two position switch in series with OC signal (logical AND) allows local enable/disable; "0" Position => PS disabled; "1" Position => PS Enabled                                                                                                                                                                                                                                                                                                                                                     |  |

| Power supply OK                               | I <sup>2</sup> C             | AC OK & DC OK & no overcurrent & no over-temperature & fans working                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| DC current fail                               | I <sup>2</sup> C             | Reports over-current condition on main output, I <sub>O1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| AC fail / Power down warning                  | OC[U2]<br>& I <sup>2</sup> C | Provides a warning that the input power has failed at least 5 ms before the output falls out of regulation (<90% V <sub>01</sub> set).  • Open collector signal with 20 mA pull-down capability, referenced to logic return (LRTN).  • AC fail will go high or open during power fail condition and will go low when input is within the operating range.  • A Power Fail warning will turn off the front panel green AC OK LED.                                                                    |  |

| DC fail / Output<br>voltage fault             | OC[U4]<br>& I <sup>2</sup> C | <ul> <li>Internal under-voltage and overvoltage supervision of V<sub>O1</sub>.</li> <li>Open collector signal with 20 mA pull-down capability, referenced to logic return (LRTN).</li> <li>DC fail will go high or open if Vo1 &lt; 90% or V<sub>O1</sub>&gt; 110% of V<sub>O1</sub> set, measured in front of the ORing FETs.</li> <li>Green LED on the front panel indicates normal operation; LED will flash if in parallel operation V<sub>O1</sub> is OK, but the unit is disabled.</li> </ul> |  |

| Critical temperature<br>Warning/Fan Fail      | OC[U1]<br>& I <sup>2</sup> C | Indicates the PSU operating temperature has reached [T <sub>shut-down</sub> – 10K] Indicates if the unit is in over-temperature shutdown.  • Open collector signal with 20 mA pull-down capability, referenced to logic return (LRTN).  • The OC-output will go low 100 ms before an over-temperature condition shuts down the unit.  • An amber LED on the front panel indicates over-temperature or fan fail.                                                                                     |  |

| DC voltage monitoring                         | I <sup>2</sup> C             | Monitors the main output voltage, $V_{\text{O1}}$ , seen at the output connector Accuracy is $\pm 0.45 V$ over setting range and temperature.                                                                                                                                                                                                                                                                                                                                                       |  |

| DC current monitoring                         | I <sup>2</sup> C             | Monitors the output current I <sub>O1</sub> : Accuracy ± 0.4A over the load range.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| DC voltage trimming                           | OC[R4]                       | Output voltage trimming V <sub>O1</sub> : ±8% of V <sub>O</sub> set using external resistor                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| (margining)                                   | I <sup>2</sup> C             | Setting accuracy over I2C: ± 50mV at V <sub>o1</sub> nom, ± 150mV over setting range                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Fan speed control                             | I <sup>2</sup> C             | Two fan speed levels automatically set depending on the internal temperature. The fan speed can be set to full speed or automatic control via I <sup>2</sup> C command.                                                                                                                                                                                                                                                                                                                             |  |

| Fan OK/FAIL                                   | OC[U1]<br>& I <sup>2</sup> C | Indicates if the cooling fans are operating or have failed.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Synchronized startup pin                      | OC[R5]                       | Overcurrent signal which can be used for synchronous startup of units in parallel or to recover from an overload condition.                                                                                                                                                                                                                                                                                                                                                                         |  |

<sup>&</sup>lt;sup>1</sup> Abbreviations used:

- OC[#] => Hardwired signal accessible at PSU output connector, with pin number reference

FP => Provided by devices located on PSU Front panel

I²C => Signal provided over l²C communication system; detailed l²C information is available from the specific model's l²C Manual found on the Power-One web site.

<sup>&</sup>lt;sup>2</sup> See LED Function table for further details

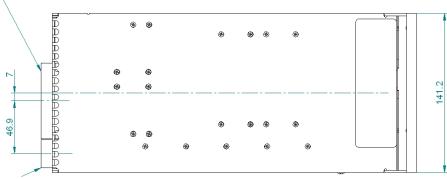

# **Output Connector Pinning and Signal Specification (48V models)**

| Output Connector<br>Description             | OC<br>Pin #                                                                                                                                                                                       | Type Signal Reference                                                                                           |                                                                       | Low level<br>High level   | V max<br>I max                |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|-------------------------------|

| Over-temperature /<br>Fan Fail              | U1                                                                                                                                                                                                | OC-output, protected by 16 V Zener diode                                                                        | LCND                                                                  | <0.4 V @ 20 mA<br>Pull up | 15 V<br>20 mA                 |

| AC Fail /<br>Power down warning             | U2                                                                                                                                                                                                | and a $10\Omega$ resistor in series                                                                             | LGND                                                                  | <0.4 V @ 20 mA<br>Pull up | 15 V<br>20 mA                 |

| Power Supply Present                        | U3                                                                                                                                                                                                | 1KΩ Resistor connected to logic GND LGND                                                                        |                                                                       | Open<br>Pull up           | 10 V<br>10 mA                 |

| DC Fail /<br>Output voltage fault           | U4                                                                                                                                                                                                | OC-output, protected by 16 V Zener diode and a 10Ω resistor in series                                           |                                                                       | <0.4V @ 20 mA<br>Pull up  | 15 V<br>20 mA                 |

| Internal ground<br>(INT GND)                | U5                                                                                                                                                                                                | Used only for ADDRx and V <sub>O1</sub> set. Do not connect the internal grounds in systems with several units. | connect the internal grounds in systems V <sub>O1</sub> - line before |                           | -                             |

| ADDR0 I <sup>2</sup> C address bus          | T1                                                                                                                                                                                                |                                                                                                                 |                                                                       |                           |                               |

| ADDR1 I <sup>2</sup> C address bus          | T2                                                                                                                                                                                                | High = internal 10 KΩ PU to 5V=> Logic 1                                                                        |                                                                       |                           |                               |

| ADDR2 I <sup>2</sup> C address bus          | Т3                                                                                                                                                                                                |                                                                                                                 | INT GND                                                               | Logic 1<br>Logic 0        | 5V<br>0V                      |

| ADDR3 I <sup>2</sup> C address bus          | T4                                                                                                                                                                                                | Low = connect to INT GND => Logic 0                                                                             |                                                                       | 20910 0                   | •                             |

| ADDR4 I <sup>2</sup> C address bus          | T5                                                                                                                                                                                                |                                                                                                                 |                                                                       |                           |                               |

| SDA, I <sup>2</sup> C serial data line      | S1                                                                                                                                                                                                | I <sup>2</sup> C compatible signal referenced to logic                                                          |                                                                       | Logic 1                   | 3.3V to 5V                    |

| SCL, I <sup>2</sup> C serial clock<br>line  | erial clock S2 GND 5 V or 3.3 V logic                                                                                                                                                             |                                                                                                                 | LGND                                                                  | Logic 0                   | 0V                            |

| Auxiliary power +12 V                       | S3                                                                                                                                                                                                | V <sub>O2</sub> + output, isolated from main output                                                             | Aux output is                                                         |                           |                               |

| Auxiliary power<br>+12VRTN                  | S4                                                                                                                                                                                                | Aux output return; ground isolated from main output                                                             | floating                                                              | -                         | 1                             |

| Logic ground (LGND)                         | Internally connected to Aux GND through $10\Omega$ resistor. Wire LGND separately from Aux RTN and main output GND to minimize noise on signals and I <sup>2</sup> C bus. Leave open if not used. |                                                                                                                 | -                                                                     | -                         |                               |

| Output inhibit R1                           | R1                                                                                                                                                                                                | PS active when pulled low (DC-DC stage off when left open)                                                      | LGND                                                                  | <0.8 V<br>>2.0 V          | 10 V<br>3.5 mA                |

| V sense +                                   | R2                                                                                                                                                                                                | Open or connected to $V_{\text{O1}}$ + at the load Internally connected to $V_{\text{O1}}$ + via 100 $\Omega$ . | -                                                                     | -                         | dV<3 V <sub>pp</sub><br>30 mA |

| V sense -                                   | R3                                                                                                                                                                                                | Open or connected to $V_{\text{O1}^-}$ at the load Internally connected to $V_{\text{O1}^-}$ via 100 $\Omega$ . | -                                                                     | -                         | 30 IIIA                       |

| Output margin                               | R4 Oper or connected to INT GND (+8% $V_{o1}$ ) or $V_{sense+}$ (-8% $V_{o1}$ ), Do not interconnect margin pins in systems with paralleled PSUs.                                                 |                                                                                                                 | -                                                                     | 60V                       |                               |

| Synchronized Startup (for paralleled units) | R5                                                                                                                                                                                                | Open or connected to synch startup circuit V <sub>01</sub> – at the                                             |                                                                       |                           | 12V<br>2mA                    |

| V <sub>01</sub> -                           | P1, P3, P5                                                                                                                                                                                        | Main output - pins                                                                                              | -                                                                     | -                         | -                             |

| V <sub>01</sub> +                           | P2, P4, P6                                                                                                                                                                                        | Main output + pins                                                                                              | -                                                                     | -                         | -                             |

| Input Connector Description                 | OC<br>Pin #                                                                                                                                                                                       | Туре                                                                                                            |                                                                       | 1                         |                               |

| Protection Earth                            | P1                                                                                                                                                                                                | PE                                                                                                              |                                                                       |                           |                               |

| Phase                                       | P2                                                                                                                                                                                                | L                                                                                                               |                                                                       |                           |                               |

| Neutral                                     | P3                                                                                                                                                                                                | N                                                                                                               |                                                                       |                           |                               |

#### **Protection**

| Parameter Conditions/Description             |                                              | Min              | Nom         | Max       | Unit                 |

|----------------------------------------------|----------------------------------------------|------------------|-------------|-----------|----------------------|

| Input fuse                                   | Not user accessible 25A, fast blow           |                  | low         |           |                      |

| Inrush current limitation                    |                                              | With NTCs        |             |           |                      |

| Output                                       |                                              | No-load -, short | circuit - a | nd overlo | ad proof             |

| Overvolte se protection letching!            | Tracking                                     | 115              |             | 122       | % V <sub>o nom</sub> |

| Overvoltage protection latching <sup>1</sup> | Absolute                                     |                  |             | 59.5      | V                    |

| Overtemperature protection                   | Automatic power shutdown at $T_{\mathbb{C}}$ |                  | 95          |           | °C                   |

<sup>&</sup>lt;sup>1</sup> Remove input voltage to reset.

#### **LED Indicator Functionality**

| Condition                                 | Power Fail<br>(AC OK) | Output Good<br>(DC OK) | Fan Fail and<br>Over - Temperature |

|-------------------------------------------|-----------------------|------------------------|------------------------------------|

| Normal Operation                          | Green                 | Green                  | OFF                                |

| Power Supply is inhibited                 | Green                 | OFF                    | Amber                              |

| Input AC is low                           | OFF                   | OFF                    | Amber                              |

| Input AC is low or missing                | OFF                   | OFF                    | Amber/OFF                          |

| Over-temperature                          | Green                 | OFF                    | Amber                              |

| Output overload (In regulation)           | Green                 | Green                  | OFF                                |

| Output Overloaded (Out of Regulation)     | Green                 | OFF                    | OFF                                |

| Fan Fault (No overtemperature shutdown)   | Green                 | Green                  | Amber                              |

| Fan Fault (With overtemperature shutdown) | Green                 | OFF                    | Amber                              |

| Power Supply Failed                       | OFF                   | OFF                    | OFF/ Amber                         |

#### Cooling:

To achieve best cooling results sufficient airflow through the unit must be ensured. Do not block or obstruct the airflow at the rear of the unit by placing large components directly at the output connector.

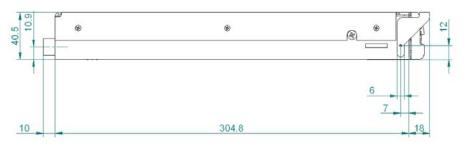

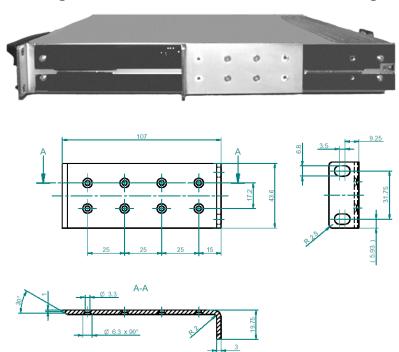

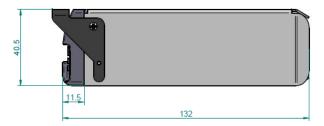

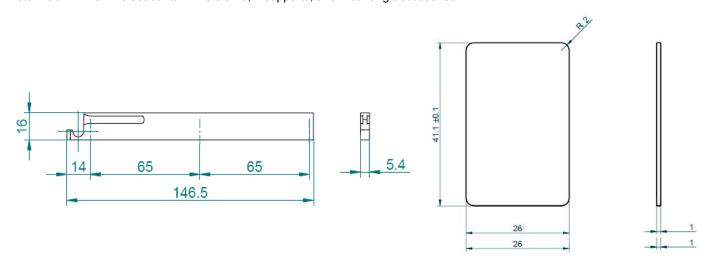

#### Mechanical Data (FXP1500/1800 48V Models)

5.6" (141.2mm) x 1.6" (40.5mm) x 12" (304.8mm) Mechanical Data (H, W, D)

Output Connector FCI part no. 51732-020LF

Input Connector FCI part no. 51939-126LF

#### **Input and Output Connector Descriptions**

Output Connector: FCI (51732-020 LF) Input Connector: FCI (51939-126 LF)

**FXP** series front bezel showing LED indicators and recessed enable switch

Female ledge connector: Manufacturer: FCI

Output connector Part No.: 51762-106020000AA LF (Horizontal) Output connector Part No.: 51742-106020000AA LF (Vertical)

Input connector Part No.: 51915-056LF (Horizontal) Input connector Part No.: 51940-099LF (Vertical)

Information on availability under http://www.stkcheck.com/evs/fcielectronics/fcisearch.asp

#### **Paralleling Front-Ends:**

For parallel use in minimal configuration systems, only the inhibit pins must be shorted to logic GND. All other pins can be left open. The power supplies will share the output current automatically (droop current share).

For parallel applications without  $I^2C$  bus, but the use of all other features, it is recommended to connect all logic GND's on a backplane together, to connect all  $V_{o2}$  -, all  $V_{o2}$  + and to leave the internal GND's open.

The sense wires can be left open or connected to a common load point, the synch-start pin can be left open or connected to a synch-start circuit, the inhibit pins can be connected together or used individually. All I<sup>2</sup>C signals (T1-T5, S1, and S2) can be left open.

Use of a small foil capacitor >  $3\mu$ F directly at the power outputs of each unit is recommended in order to prevent voltage drops at the hot plug. For additional information on paralleling see the following Rack (Power Shelf) section.

#### **Racks**

#### (FXR-3-48G Power Shelves)

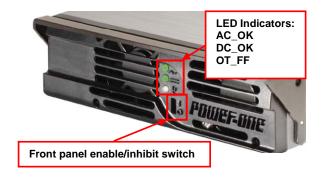

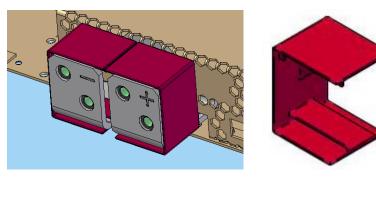

Each rack (power shelf) is 1U high with backplane and designed for up to three front-end models in parallel or in n+1 operation. Each power shelf has:

- Massive copper bus bars for low-loss current distribution.

- Output terminals with two M4-screws on each power tab.

- Two fast-on contacts for system earthing.

- Address coding over five pole DIP switch on each unit, 37-pin D-Sub connector with I<sup>2</sup>C-lines, monitoring signals and support functions.

- Provides a start-up synchronization circuit and EMV filters.

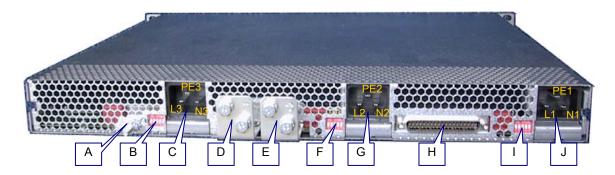

**FXR-3-48G Power Shelf Front View**

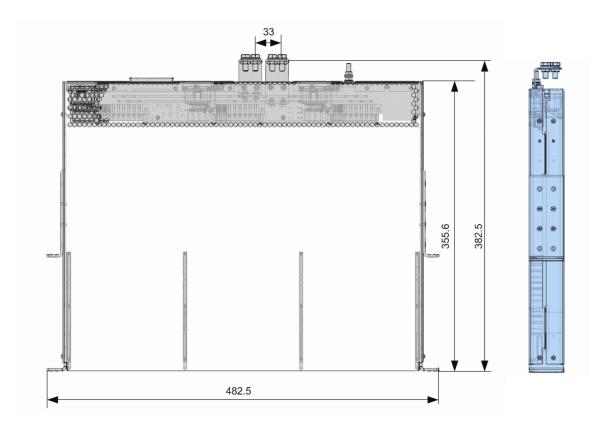

#### **Overall Mechanical Dimensions (FXR-3-48G Power Shelves)**

| FXR-3 Mechanical Data (W, H, D) | 17.7" (449.6 mm) x 1.7" (43.1 mm) x 14" (355.6 mm) |

|---------------------------------|----------------------------------------------------|

|---------------------------------|----------------------------------------------------|

# **Output Connector Descriptions (FXR-3-48G)**

| Location | Description                                                                  |          |

|----------|------------------------------------------------------------------------------|----------|

| Α        | Earth connection                                                             |          |

| В        | 5-bit DIP switch for I <sup>2</sup> C addressing of PSU #3                   | ON APEMS |

| С        | Mains connector of PSU #3                                                    |          |

| D        | Output 1 Minus                                                               |          |

| Е        | Output 1 Plus                                                                |          |

| F        | 5-bit DIP switch for I <sup>2</sup> C addressing of PSU #2                   | 0N APEMs |

| G        | Mains connector of PSU #2                                                    |          |

| Н        | 37-pin SUB-D connector, control, sense, check and Auxiliary power (Output 2) |          |

| I        | 5-bit DIP switch for I <sup>2</sup> C addressing of PSU #1                   | ON APEMs |

| J        | Mains connector of PSU #1                                                    |          |

#

# **SUB-D Output Connector Pinout and Signal Specification**

| Output Connector<br>Description         | OC<br>Pin | Туре                                                                                                                                                                                                    | Signal<br>Reference | Low level<br>High level   | V max<br>I max                  |

|-----------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|---------------------------------|

| Overtemperature /<br>Fan Fail PSU1      | 1         | OC-output, protected by 16 V Zener diode and a 10 $\Omega$ resistor in series.                                                                                                                          | LGND                | <0.4 V @ 20 mA<br>Pull up | 15 V<br>20 mA                   |

| Power Supply Present<br>PSU 1           | 2         | Posister (4 kg) connected to logic CND                                                                                                                                                                  | LGND                | Open<br>Pull up           | 10 V<br>10 mA                   |

| Power Supply Present<br>PSU 2           | 3         | Resistor (1 kΩ) connected to logic GND                                                                                                                                                                  |                     |                           |                                 |

| Spare                                   | 4         |                                                                                                                                                                                                         |                     |                           |                                 |

| Overtemperature / Fan Fail PSU 3        | 5         | OC-output, protected by 16 V Zener diode                                                                                                                                                                | LGND                | <0.4 V @ 20 mA<br>Pull up | 15 V<br>20 mA                   |

| AC Fail /<br>Power down warning PSU 3   | 6         | and a 10 $\Omega$ resistor in series.                                                                                                                                                                   |                     |                           |                                 |

| Power Supply Present PSU 3              | 7         | Resistor (1 kΩ) connected to logic GND                                                                                                                                                                  | LGND                | Open<br>Pull up           | 10 V<br>10 mA                   |

| DC Fail /<br>Output voltage fault PSU 3 | 8         | OC-output, protected by 16 V Zener diode                                                                                                                                                                | LGND                | <0.4 V @ 20 mA            | 15 V<br>20 mA                   |

| Overtemperature / Fan Fail PSU 2        | 9         | and a 10 $\Omega$ resistor in series                                                                                                                                                                    | 20115               | Pull up                   |                                 |

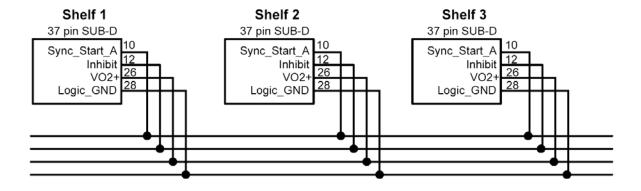

| SynchStart_A                            | 10        | Sync_start_A , Active high The signals of several racks can be connected together in such a way that all supplies will be inhibited until the last supply has recovered from its overcurrent condition. | LGND                | <7V off<br>< 9V           | 15V<br>10mA                     |

| Spare                                   | 11        |                                                                                                                                                                                                         |                     |                           |                                 |

| Output inhibit<br>PSU 1-3               | 12        | DC-DC stage ON when pin is open or connected to LGND DC-DC stage OFF when pin is connected on high potential                                                                                            | LGND                | <0.8 V<br>>2.0 V          | 10 V<br>3.5 mA                  |

| V sense +                               | 13        | Open or connected to $V_{\text{o1}}$ + at the load Internally (PSU) connected to $V_{\text{o1}}$ + over 100 $\Omega$                                                                                    | V <sub>o1+</sub>    |                           | dV < 3 V <sub>pp</sub><br>30 mA |

| V sense -                               | 14        | Open or connected to $V_{\text{o1}}$ at the load Internally (PSU) connected to $V_{\text{o1}}$ over 100 $\Omega$                                                                                        | V <sub>01-</sub>    |                           | dV < 3 V <sub>pp</sub><br>30 mA |

| Spare                                   | 15        |                                                                                                                                                                                                         |                     |                           |                                 |

| NC                                      | 16        |                                                                                                                                                                                                         |                     |                           |                                 |

| NC                                      | 17        |                                                                                                                                                                                                         |                     |                           |                                 |

| NC                                      | 18        |                                                                                                                                                                                                         |                     |                           |                                 |

| NC                                      | 19        |                                                                                                                                                                                                         |                     |                           |                                 |

| AC Fail/<br>Power-down warning PSU 1    | 20        |                                                                                                                                                                                                         |                     |                           |                                 |

| DC Fail/<br>Output voltage fault PSU 1  | 21        | OC-output, protected by 16 V Zener diode                                                                                                                                                                | LGND                | <0.4 V @ 20 mA            | 15 V                            |

| AC Fail/<br>Power-down warning PSU 2    | 22        | and a 10 Ω resistor in series                                                                                                                                                                           |                     | Pull up                   | 20 mA                           |

| DC Fail/<br>Output voltage fault PSU 2  | 23        |                                                                                                                                                                                                         |                     |                           |                                 |

| SDA, I <sup>2</sup> C data line         | 24        | I <sup>2</sup> C compatible signal                                                                                                                                                                      | LGND                | 5 V or 3.3 Vlogic         |                                 |

#### **SUB-D Output Connector Pinout and Signal Specification (Continued)**

| Output Connector Description              | OC<br>Pin | Туре                                                                                                                                                         | Signal<br>Reference                                         | Low level<br>High level | V max<br>I max |

|-------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------|----------------|

| SCL, I <sup>2</sup> C clock line          | 25        | I <sup>2</sup> C compatible signal                                                                                                                           | LGND                                                        | 5 V or 3.3 V<br>logic   |                |

| $V_{o2+}$ = +12 V<br>(Auxiliary power)    | 26        | V <sub>o2</sub> + Aux output, insulated from main output                                                                                                     | Aux output is isolated supply                               |                         |                |

| $V_{o2-}$ = +12 VRTN<br>(Auxiliary power) | 27        | V <sub>o2</sub> - Aux output, insulated from main output                                                                                                     |                                                             |                         |                |

| Logic Gnd<br>(LGND)                       | 28        | Wire separately from auxiliary and main output GND to minimize noise and avoid voltage drops on signal- and I <sup>2</sup> C return. Leave open if not used. | Internally<br>connected to<br>Vo2 Auxiliary<br>GND via 10 Ω |                         |                |

| Output margin PSU 1                       | 29        |                                                                                                                                                              |                                                             |                         |                |

| Output margin PSU 2                       | 30        | Open or connected to $V_{\text{sense-}}$<br>$V_{\text{sense-}}$ (+8 % $V_{\text{o1}}$ ) or $V_{\text{sense+}}$ (-8 % $V_{\text{o1}}$ )                       |                                                             |                         | 60V            |

| Output margin PSU 3                       | 31        |                                                                                                                                                              |                                                             |                         |                |

| NC                                        | 32        |                                                                                                                                                              |                                                             |                         |                |

| NC                                        | 33        |                                                                                                                                                              |                                                             |                         |                |

| NC                                        | 34        |                                                                                                                                                              |                                                             |                         |                |

| NC                                        | 35        |                                                                                                                                                              |                                                             |                         |                |

| NC                                        | 36        |                                                                                                                                                              |                                                             |                         |                |

| NC                                        | 37        |                                                                                                                                                              |                                                             |                         |                |

# Synchronized start-up circuit for paralleling operation

The FXP1500-48G and FXP1800-48G power supplies exhibit an overcurrent hiccup behaviour. This means if either of these supplies reaches an overcurrent limit, the output voltage will immediately turn OFF and after a delay turn ON again. In parallel use, all power supplies have to start synchronized because of the internal hiccup behaviour. Otherwise, the supply which has reached overcurrent first will go to hiccup; this will overload the other supplies, which then will also go to hiccup. When the first supply has recovered from hiccup (hiccup dead time), the others remain in hiccup. This will immediately drive the first one into hiccup once again. This means that without a start-up circuit, a system with several power supplies can never recover from an overload condition or start-up into full load.

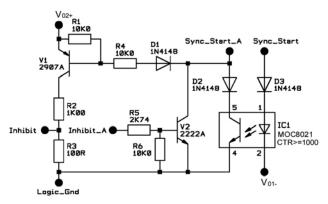

The following additional circuit, required to reach synchronized startup, is already implemented inside the FXR-3-48G shelf.

#### **Synch Start-up Connection Between Shelves**

The following connection between the shelves is required to achieve a parallel operation. The synch-start circuits inside the shelves inhibit all power supplies until the last one has recovered from its overcurrent condition and then synchronize the restart of the outputs.

#### **Synch Start-up Circuit Description**

| Description                                                                     | Pin<br>Location,<br>Definition | Туре                                                                                                                                                                                                   | Signal<br>Reference                                | Low level<br>High level | V max<br>I max |

|---------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------|----------------|

| Auxiliary power +12 V (Output 2)                                                | 26                             | V <sub>o2</sub> +, Aux output, insulated from main output                                                                                                                                              |                                                    |                         |                |

| Logic ground                                                                    | 28                             | Logic_GND ,Internally connected over 10 $\Omega$ to $V_{o2}$ -, ( Auxiliary power ground (Output 2))                                                                                                   | Internally connected over $10\Omega$ to $V_{02}$ - |                         |                |

| Output inhibit_A<br>PSU 1-3                                                     | 12                             | Inhibit_A, DC-DC stage ON when pin is open or connected to LGND DC-DC stage OFF when pin is connected on high potential                                                                                | LGND                                               | <0.8 V<br>>2.0 V        | 10 V<br>3.5 mA |

| Synch. Startup 1<br>PSU 1-3                                                     | R5<br>(at PSU)                 | The synch_start pin is connected to the over-current signal of the PSU1-3. In the case of an overcurrent shutdown, this signal goes high.                                                              | V <sub>o1</sub> .                                  | <7V off<br>> 9V         | 15V<br>10mA    |

| Synch. Startup_A Rack FXR-3-48G 1-N Pin on the D-Sub connector on the backplane | 10                             | Sync_start_A, Active high The signals of several racks can be connected together in such a way that all supplies will be inhibited until the last supply has recovered from its overcurrent condition. | LGND                                               |                         |                |

NOTE: The Sync-Start pins can be wired together only if the power supplies are connected with a minimal voltage drop on power ground as achieved on a backplane with massive copper bus bars. If there is a less ideal connection, it is recommended to use an opto-coupler for each unit (IC1, D3, D2).

# Mechanical Data (FXR-3-48G Power Shelf)

#### **Accessories:**

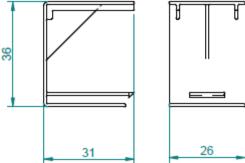

Center Angular Brackets are set in the middle for shelf mounting:

Center Angular Bracket sets can be ordered: Power-One part no.: HZZ01222 Note: Each Center Angular Bracket set contains 2 brackets and 8 screws.

#### Filler for covering empty shelf slots:

Filler can be ordered: Power-One part no.: XAK.00043.0

#### Plastic cover set for the bus bars:

Plastic cover set can be ordered: Power-One part no.: XEB.00031.0

Note1: Available upon special request.

Note2: Each plastic cover set contains 2 pieces.

#### Fulcrum:

The handle has been designed to allow easy plug-in and -out in a rack system. The handle (lever) fits into a counter piece (fulcrum) which is fixed to the bottom of the rack. During the plug, the fulcrum holds the unit down and guides it towards the output connector. The Power-One part number of the fulcrum and its associated mounting accessories is: HZZ01223.

Individual fulcrum sets can be also ordered: Power-One part no.: HZZ01223. Note: Each HZZ01223 set contain 2 fulcrums, 2 supports, and mounting accessories.

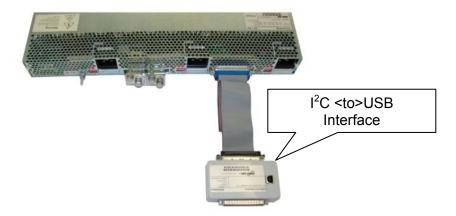

#### I<sup>2</sup>C to USB Interface HZZ02002G:

**I<sup>2</sup>C Management Software**: All FNP and FXP front-ends can be controlled via Power-One's GUI-driven I<sup>2</sup>C Management software and an I<sup>2</sup>C-to-USB interface (P/N HZZ02002G). An I<sup>2</sup>C Programming Manual describes the complete range of parameters that can be programmed to the FXP1500/1800 front-ends. This manual is available by searching on "FXP1500" at www.power-one.com.

NUCLEAR AND MEDICAL APPLICATIONS - Power-One products are not designed, intended for use in, or authorized for use as critical components in life support systems, equipment used in hazardous environments, or nuclear control systems without the express written consent of the respective divisional president of Power-One, Inc.

TECHNICAL REVISIONS - The appearance of products, including safety agency certifications pictured on labels, may change depending on the date manufactured. Specifications are subject to change without notice.