PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Product Description**

The KX023 is a tri-axis ±2g, ±4g or ±8g silicon micromachined accelerometer with integrated 256 byte buffer, orientation, tap/double tap, and activity detecting algorithms. The sense element is fabricated using Kionix's proprietary plasma micromachining process technology. Acceleration sensing is based on the principle of a differential capacitance arising from acceleration-induced motion of the sense element, which further utilizes common mode cancellation to decrease errors from process variation, temperature, and environmental stress. The sense element is hermetically sealed at the wafer level by bonding a second silicon lid wafer to the device using a glass frit. A separate ASIC device packaged with the sense element provides signal conditioning, user-programmable application algorithms. intelliaent accelerometer is delivered in a 3 x 3 x 0.9 mm LGA plastic package operating from a 1.71 – 3.6V DC supply. Voltage regulators are used to

maintain constant internal operating voltages over the range of input supply voltages. This results in stable operating characteristics over the range of input supply voltages and virtually undetectable ratiometric error. I<sup>2</sup>C or SPI digital protocol is used to communicate with the chip to configure and check for updates to the orientation, Directional Tap<sup>TM</sup> detection and activity monitoring algorithms.

#### **Features**

- 3 x 3 x 0.9 mm LGA

- User-selectable g Range and Output Data Rate

- User-selectable low power mode or high resolution mode

- Digital High-Pass Filter Outputs

- Embedded FIFO/FILO buffer

- Low Power Consumption with FlexSet™ Performance Optimization

- Internal voltage regulator

- Enhanced integrated Directional Tap/Double-Tap<sup>™</sup>, and Device-orientation Algorithms

- User-configurable wake-up function

- Digital I<sup>2</sup>C up to 3.4 MHz

- Digital 3-wire and 4-wire SPI up to 10 MHz

- Lead-free Solderability

- Excellent Temperature Performance

- High Shock Survivability

- Factory Programmed Offset and Sensitivity

- Self-test Function

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Table of Contents**

| PRODUCT DESCRIPTION                | 1  |

|------------------------------------|----|

| FEATURES                           | 1  |

| TABLE OF CONTENTS                  | 2  |

| FUNCTIONAL DIAGRAM                 | 6  |

| PRODUCT SPECIFICATIONS             | 7  |

| Mechanical                         |    |

| ELECTRICAL                         | 8  |

| Start Up Time Profile              |    |

| Current Profile                    |    |

| Power-On Procedure                 | 10 |

| Environmental                      | 11 |

| TERMINOLOGY                        | 12 |

| g                                  | 12 |

| Sensitivity                        |    |

| Zero-g offset                      |    |

| Self-test                          | 12 |

| Functionality                      | 13 |

| Sense element                      | _  |

| ASIC interface                     |    |

| Factory calibration                | 13 |

| Application Schematic              | 14 |

| PIN DESCRIPTIONS                   | 14 |

| TEST SPECIFICATIONS                | 15 |

| PACKAGE DIMENSIONS AND ORIENTATION | 16 |

| Dimensions                         | 16 |

| Orientation                        |    |

| DIGITAL INTERFACE                  | 19 |

| I <sup>2</sup> C Serial Interface  | 19 |

| I <sup>2</sup> C Operation         | 20 |

| Writing to 8-bit Register          | 21 |

| Reading from 8-bit Register        | 21 |

| Data Transfer Sequences            | 22 |

| HS-mode                            | 23 |

| I <sup>2</sup> C Timing Diagram    | 24 |

| SPI COMMUNICATIONS                 | 25 |

| 4-Wire SPI Interface               | 25 |

| 4-Wire SPI Timing Diagram          |    |

| 4-Wire Read and Write Registers    | 27 |

| 3-Wire SPI Interface               | 28 |

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

| 3-Wire SPI Timing Diagram       | 29 |

|---------------------------------|----|

| 3-Wire Read and Write Registers | 30 |

| EMBEDDED REGISTERS              | 31 |

| ACCELEROMETER OUTPUTS           | 32 |

| XHP L                           |    |

| XHP H                           |    |

| YHP L                           |    |

| YHP H                           |    |

|                                 |    |

|                                 |    |

| XOUT_L                          |    |

| XOUT_H                          | 34 |

| YOUT_L                          | 35 |

| YOUT_H                          | 35 |

| ZOUT_L                          | 35 |

| ZOUT_H                          | 35 |

| COTR                            | 36 |

| WHO_AM_I                        | 36 |

| TSCP                            |    |

| TSPP                            | 37 |

| INS1                            | 37 |

| INS2                            | 38 |

| INS3                            |    |

| STATUS_REG                      |    |

| INT_REL                         |    |

| CNTL1                           | 40 |

| CNTL2                           |    |

| CNTL3                           |    |

| ODCNTL                          |    |

| INC1                            | 45 |

| INC2                            |    |

| INC3                            |    |

| INC4                            |    |

| INC5                            | 47 |

| INC6                            |    |

| TILT_TIMER                      | 48 |

| WUFC                            | _  |

| TDTRC                           |    |

| TDTC                            |    |

| πн                              | 49 |

| ΠL                              | 50 |

| FTD                             |    |

| STD                             | 50 |

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

| TILT TWS ATH TILT_ANGLE_LL TILT_ANGLE_HL HYST_SET LP_CNTL BUF_CNTL1 BUF_CNTL2 BUF_STATUS_1 BUF_STATUS_1 BUF_STATUS_2 BUF_STATUS_2 BUF_STEAD SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE Hysteresis Device Orientation Angle (aka Tilt Angle) Tilt Timer MOTION INTERRUPT FEATURE DESCRIPTION  DIRECTIONAL TAP DETECTION FEATURE DESCRIPTION | 5152525353545556                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| ATH  TILT_ANGLE_LL  TILT_ANGLE_HL  HYST_SET  LP_CNTL  BUF_CNTL1  BUF_CNTL2  BUF_STATUS_1  BUF_STATUS_2  BUF_STATUS_2  BUF_STATUS_2  BUF_READ  SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis.  Device Orientation Angle (aka Tilt Angle)  Tilt Timer.  MOTION INTERRUPT FEATURE DESCRIPTION                                        | 52<br>52<br>53<br>54<br>55<br>56 |

| TILT_ANGLE_LL  TILT_ANGLE_HL  HYST_SET  LP_CNTL  BUF_CNTL1  BUF_CNTL2  BUF_STATUS_1  BUF_STATUS_2  BUF_STATUS_2  BUF_CLEAR  BUF_READ  SELF_TEST   EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis.  Device Orientation Angle (aka Tilt Angle)  Tilt Timer.  MOTION INTERRUPT FEATURE DESCRIPTION                                               | 52<br>53<br>53<br>54<br>55       |

| TILT_ANGLE_HL  HYST_SET  LP_CNTL  BUF_CNTL1  BUF_CNTL2  BUF_STATUS_1  BUF_STATUS_2  BUF_CLEAR  BUF_READ  SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis  Device Orientation Angle (aka Tilt Angle)  Tilt Timer  MOTION INTERRUPT FEATURE DESCRIPTION                                                                               | 52<br>53<br>54<br>55<br>56       |

| HYST_SET  LP_CNTL  BUF_CNTL1  BUF_CNTL2  BUF_STATUS_1  BUF_STATUS_2  BUF_CLEAR  BUF_READ  SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis  Device Orientation Angle (aka Tilt Angle)  Tilt Timer.  MOTION INTERRUPT FEATURE DESCRIPTION                                                                                             | 53<br>53<br>54<br>55<br>56       |

| LP_CNTL BUF_CNTL1 BUF_CNTL2 BUF_STATUS_1 BUF_STATUS_2 BUF_CLEAR BUF_READ SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis Device Orientation Angle (aka Tilt Angle) Tilt Timer.  MOTION INTERRUPT FEATURE DESCRIPTION                                                                                                                | 53<br>54<br>55<br>56             |

| BUF_CNTL1 BUF_CNTL2 BUF_STATUS_1 BUF_STATUS_2 BUF_CLEAR BUF_READ SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis Device Orientation Angle (aka Tilt Angle) Tilt Timer.  MOTION INTERRUPT FEATURE DESCRIPTION                                                                                                                        | 54<br>55<br>56                   |

| BUF_CNTL2  BUF_STATUS_1  BUF_STATUS_2  BUF_CLEAR  BUF_READ  SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis  Device Orientation Angle (aka Tilt Angle)  Tilt Timer.  MOTION INTERRUPT FEATURE DESCRIPTION                                                                                                                           | 55<br>56<br>56                   |

| BUF_STATUS_1  BUF_STATUS_2  BUF_CLEAR  BUF_READ  SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis  Device Orientation Angle (aka Tilt Angle)  Tilt Timer.  MOTION INTERRUPT FEATURE DESCRIPTION                                                                                                                                      | 56<br>56                         |

| BUF_STATUS_2  BUF_CLEAR  BUF_READ  SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis.  Device Orientation Angle (aka Tilt Angle)  Tilt Timer.  Motion Interrupt Feature Description                                                                                                                                                   | 56                               |

| BUF_CLEAR BUF_READ SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis.  Device Orientation Angle (aka Tilt Angle)  Tilt Timer.  MOTION INTERRUPT FEATURE DESCRIPTION                                                                                                                                                                   |                                  |

| BUF_READ  SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE  Hysteresis.  Device Orientation Angle (aka Tilt Angle)  Tilt Timer.  MOTION INTERRUPT FEATURE DESCRIPTION                                                                                                                                                                            |                                  |

| SELF_TEST  EMBEDDED APPLICATIONS  ORIENTATION DETECTION FEATURE                                                                                                                                                                                                                                                                                                 | 56                               |

| ORIENTATION DETECTION FEATURE                                                                                                                                                                                                                                                                                                                                   | 57                               |

| Orientation Detection Feature                                                                                                                                                                                                                                                                                                                                   | 57                               |

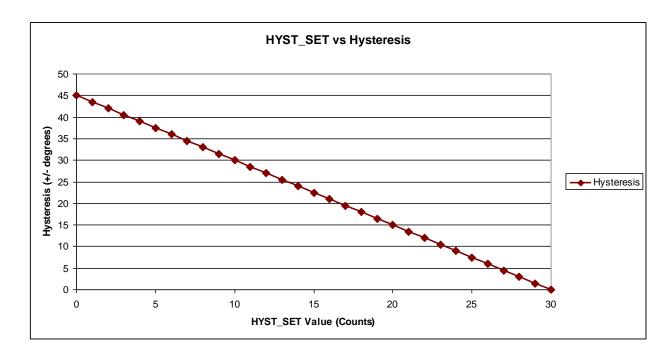

| Hysteresis  Device Orientation Angle (aka Tilt Angle)  Tilt Timer  Motion Interrupt Feature Description                                                                                                                                                                                                                                                         | 58                               |

| Device Orientation Angle (aka Tilt Angle)                                                                                                                                                                                                                                                                                                                       | 58                               |

| Tilt Timer Motion Interrupt Feature Description                                                                                                                                                                                                                                                                                                                 | 58                               |

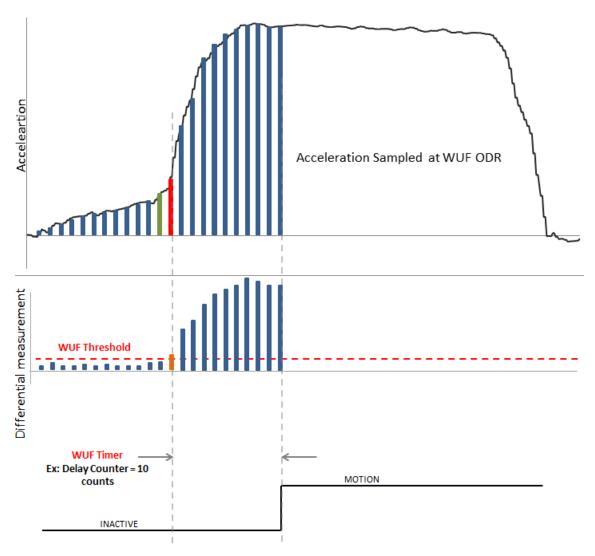

| Motion Interrupt Feature Description                                                                                                                                                                                                                                                                                                                            |                                  |

|                                                                                                                                                                                                                                                                                                                                                                 | 60                               |

| DIRECTIONAL TAP DETECTION FEATURE DESCRIPTION                                                                                                                                                                                                                                                                                                                   | 61                               |

|                                                                                                                                                                                                                                                                                                                                                                 | 63                               |

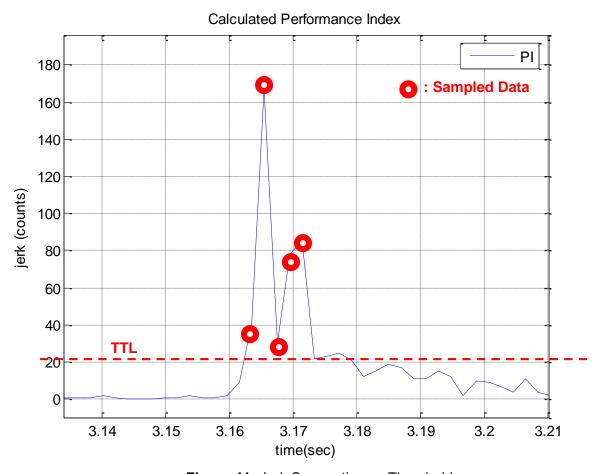

| Performance Index                                                                                                                                                                                                                                                                                                                                               | 63                               |

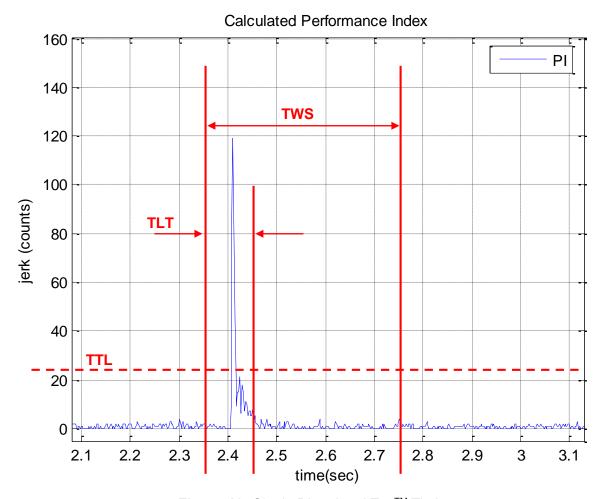

| Single Tap Detection                                                                                                                                                                                                                                                                                                                                            | 64                               |

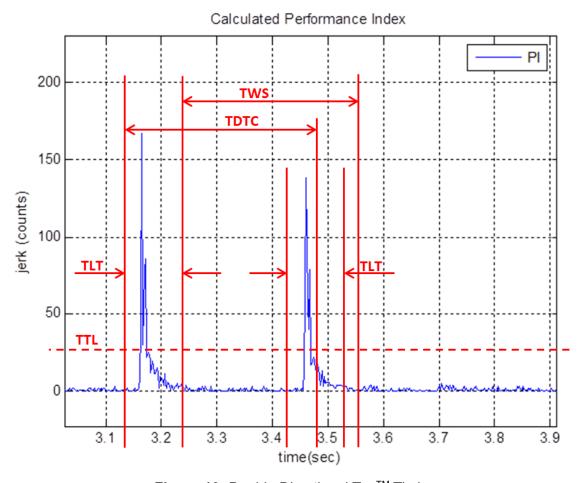

| Double Tap Detection                                                                                                                                                                                                                                                                                                                                            | 65                               |

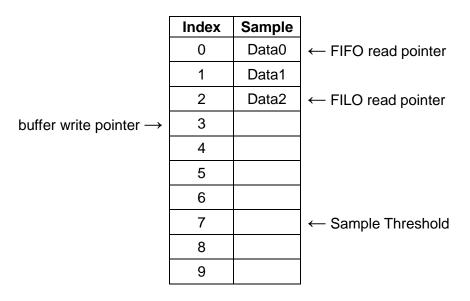

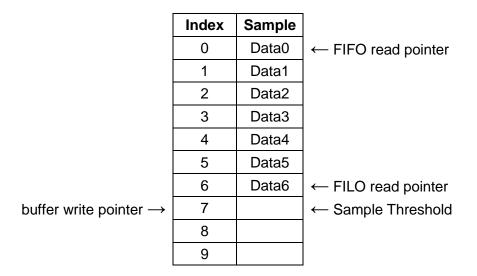

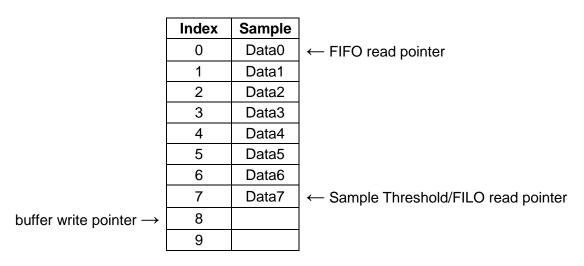

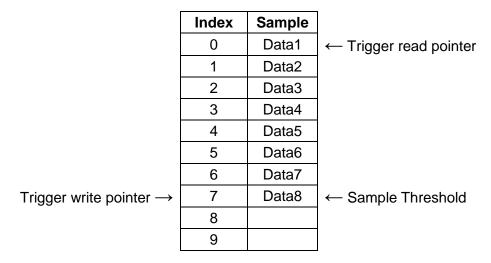

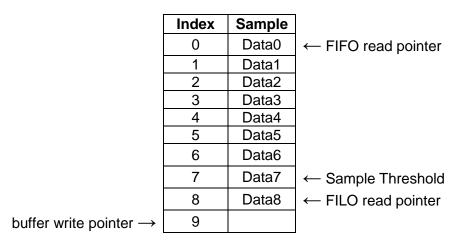

| Sample Buffer Feature Description                                                                                                                                                                                                                                                                                                                               | 66                               |

| FIFO Mode                                                                                                                                                                                                                                                                                                                                                       | 6 <i>6</i>                       |

| Stream Mode                                                                                                                                                                                                                                                                                                                                                     | 6 <i>6</i>                       |

| Trigger Mode                                                                                                                                                                                                                                                                                                                                                    | 67                               |

| FILO Mode                                                                                                                                                                                                                                                                                                                                                       | 67                               |

| Buffer Operation                                                                                                                                                                                                                                                                                                                                                | 67                               |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                | 73                               |

| NOTICE 75                                                                                                                                                                                                                                                                                                                                                       |                                  |

| Precaution on using KIONIX Products                                                                                                                                                                                                                                                                                                                             | 75                               |

| Precaution for Mounting / Circuit board design                                                                                                                                                                                                                                                                                                                  | 76                               |

| Precautions Regarding Application Examples and External Circuits                                                                                                                                                                                                                                                                                                | 76                               |

| Precaution for Electrostatic                                                                                                                                                                                                                                                                                                                                    | 76                               |

| Precaution for Storage / Transportation                                                                                                                                                                                                                                                                                                                         | 76                               |

| Precaution for Product Label                                                                                                                                                                                                                                                                                                                                    |                                  |

| Precaution for Disposition                                                                                                                                                                                                                                                                                                                                      | 77                               |

| PRECAUTION FOR FOREIGN EXCHANGE AND FOREIGN TRADE ACT                                                                                                                                                                                                                                                                                                           |                                  |

| Precaution Regarding Intellectual Property Rights                                                                                                                                                                                                                                                                                                               | 77                               |

| OTHER PRECAUTION                                                                                                                                                                                                                                                                                                                                                | 77<br>77                         |

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

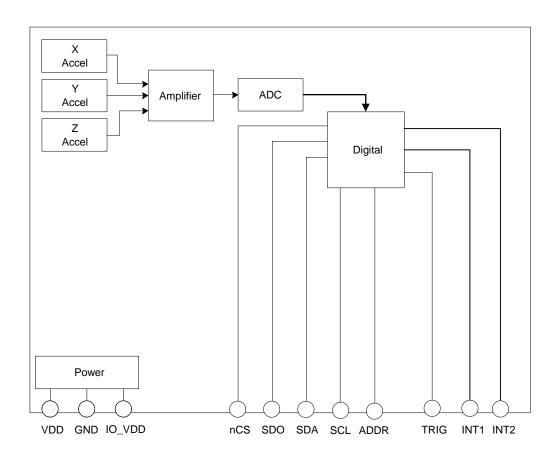

### **Functional Diagram**

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Product Specifications**

#### **Mechanical**

(Specifications are for operation at VDD = 2.5V and T = RT = 25°C unless stated otherwise)

| Pa                                             | arameters                             | Units    | Min                   | Typical | Max   |

|------------------------------------------------|---------------------------------------|----------|-----------------------|---------|-------|

| Operating Temperatur                           | e Range                               | °C       | -40                   | -       | 85    |

| Zero-g Offset                                  |                                       | mg       |                       | ±25     | ±90   |

| Zero-g Offset Variation                        | mg/°C                                 |          | 0.2                   |         |       |

|                                                | GSEL1=0, GSEL0=0 (± 2g)               |          | 15565                 | 16384   | 17203 |

| Sensitivity <sup>1</sup>                       | GSEL1=0, GSEL0=1 (± 4g)               | counts/g | 7782                  | 8192    | 8602  |

|                                                | GSEL1=1, GSEL0=0 (± 8g)               |          | 3891                  | 4096    | 4301  |

|                                                | GSEL1=0, GSEL0=0 (± 2g)               | counts/g | 61                    | 64      | 67    |

| Sensitivity (Ruffor 8 bit mode) <sup>1,2</sup> | GSEL1=0, GSEL0=1 (± 4g)               |          | 30                    | 32      | 34    |

| (Buffer 8-bit mode) <sup>1,2</sup>             | GSEL1=1, GSEL0=0 (± 8g)               |          | 15                    | 16      | 17    |

| Sensitivity Variation from                     | %/°C                                  |          | 0.01                  |         |       |

| Positive Self-Test Out                         | put change on Activation <sup>5</sup> | g        | 0.35                  | 0.5     | 0.65  |

| Mechanical Resonance                           | Hz                                    |          | 3500 (xy)<br>1800 (z) |         |       |

| Non-Linearity                                  | % of FS                               |          | 0.6                   |         |       |

| Cross Axis Sensitivity                         | %                                     |          | 2                     |         |       |

| Noise (RMS at 50Hz v                           | vith low-pass filter = ODR/9)4        | mg       |                       | 0.75    |       |

Table 1: Mechanical Specifications

#### Notes:

- 1. Resolution and acceleration ranges are user selectable via I<sup>2</sup>C or SPI.

- 2. Sensitivity is proportional to BRES in BUF\_CNTL2.

- 3. Resonance as defined by the dampened mechanical sensor.

- 4. Noise varies with Output Data Rate (ODR) and Current Consumption settings. Contact Kionix Engineering for additional details on FlexSet™ Performance Optimization.

- 5. Requires changing of STPOL bit in INC1 register to 1 prior to performing self-test.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Electrical**

(Specifications are for operation at VDD = 2.5V and T =  $25^{\circ}$ C unless stated otherwise)

| P                                   | arameters                             | Units    | Min          | Typical | Max          |

|-------------------------------------|---------------------------------------|----------|--------------|---------|--------------|

| Supply Voltage (VDD)                | Operating                             | <b>V</b> | 1.71         | 2.5     | 3.6          |

| I/O Pads Supply Voltage             | ge (IO_VDD)                           | V        | 1.7          |         | VDD          |

|                                     | High Resolution Mode (RES = 1)        |          |              | 145     |              |

| Current                             | Low Power Mode <sup>1</sup> (RES = 0) | μΑ       |              | 10      |              |

| Consumption                         | Standby                               |          |              | 0.9     |              |

| Output Low Voltage (IC              | D_VDD < 2V) <sup>2</sup>              | V        | -            | -       | 0.2 * IO_VDD |

| Output Low Voltage (IC              | D_VDD ≥ 2V) <sup>2</sup>              | <b>V</b> | -            | -       | 0.4          |

| Output High Voltage                 |                                       | V        | 0.8 * IO_VDD | -       | -            |

| Input Low Voltage                   |                                       | V        | -            | -       | 0.2 * IO_VDD |

| Input High Voltage                  |                                       | V        | 0.8 * IO_VDD | -       | -            |

| Input Pull-down Currer              | nt                                    | μΑ       |              | 0       |              |

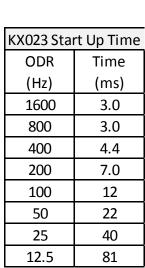

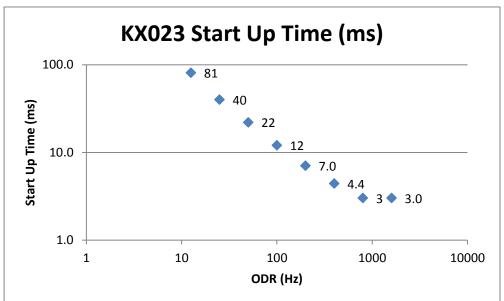

| Start Up Time <sup>3</sup>          |                                       | ms       | 2.0          |         | 650          |

| Power Up Time <sup>4</sup>          |                                       | ms       |              | 10      |              |

| I <sup>2</sup> C Communication Ra   | ate                                   | MHz      |              |         | 3.4          |

| SPI Communication Rate              |                                       |          |              |         | 10           |

| Output Data Rate (ODR) <sup>5</sup> |                                       |          | 0.781        | 50      | 1600         |

|                                     | RES = 0                               | Hz       |              | 800     |              |

| Bandwidth (-3dB) <sup>6</sup>       | RES = 1                               | Hz       |              | ODR/2   |              |

**Table 2:** Electrical Specifications

#### Notes:

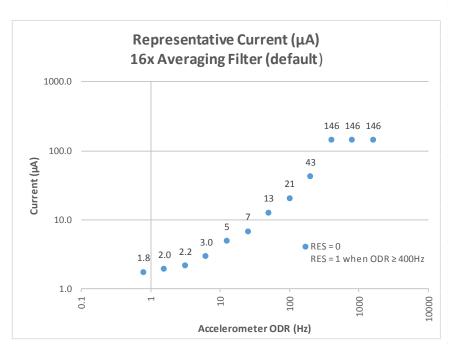

- Current varies with Output Data Rate (ODR) as shown the chart below, and with Noise level settings. Contact Kionix Engineering for additional details on FlexSet™ Performance Optimization.

- 2. For I $^2$ C communication, this assumes a minimum 1.5K $\Omega$  pull-up resistor on SCL and SDA pins.

- 3. Startup time is from PC1 set to valid outputs. Time varies with Output Data Rate (ODR); see chart below

- 4. Power up time is from VDD valid to device boot completion.

- 5. User selectable through I<sup>2</sup>C or SPI.

- 6. User selectable and dependent on ODR and RES.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

### **Start Up Time Profile**

#### **Current Profile**

| Represer | ntative Cu | rrent Profile |

|----------|------------|---------------|

| ODR (Hz) | RES        | Current (µA)  |

| 0        | Standby    | 0.9           |

| 0.781    | 0          | 1.8           |

| 1.563    | 0          | 2.0           |

| 3.125    | 0          | 2.2           |

| 6.25     | 0          | 3.0           |

| 12.5     | 0          | 5             |

| 25       | 0          | 7             |

| 50       | 0          | 13            |

| 100      | 0          | 21            |

| 200      | 0          | 43            |

| 400      | 1          | 146           |

| 800      | 1          | 146           |

| 1600     | 1          | 146           |

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Power-On Procedure**

Proper functioning of power-on reset (POR) is dependent on the specific **VDD**, **VDD**<sub>Low</sub>,  $T_{VDD}$  (rise time), and  $T_{VDD\_off}$  profile of individual applications. It is recommended to minimize **VDD**<sub>Low</sub>, and  $T_{VDD}$ , and maximize  $T_{VDD\_off}$ . It is also advised that the **VDD** ramp up time  $T_{VDD}$  be monotonic. Note that the outputs will not be stable until **VDD** has reached its final value.

To assure proper POR, the application should be evaluated over the customer specified range of VDD, VDD<sub>Low</sub>, T<sub>VDD</sub>, T<sub>VDD\_Off</sub> and temperature as POR performance can vary depending on these parameters.

Please refer to Technical Note *TN014 KX022, KX023 Accelerometer Power-On Procedure* for more information.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Environmental**

| Paran                | neters          | Units | Min  | Typical                           | Max  |

|----------------------|-----------------|-------|------|-----------------------------------|------|

| Supply Voltage (VDD) | Absolute Limits | V     | -0.5 | -                                 | 3.63 |

| Operating Temperatur | e Range         | °C    | -40  | -                                 | 85   |

| Storage Temperature  | Range           | °C    | -55  | -                                 | 150  |

| Mech. Shock (powered | g               | -     | -    | 5000 for 0.5ms<br>10000 for 0.2ms |      |

| ESD                  | V               | -     | -    | 2000                              |      |

Table 3: Environmental Specifications

Caution: ESD Sensitive and Mechanical Shock Sensitive Component, improper handling can cause permanent damage to the device.

These products conform to RoHS Directive 2011/65/EU of the European Parliament and of the Council of the European Union that was issued June 8, 2011. Specifically, these products do not contain any non-exempted amounts of lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB) or polybrominated diphenyl ethers (PBDE)

above the maximum concentration values (MCV) by weight in any of its homogenous materials. Homogenous materials are "of uniform composition throughout". The MCV for lead, mercury, hexavalent chromium, PBB, and PBDE is 0.10%. The MCV for cadmium is 0.010%.

<u>Applicable Exemption:</u> 7C-I - Electrical and electronic components containing lead in a glass or ceramic other than dielectric ceramic in capacitors (piezoelectronic devices) or in a glass or ceramic matrix compound.

These products are also in conformance with REACH Regulation No 1907/2006 of the European Parliament and of the Council that was issued Dec. 30, 2011. They do not contain any Substances of Very High Concern (SVHC-161) as identified by the European Chemicals Agency as of 17 December 2014.

This product is halogen-free per IEC 61249-2-21. Specifically, the materials used in this product contain a maximum total halogen content of 1500 ppm with less than 900-ppm bromine and less than 900-ppm chlorine.

#### Soldering

Soldering recommendations are available upon request or from www.kionix.com.

36 Thornwood Dr. – Ithaca, NY 14850 tel: 607-257-1080 – fax:607-257-1146 www.kionix.com - info@kionix.com

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Terminology**

g

A unit of acceleration equal to the acceleration of gravity at the earth's surface.

$$1g = 9.8 \frac{m}{s^2}$$

One thousandth of a g (0.0098 m/ s<sup>2</sup>) is referred to as 1 milli-g (1 mg).

#### Sensitivity

The sensitivity of an accelerometer is the change in output per unit of input acceleration at nominal VDD and temperature. The term is essentially the gain of the sensor expressed in counts per g (counts/g) or LSB's per g (LSB/g). Occasionally, sensitivity is expressed as a resolution, i.e. milli-g per LSB (mg/LSB) or milli-g per count (mg/count). Sensitivity for a given axis is determined by measurements of the formula:

$$Sensitivity = \frac{\left(Output @+1g - Output @-1g\right)}{2g}$$

The sensitivity tolerance describes the range of sensitivities that can be expected from a large population of sensors at room temperature and over life. When the temperature deviates from room temperature (25°C), the sensitivity will vary by the amount shown in Table 1.

#### Zero-g offset

Zero-g offset or 0-g offset describes the actual output of the accelerometer when no acceleration is applied. Ideally, the output would always be in the middle of the dynamic range of the sensor (content of the OUTX, OUTY, OUTZ registers = 00h, expressed as a 2's complement number). However, because of mismatches in the sensor, calibration errors, and mechanical stress, the output can deviate from 00h. This deviation from the ideal value is called 0-g offset. The zero-g offset tolerance describes the range of 0-g offsets of a population of sensors over the operating temperature range.

#### Self-test

Self-test allows a functional test of the sensor without applying a physical acceleration to it. When activated, an electrostatic force is applied to the sensor, simulating an input acceleration. The sensor outputs respond accordingly. If the output signals change within the amplitude specified in Table 1, then the sensor is working properly and the parameters of the interface chip are within the defined specifications.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Functionality**

#### Sense element

The sense element is fabricated using Kionix's proprietary plasma micromachining process technology. This process technology allows Kionix to create mechanical silicon structures which are essentially mass-spring systems that move in the direction of the applied acceleration. Acceleration sensing is based on the principle of a differential capacitance arising from the acceleration-induced motion. Capacitive plates on the moving mass move relative to fixed capacitive plates anchored to the substrate. The sense element is hermetically sealed at the wafer level by bonding a second silicon lid wafer to the device using a glass frit.

#### **ASIC** interface

A separate ASIC device packaged with the sense element provides all of the signal conditioning and communication with the sensor. The complete measurement chain is composed by a low-noise capacitance to voltage amplifier which converts the differential capacitance of the MEMS sensor into an analog voltage that is sent through an analog-to-digital converter. The acceleration data may be accessed through the I<sup>2</sup>C digital communications provided by the ASIC. In addition, the ASIC contains all of the logic to allow the user to choose data rates, g-ranges, filter settings, and interrupt logic. Plus, there are two programmable state machines which allow the user to create unique embedded functions based on changes in acceleration.

#### **Factory calibration**

Kionix trims the offset and sensitivity of each accelerometer by adjusting gain (sensitivity) and 0-g offset trim codes stored in nonvolatile memory (OTP). Additionally, all functional register default values are also programmed into the nonvolatile memory. Every time the device is turned on or a software reset command is issued, the trimming parameters and default register values are downloaded into the volatile registers to be used during active operation. This allows the device to function without further calibration.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

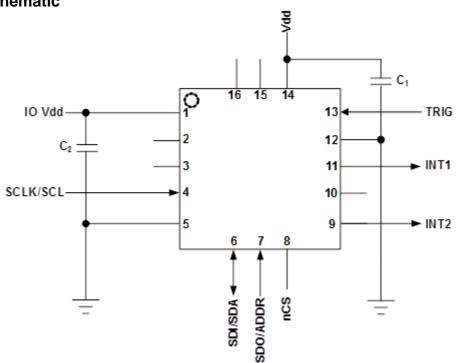

### **Application Schematic**

### **Pin Descriptions**

| Pin | Name     | Description                                                                                                                      |  |  |  |  |  |  |  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1   | IO_VDD   | The power supply input for the digital communication bus. Optionally decouple this pin to ground with a 0.1uF ceramic capacitor. |  |  |  |  |  |  |  |

| 2   | NC       | Not Internally Connected – Can be connected to VDD, IO_VDD, GND or Float                                                         |  |  |  |  |  |  |  |

| 3   | NC       | Not Internally Connected – Can be connected to VDD, IO_VDD, GND or Float                                                         |  |  |  |  |  |  |  |

| 4   | SCLK/SCL | SPI and I <sup>2</sup> C Serial Clock                                                                                            |  |  |  |  |  |  |  |

| 5   | GND      | Ground                                                                                                                           |  |  |  |  |  |  |  |

| 6   | SDI/SDA  | SPI Data input / I2C Serial Data                                                                                                 |  |  |  |  |  |  |  |

| 7   | SDO/ADDR | Serial Data Out pin during 4 wire SPI communication and part of the device address during I2C communication.                     |  |  |  |  |  |  |  |

| 8   | nCS      | SPI enable / I2C mode select (GND = SPI enabled, I2C communication disabled / IO_VDD = SPI disabled, I2C communication enabled)  |  |  |  |  |  |  |  |

| 9   | INT2     | Physical Interrupt 2                                                                                                             |  |  |  |  |  |  |  |

| 10  | NC       | Not Internally Connected – Can be connected to VDD, IO_VDD, GND or Float                                                         |  |  |  |  |  |  |  |

| 11  | INT1     | Physical Interrupt 1                                                                                                             |  |  |  |  |  |  |  |

| 12  | GND      | Ground                                                                                                                           |  |  |  |  |  |  |  |

| 13  | TRIG     | Trigger pin for FIFO buffer control – Connect to GND when not using external trigger option                                      |  |  |  |  |  |  |  |

| 14  | VDD      | The power supply input. Decouple this pin to ground with a 0.1uF ceramic capacitor.                                              |  |  |  |  |  |  |  |

| 15  | NC       | Not Internally Connected – Can be connected to VDD, IO_VDD, GND or Float                                                         |  |  |  |  |  |  |  |

| 16  | NC       | Not Internally Connected – Can be connected to VDD, IO_VDD, GND or Float                                                         |  |  |  |  |  |  |  |

Table 4: Pin Descriptions

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

### **Test Specifications**

These characteristics have been identified as being critical to the customer. Every part is tested to verify its conformance to specification prior to shipment.

| Parameter                                | Specification        | Test Conditions   |

|------------------------------------------|----------------------|-------------------|

| Zero-g Offset @ RT1 (2g range)           | 0 ± 1475 counts      | 25°C, VDD = 2.5 V |

| Sensitivity @ RT <sup>1</sup> (2g range) | 16384 ± 819 counts/g | 25°C, VDD = 2.5 V |

Table 5: Test Specifications

<sup>&</sup>lt;sup>1</sup>Room Temperature = 25°C

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

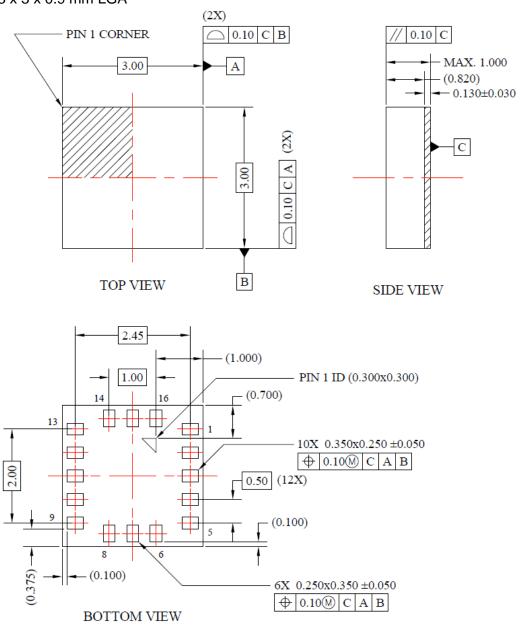

### **Package Dimensions and Orientation**

#### **Dimensions**

3 x 3 x 0.9 mm LGA

All dimensions and tolerances conform to ASME Y14.5M-1994

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

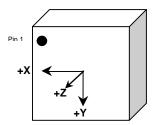

#### Orientation

When device is accelerated in +X, +Y or +Z direction, the corresponding output will increase.

### Static X/Y/Z Output Response versus Orientation to Earth's surface (1g): GSEL1=0, GSEL0=0 (± 2g)

**Position** Top **Bottom** Diagram **Bottom** Top Resolution (bits) -16384 -64 X (counts) -16384 Y (counts) -64 Z (counts) -16384 -64 X-Polarity Y-Polarity + **Z-Polarity**

**↓** (1g)

Earth's Surface

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

### Static X/Y/Z Output Response versus Orientation to Earth's surface (1g):

GSEL1=0, GSEL0=1 (± 4g)

| Position          | 1     |     | 2     | 2   |               | 3  |            | 4  |      | 5  |       |     |

|-------------------|-------|-----|-------|-----|---------------|----|------------|----|------|----|-------|-----|

| Diagram           |       |     |       |     | Top<br>Bottom |    | Bottom Top |    |      |    |       |     |

| Resolution (bits) | 16    | 8   | 16    | 8   | 16            | 8  | 16         | 8  | 16   | 8  | 16    | 8   |

| X (counts)        | 0     | 0   | -8192 | -32 | 0             | 0  | 8192       | 32 | 0    | 0  | 0     | 0   |

| Y (counts)        | -8192 | -32 | 0     | 0   | 8192          | 32 | 0          | 0  | 0    | 0  | 0     | 0   |

| Z (counts)        | 0     | 0   | 0     | 0   | 0             | 0  | 0          | 0  | 8192 | 32 | -8192 | -32 |

|                   |       |     |       |     |               |    |            |    |      |    |       |     |

| X-Polarity        | 0     |     | -     |     | 0             |    | +          |    | 0    |    | 0     |     |

| Y-Polarity        | -     |     | 0     |     | +             |    | 0          |    | 0    |    | 0     |     |

| Z-Polarity        | 0     |     | 0     | -   |               | 0  |            | 0  |      | +  |       |     |

(1g)

Earth's Surface

### Static X/Y/Z Output Response versus Orientation to Earth's surface (1g):

GSEL1=1, GSEL0=0 (± 8g)

| Position          | 1     |     | 2     |     | 3    | 3  |      | 4  |               | 5  |            | 6   |   |  |

|-------------------|-------|-----|-------|-----|------|----|------|----|---------------|----|------------|-----|---|--|

| Diagram           |       |     |       |     |      |    |      |    | Top<br>Bottom |    | Bottom Top |     |   |  |

| Resolution (bits) | 16    | 8   | 16    | 8   | 16   | 8  | 16   | 8  | 16            | 8  | 16         | 8   |   |  |

| X (counts)        | 0     | 0   | -4096 | -16 | 0    | 0  | 4096 | 16 | 0             | 0  | 0          | 0   |   |  |

| Y (counts)        | -4096 | -16 | 0     | 0   | 4096 | 16 | 0    | 0  | 0             | 0  | 0          | 0   |   |  |

| Z (counts)        | 0     | 0   | 0     | 0   | 0    | 0  | 0    | 0  | 4096          | 16 | -4096      | -16 |   |  |

|                   |       |     |       |     |      |    |      |    |               |    |            |     |   |  |

| X-Polarity        | 0     |     | -     | -   |      | -  |      | 0  |               | +  |            |     | 0 |  |

| Y-Polarity        | -     |     | 0     |     | +    |    | 0    |    | 0             |    | 0          |     |   |  |

| Z-Polarity        | 0     |     | 0     |     | 0    |    | 0    |    | +             |    | -          |     |   |  |

| <b>1</b> (1g)     |       |     |       |     |      |    |      |    |               |    |            |     |   |  |

Earth's Surface

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Digital Interface**

The Kionix KX023 digital accelerometer has the ability to communicate via the I<sup>2</sup>C and SPI digital serial interface protocols. This allows for easy system integration by eliminating analog-to-digital converter requirements and by providing direct communication with system micro-controllers.

The serial interface terms and descriptions as indicated in Table 6 below will be observed throughout this document.

| Term        | Description                                                                               |

|-------------|-------------------------------------------------------------------------------------------|

| Transmitter | The device that transmits data to the bus.                                                |

| Receiver    | The device that receives data from the bus.                                               |

| Master      | The device that initiates a transfer, generates clock signals, and terminates a transfer. |

| Slave       | The device addressed by the Master.                                                       |

Table 6. Serial Interface Terminologies

#### I<sup>2</sup>C Serial Interface

As previously mentioned, the KX023 has the ability to communicate on an I<sup>2</sup>C bus. I<sup>2</sup>C is primarily used for synchronous serial communication between a Master device and one or more Slave devices. The Master, typically a micro controller, provides the serial clock signal and addresses Slave devices on the bus. The KX023 always operates as a Slave device during standard Master-Slave I<sup>2</sup>C operation.

I<sup>2</sup>C is a two-wire serial interface that contains a Serial Clock (SCL) line and a Serial Data (SDA) line. SCL is a serial clock that is provided by the Master, but can be held low by any Slave device, putting the Master into a wait condition. SDA is a bi-directional line used to transmit and receive data to and from the interface. Data is transmitted MSB (Most Significant Bit) first in 8-bit per byte format, and the number of bytes transmitted per transfer is unlimited. The I<sup>2</sup>C bus is considered free when both lines are high.

The I2C interface is compliant with high-speed mode, fast mode and standard mode I2C protocols.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

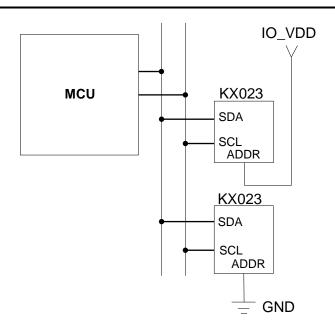

Figure 1: Multiple KX023 I<sup>2</sup>C Connection

#### **I2C Address**

|             | Address | 7 bit   |         |     |     |     |     |     |     |     |     |

|-------------|---------|---------|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Description | Pad     | Address | Address | <7> | <6> | <5> | <4> | <3> | <2> | <1> | <0> |

| I2C Wr      | IO_VDD  | 1Fh     | 3Eh     | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 0   |

| I2C Rd      | IO_VDD  | 1Fh     | 3Fh     | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1   |

| I2C Wr      | GND     | 1Eh     | 3Ch     | 0   | 0   | 1   | 1   | 1   | 1   | 0   | 0   |

| I2C Rd      | GND     | 1Eh     | 3Dh     | 0   | 0   | 1   | 1   | 1   | 1   | 0   | 1   |

#### I<sup>2</sup>C Operation

Transactions on the I<sup>2</sup>C bus begin after the Master transmits a start condition (S), which is defined as a high-to-low transition on the data line while the SCL line is held high. The bus is considered busy after this condition. The next byte of data transmitted after the start condition contains the Slave Address (SAD) in the seven MSBs (Most Significant Bits), and the LSB (Least Significant Bit) tells whether the Master will be receiving data '1' from the Slave or transmitting data '0' to the Slave. When a Slave Address is sent, each device on the bus compares the seven MSBs with its internally stored address. If they match, the device considers itself addressed by the Master. The KX023's Slave Address is comprised of a programmable part and a fixed part, which allows for connection of multiple KX023's to the same I<sup>2</sup>C bus. The Slave Address associated with the KX023 is 001111X, where the programmable bit, X, is determined by the assignment of ADDR (pin 7) to GND or IO\_VDD. Figure 1 above shows how two KX023's would be implemented on an I<sup>2</sup>C bus.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

It is mandatory that receiving devices acknowledge (ACK) each transaction. Therefore, the transmitter must release the SDA line during this ACK pulse. The receiver then pulls the data line low so that it remains stable low during the high period of the ACK clock pulse. A receiver that has been addressed, whether it is Master or Slave, is obliged to generate an ACK after each byte of data has been received. To conclude a transaction, the Master must transmit a stop condition (P) by transitioning the SDA line from low to high while SCL is high. The I<sup>2</sup>C bus is now free. Note that if the KX023 is accessed through I<sup>2</sup>C protocol before the startup is finished a NACK signal is sent.

#### Writing to 8-bit Register

Upon power up, the Master must write to the KX023's control registers to set its operational mode. Therefore, when writing to a control register on the I²C bus, as shown Sequence 1 on the following page, the following protocol must be observed: After a start condition, SAD+W transmission, and the KX023 ACK has been returned, an 8-bit Register Address (RA) command is transmitted by the Master. This command is telling the KX023 to which 8-bit register the Master will be writing the data. Since this is I²C mode, the MSB of the RA command should always be zero (0). The KX023 acknowledges the RA and the Master transmits the data to be stored in the 8-bit register. The KX023 acknowledges that it has received the data and the Master transmits a stop condition (P) to end the data transfer. The data sent to the KX023 is now stored in the appropriate register. The KX023 automatically increments the received RA commands and, therefore, multiple bytes of data can be written to sequential registers after each Slave ACK as shown in Sequence 2 on the following page.

Note\*\* If a STOP condition is sent on the least significant bit of write data or the following master acknowledge cycle, the last write operation is not guaranteed and it may alter the content of the affected registers.

#### Reading from 8-bit Register

When reading data from a KX023 8-bit register on the I<sup>2</sup>C bus, as shown in Sequence 3 on the next page, the following protocol must be observed: The Master first transmits a start condition (S) and the appropriate Slave Address (SAD) with the LSB set at '0' to write. The KX023 acknowledges and the Master transmits the 8-bit RA of the register it wants to read. The KX023 again acknowledges, and the Master transmits a repeated start condition (Sr). After the repeated start condition, the Master addresses the KX023 with a '1' in the LSB (SAD+R) to read from the previously selected register. The Slave then acknowledges and transmits the data from the requested register. The Master does not acknowledge (NACK) it received the transmitted data, but transmits a stop condition to end the data transfer. The accelerometer automatically increments through its sequential registers, allowing data to be read from multiple registers following a single SAD+R command as shown below in Sequence 4 on the following page. Reading data from a buffer read register is a special case because if register address (RA) is set to buffer read register (BUF\_READ) in Sequence 4, the register autoincrement feature is automatically disabled. Instead, the Read Pointer will increment to the next data in the buffer, thus allowing reading multiple bytes of data from the buffer using a single SAD+R command.

Note\*\* Accelerometer's output data should be read in a single transaction using the auto-increment feature to prevent output data from being updated prior to intended completion of the read transaction.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Data Transfer Sequences**

The following information clearly illustrates the variety of data transfers that can occur on the I<sup>2</sup>C bus and how the Master and Slave interact during these transfers. **Table 7** defines the I<sup>2</sup>C terms used during the data transfers.

| Term | Definition                |

|------|---------------------------|

| S    | Start Condition           |

| Sr   | Repeated Start Condition  |

| SAD  | Slave Address             |

| W    | Write Bit                 |

| R    | Read Bit                  |

| ACK  | Acknowledge               |

| NACK | Not Acknowledge           |

| RA   | Register Address          |

| Data | Transmitted/Received Data |

| Р    | Stop Condition            |

Table 7: I<sup>2</sup>C Terms

#### **Sequence 1:** The Master is writing one byte to the Slave.

| Master | S | SAD + W |     | RA |     | DATA |     | Р |

|--------|---|---------|-----|----|-----|------|-----|---|

| Slave  |   |         | ACK |    | ACK |      | ACK |   |

#### **Sequence 2:** The Master is writing multiple bytes to the Slave.

| Master | S | SAD + W |     | RA |     | DATA |     | DATA |     | Ρ |

|--------|---|---------|-----|----|-----|------|-----|------|-----|---|

| Slave  |   |         | ACK |    | ACK |      | ACK |      | ACK |   |

#### **Sequence 3:** The Master is receiving one byte of data from the Slave.

| Master | S | SAD + W |     | RA |     | Sr | SAD + R |     |      | NACK | Р |

|--------|---|---------|-----|----|-----|----|---------|-----|------|------|---|

| Slave  |   |         | ACK |    | ACK |    |         | ACK | DATA |      |   |

#### **Sequence 4:** The Master is receiving multiple bytes of data from the Slave.

| Master | S | SAD + W |     | RA |            | Sr | SAD + R |     |      | ACK |      | NACK | Р |

|--------|---|---------|-----|----|------------|----|---------|-----|------|-----|------|------|---|

| Slave  |   |         | ACK |    | <b>ACK</b> |    |         | ACK | DATA |     | DATA |      |   |

36 Thornwood Dr. – Ithaca, NY 14850 tel: 607-257-1080 – fax:607-257-1146 www.kionix.com - info@kionix.com

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **HS-mode**

To enter the 3.4MHz high speed mode of communication, the device must receive the following sequence of conditions from the master: a Start condition followed by a Master code (00001XXX) and a Master Non-acknowledge. Once recognized, the device switches to HS-mode communication. Read/write data transfers then proceed as described in the sequences above. Devices return to the FS-mode after a STOP occurrence on the bus.

**Sequence 5:** HS-mode data transfer of the Master writing multiple bytes to the Slave.

| Speed  |   | FS-mode | )    |    | HS-mode |     |    |     |      |     | FS-mode |  |

|--------|---|---------|------|----|---------|-----|----|-----|------|-----|---------|--|

| Master | S | M-code  | NACK | Sr | SAD + W |     | RA |     | DATA |     | Р       |  |

| Slave  |   |         |      |    |         | ACK |    | ACK |      | ACK |         |  |

n bytes + ack.

Sequence 6: HS-mode data transfer of the Master receiving multiple bytes of data from the Slave.

| Speed  |   | FS-mode | Э    |    | HS-mode |     |    |     |  |  |  |

|--------|---|---------|------|----|---------|-----|----|-----|--|--|--|

| Master | S | M-code  | NACK | Sr | SAD + W |     | RA |     |  |  |  |

| Slave  |   |         |      |    |         | ACK |    | ACK |  |  |  |

| Speed  |    |         |     | HS-mo | ode |      |      |   | FS-mode |

|--------|----|---------|-----|-------|-----|------|------|---|---------|

| Master | Sr | SAD + R |     |       |     |      | NACK | Р |         |

| Slave  |    |         | ACK | DATA  | ACK | DATA |      |   |         |

(n-1) bytes + ack.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

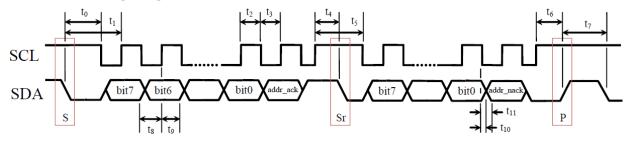

### I<sup>2</sup>C Timing Diagram

Table 8: I2C Timing (Fast Mode)

| Number                | Description                                                  | MIN | MAX | Units |

|-----------------------|--------------------------------------------------------------|-----|-----|-------|

| t <sub>o</sub>        | SDA low to SCL low transition (Start event)                  | 50  | -   | ns    |

| $t_1$                 | SDA low to first SCL rising edge                             | 100 | -   | ns    |

| $t_2$                 | SCL pulse width: high                                        | 100 | -   | ns    |

| $t_3$                 | SCL pulse width: low                                         | 100 | -   | ns    |

| $t_4$                 | SCL high before SDA falling edge (Start Repeated)            | 50  | -   | ns    |

| <b>t</b> <sub>5</sub> | SCL pulse width: high during a S/Sr/P event                  | 100 | -   | ns    |

| t <sub>6</sub>        | SCL high before SDA rising edge (Stop)                       | 50  | -   | ns    |

| t <sub>7</sub>        | SDA pulse width: high                                        | 25  | -   | ns    |

| t <sub>8</sub>        | SDA valid to SCL rising edge                                 | 50  | -   | ns    |

| t <sub>9</sub>        | SCL rising edge to SDA invalid                               | 50  | -   | ns    |

| t <sub>10</sub>       | SCL falling edge to SDA valid (when slave is transmitting)   | -   | 100 | ns    |

| t <sub>11</sub>       | SCL falling edge to SDA invalid (when slave is transmitting) | 0   | -   | ns    |

| Note                  | Recommended I <sup>2</sup> C CLK                             | 2.5 | -   | us    |

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **SPI Communications**

#### 4-Wire SPI Interface

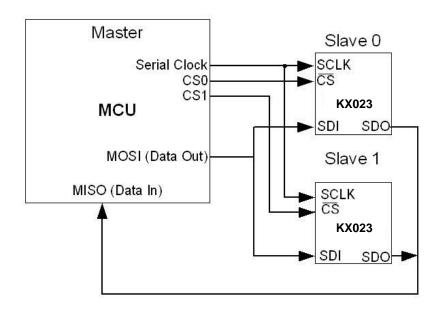

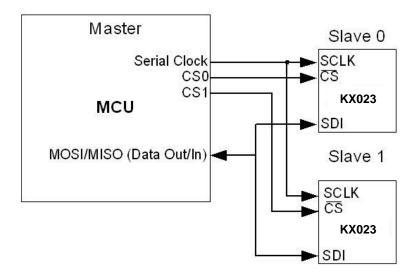

The KX023 also utilizes an integrated 4-Wire Serial Peripheral Interface (SPI) for digital communication. The SPI interface is primarily used for synchronous serial communication between one Master device and one or more Slave devices. The Master, typically a micro controller, provides the SPI clock signal (SCLK) and determines the state of Chip Select (nCS). The KX023 always operates as a Slave device during standard Master-Slave SPI operation.

4-wire SPI is a synchronous serial interface that uses two control and two data lines. With respect to the Master, the Serial Clock output (SCLK), the Data Output (SDI or MOSI) and the Data Input (SDO or MISO) are shared among the Slave devices. The Master generates an independent Chip Select (nCS) for each Slave device that goes low at the start of transmission and goes back high at the end. The Slave Data Output (SDO) line, remains in a high-impedance (hi-z) state when the device is not selected, so it does not interfere with any active devices. This allows multiple Slave devices to share a master SPI port as shown in Figure 2 below.

Figure 2: 4-wire SPI Connections

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

### 4-Wire SPI Timing Diagram

Table 9: 4-Wire SPI Timing

| Number                | Description                             | MIN | MAX | Units |

|-----------------------|-----------------------------------------|-----|-----|-------|

| $t_1$                 | CLK pulse width: high                   | 40  |     | ns    |

| $t_2$                 | CLK pulse width: low                    | 40  |     | ns    |

| $t_3$                 | nCS low to first CLK rising edge        | 20  |     | ns    |

| $t_4$                 | nCS low after the final CLK rising edge | 30  |     | ns    |

| <b>t</b> <sub>5</sub> | SDI valid to CLK rising edge            | 10  |     | ns    |

| t <sub>6</sub>        | CLK rising edge to SDI invalid          | 10  |     | ns    |

| t <sub>7</sub>        | CLK falling edge to SDO valid           |     | 35  | ns    |

#### Notes

- 1. t<sub>7</sub> is only present during reads.

- 2. Timings are for VDD of 1.8V to 3.6V with 1K $\Omega$  pull-up resistor and maximum 20pF load capacitor on SDO.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

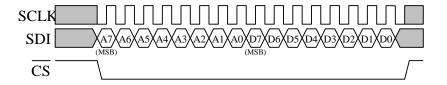

#### 4-Wire Read and Write Registers

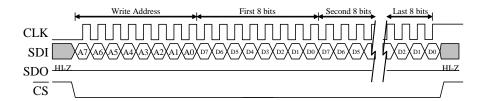

The registers embedded in the KX023 have 8-bit addresses. Upon power up, the Master must write to the accelerometer's control registers to set its operational mode. On the falling edge of nCS, a 2-byte command is written to the appropriate control register. The first byte initiates the write to the appropriate register, and is followed by the user-defined, data byte. The MSB (Most Significant Bit) of the register address byte will indicate "0" when writing to the register and "1" when reading from the register. This operation occurs over 16 clock cycles. All commands are sent MSB first. The host must return nCS high for at least one clock cycle before the next data request. However, when data is being read from a buffer read register (BUF\_READ), the nCS signal can remain low until the buffer is read. Figure 3 below shows the timing diagram for carrying out an 8-bit register write operation.

Figure 3: Timing Diagram for 8-Bit Register Write Operation

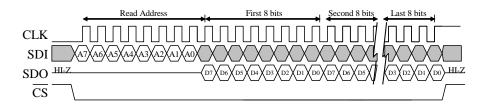

In order to read an 8-bit register, an 8-bit register address must be written to the accelerometer to initiate the read. The MSB of this register address byte will indicate "0" when writing to the register and "1" when reading from the register. Upon receiving the address, the accelerometer returns the 8-bit data stored in the addressed register. This operation also occurs over 16 clock cycles. All returned data is sent MSB first, and the host must return nCS high for at least one clock cycle before the next data request. Figure 4 shows the timing diagram for an 8-bit register read operation.

Figure 4: Timing Diagram for 8-Bit Register Read Operation

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### 3-Wire SPI Interface

The KX023 also utilizes an integrated 3-Wire Serial Peripheral Interface (SPI) for digital communication. 3-wire SPI is a synchronous serial interface that uses two control lines and one data line. With respect to the Master, the Serial Clock output (SCLK), the Data Output/Input (SDI) are shared among the Slave devices. The Master generates an independent Chip Select (nCS) for each Slave device that goes low at the start of transmission and goes back high at the end. This allows multiple Slave devices to share a master SPI port as shown in Figure 5 below.

Figure 5: 3-wire SPI Connections

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

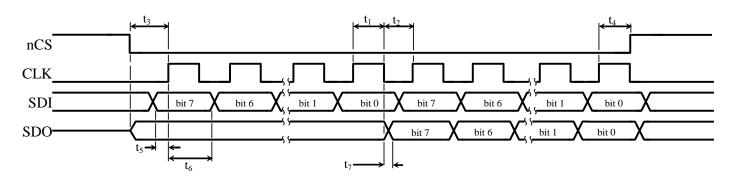

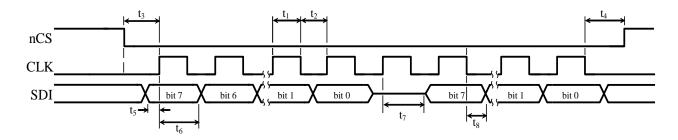

### 3-Wire SPI Timing Diagram

| Number                | Description                                     | MIN | MAX | Units |

|-----------------------|-------------------------------------------------|-----|-----|-------|

| $t_1$                 | CLK pulse width: high                           | 40  | -   | ns    |

| t <sub>2</sub>        | CLK pulse width: low                            | 40  | •   | ns    |

| t <sub>3</sub>        | nCS low to first CLK rising edge                | 20  | -   | ns    |

| <b>t</b> 4            | nCS low after the final CLK falling edge        | 20  | -   | ns    |

| <b>t</b> <sub>5</sub> | SDI valid to CLK rising edge                    | 10  | -   | ns    |

| t <sub>6</sub>        | CLK rising edge to SDI input invalid            | 10  | -   | ns    |

| t <sub>7</sub>        | CLK extra clock cycle rising edge to SDI output | -   | -   | ns    |

| t <sub>8</sub>        | CLK falling edge to SDI output becomes valid    | -   | 35  | ns    |

Table 10: 3-Wire SPI Timing

#### Notes

- 1.  $t_7$  and  $t_8$  are only present during reads.

- 2. Timings are for VDD of 1.8V to 3.6V with 1K $\Omega$  pull-up resistor and maximum 20pF load capacitor on SDI.

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

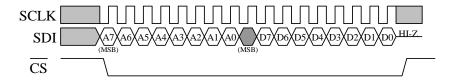

#### 3-Wire Read and Write Registers

The registers embedded in the KX023 have 8-bit addresses. Upon power up, the Master must write to the accelerometer's control registers to set its operational mode. On the falling edge of nCS, a 2-byte command is written to the appropriate control register. The first byte initiates the write to the appropriate register, and is followed by the user-defined, data byte. The MSB (Most Significant Bit) of the register address byte will indicate "0" when writing to the register and "1" when reading from the register. A read operation occurs over 17 clock cycles and a write operation occurs over 16 clock cycles. All commands are sent MSB first. The host must return nCS high for at least one clock cycle before the next data request. However, when data is being read from a buffer read register (BUF\_READ), the nCS signal can remain low until the buffer is read. Figure 6 below shows the timing diagram for carrying out an 8-bit register write operation.

Figure 6: Timing Diagram for 8-Bit Register Write Operation

In order to read an 8-bit register, an 8-bit register address must be written to the accelerometer to initiate the read. The MSB of this register address byte will indicate "0" when writing to the register and "1" when reading from the register. Upon receiving the address, the accelerometer returns the 8-bit data stored in the addressed register. For 3-wire read operations, one extra clock cycle between the address byte and the data output byte is required. Therefore, this operation occurs over 17 clock cycles. All returned data is sent MSB first, and the host must return nCS high for at least one clock cycle before the next data request. Figure 7 shows the timing diagram for an 8-bit register read operation.

Figure 7: Timing Diagram for 8-Bit Register Read Operation

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

### **Embedded Registers**

The KX023 has 57 embedded 8-bit registers that are accessible by the user. This section contains the addresses for all embedded registers and also describes bit functions of each register. Table 11 below provides a listing of the accessible 8-bit registers and their addresses.

| Address | Register Name   | R/W |

|---------|-----------------|-----|

| 00h     | XHPL            | R   |

| 01h     | XHPH            | R   |

| 02h     | YHPL            | R   |

| 03h     | YHPH            | R   |

| 04h     | ZHPL            | R   |

| 05h     | ZHPH            | R   |

| 06h     | XOUTL           | R   |

| 07h     | XOUTH           | R   |

| 08h     | YOUTL           | R   |

| 09h     | YOUTH           | R   |

| 0Ah     | ZOUTL           | R   |

| 0Bh     | ZOUTH           | R   |

| 0Ch     | COTR            | R   |

| 0Dh     | Kionix Reserved |     |

| 0Eh     | Kionix Reserved |     |

| 0Fh     | Who_AM_I        | R/W |

| 10h     | TSCP            | R   |

| 11h     | TSPP            | R   |

| 12h     | INS1            | R   |

| 13h     | INS2            | R   |

| 14h     | INS3            | R   |

| 15h     | STAT            | R   |

| 16h     | Kionix Reserved |     |

| 17h     | INT_REL         | R   |

| 18h     | CNTL1*          | R/W |

| 19h     | CNTL2*          | R/W |

| 1Ah     | CNTL3*          | R/W |

| 1Bh     | ODCNTL*         | R/W |

| 1Ch     | INC1*           | R/W |

| 1Dh     | INC2*           | R/W |

| 1Eh     | INC3*           | R/W |

| 1Fh     | INC4*           | R/W |

| 20h     | INC5*           | R/W |

| Address | Register Name   | R/W |

|---------|-----------------|-----|

| 21h     | INC6*           | R/W |

| 22h     | TILT_TIMER*     | R/W |

| 23h     | WUFC*           | R/W |

| 24h     | TDTRC*          | R/W |

| 25h     | TDTC*           | R/W |

| 26h     | TTH*            | R/W |

| 27h     | TTL*            | R/W |

| 28h     | FTD*            | R/W |

| 29h     | STD*            | R/W |

| 2Ah     | TLT*            | R/W |

| 2Bh     | TWS*            | R/W |

| 2Ch     | Kionix Reserved |     |

| 2Dh     | Kionix Reserved |     |

| 2Eh     | Kionix Reserved |     |

| 2Fh     | Kionix Reserved |     |

| 30h     | ATH*            | R/W |

| 31h     | Kionix Reserved |     |

| 32h     | TILT_ANGLE_LL*  | R/W |

| 33h     | TILT_ANGLE_HL*  | R/W |

| 34h     | HYST_SET*       | R/W |

| 35h     | LP_CNTL*        | R/W |

| 36h     | Kionix Reserved |     |

| 37h     | Kionix Reserved |     |

| 38h     | Kionix Reserved |     |

| 39h     | Kionix Reserved |     |

| 3Ah     | BUF_CNTL1*      | R/W |

| 3Bh     | BUF_CNTL2*      | R/W |

| 3Ch     | BUF_STATUS_1    | R   |

| 3Dh     | BUF_STATUS_2    | R   |

| 3Eh     | BUF_CLEAR       | W   |

| 3Fh     | BUF_READ        | R   |

| 60h     | SELF_TEST       | W   |

|         |                 |     |

<sup>\*</sup> Note: - When changing the contents of these registers, the PC1 bit in CNTL1 must first be set to "0".

- Reserved registers should not be written.

Table 11: Register Map

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### **Register Descriptions**

#### **Accelerometer Outputs**

These registers contain up to 16-bits of valid acceleration data for each axis. Depending on the setting of the RES bit in CNTL1, the user may choose to read only the 8 MSB thus reading an effective 8-bit resolution. When BRES = '0' in BUF\_CNTL2 the 8 MSB is the only data recorded in the buffer. The data is updated every user-defined ODR period, is protected from overwrite during each read, and can be converted from digital counts to acceleration (g) per Table 12 below. The register acceleration output binary data is represented in 2's complement format. For example, if N = 16 bits, then the Counts range is from -32768 to 32767, and if N = 8 bits, then the Counts range is from -128 to 127.

| 16-bit<br>Register Data<br>(2's complement) | Equivalent<br>Counts in<br>decimal | Range = ±2g | Range = ±4g | Range = ±8g |

|---------------------------------------------|------------------------------------|-------------|-------------|-------------|

| 0111 1111 1111 1111                         | 32767                              | +1.99994g   | +3.99988g   | +7.99976g   |

| 0111 1111 1111 1110                         | 32766                              | +1.99988g   | +3.99976g   | +7.99951g   |

|                                             |                                    |             |             |             |

| 0000 0000 0001                              | 1                                  | +0.00006g   | +0.00012g   | +0.00024g   |

| 0000 0000 0000                              | 0                                  | 0.000g      | 0.0000g     | 0.0000g     |

| 1111 1111 1111 1111                         | -1                                 | -0.00006g   | -0.00012g   | -0.00024g   |

|                                             |                                    |             |             |             |

| 1000 0000 0000 0001                         | -32767                             | -1.99994g   | -3.99988g   | -7.99976g   |

| 1000 0000 0000 0000                         | -32768                             | -2.0000g    | -4.0000g    | -8.0000g    |

| 8-bit<br>Register Data<br>(2's complement) | Equivalent<br>Counts in<br>decimal | Range = ±2g | Range = ±4g | Range = ±8g |

|--------------------------------------------|------------------------------------|-------------|-------------|-------------|

| 0111 1111                                  | 127                                | +1.9844g    | +3.9688g    | +7.9375g    |

| 0111 1110                                  | 126                                | +1.9688g    | +3.9375g    | +7.8750g    |

|                                            |                                    |             |             |             |

| 0000 0001                                  | 1                                  | +0.0156g    | +0.0313g    | +0.0625g    |

| 0000 0000                                  | 0                                  | 0.0000g     | 0.0000g     | 0.0000g     |

| 1111 1111                                  | -1                                 | -0.0156g    | -0.0313g    | -0.0625g    |

|                                            |                                    |             |             | •••         |

| 1000 0001                                  | -127                               | -1.9844g    | -3.9688g    | -7.9375g    |

| 1000 0000                                  | -128                               | -2.000g     | -4.000g     | -8.000g     |

Table 12: Acceleration (g) Calculation

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### XHP\_L

X-axis high pass filter accelerometer output least significant byte. Data is updated at the ODR frequency determined by OWUF in CNTL3.

| R     | R     | R     | R          | R          | R     | R     | R     |

|-------|-------|-------|------------|------------|-------|-------|-------|

| XHPD7 | XHPD6 | XHPD5 | XHPD4      | XHPD3      | XHPD2 | XHPD1 | XHPD0 |

| Bit7  | Bit6  | Bit5  | Bit4       | Bit3       | Bit2  | Bit1  | Bit0  |

| •     |       |       | <b> </b> 2 | C Address: | 0x00h |       |       |

#### XHP\_H

X-axis high pass filter accelerometer output most significant byte. Data is updated at the ODR frequency determined by OWUF in CNTL3.

| R      | R      | R      | R              | R          | R      | R     | R     |

|--------|--------|--------|----------------|------------|--------|-------|-------|

| XHPD15 | XHPD14 | XHPD13 | XHPD12         | XHPD11     | XHPD10 | XHPD9 | XHPD8 |

| Bit7   | Bit6   | Bit5   | Bit4           | Bit3       | Bit2   | Bit1  | Bit0  |

|        |        |        | J <sup>2</sup> | C Address: | 0x01h  |       |       |

#### YHP L

Y-axis high pass filter accelerometer output least significant byte. Data is updated at the ODR frequency determined by OWUF in CNTL3.

| R     | R     | R     | R     | R          | R     | R     | R     |

|-------|-------|-------|-------|------------|-------|-------|-------|

| YHPD7 | YHPD6 | YHPD5 | YHPD4 | YHPD3      | YHPD2 | YHPD1 | YHPD0 |

| Bit7  | Bit6  | Bit5  | Bit4  | Bit3       | Bit2  | Bit1  | Bit0  |

|       |       |       | 2     | C Address: | 0x02h |       |       |

#### YHP H

Y-axis high pass filter accelerometer output most significant byte. Data is updated at the ODR frequency determined by OWUF in CNTL3.

| _ | R      | R      | R      | R      | R          | R      | R     | R     |

|---|--------|--------|--------|--------|------------|--------|-------|-------|

|   | YHPD15 | YHPD14 | YHPD13 | YHPD12 | YHPD11     | YHPD10 | YHPD9 | YHPD8 |

|   | Bit7   | Bit6   | Bit5   | Bit4   | Bit3       | Bit2   | Bit1  | Bit0  |

|   |        |        |        | 2      | C Address: | 0x03h  |       |       |

PART NUMBER: KX023-1025 Rev. 12.0 5-Apr-16

#### ZHP\_L

Z-axis high pass filter accelerometer output least significant byte. Data is updated at the ODR frequency determined by OWUF in CNTL3.

| R     | R     | R     | R     | R          | R     | R     | R     |

|-------|-------|-------|-------|------------|-------|-------|-------|

| ZHPD7 | ZHPD6 | ZHPD5 | ZHPD4 | ZHPD3      | ZHPD2 | ZHPD1 | ZHPD0 |

| Bit7  | Bit6  | Bit5  | Bit4  | Bit3       | Bit2  | Bit1  | Bit0  |

|       |       |       | 2     | C Address: | 0x04h |       |       |

#### ZHP\_H