# 1/5-Inch 2 Mp CMOS Digital Image Sensor

# MT9D015 Datasheet, Rev. M

For the latest datasheet, please visit www.onsemi.com

## Features

- Superior low light performance

- High sensitivity

- Low dark current

- Simple two-wire serial interface

- Auto black level calibration

- Programmable controls: gain, frame size/rate, exposure, left–right and top–bottom image reversal, window size and panning

- Data interface: CCP2 compliant sub-low-voltage differential signaling (sub-LVDS) or single lane serial mobile industry processor interface (MIPI)

- SMIA 1.0 compatible; MIPI 1.0 compliant

- On-chip phase-locked loop (PLL) oscillator

- Bayer-pattern down-size scaler

- Integrated lens shading correction

- Internal power switch for ultra-low standby current consumption

- 30 fps at full resolution

- 2D defect pixel correction

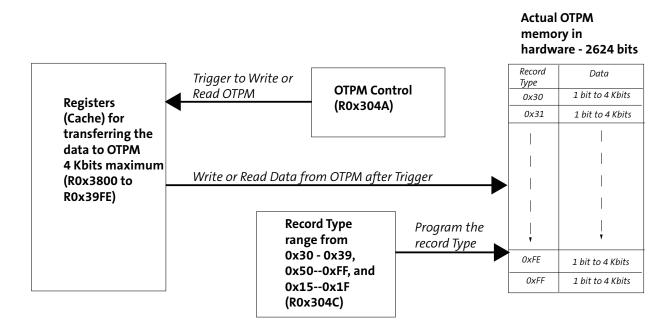

- 2624-bit one-time programmable memory (OTPM) for storing module information and lens shading correction.

# **General Description**

The ON Semiconductor MT9D015 is a 1/5-inch UXGA-format CMOS active-pixel digital image sensor with a pixel array of 1600H x 1200V (1608H x 1208V including border pixels). It incorporates sophisticated on-chip camera functions such as windowing, mirroring, column and subsampling modes. It is programmable through a simple two-wire serial interface and has very low power consumption.

# Applications

- Cellular phones

- Digital still cameras

- PC cameras

- PDAs

| Table 1: Key Performance Par |

|------------------------------|

|------------------------------|

| Paramet                                             | er                    | Value                                                                                                              |  |  |  |

|-----------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| Die size                                            |                       | 4356.15 μm (H) x 4354.85 μm (V)                                                                                    |  |  |  |

| Optical f                                           | ormat                 | 1/5-inch UXGA (4:3)                                                                                                |  |  |  |

| Active in                                           | nager size            | 2.828 mm (H) x 2.128 (V)                                                                                           |  |  |  |

| Active p                                            | ixels                 | 1608 H x 1208 V                                                                                                    |  |  |  |

| Pixel size                                          | 2                     | 1.75 x 1.75 μm                                                                                                     |  |  |  |

| Color filt                                          | er array              | RGB Bayer pattern                                                                                                  |  |  |  |

| Shutter                                             | type                  | Electronic rolling shutter (ERS)                                                                                   |  |  |  |

| Input clo                                           | ock frequency         | 6–27 MHz                                                                                                           |  |  |  |

| Maximu                                              | m data rate           | 640 Mb/s (CCP) and 768 Mb/s (MIPI)                                                                                 |  |  |  |

|                                                     | UXGA<br>(1600 x 1200) | Programmable up to 21 fps in profile<br>0 mode (RAW10)<br>Programmable up to 30 fps in profile<br>1/2 mode (RAW10) |  |  |  |

| CCP<br>frame<br>rate                                | XGA<br>(1024 x 768)   | Programmable up to 42 fps in profile<br>0 mode (RAW10)<br>Programmable up to 61 fps in profile<br>1/2 mode (RAW10) |  |  |  |

|                                                     | HD (1280 x 720)       | 30 fps                                                                                                             |  |  |  |

|                                                     | UXGA<br>(1600 x 1200) | 30 fps (RAW10)                                                                                                     |  |  |  |

| MIPI<br>frame                                       | VGA (640 x 480)       | 60 fps (RAW10)                                                                                                     |  |  |  |

| rate                                                | QVGA (320X240)        | 120 fps (RAW10)                                                                                                    |  |  |  |

|                                                     | HD (1280 x 720)       | 30 fps (RAW10)                                                                                                     |  |  |  |

| ADC reso                                            | olution               | 10-bit                                                                                                             |  |  |  |

| Responsivity<br>Dynamic range<br>SNR <sub>MAX</sub> |                       | 0.86 V/lux-sec                                                                                                     |  |  |  |

|                                                     |                       | 62 dB                                                                                                              |  |  |  |

|                                                     |                       | 38.7 dB                                                                                                            |  |  |  |

| Supply                                              | Analog                | 2.40–2.90 V (2.80 V nominal)                                                                                       |  |  |  |

| voltage                                             | Digital               | 1.70–1.90 V (1.80 V nominal)                                                                                       |  |  |  |

| Power consumption                                   |                       | 272 mW at 30 fps (TYP)                                                                                             |  |  |  |

| Operatir                                            | ng temperature        | –30°C to +70°C                                                                                                     |  |  |  |

| Packaging                                           |                       | Bare die                                                                                                           |  |  |  |

# **Ordering Information**

#### Table 2: Available Part Numbers

| Part Number              | Product Description | Orderable Product Attribute Description |

|--------------------------|---------------------|-----------------------------------------|

| MT9D015D00STCMC25BC1-200 | 2 MP 1/4" CIS       | Die Sales, 200µm Thickness              |

| MT9D015D00STCPC25BC1-400 | 2 MP 1/4" CIS       | Die Sales, 400µm Thickness              |

### **Table of Contents**

ON

|                                       | 1  |

|---------------------------------------|----|

| General Description                   | 1  |

| Applications                          | 1  |

| Ordering Information                  | 2  |

| General Description                   | 6  |

| Functional Overview                   | 6  |

| Operating Modes                       | 8  |

| Signal Descriptions                   | 10 |

| Two-Wire Serial Register Interface    | 11 |

| Registers                             | 15 |

| Embedded Data Format and Control      | 19 |

| Programming Restrictions              | 27 |

| Control of the Signal Interface       | 32 |

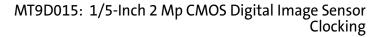

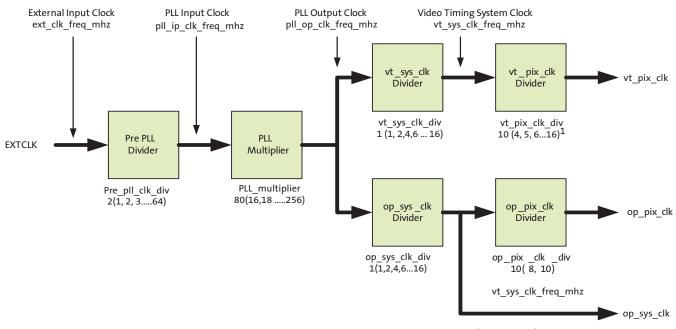

| Clocking.                             |    |

| Features                              | 41 |

| Sensor Core Digital Data Path         | 55 |

| Digital Data Path                     | 61 |

| Timing Specifications                 | 62 |

| Electrical Specifications             | 66 |

| Chief Ray Angle                       | 72 |

| SMIA and MIPI Specification Reference | 73 |

| Revision History.                     | 74 |

# List of Figures

| Figure 1:  | Block Diagram                                           | .6 |

|------------|---------------------------------------------------------|----|

| Figure 2:  | Pixel Color Pattern Detail (Top Right Corner)           | .7 |

| Figure 3:  | Typical Configuration (Connection) – Serial Output Mode | .8 |

| Figure 4:  | Typical Configuration (Connection) – MIPI Mode          | .9 |

| Figure 5:  | Single READ from Random Location                        | 13 |

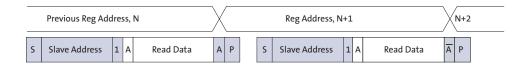

| Figure 6:  | Single READ from Current Location                       | 13 |

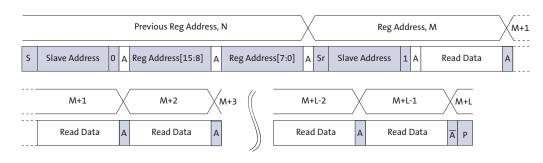

| Figure 7:  | Sequential READ, Start from Random Location             | 13 |

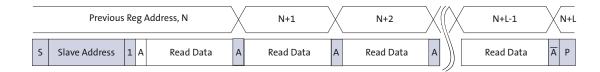

| Figure 8:  | Sequential READ, Start from Current Location            | 14 |

| Figure 9:  | Single WRITE to Random Location                         | 14 |

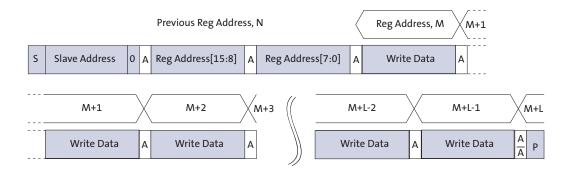

| Figure 10: | Sequential Write, Start at Random Location              | 14 |

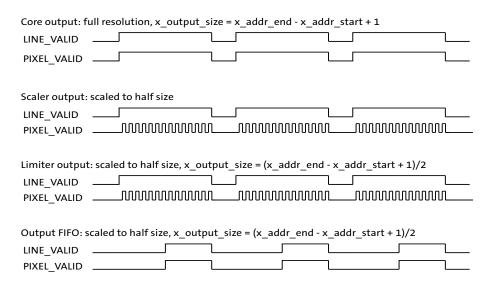

| Figure 11: | Effect of Limiter on the SMIA Data Path                 | 29 |

| Figure 12: | Timing of SMIA Data Path                                |    |

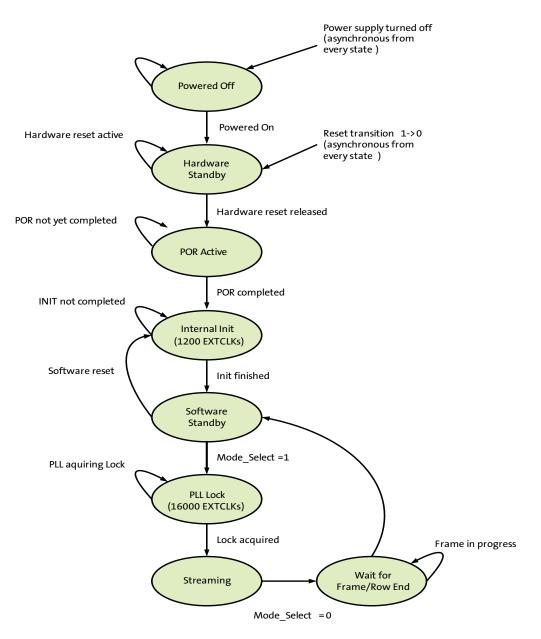

| Figure 13: | MT9D015 System States                                   |    |

| Figure 14: | MT9D015 SMIA Profile 1/2 Clocking Structure             |    |

| Figure 15: | MT9D015 SMIA Profile 0 Clocking Structure               |    |

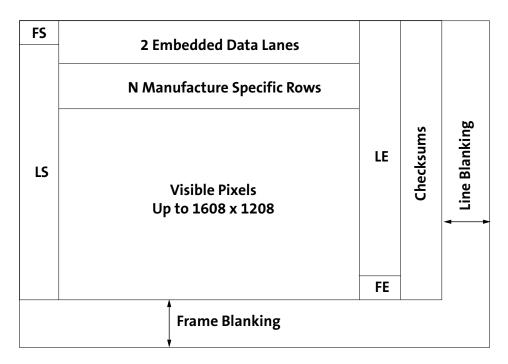

| Figure 17: | Full Resolution Frame Structure Example                 |    |

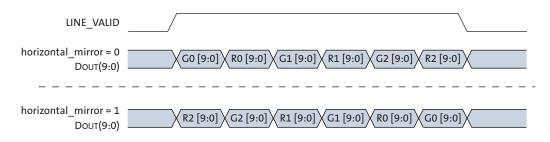

| Figure 18: | Effect of horizontal_mirror on Readout Order            |    |

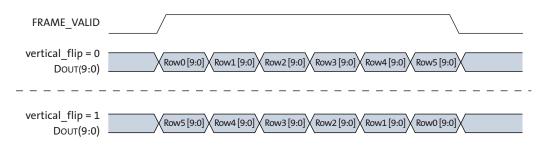

| Figure 19: | Effect of vertical_flip on Readout Order4               | 14 |

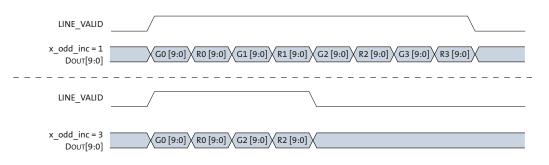

| Figure 20: | Effect of x_odd_inc = 3 on Readout Sequence             |    |

| Figure 21: | Pixel Readout (No Subsampling)                          |    |

| Figure 22: | Pixel Readout (x_odd_inc = 3, y_odd_inc = 3)4           |    |

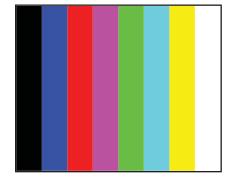

| Figure 23: | 100 Percent Color Bars Test Pattern                     |    |

| Figure 24: | Fade-to-Gray Color Bars Test Pattern                    |    |

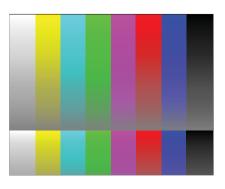

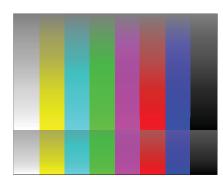

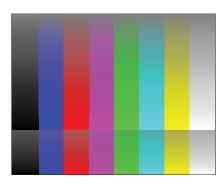

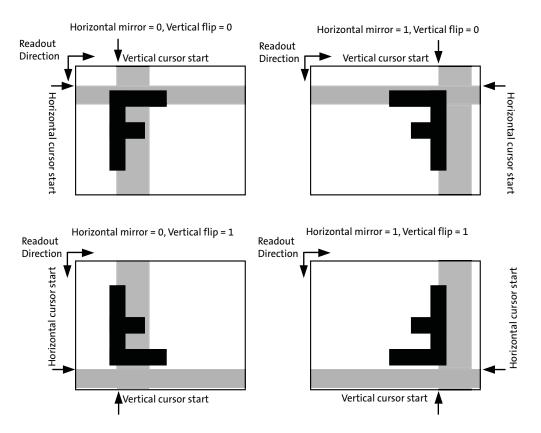

| Figure 25: | Test Cursor Behavior when image_orientation             | 30 |

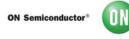

| Figure 26: | Data Path                                               |    |

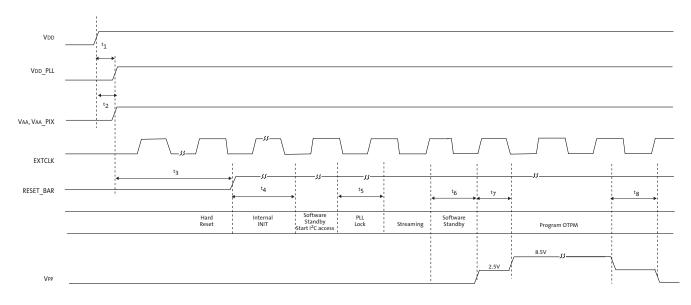

| Figure 27: | Power-Up Sequence                                       |    |

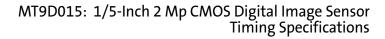

| Figure 28: | Power-Down Sequence                                     |    |

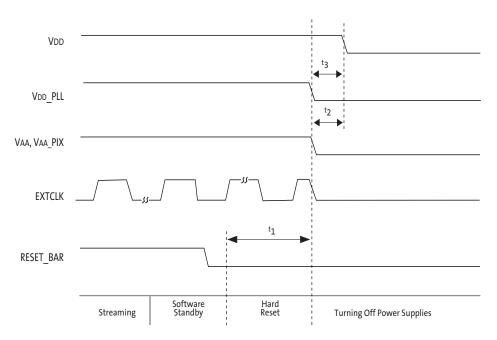

| Figure 29: | Soft Standby and Soft Reset                             |    |

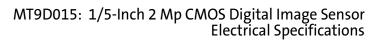

| Figure 30: | Definition of Timing for Two-Wire Serial Interface      | 37 |

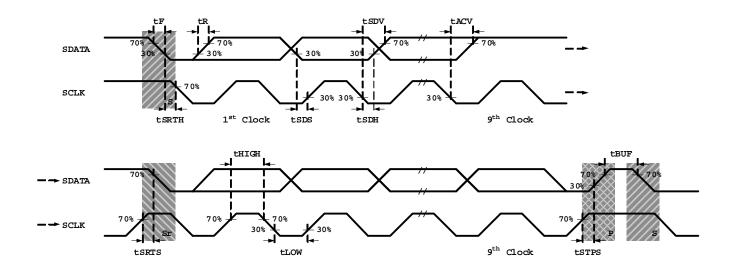

| Figure 31: | Internal Power-On Reset                                 |    |

| Figure 32: | Chief Ray Angle                                         | 72 |

#### **List of Tables**

| Table 1:  | Key Performance Parameters1                                   |

|-----------|---------------------------------------------------------------|

| Table 2:  | Available Part Numbers                                        |

| Table 3:  | Signal Descriptions                                           |

| Table 4:  | Address Space Regions                                         |

| Table 5:  | Data Formats                                                  |

| Table 6:  | Embedded Data                                                 |

| Table 7:  | Definitions for Programming Rules                             |

| Table 8:  | Programming Rules                                             |

| Table 9:  | PLL in System States                                          |

| Table 10: | Signal State During Reset                                     |

| Table 11: | Streaming/STANDBY                                             |

| Table 12: | Row Address Sequencing                                        |

| Table 13: | Minimum Row Time and Blanking Numbers                         |

| Table 14: | Minimum Frame Time and Blanking Numbers                       |

| Table 15: | fine_integration_time Limits                                  |

| Table 16: | Gain Table                                                    |

| Table 17: | Test Patterns                                                 |

| Table 18: | Power-Up Sequence                                             |

| Table 19: | Power-Down Sequence                                           |

| Table 20: | Electrical Characteristics (EXTCLK)                           |

| Table 21: | Two-Wire Serial Interface Electrical Characteristics          |

| Table 22: | Two-Wire Serial Interface Timing Specification                |

| Table 23: | Electrical Characteristics (Serial CCP2 Pixel Data Interface) |

| Table 24: | Electrical Characteristics (Serial MIPI Pixel Data Interface) |

| Table 25: | Electrical Characteristics                                    |

| Table 26: | Power-On Reset Characteristics                                |

| Table 27: | DC Electrical Definitions and Characteristics                 |

| Table 28: | Absolute Maximum Values                                       |

### **General Description**

The MT9D015 digital image sensor features ON Semiconductor's breakthrough low noise CMOS imaging technology that achieves near-CCD image quality (based on signal-to-noise ratio and low-light sensitivity) while maintaining the inherent size, cost, and integration advantages of CMOS.

When operated in its default mode, the sensor generates a UXGA image at 21 frames per second (fps) when ext\_clk\_freq\_mhz = 16 MHz. An on-chip analog-to-digital converter (ADC) generates a 10-bit value for each pixel.

### **Functional Overview**

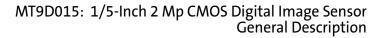

The MT9D015 is a progressive-scan sensor that generates a stream of pixel data at a constant frame rate. It uses an on-chip, phase-locked loop (PLL) to generate all internal clocks from a single master input clock running between 6 and 27 MHz. The maximum pixel rate is 64 Mp/s, corresponding to a video timing pixel clock rate of 91.4 MHz. A block diagram of the sensor is shown in Figure 1.

#### Figure 1: Block Diagram

The core of the sensor is a 2Mp active-pixel array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been read, the data from the columns is sequenced through an analog signal chain (providing offset correction and gain), and then through an ADC. The output from the ADC is a 10-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further data corrections and applies digital gain).

The pixel array contains optically active and light-shielded (dark) pixels. The dark pixels are used to provide data for on-chip offset-correction algorithms (black level control).

The sensor contains a set of control and status registers that can be used to control many aspects of the sensor behavior including the frame size, exposure, and gain setting. These registers can be accessed through a two-wire serial interface.

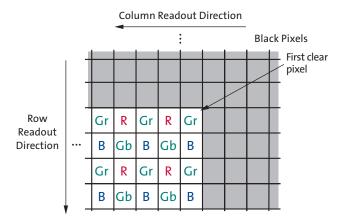

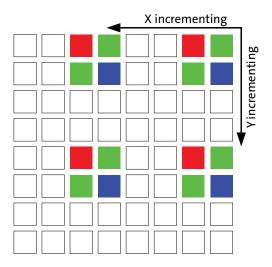

The output from the sensor is a Bayer pattern; alternate rows are a sequence of either green and red pixels or blue and green pixels. The offset and gain stages of the analog signal chain provide per-color control of the pixel data.

The control registers, timing and control, and digital processing functions shown in Figure 1 on page 6 are partitioned into three logical parts:

- A sensor core that provides array control and data path corrections.

- A digital shading correction block to compensate for color/brightness shading introduced by the lens or CRA curve mismatch.

- Functionality to support the SMIA standard. This includes a horizontal and vertical image scaler, a limiter, a data compressor, an output FIFO, and a serializer.

The output FIFO prevents data bursts by keeping the data rate continuous.

#### **Pixel Array**

The sensor core uses a Bayer color pattern, as shown in Figure 2. The even-numbered rows contain green and red pixels; odd-numbered rows contain blue and green pixels. Even-numbered columns contain green and blue pixels; odd-numbered columns contain red and green pixels.

#### Figure 2: Pixel Color Pattern Detail (Top Right Corner)

# **Operating Modes**

The MT9D015 can operate in either serial CCP2 or serial MIPI mode (preconfigured at the factory). In both cases, the sensor has a SMIA-compatible register interface while the  $I^2C$  device address is compliant with SMIA or MIPI requirements as appropriate. The reset level on the TEST pin must be tied in a way that is compatible with the configured serial interface of the sensor, for instance TEST = 0 for CCP2 and TEST = 1 for MIPI.

Typical configurations are shown in Figure 3 and Figure 4 on page 9. These operating modes are described in "Control of the Signal Interface" on page 32.

For low-noise operation, the MT9D015 requires separate power supplies for analog and digital. Incoming digital and analog ground conductors can be tied together next to the die. Both power supply rails should be decoupled from ground using capacitors as close as possible to the die. The use of inductance filters is not recommended on the power supplies or output signals.

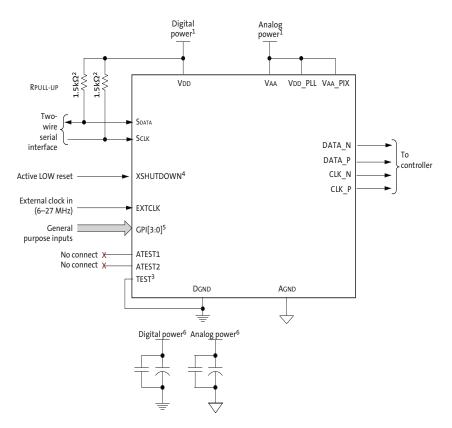

#### Figure 3: Typical Configuration (Connection) – Serial Output Mode

Notes: 1. All power supplies must be adequately decoupled.

- 2. A resistor value of  $1.5k\Omega$  is recommended, but it may be greater for slower two-wire speed.

- 3. TEST must be tied to GND for SMIA configuration.

- 4. Also referred to as RESET BAR.

- 5. The GPI pins can be statically pulled HIGH or LOW and used as module IDs. All GPI pins must be driven to avoid leakage current.

- 6. ON Semiconductor recommends that 0.1μF and 1μF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations.

- 7. VPP, which can be used during the module manufacturing process, is not shown in Figure 3. This pad is left unconnected during normal operation.

- 8. ATEST1 and ATEST2 must be floating.

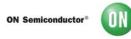

#### Figure 4: Typical Configuration (Connection) – MIPI Mode

Notes: 1. All power supplies must be adequately decoupled.

- 2. A resistor value of  $1.5k\Omega$  is recommended, but it may be greater for slower two-wire speed.

- 3. TEST must be tied to VDD for MIPI configuration.

- 4. Also referred to as RESET BAR.

- 5. The GPI pins can be statically pulled HIGH or LOW and used as module IDs. All GPI pins must be driven to avoid leakage current.

- 6. ON Semiconductor recommends that 0.1µF and 1µF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations.

- 7. VPP, which can be used during the module manufacturing process, is not shown in Figure 3. This pad is left unconnected during normal operation.

- 8. ATEST1 and ATEST2 must be floating.

# **Signal Descriptions**

Table 3 provides signal descriptions for MT9D015 die. For pad location and aperture information, refer to the MT9D015 die data sheet.

#### Table 3:Signal Descriptions

UN

| Pad Name                 | Pad Type | Description                                                                                                                                                                                                                         |

|--------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTCLK                   | Input    | Master clock input. PLL input clock. 6–27 MHz.                                                                                                                                                                                      |

| RESET_BAR<br>(XSHUTDOWN) | Input    | Asynchronous active LOW reset. When asserted, data output stops and all internal registers are restored to their factory default settings.                                                                                          |

| Sclk                     | Input    | Serial clock for access to control and status registers.                                                                                                                                                                            |

| GPI[3:0]                 | Input    | General purpose inputs.<br>After reset, these pads are powered up (enabled—see R0x301A) by default; these pads<br>must be bonded to a HIGH or LOW state.<br>Failure to bond as required will result in excessive power consumption. |

| TEST                     | Input    | Enable manufacturing test modes. Connect to DGND for normal operation of the CCP2-configured sensor, or connect to VDD power for the MIPI configured sensor.                                                                        |

| Sdata                    | I/O      | Serial data for reads from and writes to control and status registers.                                                                                                                                                              |

| DATA_P                   | Output   | Differential CCP2/MIPI (sub-LVDS) serial data (positive).                                                                                                                                                                           |

| DATA_N                   | Output   | Differential CCP2/MIPI (sub-LVDS) serial data (negative).                                                                                                                                                                           |

| CLK_P                    | Output   | Differential CCP2/MIPI (sub-LVDS) serial clock/strobe (positive).                                                                                                                                                                   |

| CLK_N                    | Output   | Differential CCP2/MIPI (sub-LVDS) serial clock/strobe (negative).                                                                                                                                                                   |

| VAA                      | Supply   | Analog power supply.                                                                                                                                                                                                                |

| VDD_PLL                  | Supply   | PLL power supply.                                                                                                                                                                                                                   |

| VAA_PIX                  | Supply   | Analog power supply.                                                                                                                                                                                                                |

| Agnd                     | Supply   | Analog ground.                                                                                                                                                                                                                      |

| Vdd                      | Supply   | Digital power supply.                                                                                                                                                                                                               |

| Dgnd                     | Supply   | Digital ground.                                                                                                                                                                                                                     |

| VPP                      | Supply   | OTPM programming power supply                                                                                                                                                                                                       |

# **Two-Wire Serial Register Interface**

ON

|                         | The two-wire serial interface bus enables read/write access to control and status regis-<br>ters within the sensor. This interface is designed to be compatible with the SMIA 1.0 Part<br>2: CCP2 Specification camera control interface (CCI), which uses the electrical charac-<br>teristics and transfer protocols of the I <sup>2</sup> C specification.                                                                                                                                                              |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | The protocols described in the I <sup>2</sup> C specification allow the slave device to drive SCLK LOW; the sensor uses SCLK as an input only and therefore never drives it LOW.                                                                                                                                                                                                                                                                                                                                          |

| Protocol                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | <ul> <li>Data transfers on the two-wire serial interface bus are performed by a sequence of low-level protocol elements:</li> <li>1. a (repeated) start condition</li> <li>2. a slave address/data direction byte</li> <li>3. an (a no) acknowledge bit</li> <li>4. a message byte</li> <li>5. a stop condition</li> </ul>                                                                                                                                                                                                |

|                         | The bus is idle when both SCLK and SDATA are HIGH. Control of the bus is initiated with a start condition, and the bus is released with a stop condition. Only the master can generate the start and stop conditions.                                                                                                                                                                                                                                                                                                     |

| Start Condition         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | A start condition is defined as a HIGH-to-LOW transition on SDATA while SCLK is HIGH.<br>At the end of a transfer, the master can generate a start condition without previously<br>generating a stop condition; this is known as a "repeated start" or "restart" condition.                                                                                                                                                                                                                                               |

| Slave Address/Data Dire | ction Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | Bits [7:1] of this byte represent the device slave address and bit [0] indicates the data transfer direction. A "0" in bit [0] indicates a write, and a "1" indicates a read. The default slave addresses used by the MT9D015 for the MIPI configured sensor are 0x6C (write address) and 0x6D (read address) in accordance with the MIPI specification. But for the CCP2 configured sensor, the default slave addresses used are 0x20 (write address) and 0x21 (read address) in accordance with the SMIA specification. |

| Acknowledge Bit         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | Each 8-bit data transfer is followed by an acknowledge bit or a no-acknowledge bit in the SCLK clock period following the data transfer. The transmitter (which is the master when writing, or the slave when reading) releases SDATA. The receiver indicates an acknowledge bit by driving SDATA LOW. As for data transfers, SDATA can change when SCLK is LOW and must be stable while SCLK is HIGH.                                                                                                                    |

| No-Acknowledge Bit      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | The no-acknowledge bit is generated when the receiver does not drive SDATA LOW during the SCLK clock period following a data transfer. A no-acknowledge bit is used to terminate a read sequence.                                                                                                                                                                                                                                                                                                                         |

| Message Byte            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | Message bytes are used for sending register addresses and register write data to the slave device and for retrieving register read data. The protocol used is outside the scope of the SMIA CCI.                                                                                                                                                                                                                                                                                                                          |

| Stop Condition   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | A stop condition is defined as a LOW-to-HIGH transition on SDATA while SCLK is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Data Transfer    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | Data is transferred serially, 8 bits at a time, with the MSB transmitted first. Each byte of data is followed by an acknowledge bit or a no-acknowledge bit. This data transfer mechanism is used for the slave address/data direction byte and for message bytes.                                                                                                                                                                                                                                                                                                                      |

|                  | One data bit is transferred during each SCLK clock period. SDATA can change when SCLK is LOW and must be stable while SCLK is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Typical Sequence |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | A typical READ or WRITE sequence begins by the master generating a start condition on<br>the bus. After the start condition, the master sends the 8-bit slave address/data direction<br>byte. The last bit indicates whether the request is for a READ or a WRITE, where a "0"<br>indicates a WRITE and a "1" indicates a READ. If the address matches the address of the<br>slave device, the slave device acknowledges receipt of the address by generating an<br>acknowledge bit on the bus.                                                                                         |

|                  | If the request was a READ, the master sends the 8-bit write slave address/data direction<br>byte and 16-bit register address, just as in the write request. The master then generates a<br>(re)start condition and the 8-bit READ slave address/data direction byte, and clocks out<br>the register data, 8 bits at a time. The master generates an acknowledge bit after each<br>8-bit transfer. The slave's internal register address is automatically incremented after<br>every 8 bits are transferred. The data transfer is stopped when the master sends a<br>no-acknowledge bit. |

#### Single READ from Random Location

This sequence (Figure 5) starts with a dummy WRITE to the 16-bit address that is to be used for the READ. The master terminates the WRITE by generating a restart condition. The master then sends the 8-bit READ slave address/data direction byte and clocks out 1 byte of register data. The master terminates the READ by generating a no-acknowledge bit followed by a stop condition. Figure 5 shows how the internal register address maintained by the MT9D015 is loaded and incremented as the sequence proceeds.

#### Figure 5: Single READ from Random Location

| _            |                                                                                                                                     |     | Previous Reg Addre                 | ss, | N                | X    | Reg A         | ddress, I | N         | M+1 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------|-----|------------------|------|---------------|-----------|-----------|-----|

| s            | Slave Address                                                                                                                       | 0 A | Reg Address[15:8]                  | А   | Reg Address[7:0] | A Sr | Slave Address | 1 A       | Read Data | A P |

| P<br>Si<br>A | <ul> <li>start condition</li> <li>stop condition</li> <li>restart condition</li> <li>acknowledge</li> <li>no-acknowledge</li> </ul> | [   | slave to master<br>master to slave |     |                  |      |               |           |           |     |

#### **Single READ from Current Location**

This sequence (Figure 6) performs a read using the current value of the MT9D015 internal register address. The master terminates the READ by generating a no-acknowl-edge bit followed by a stop condition. The figure shows two independent read sequences.

#### Figure 6: Single READ from Current Location

#### Sequential READ, Start from Random Location

This sequence (Figure 7) starts in the same way as the single READ from random location (Figure 5). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit and continues to perform byte reads until L bytes have been read.

#### Figure 7: Sequential READ, Start from Random Location

#### Sequential READ, Start from Current Location

This sequence (Figure 8) starts in the same way as the single READ from current location (Figure 6 on page 13). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit and continues to perform byte reads until L bytes have been read.

#### Figure 8: Sequential READ, Start from Current Location

#### Single WRITE to Random Location

This sequence (Figure 9) begins with the master generating a start condition. The slave address/data direction byte signals a WRITE and is followed by the HIGH then LOW bytes of the register address that is to be written. The master follows this with the byte of write data. The WRITE is terminated by the master generating a stop condition.

#### Figure 9: Single WRITE to Random Location

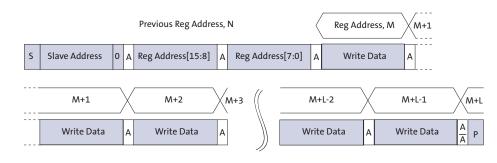

#### Sequential WRITE, Start at Random Location

This sequence (Figure 10) starts in the same way as the single WRITE to random location (Figure 9). Instead of generating a stop condition after the first byte of data has been transferred, the master continues to perform byte writes until *L* bytes have been written. The WRITE is terminated by the master generating a stop condition.

#### Figure 10: Sequential Write, Start at Random Location

# Registers

**Note:** The detailed register lists and descriptions are in a separate document, the MT9D015 Register Reference.

The MT9D015 provides a 32-bit register address space accessed through a serial interface ("Single READ from Random Location" on page 13). Each register location is 8 or 16 bits in size.

The address space is divided into the five major regions shown in Table 4.

#### Table 4:Address Space Regions

| Address Range | Description                                  |

|---------------|----------------------------------------------|

| 0x0000-0x0FFF | Configuration registers                      |

|               | (read-only and read-write dynamic registers) |

| 0x1000-0x1FFF | Parameter limit registers                    |

|               | (read-only static registers)                 |

| 0x2000–0x2FFF | Image statistics registers                   |

|               | (none currently defined)                     |

| 0x3000–0x3FFF | Manufacturer-specific registers              |

|               | (read-only and read-write dynamic registers) |

| 0x4000–0xFFFF | Reserved (undefined)                         |

#### **Register Notation**

|                  | The underlying mechanism for reading and writing registers provides byte write capa-<br>bility. However, it is convenient to consider some registers as multiple adjacent bytes.<br>The MT9D015 uses 8-bit, 16-bit, and 32-bit registers, all implemented as 1 or more bytes<br>at naturally aligned, contiguous locations in the address space.                                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | In this document, registers are described either by address or by name. When registers are described by address, the size of the registers is explicit. For example, R0x3024 is an 8-bit register at address 0x3024, and R0x3000–1 is a 16-bit register at address 0x3000–0x3001. When registers are described by name, refer to the register table to determine their size.                                                                                                                                                                              |

| Register Aliases |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  | A consequence of the internal architecture of the MT9D015 is that some registers are decoded at multiple addresses. Some registers in "configuration space" are also decoded in "manufacturer-specific space." To provide unique names for all registers, the name of the register within manufacturer-specific register space has a trailing underscore. For example, R0x0000–1 is model_id, and R0x3000–1 is model_id_ (see the register table for more examples). The effect of reading or writing a register through any of its aliases is identical. |

| Bit Fields       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  | Some registers provide control of several different pieces of related functionality, making it necessary to refer to bit fields within registers. As an example of the notation used for this, the least significant 4 bits of the model_id register are referred to as model_id[3:0] or R0x0000–1[3:0].                                                                                                                                                                                                                                                  |

| Bit Field Aliases  |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | register fields a only one opera                                      | the register aliases described in "Register Aliases" on page 15, some<br>are aliased in multiple places. For example, R0x0100 (mode_select) has<br>ational bit, R0x0100[0]. This bit is aliased to R0x301A–B[2]. The effect of<br>ing a bit field through any of its aliases is identical.                                                                                                                                                                             |

| Byte Ordering      |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    | address in the l<br>example, the m<br>shown as 0x150<br>READ from add | beccupy more than 1 byte of address space are shown with the lowest<br>highest-order byte lane to match the byte-ordering on the SMIA bus. For<br>nodel_id register is R0x0000–1. In the register table the default value is<br>01. This means that a READ from address 0x0000 would return 0x15, and a<br>dress 0x0001 would return 0x01. When reading this register as two 8-bit<br>e serial interface, the 0x15 will appear on the serial interface first, followed |

| Address Alignment  |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    | are aligned to e                                                      | resses are aligned naturally. Registers that occupy 2 bytes of address space<br>even 16-bit addresses, and registers that occupy 4 bytes of address space<br>16-bit addresses that are an integer multiple of 4.                                                                                                                                                                                                                                                       |

| Bit Representation |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    |                                                                       | bit hex numbers are shown with an underscore between the upper and for example: 0x3000_01AB.                                                                                                                                                                                                                                                                                                                                                                           |

| Data Format        |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    | formats, the for                                                      | represent an unsigned binary value or set of bit fields. For all other register<br>rmat is stated explicitly at the start of the register description. The nota-<br>ormats is shown in Table 5.                                                                                                                                                                                                                                                                        |

|                    | Table 5: Da                                                           | ata Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | Name                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Signed fixed-point, 16-bit number: two's complement number,

8 fractional bits. Examples: 0x0100 = 1.0, 0x8000 = -128, 0xFFFF = -0.0039065

Unsigned fixed-point, 16-bit number: 8.8 format. Examples: 0x0100 = 1.0, 0x280 =

Signed floating-point, 32-bit number: IEEE 754 format. Example: 0x4280\_0000 =

FIX16

UFIX16

FLP32

2.5

64.0

#### **Register Behavior**

Registers vary from "read-only," "read/write," and "read, write-1-to-clear."

#### **Double-Buffered Registers**

Some sensor settings cannot be changed during frame readout. For example, changing R0x0344–5 (x\_addr\_start) partway through frame readout would result in inconsistent row lengths within a frame. To avoid this, the MT9D015 double-buffers many registers by implementing a "pending" and a "live" version. READs and WRITEs access the pending register. The live register controls the sensor operation.

The value in the pending register is transferred to a live register at a fixed point in the frame timing, called frame start. Frame start is defined as the point at which the first dark row is read out internally to the sensor. In the register tables the "Sync'd" column shows which registers or register fields are double-buffered in this way.

#### Using grouped\_parameter\_hold

Register grouped\_parameter\_hold (R0x0104) can be used to inhibit transfers from the pending to the live registers. When the MT9D015 is in streaming mode, write "1" to this register before making changes to any group of registers where a set of changes is required to take effect simultaneously. When this register is set to "0," all transfers from pending to live registers take place on the next frame start.

An example of the consequences of failing to set this bit follows:

An external auto exposure algorithm might want to change both gain and integration time between two frames. If the next frame starts between these operations, it will have the new gain, but not the new integration time, which would return a frame with the wrong brightness that might lead to a feedback loop with the AE algorithm resulting in flickering.

#### **Bad Frames**

A bad frame is a frame where all rows do not have the same integration time or where offsets to the pixel values have changed during the frame.

Many changes to the sensor register settings can cause a bad frame. For example, when line\_length\_pck (R0x0342–3) is changed, the new register value does not affect sensor behavior until the next frame start. However, the frame that would be read out at that frame start will have been integrated using the old row width, so reading it out using the new row width would result in a frame with an incorrect integration time.

In the register tables, the "Bad Frame" column shows where changing a register or register field will cause a bad frame. The following notation is used:

N—No. Changing the register value will not produce a bad frame.

Y—Yes. Changing the register value might produce a bad frame.

YM—Yes; but the bad frame will be masked out when mask\_corrupted\_frames (R0x0105) is set to "1."

#### **Changes to Integration Time**

If the integration time is changed while FRAME\_VALID (FV) is asserted for frame n, the first frame output using the new integration time is frame (n + 2). The sequence is as follows:

- 1. During frame *n*, the new integration time is held in the pending register.

- 2. At the start of frame (n + 1), the new integration time is transferred to the live register. Integration for each row of frame (n + 1) has been completed using the old integration time.

- 3. The earliest time that a row can start integrating using the new integration time is immediately after that row has been read for frame (n + 1). The actual time that rows start integrating using the new integration time is dependent upon the new value of the integration time.

- 4. When frame (n + 2) is read out, it will have been integrated using the new integration time.

If the integration time is changed on successive frames, each value written will be applied for a single frame; the latency between writing a value and it affecting the frame readout remains at two frames.

#### **Changes to Gain Settings**

Usually, when the gain settings are changed, the gain is updated on the next frame start. When the integration time and the gain are changed at the same time, the gain update is held off by one frame so that the first frame output with the new integration time also has the new gain applied. In this case, a new gain should not be set during the extra frame delay. There is an option to turn off the extra frame delay by setting reset\_reg-ister[14] bit.

#### **Embedded Data**

The current values of implemented registers in the address range 0x0000–0x0FFF can be generated as part of the pixel data. This embedded data is enabled by default when the serial pixel data interface is enabled.

The current value of a register is the value that was used for the image data in that frame. In general, this is the live value of the register. The exceptions are:

- The integration time is delayed by one further frame, so that the value corresponds to the integration time used for the image data in the frame. See "Changes to Integration Time" on page 18.

- The PLL timing registers are not double-buffered, because the result of changing them in streaming mode is undefined. Therefore, the pending and live values for these registers are equivalent.

# **Embedded Data Format and Control**

When the serial pixel data path is selected, the first two rows of the output image contain register values that are appropriate for the image. In this mode, the first two lines and the last line of data are not equally spaced. The format of this data is shown in Table 6. In the table, 8-bit (RAW8) and 10-bit (RAW10) versions of the data are shown. The 10-bit format places the data byte in bits [9:2] and sets bits [1:0] to a constant value of 01. Register values that are shown as "??" are dynamic and may change from frame to frame.

When the parallel pixel data path is selected and R0x306E-F[2:0]= 2 (parallel pixel data output MUX selects FIFO data). The output image contains two rows of embedded data.

|        |        |       | Row 0                                      |                                              |        | ROW 1 |                                                |                                              |  |

|--------|--------|-------|--------------------------------------------|----------------------------------------------|--------|-------|------------------------------------------------|----------------------------------------------|--|

| Offset | 10-Bit | 8-Bit | Two-wire<br>Serial<br>Interface<br>Address | Comment                                      | 10-Bit | 8-Bit | Two-<br>wire<br>Serial<br>Interface<br>Address | Comment                                      |  |

| 0      | 0X029  | 0X0A  |                                            | 2-byte tagged data format<br>(embedded data) | 0X029  | 0X0A  |                                                | 2-byte tagged data format<br>(embedded data) |  |

| 1      | 0X2A9  | 0XAA  |                                            | cci register index msb                       | 0X2A9  | 0XAA  |                                                | CCI register index MSB                       |  |

| 2      | 0X001  | 0X00  |                                            | address 00xx                                 | 0X009  | 0X02  |                                                | Address 02xx                                 |  |

| 3      | 0X295  | 0XA5  |                                            | cci register index lsb                       | 0X295  | 0XA5  |                                                | CCI register index LSB                       |  |

| 4      | 0X001  | 0X00  |                                            | address xx00                                 | 0X001  | 0X00  |                                                | Address xx00                                 |  |

| 5      | 0X169  | 0X5A  |                                            | auto increment                               | 0X169  | 0X5A  |                                                | auto increment                               |  |

| 6      | 0X055  | 0X15  | 0                                          | model_id hi                                  | ??     | ??    | 200                                            | fine_integration_time hi                     |  |

| 7      | 0X169  | 0X5A  |                                            |                                              | 0X169  | 0X5A  |                                                |                                              |  |

| 8      | 0X005  | 0X01  | 1                                          | model_id lo                                  | ??     | ??    | 201                                            | fine_integration_time lo                     |  |

| 9      | 0X169  | 0X5A  |                                            |                                              | 0X169  | 0X5A  |                                                |                                              |  |

| 10     | 0X080  | 0X20  | 2                                          | revision_number                              | ??     | ??    | 202                                            | coarse_integration_time hi                   |  |

| 11     | 0X169  | 0X5A  |                                            |                                              | 0X169  | 0X5A  |                                                |                                              |  |

| 12     | 0X019  | 0X06  | 3                                          | manufacturer_id                              | ??     | ??    | 203                                            | coarse_integration_time lo                   |  |

| 13     | 0X169  | 0X5A  |                                            |                                              | 0X169  | 0X5A  |                                                |                                              |  |

| 14     | 0X029  | 0X0A  | 4                                          | smia_version                                 | ??     | ??    | 204                                            | analogue_gain_code_glob<br>al hi             |  |

| 15     | 0X169  | 0X5A  |                                            |                                              | 0X169  | 0X5A  |                                                |                                              |  |

| 16     | ??     | ??    | 5                                          | frame_count                                  | ??     | ??    | 205                                            | analogue_gain_code_glob<br>al lo             |  |

| 17     | 0X169  | 0X5A  |                                            |                                              | 0X169  | 0X5A  |                                                |                                              |  |

| 18     | ??     | ??    | 6                                          | pixel_order                                  | ??     | ??    | 206                                            | analogue_gain_code_gree<br>nR hi             |  |

| 19     | 0X169  | 0X5A  |                                            |                                              | 0X169  | 0X5A  |                                                |                                              |  |

| 20     | ??     | ??    | 7                                          | reserved                                     | ??     | ??    | 207                                            | analogue_gain_code_gree<br>nR lo             |  |

| 21     | 0X169  | 0X5A  |                                            |                                              | 0X169  | 0X5A  |                                                |                                              |  |

| 22     | 0X001  | 0X00  | 8                                          | data_pedestal_hi                             | ??     | ??    | 208                                            | analogue_gain_code_red<br>hi                 |  |

| 23     | 0X169  | 0X5A  |                                            |                                              | 0X169  | 0X5A  |                                                |                                              |  |

|        |        |       | Row 0                                      |                         |        | ROW 1 |                                                |                                  |  |

|--------|--------|-------|--------------------------------------------|-------------------------|--------|-------|------------------------------------------------|----------------------------------|--|

| Offset | 10-Bit | 8-Bit | Two-wire<br>Serial<br>Interface<br>Address | Comment                 | 10-Bit | 8-Bit | Two-<br>wire<br>Serial<br>Interface<br>Address | Comment                          |  |

| 24     | 0X0A9  | 0X2A  | 9                                          | data_pedestal lo        | ??     | ??    | 209                                            | analogue_gain_code_red<br>lo     |  |

| 25     | 0X2A9  | 0XAA  |                                            | cci register index msb  | 0X169  | 0X5A  |                                                |                                  |  |

| 26     | 0X001  | 0X00  |                                            | address 00xx            | ??     | ??    | 020a                                           | analogue_gain_code_blue<br>hi    |  |

| 27     | 0X295  | 0XA5  |                                            | cci register index lsb  | 0X169  | 0X5A  |                                                |                                  |  |

| 28     | 0X041  | 0X10  |                                            | address xx10            | ??     | ??    | 020b                                           | analogue_gain_code_blue<br>lo    |  |

| 29     | 0X169  | 0X5A  |                                            | auto increment          | 0X169  | 0X5A  |                                                |                                  |  |

| 30     | 0X005  | 0X01  | 10                                         | revision_number_minor   | ??     | ??    | 020c                                           | analogue_gain_code_gree<br>nB hi |  |

| 31     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 32     | 0X001  | 0X00  | 11                                         | smia_pp_version         | ??     | ??    | 020d                                           | analogue_gain_codegreen<br>B lo  |  |

| 33     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 34     | 0X001  | 0X00  | 12                                         | module_date_year        | ??     | ??    | 020e                                           | digital_gain_greenR hi           |  |

| 35     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 36     | 0X001  | 0X00  | 13                                         | module_date_month       | ??     | ??    | 020f                                           | digital_gain_greenR lo           |  |

| 37     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 38     | 0X001  | 0X00  | 14                                         | module_date_day         | ??     | ??    | 210                                            | digital_gain_red hi              |  |

| 39     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 40     | 0X001  | 0X00  | 15                                         | module_date_phase       | ??     | ??    | 211                                            | digital_gain_red lo              |  |

| 41     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 42     | 0X001  | 0X00  | 16                                         | sensor_model_id hi      | ??     | ??    | 212                                            | digital_gain_blue hi             |  |

| 43     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 44     | 0X001  | 0X00  | 17                                         | sensor_model_id lo      | ??     | ??    | 213                                            | digital_gain_blue lo             |  |

| 45     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 46     | 0X005  | 0X01  | 18                                         | sensor_revision_number  | ??     | ??    | 214                                            | digital_gain_greenB hi           |  |

| 47     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 48     | 0X001  | 0X00  | 19                                         | sensor_manufacturer_id  | ??     | ??    | 215                                            | digital_gain_greenB lo           |  |

| 49     | 0X169  | 0X5A  |                                            |                         | 0X2A9  | 0XAA  |                                                | CCI register index MSB           |  |

| 50     | 0X001  | 0X00  | 1A                                         | sensor_firmwave_version | 0X00D  | 0X03  |                                                | Address 03xx                     |  |

| 51     | 0X169  | 0X5A  |                                            |                         | 0X295  | 0XA5  |                                                | CCI register index LSB           |  |

| 52     | ??     | ??    | 1B                                         | reserved                | 0X001  | 0X00  |                                                | Address xx00                     |  |

| 53     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                | auto increment                   |  |

| 54     | 0X001  | 0X00  | 1C                                         | serial_number_0 hi      | ??     | ??    | 300                                            | vt_pix_clk_div hi                |  |

| 55     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 56     | 0X001  | 0X00  | 1D                                         | serial_number_0 lo      | ??     | ??    | 301                                            | vt_pix_clk_div lo                |  |

| 57     | 0X169  | 0X5A  |                                            |                         | 0X169  | 0X5A  |                                                |                                  |  |

| 58     | 0X001  | 0X00  | 1E                                         | serial_number_1 hi      | ??     | ??    | 302                                            | vt_sys_clk_div hi                |  |

|        |        |       | Row 0                                      |                                 | ROW 1  |       |                                                |                        |

|--------|--------|-------|--------------------------------------------|---------------------------------|--------|-------|------------------------------------------------|------------------------|

| Offset | 10-Bit | 8-Bit | Two-wire<br>Serial<br>Interface<br>Address | Comment                         | 10-Bit | 8-Bit | Two-<br>wire<br>Serial<br>Interface<br>Address | Comment                |

| 59     | 0X169  | 0X5A  |                                            |                                 | 0X169  | 0X5A  |                                                |                        |

| 60     | 0X001  | 0X00  | 1F                                         | serial_number_1 lo              | ??     | ??    | 303                                            | vt_sys_clk_div lo      |

| 61     | 0X2A9  | 0XAA  |                                            | cci register index msb          | 0X169  | 0X5A  |                                                |                        |

| 62     | 0X001  | 0X00  |                                            | address 00xx                    | ??     | ??    | 304                                            | pre_pll_clk_div hi     |

| 63     | 0X295  | 0XA5  |                                            | cci register index lsb          | 0X169  | 0X5A  |                                                |                        |

| 64     | 0X101  | 0X40  |                                            | address xx40                    | ??     | ??    | 305                                            | pre_pll_clk_div lo     |

| 65     | 0X169  | 0X5A  |                                            | auto increment                  | 0X169  | 0X5A  |                                                |                        |

| 66     | 0X005  | 0X01  | 40                                         | frame_format_model_type         | ??     | ??    | 306                                            | pll_multiplier_hi      |

| 67     | 0X169  | 0X5A  |                                            |                                 | 0X169  | 0X5A  |                                                |                        |

| 68     | 0X049  | 0X12  | 41                                         | frame_format_model_subtyp<br>e  | ??     | ??    | 307                                            | pll_multiplier_lo      |