# Analog LCD Display Engine for XGA and SXGA Resolutions with Embedded LVDS and RSDS Transmitters

#### **Feature Overview**

- Programmable Context Sensitive<sup>™</sup> Filtering

- High-quality Up-scaling and Down-scaling

- Integrated 10-bit Triple Channel ADC/PLL

- IQSync<sup>™</sup> AutoSetup

- Integrated Programmable Timing Controller

- Integrated LVDS Transmitters

- Integrated Pattern Generator

- Perfect Picture<sup>™</sup> Technology

- sRGB 3D Color Warp

- High performance OSD supporting 1- to 4-bpp, proportional fonts

- Advanced EMI reduction features

- Serial I<sup>2</sup>C interface

- Low power 0.15 µm process technology

- Low cost 100-pin LQFP and 128-pin LQFP packages

- Lead-free versions available in 2005.

#### **General Description**

ADE3800 devices are a family of highly-integrated display engine ICs, enabling the most advanced, flexible, and cost-effective system-on-chip solutions for analogonly input LCD display applications.

The ADE3800 covers the full range of XGA and SXGA analog-only monitor applications using LVDS or RSDS interface.

The ADE3800 family is software compatible.

#### LCD Scaler Product Selector

| Product    | Package  | Output Format Support   |     |     |  |  |

|------------|----------|-------------------------|-----|-----|--|--|

| Floduct    | Fackage  | Resolution RSDS/TCON LV |     |     |  |  |

| ADE3800XL  | 100 LQFP | Up to XGA 75 Hz         |     | Yes |  |  |

| ADE3800XT  | 100 LQFP | Up to XGA 75 Hz         | Yes |     |  |  |

| ADE3800SXL | 100 LQFP | Up to SXGA 75 Hz        |     | Yes |  |  |

| ADE3800SXT | 128 LQFP | Up to SXGA 75 Hz        | Yes |     |  |  |

April 2005 1/138

#### Context Sensitive™ Scaler

- Sharper text with Edge Enhancement

- Programmable coefficients for unique customization

- From 5:1 upscale to 2:1 downscale

- Independent X Y axis zoom and shrink

### **Analog RGB input**

- 140 MHz 10-bit ADC

- Ultra low jitter digital Line Lock PLL

- Composite Sync and Sync on Green built-in support

### IQsync™ AutoSetup

- AutoSetup configures phase, clock, level, and position

- Automatically detects activity on input

- Compatible with all standard VESA and GTF modes

### Perfect Picture™ Technology

- Video & Picture highlight zone

- Supports up to 4 different windows

- Independent window controls for contrast, brightness and color

### Perfect Color™ Technology

- Programmable 3D Color Warp

- Digital brightness, contrast, hue, and saturation gamma controls

- Simple white point control

- Compatible with sRGB standard

- True color dithering for 18 and 24-bit panels

- Temporal and spatial dithering

- 30-bit programmable gamma table

### **OSD Engine**

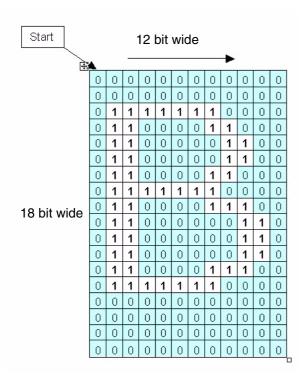

- 12 KB RAM based 12x18 characters

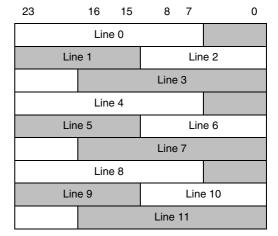

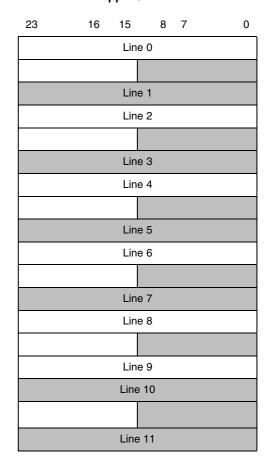

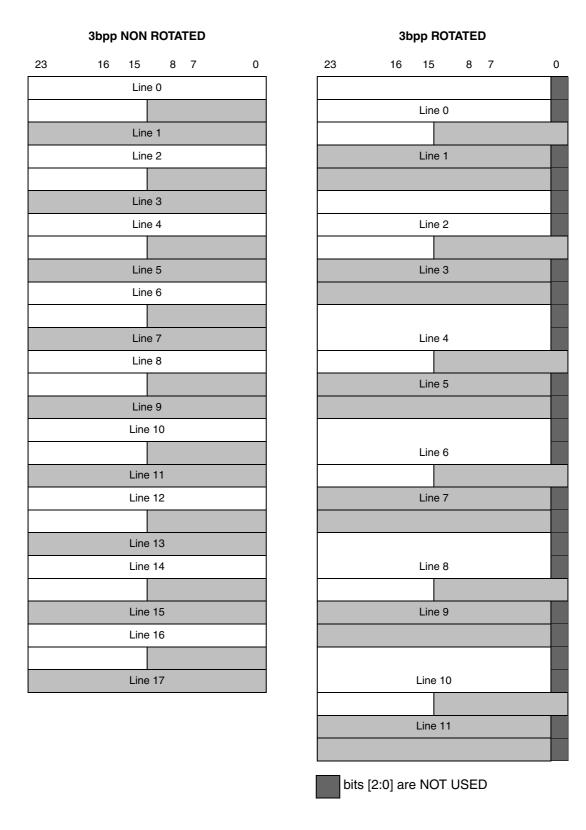

- 1, 2, 3, 4-bit per pixel color characters

- Multiple Windows

- Bordering, shadowing, transparency, fade-in and fade-out effects

- Supports font rotation

- Up to full screen size, multiple windows

- 64-entry TrueColor LUT with alpha-blending

# Programmable Timing Controller (TCON)

- Highly programmable support for XGA and SXGA smart panels

- RSDS split line support for SXGA smart panels

- Supports 18, 24, 36, and 48-bit RSDS outputs

- Advanced Flicker Detection and Reduction

- 8 programmable timing signals for row/column control

- Wide range of drivers & TCON compatibility

### **Integrated LVDS Transmitters**

- Dual 4 channel 6/8 bit LVDS transmitters

- Programmable channel swapping

- Programmable channel polarity

- Programmable group channel swapping for flexibility in board layout

- Programmable output swing control

#### **Advanced EMI Reduction Features**

- Flexible data transition minimization, single and dual

- Differential clock and signals

- Spread spectrum programmable digital FM modulation of the output clock with no external components

### **Output Format**

- Supports resolutions up to SXGA @ 75Hz

- Supports resolution above SXGA (1280x1024) with convenient input and output pixel clocks

- Supports 6 or 8-bit Panels

- Supports single or double pixel wide formats

# **Table of Contents**

| Chapter 1 | Important Information               | 6  |

|-----------|-------------------------------------|----|

| Chapter 2 | General Description                 | 7  |

| Chapter 3 | Pin Descriptions                    | 11 |

| Chapter 4 | Register Description by Block       | 18 |

| 4.1       | Global Control (GLBL)               | 18 |

| 4.2       | Frequency Synthesizer (FSYN)        | 20 |

| 4.2.1     | Dotclock vs Outclock                | 20 |

| 4.3       | Analog-to-Digital Converter (ADC)   | 21 |

| 4.3.1     | 216MHz Frequency Synthesizer        | 22 |

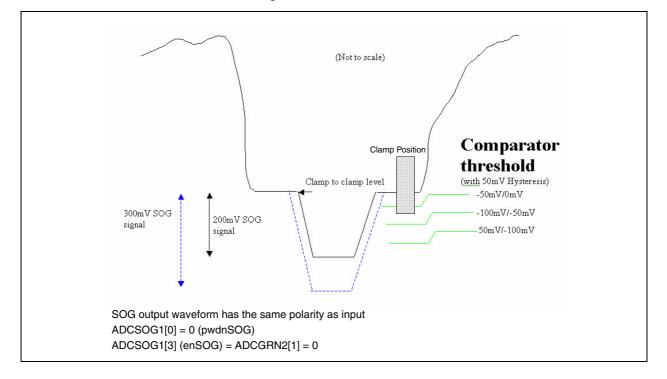

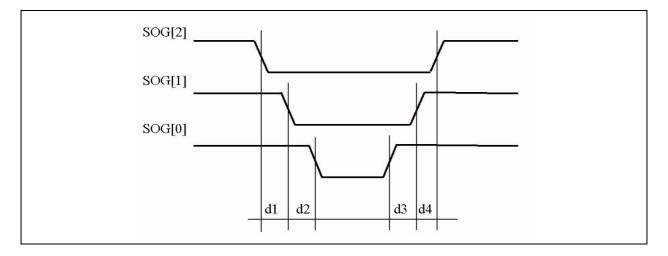

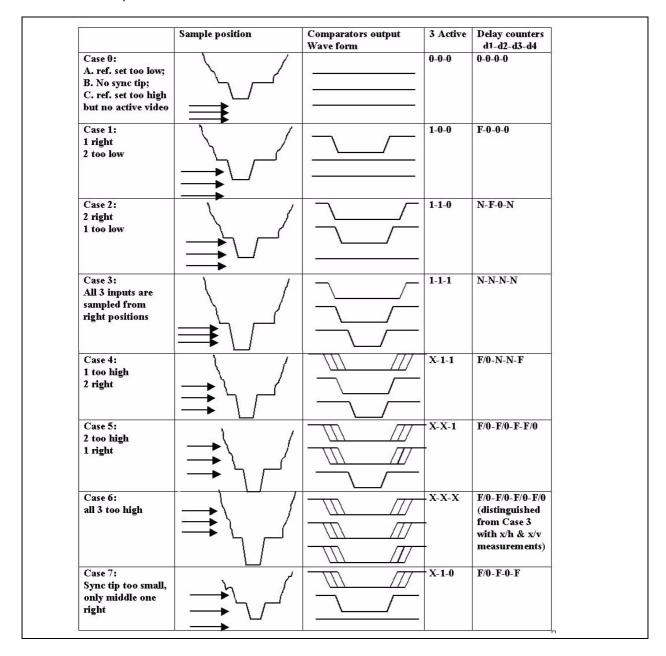

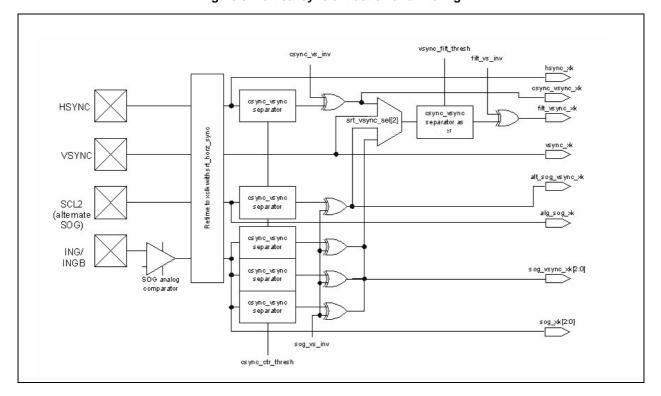

| 4.3.2     | Sync-on-Green (SOG)                 | 22 |

| 4.4       | Analog Dithering (ADTH)             | 29 |

| 4.4.1     | Function                            | 29 |

| 4.4.2     | Addressing Technique                | 29 |

| 4.4.3     | Output Amplitude Control            | 29 |

| 4.4.4     | Miscellaneous                       | 29 |

| 4.5       | Line Lock PLL (LLK)                 | 30 |

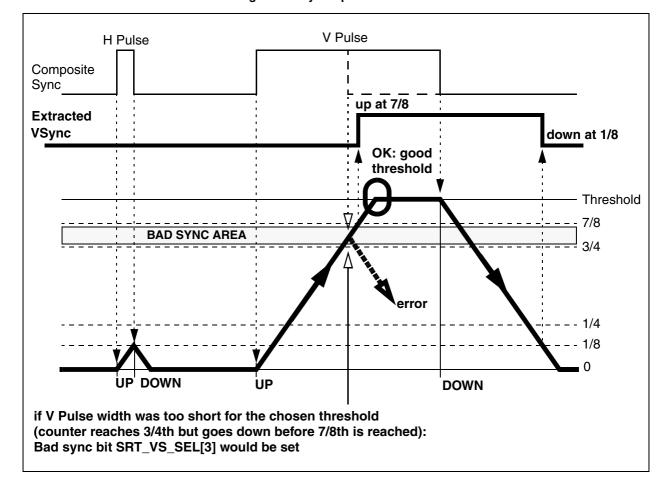

| 4.6       | Sync Retiming (SRT)                 | 33 |

| 4.6.1     | Coast Signal                        | 33 |

| 4.7       | Input Sync Measurement (SMEAS)      | 36 |

| 4.7.1     | Input Sync - Activity Detection     | 36 |

| 4.7.2     | Input Sync - Measurement            | 37 |

| 4.7.3     | Fast Mute                           | 37 |

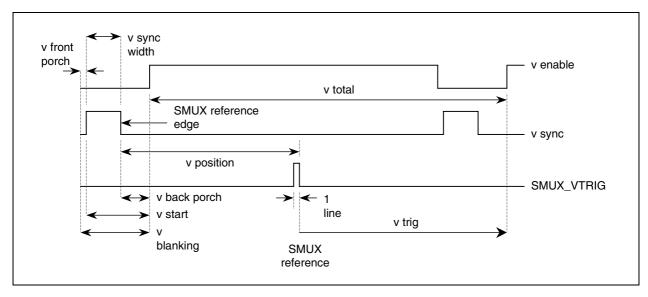

| 4.8       | Sync Multiplexer (SMUX)             | 43 |

| 4.9       | Data Measurement (DMEAS)            | 47 |

| 4.9.1     | Function Summary                    | 47 |

| 4.9.2     | Window Control                      | 47 |

| 4.9.3     | Algorithm Control                   | 47 |

| 4.9.4     | Mode Control                        | 48 |

| 4.9.5     | Edge Intensity                      | 48 |

| 4.9.6     | Pixel Sum                           | 48 |

| 4.9.7     | Min / Max                           |    |

| 4.9.8     | Pixel Cumulative Distribution (PCD) | 49 |

| H Position Min / Max                                                | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V Position Min / Max                                                | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DE Size                                                             | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

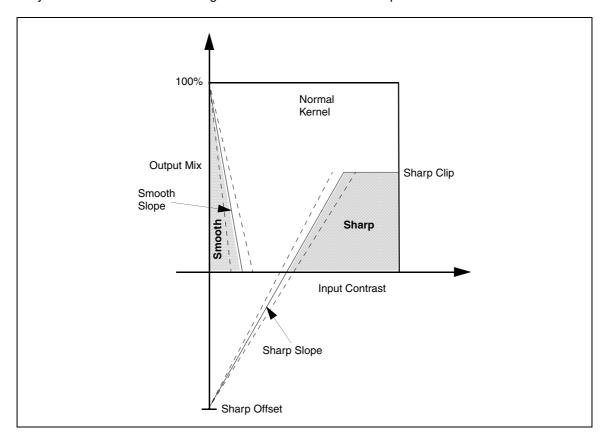

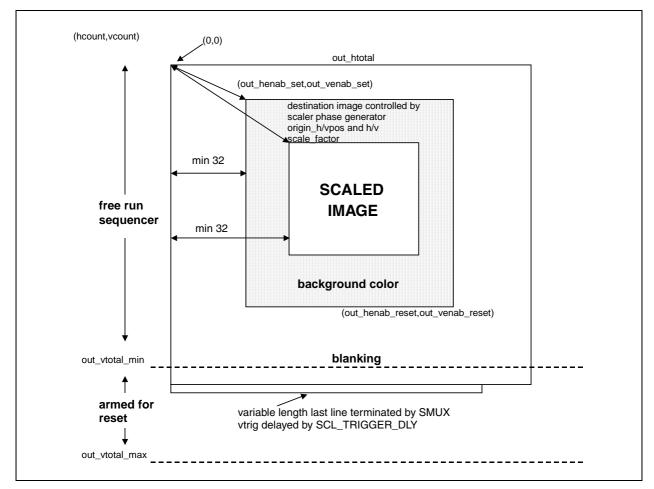

| Scale (SCL)                                                         | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Frame Synchronization                                               | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Context Description                                                 | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Scale Kernel Example                                                | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

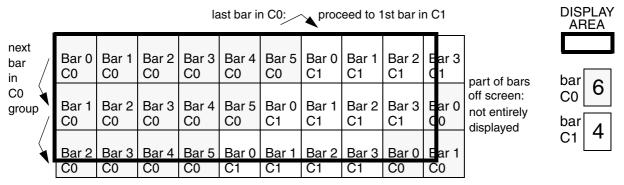

| Pattern Generator (PGEN)                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Overview                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

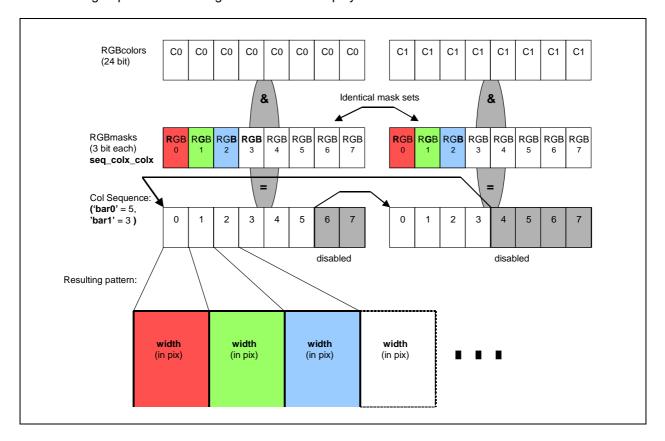

| Color Mask Sequencer                                                | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

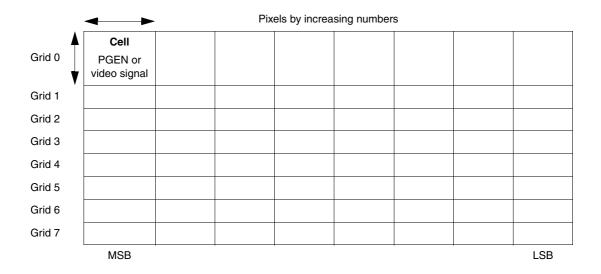

| 8 x 8 Grid Layout with Optional Resets                              | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Borders                                                             | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TCON Window Control                                                 | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| sRGB (SRGB)                                                         | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Parametric Gamma, Digital Contrast / Brightness on Multiple Windows | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

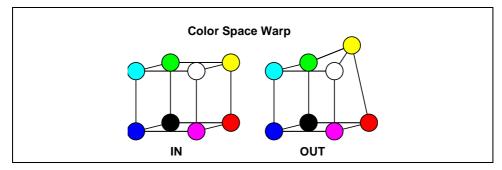

| Color Space Warp                                                    | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Gamma (GAM)                                                         | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| On-Screen Display (OSD)                                             | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Implementation                                                      | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Color LUT Calculation                                               | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Alpha Blending                                                      | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RAM Memory                                                          | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

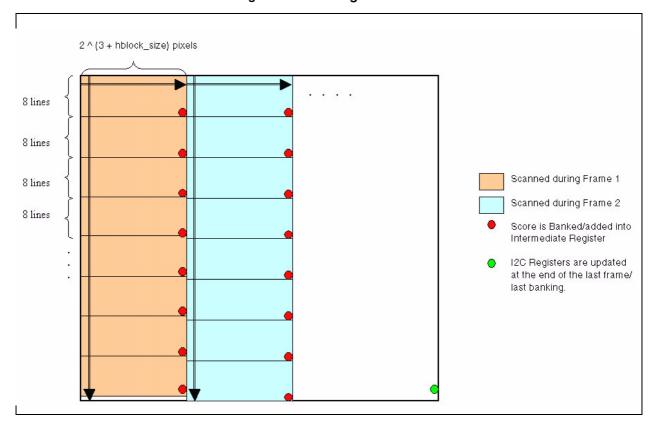

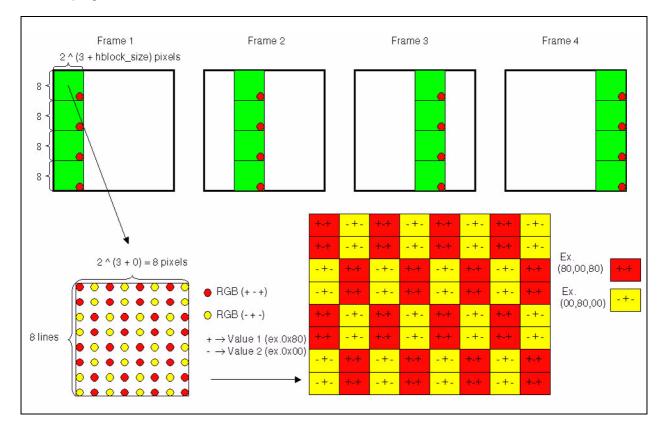

| Flicker (FLK)                                                       | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Function                                                            | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Adaptive Phase Control (APC)                                        | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Function                                                            | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Addressing Technique                                                | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Dither threshold Control                                            | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

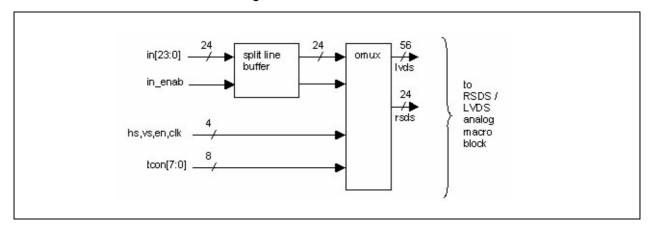

| Output Mux (OMUX)                                                   | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Output Data                                                         | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Output Clocks                                                       | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Clock Sources and Timing Considerations                             | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Timing Controller (TCON)                                            | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LVDS/RSDS Features                                                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Output Channels                                                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pulse Width Modulation (PWM)1                                       | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I <sup>2</sup> C Block Transfer (I2CBKT)                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                     | H Position Min / Max V Position Min / Max DE Size Scale (SCL) Frame Synchronization Context Description Scale Kernel Example Pattern Generator (PGEN) Overview Color Mask Sequencer 8 x 8 Grid Layout with Optional Resets Borders TCON Window Control RRGB (SRGB) Parametric Gamma, Digital Contrast / Brightness on Multiple Windows Color Space Warp Gamma (GAM) On-Screen Display (OSD) Implementation Color LUT Calculation Alpha Blending RAM Memory Flicker (FLK) Function Adaptive Phase Control (APC) Function Addressing Technique Dither threshold Control Output Mux (OMUX) Output Data Output Clocks 1 Clock Sources and Timing Considerations 1 Timing Controller (TCON) 1 LVDS/RSDS Features 1 Pulse Width Modulation (PWM) 1 PC Block Transfer (I2CBKT) 1 Transfer Setup and Start 1 Transfer Setup and Start 1 Transfer Setup and Start |

### **ADE3800**

| 4.21.2     | Transfer Progress                            |     |

|------------|----------------------------------------------|-----|

| 4.21.3     | Concurrent I2C Transfers                     |     |

| 4.22       | I <sup>2</sup> C Registers and RAM Addresses | 122 |

| 4.22.1     | I2C Transfer Format                          |     |

| 4.22.2     | Dedicated RAM Areas per Block                |     |

| 4.22.3     | Multi-byte Registers                         | 122 |

| Chapter 5  | Electrical Specifications                    | 124 |

| 5.1        | Absolute Maximum Ratings                     | 124 |

| 5.2        | Nominal Operating Conditions                 | 124 |

| 5.3        | Preliminary Thermal Data                     | 126 |

| 5.4        | Preliminary DC Specifications                | 126 |

| 5.4.1      | LVTTL 5-Volt Tolerant Inputs with Hysteresis | 126 |

| 5.4.2      | LVTTL 3-Volt Tolerant Inputs with Hysteresis | 126 |

| 5.4.3      | LVTTL 5-Volt Tolerant I/O with Hysteresis    | 126 |

| 5.4.4      | LVTTL 3-Volt Tolerant I/O                    |     |

| 5.4.5      | LVTTL 3-Volt Tolerant I/O                    | 127 |

| 5.5        | LVDS Outputs                                 | 127 |

| 5.6        | RSDS Outputs                                 | 127 |

| 5.7        | ADC Characteristics                          | 128 |

| Chapter 6  | Package Mechanical Data                      | 129 |

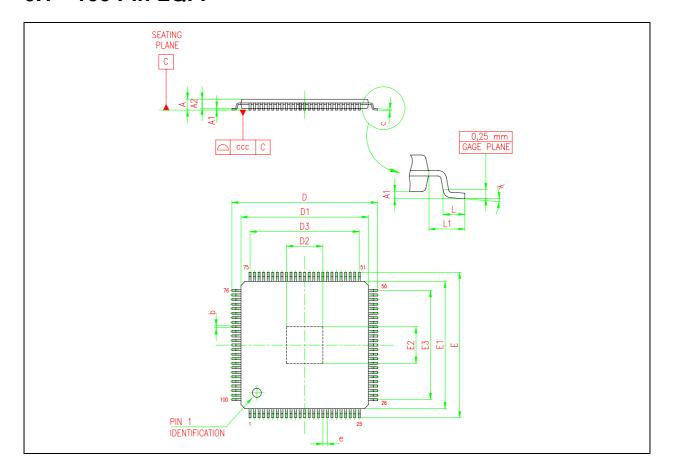

| 6.1        | 100 Pin LQFP                                 | 129 |

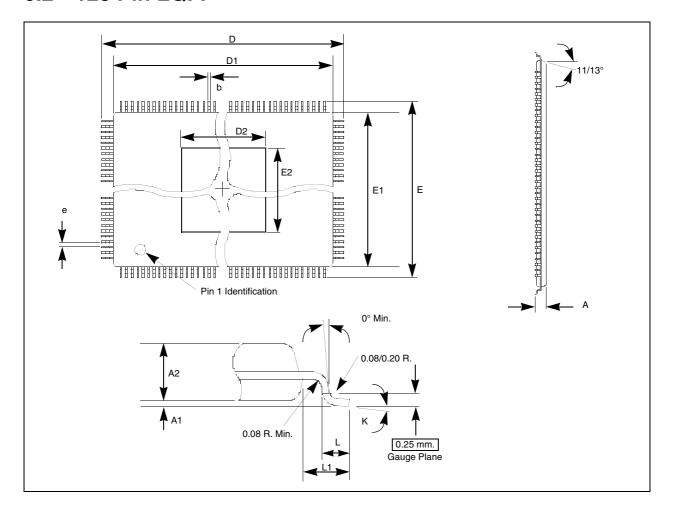

| 6.2        | 128 Pin LQFP                                 | 130 |

| Chapter 7  | Scaler Equations                             | 132 |

| Chapter 8  | ADE3800 vs ADE3700                           | 133 |

| Chapter 9  | Glossary                                     | 136 |

| Chapter 10 | Pavisian History                             | 127 |

# 1 Important Information

- XCLK: Crystal oscillator, usually 27 MHz.

- INCLK: ADC Sampling clock frequency, depends on input video mode pixel rate.

- DOTCLK and OUTCLK: Related to Panel Output Pixel Rate.

- SCLK: Scale Clock used for the line buffer Ram and picture zooming.

- If some bit fields are missing, these bits are marked as "reserved":

- return 0 when read, but it is also the user's duty to mask them upon readout, to ensure compatibility with later device releases

- must be written to 0 when the whole register is written

#### in all cases, the default reset value always prevails

- An asterisk denotes the default reset value for the corresponding bit(s).

- Unless all addresses and registers values are in hexadecimal.

- "not sticky" means dynamically updated (set or reset) by hardware, not a static bit.

- A "sticky" bit, once set remains set until the user clears it.

- When a value is followed by "typ" this means it is a typical value and PVT dependent.

- If a time or delay value does not have "min/typ/max" information, it is proportional to the XCLK frequency.

- Any register names containing HW are shadow registers: they report which value is currently being used by the chip.

- When a register bit field list has one bold option, it is the only choice for normal mode of operation.

- TCON must always be programmed for any panel type.

- Values spread out over several registers are organised as follows:

| 32-bit values |     | 24-bit values |     | 16-bit values |     |

|---------------|-----|---------------|-----|---------------|-----|

| _0            | LSB | _L or _0      | LSB | _L            | LSB |

| _1            |     | _M or _1      | MSB | _U            | USB |

| _2            |     | _U or _2      | USB |               |     |

| _3            | USB |               |     | •             |     |

### 2 General Description

The ADE3800 family of devices is capable of implementing all of the advanced features of todays LCD monitor products. For maximum flexibility, an external microcontroller (MCU) is used for controlling the ADE3800 and other monitor functions.

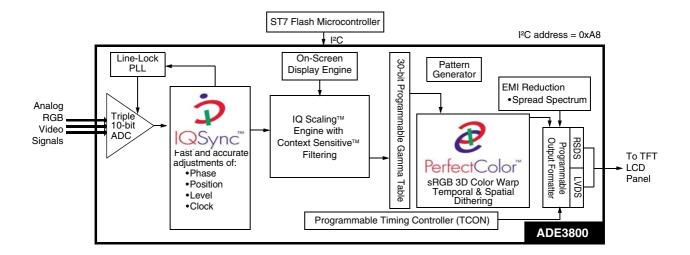

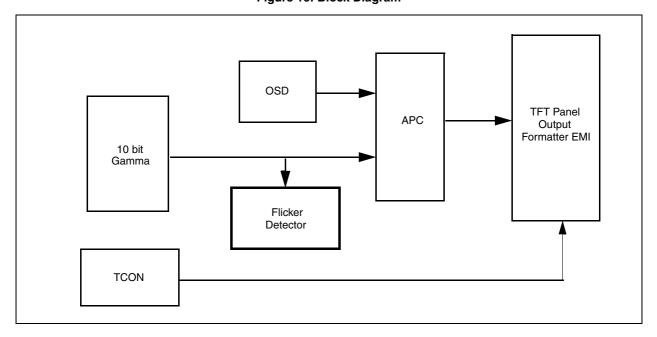

Figure 1: ADE3800 Block Diagram

The ADE3800 architecture unburdens the MCU from all data-intensive pixel manipulations, providing an optimal blend of features and code customizing without incurring the cost of a 16-bit processor or memory. The key interactions between the monitor MCU and the ADE3800 can be broken down into the features shown in Table 1.

**Feature Description of ADE3800 Operation Blocks Used Pages** Power-up / Initialize When power is first applied, the ADE3800 is asynchronously reset from a pin. **GLBL** 18 The MCU typically programs the ADE3800 with a number of default values and **SMEAS** 36 sets up the ADE3800 to identify activity on any of the input pins. All pre-LLK 30 configured values and RAMs, such as line-lock PLL settings, OSD characters, ADC 21 72 LCD timing values (output sequencer), scale kernels, gamma curves, sRGB OSD 53 color warp, APC dithering, output pin configuration (OMUX), etc. can be pre-**SCALER** loaded into the ADE3800. The typical end state is that the ADE3800 is **GAMMA** 71 **SRGB** 68 initialized into a low power mode, ready to turn active once the power button is **TCON** 102 pressed. APC 92 **OMUX** 94 Activity Detect When the monitor has been powered on, the inputs can be monitored for active **SMEAS** 36 video sources. Based on the activity monitors, the MCU chooses an input or power down state.

Table 1: ADE3800 Features (Sheet 1 of 2)

**General Description**

Table 1: ADE3800 Features (Sheet 2 of 2)

| Feature                          | Description of ADE3800 Operation                                                                                                                                                                                                                                                                                                                                                   | Blocks Used                          | Pages                      |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------|

| Sync / Timing<br>Measurement     | Once an input source is selected, all available information on frequencies and line/pixel counts is measured for the selected source and made available to the MCU.                                                                                                                                                                                                                | SMEAS                                | 36                         |

| Mode Set                         | Once the MCU has determined the matching video mode or calculated a video mode using a GTF algorithm, the datapath is programmed to drive the flat panel. Clock frequencies for the internal memory and datapath are also set at this time.                                                                                                                                        | GLBL<br>LLK<br>SRT<br>SMUX<br>SCALER | 18<br>30<br>33<br>43<br>53 |

| Autotune                         | When the MCU calls for an autotune, the MCU sets up an iterative loop to search for the best phase, gain, offset, etc. At each step of the loop, the MCU kicks off a test in which the ADE3800 performs extensive statistical analysis of the incoming data stream. The results of the analysis are made available to the MCU which is responsible for the optimization algorithm. | DMEAS<br>LLK<br>ADC<br>SMUX<br>SRT   | 47<br>30<br>21<br>43<br>33 |

| Digital Contrast /<br>Brightness | In response to user OSD control, the MCU can program single 8-bit registers that set brightness and contrast for each color channel independently.                                                                                                                                                                                                                                 | SRGB                                 | 68                         |

| White Point Control              | In response to user OSD control, the MCU can program three 8-bit registers that set the white point for the output.                                                                                                                                                                                                                                                                | SRGB                                 | 68                         |

| GAMMA<br>Adjustment              | The MCU can program the gamma RAMs to implement 10-bit accurate color transformations to match the panel color characteristics.                                                                                                                                                                                                                                                    | GAMMA                                | 71                         |

| sRGB Control                     | Allows simple, intuitive color control for parametric gamma correction and 3D color cube warping.                                                                                                                                                                                                                                                                                  | SRGB                                 | 68                         |

| Pattern Generation               | For production testing, the ADE3800 can be programmed by the MCU to output a wide set of test patterns.                                                                                                                                                                                                                                                                            | PGEN                                 | 59                         |

| Flicker Reduction                | For Smart Panel applications, the MCU can set up the flicker detection block to report any correlation with the polarity inversion signal. The MCU can then change the polarity inversion to a non-correlating pattern to eliminate flicker.                                                                                                                                       |                                      | 88<br>102                  |

| Backlight Control                | The ADE3800 provides two PWM outputs for direct control of the power components in a typical backlight. The MCU sets up the registers and enables the function.                                                                                                                                                                                                                    | PWM                                  | 119                        |

| Low Power State                  | To enter a low power state, the MCU can gate off most of the clocks and put the analog blocks into a low power standby state.                                                                                                                                                                                                                                                      | GLBL                                 | 18                         |

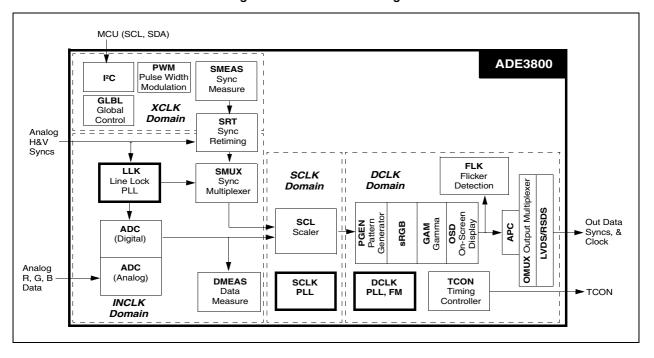

The following table gives a brief description of each block of the ADE3800:

Table 2: ADE3800 Block Descriptions

| Block                             | Description                                                                                                                                                                                                       |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Global Control (GLBL)             | Responsible for selecting clock sources, power control, I <sup>2</sup> C control and block by block synchronous reset generation                                                                                  |

| Frequency Synthesizer (FSYN)      | Generates the output clock (also known as the dot clock & DCLK) and the scaler clock (SCLK). Frequency modulation, phase control, and pulse extension (duty cycle control) of the output clock are also provided. |

| Analog-to-Digital Converter (ADC) | Has the following features:                                                                                                                                                                                       |

|                                   | - Supports input clocks up to 140MHz (SXGA 75Hz)                                                                                                                                                                  |

|                                   | - Adjustable analog amplifier bandwidth                                                                                                                                                                           |

|                                   | - Differential RGB input path for noise immunity                                                                                                                                                                  |

|                                   | - Built-in Sync-on-Green support                                                                                                                                                                                  |

|                                   | - Individual RGB clock delay control                                                                                                                                                                              |

|                                   | - Power down control                                                                                                                                                                                              |

|                                   | - Linear and independent Gain/Offset adjustment                                                                                                                                                                   |

| Analog Dithering (ADTH)           | Generates a 3-bit dither pattern to tune the 10-bit resolution of the ADC block.                                                                                                                                  |

| Line Lock PLL (LLK)               | Generates the ADC sample clock from an incoming HSync source.                                                                                                                                                     |

| Sync Retiming (SRT)               | Retimes synchronization signals (e.g. HSync and VSync) into either the XCLK or in-clock domains.                                                                                                                  |

| Input Sync Measurement (SMEAS)    | Monitors input port activity and measures input sync signals from all sources.                                                                                                                                    |

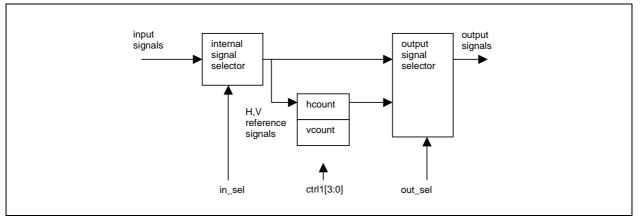

| Sync Multiplexer (SMUX)           | Synthesizes clamp and horizontal and vertical enable signals from input sync signals.                                                                                                                             |

|                                   | Selects which signals continue to the scaler block                                                                                                                                                                |

| Data Measurement (DMEAS)          | Measures several characteristics of the pixel data and sync signals.                                                                                                                                              |

| Scale (SCL)                       | Resizes images from one resolution to another.                                                                                                                                                                    |

| Pattern Generator (PGEN)          | Provides the ability of displaying a set of useful graphic patterns to help debugging and testing LCD panels.                                                                                                     |

| sRGB (SRGB)                       | Performs parametric gamma correction on multiple windows or full screen, used for video enhancement in a window and digital contrast/brightness control.                                                          |

|                                   | Allows 3D color cube warping RGB color space.                                                                                                                                                                     |

| Gamma (GAM)                       | Implements three independent 256 point gamma curves for each of R, G, and B channels.                                                                                                                             |

| On-Screen Display (OSD)           | Has the following features:                                                                                                                                                                                       |

|                                   | - One RAM block 4096x24 is used for the full operation of the OSD.                                                                                                                                                |

|                                   | - The characters can be displayed anywhere on the screen.                                                                                                                                                         |

|                                   | - Horizontal/Vertical Start location for each row in the OSD.                                                                                                                                                     |

|                                   | - Global Alpha blending for all the characters displayed as well as Alpha blending per color with 16 levels.                                                                                                      |

|                                   | - Horizontal/Vertical flip based per character.                                                                                                                                                                   |

|                                   | - 1bpp/2bpp/3bpp/4bpp characters supported.                                                                                                                                                                       |

|                                   | - Rotation supported by means of having a 18x12 pixel character or 12x18 pixel character.                                                                                                                         |

|                                   | - Color LUT of 64 colors (24bit RGB True Color)                                                                                                                                                                   |

| Flicker (FLK)                     | Computes a nonlinear correlation of LCD polarity inversion patterns and the LCD output data stream and provides the correlation results as scores to the microcontroller.                                         |

| Adaptive Phase Control (APC)      | Generates a 2-bit dither pattern for an 8-bit panel or a 4-bit dither pattern for a 6-bit panel to visually improve the amplitude resolution of the 10-bit RGB output signal.                                     |

**Table 2: ADE3800 Block Descriptions**

| Block                                        | Description                                                                                                                                                                                                                           |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Mux (OMUX)                            | An extension of the ADE3700 output mux block. The major changes are:                                                                                                                                                                  |

|                                              | - LVDS controls                                                                                                                                                                                                                       |

|                                              | - RSDS split line buffer                                                                                                                                                                                                              |

| Timing Controller (TCON)                     | Provides timing for Smart Panel applications and other applications that are sensitive to output synchronization timing. The timing unit is based on horizontal and vertical counters, which are locked with the output video stream. |

| LVDS/RSDS Features                           | Has the following features:                                                                                                                                                                                                           |

|                                              | - Power down                                                                                                                                                                                                                          |

|                                              | - Output swing and common mode programmable                                                                                                                                                                                           |

|                                              | - Individual channel programmable delay                                                                                                                                                                                               |

|                                              | - Programmable LVDS clock output polarity                                                                                                                                                                                             |

| Pulse Width Modulation (PWM)                 | Generates two signals that can be used to control backlight inverter switching power components directly. It is derived from XCLK and can be powered up independently of the DOTCLK and INCLK domains.                                |

| I <sup>2</sup> C Block Transfer (I2CBKT)     | Allows the internal I <sup>2</sup> C parallel bus to be driven by an xclk state machine to perform rapid block transfers between internal addresses.                                                                                  |

| I <sup>2</sup> C Registers and RAM Addresses | Memory mapping of all RAM and register locations accessible by I <sup>2</sup> C.                                                                                                                                                      |

ADE3800 Pin Descriptions

### 3 Pin Descriptions

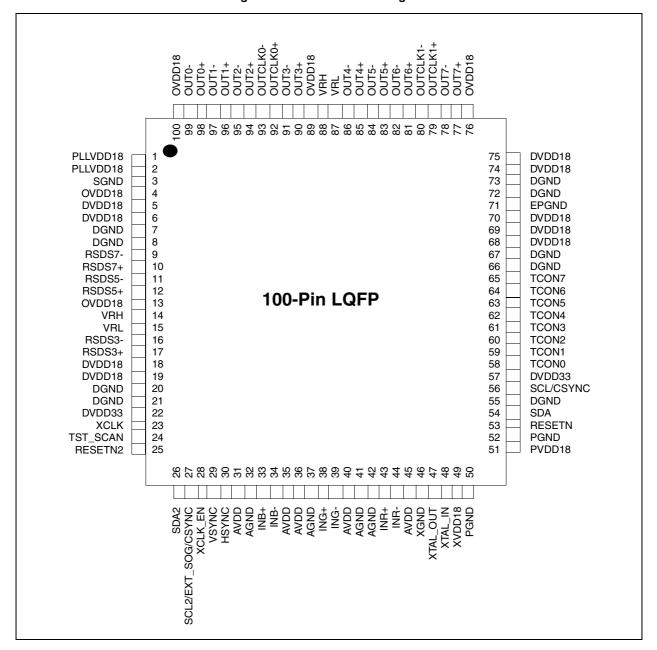

Figure 2: LQFP100 Pinout Diagram

Pin Descriptions ADE3800

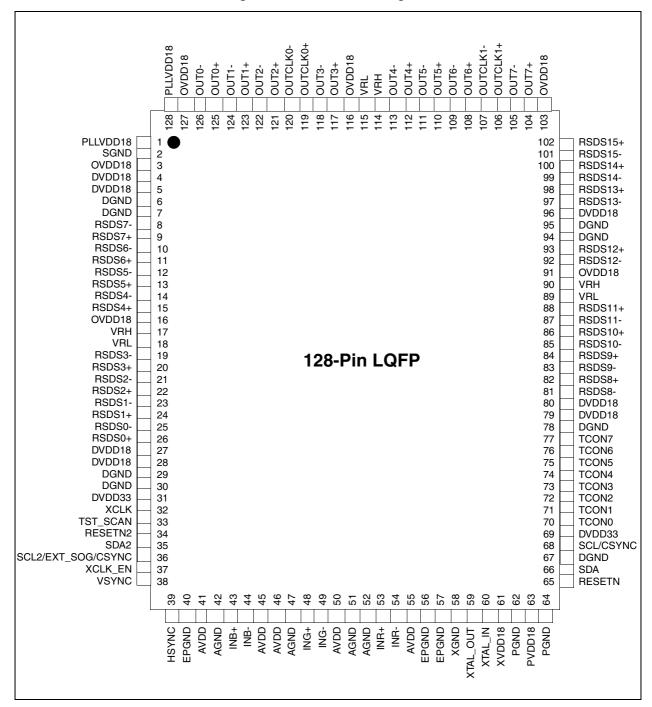

Figure 3: LQFP128 Pinout Diagram

Table 3: Analog Input Signals (Sheet 1 of 2)

| LQFP100 | LQFP128 | Name | Input/<br>Output | Description                    |

|---------|---------|------|------------------|--------------------------------|

| 43      | 53      | INR+ | I                | Positive ADC Red Channel Input |

| 44      | 54      | INR- | I                | Negative ADC Red Channel Input |

ADE3800 Pin Descriptions

Table 3: Analog Input Signals (Sheet 2 of 2)

| LQFP100 | LQFP128 | Name  | Input/<br>Output | Description                                    |

|---------|---------|-------|------------------|------------------------------------------------|

| 38      | 48      | ING+  | I                | Positive ADC Green Channel Input               |

| 39      | 49      | ING-  | I                | Negative ADC Green Channel Input               |

| 33      | 43      | INB+  | I                | Positive ADC Blue Channel Input                |

| 34      | 44      | INB-  | I                | Negative ADC Blue Channel Input                |

| 29      | 38      | VSYNC | I                | Vertical Sync Input Signal                     |

| 30      | 39      | HSYNC | I                | Horizontal Sync or Composite Sync Input Signal |

Table 4: Output Signals and TCON Signals (Sheet 1 of 2)

| LQFP100 | LQFP128 | Name    | Input/<br>Output | Description            |

|---------|---------|---------|------------------|------------------------|

|         | 25      | RSDS0-  | 0                | RSDS Channel 0 Data -  |

|         | 26      | RSDS0+  | 0                | RSDS Channel 0 Data +  |

|         | 23      | RSDS1-  | 0                | RSDS Channel 1 Data -  |

|         | 24      | RSDS1+  | 0                | RSDS Channel 1 Data +  |

|         | 21      | RSDS2-  | 0                | RSDS Channel 2 Data -  |

|         | 22      | RSDS2+  | 0                | RSDS Channel 2 Data +  |

| 16      | 19      | RSDS3-  | 0                | RSDS Channel 3 Data -  |

| 17      | 20      | RSDS3+  | 0                | RSDS Channel 3 Data +  |

|         | 14      | RSDS4-  | 0                | RSDS Channel 4 Data -  |

|         | 15      | RSDS4+  | 0                | RSDS Channel 4 Data +  |

| 11      | 12      | RSDS5-  | 0                | RSDS Channel 5 Data -  |

| 12      | 13      | RSDS5+  | 0                | RSDS Channel 5 Data +  |

|         | 10      | RSDS6-  | 0                | RSDS Channel 6 Data -  |

|         | 11      | RSDS6+  | 0                | RSDS Channel 6 Data +  |

| 9       | 8       | RSDS7-  | 0                | RSDS Channel 7 Data -  |

| 10      | 9       | RSDS7+  | 0                | RSDS Channel 7 Data +  |

|         | 81      | RSDS8-  | 0                | RSDS Channel 8 Data -  |

|         | 82      | RSDS8+  | 0                | RSDS Channel 8 Data +  |

|         | 83      | RSDS9-  | 0                | RSDS Channel 9 Data -  |

|         | 84      | RSDS9+  | 0                | RSDS Channel 9 Data +  |

|         | 85      | RSDS10- | 0                | RSDS Channel 10 Data - |

|         | 86      | RSDS10+ | 0                | RSDS Channel 10 Data + |

|         | 87      | RSDS11- | 0                | RSDS Channel 11 Data - |

|         | 88      | RSDS11+ | 0                | RSDS Channel 11 Data + |

|         | 92      | RSDS12- | 0                | RSDS Front Side CLK-   |

|         | 93      | RSDS12+ | 0                | RSDS Front Side CLK+   |

|         | 97      | RSDS13- | 0                | RSDS Channel 13 Data-  |

|         | 98      | RSDS13+ | 0                | RSDS Channel 13 Data+  |

Pin Descriptions ADE3800

Table 4: Output Signals and TCON Signals (Sheet 2 of 2)

| LQFP100 | LQFP128 | Name     | Input/<br>Output | Description                                                         |

|---------|---------|----------|------------------|---------------------------------------------------------------------|

|         | 99      | RSDS14-  | 0                | RSDS Channel 14 Data-                                               |

|         | 100     | RSDS14+  | 0                | RSDS Channel 14 Data+                                               |

|         | 101     | RSDS15-  | 0                | RSDS Channel 15 Data-                                               |

|         | 102     | RSDS15+  | 0                | RSDS Channel 15 Data+                                               |

| 98      | 125     | OUT0+    | 0                | +LVDS Channel 0 Differential Data Output or RSDS Channel 16 Data +  |

| 99      | 126     | OUT0-    | 0                | -LVDS Channel 0 Differential Data Output or RSDS Channel 16 Data -  |

| 96      | 123     | OUT1+    | 0                | +LVDS Channel 1 Differential Data Output or RSDS channel 17 Data +  |

| 97      | 124     | OUT1-    | 0                | -LVDS Channel 1 Differential Data Output or RSDS Channel 17 Data -  |

| 94      | 121     | OUT2+    | 0                | +LVDS Channel 2 Differential Data Output or RSDS Channel 18 Data +  |

| 95      | 122     | OUT2-    | 0                | -LVDS Channel 2 Differential Data Output or RSDS Channel 18 Data -  |

| 90      | 117     | OUT3+    | 0                | +LVDS Channel 3 Differential Data Output or RSDS Channel 19 Data +  |

| 91      | 118     | OUT3-    | 0                | -LVDS Channel 3 Differential Data Output or RSDS Channel 19 Data -  |

| 85      | 112     | OUT4+    | 0                | +LVDS Channel 4 Differential Data Output or RSDS Back Side CLK-     |

| 86      | 113     | OUT4-    | 0                | -LVDS Channel 4 Differential Data Output or RSDS Back Side CLK+     |

| 83      | 110     | OUT5+    | 0                | +LVDS Channel 5 Differential Data Output or RSDS Channel 22 Data +  |

| 84      | 111     | OUT5-    | 0                | -LVDS Channel 5 Differential Data Output or RSDS Channel 22 Data -  |

| 81      | 108     | OUT6+    | 0                | +LVDS Channel 6 Differential Data Output or RSDS Channel 23 Data +  |

| 82      | 109     | OUT6-    | 0                | -LVDS Channel 6 Differential Data Output or RSDS Channel 23 Data -  |

| 77      | 104     | OUT7+    | 0                | +LVDS Channel 7 Differential Data Output or RSDS Channel 24 Data +  |

| 78      | 105     | OUT7-    | 0                | -LVDS Channel 7 Differential Data Output or RSDS Channel 24 Data -  |

| 92      | 119     | OUTCLK0+ | 0                | +LVDS Channel A Differential Clock Output or RSDS Channel 20 Data + |

| 93      | 120     | OUTCLK0- | 0                | -LVDS Channel A Differential Clock Output or RSDS Channel 20 Data - |

| 79      | 106     | OUTCLK1+ | 0                | +LVDS Channel B Differential Clock Output or RSDS Channel 25 Data + |

| 80      | 107     | OUTCLK1- | 0                | -LVDS Channel B Differential Clock Output or RSDS Channel 25 Data - |

| 58      | 70      | TCON0    | 0                | TCON Output 0 or PWM B Output                                       |

| 59      | 71      | TCON1    | 0                | TCON Output 1 or PWM A Output                                       |

| 60      | 72      | TCON2    | 0                | TCON Output 2                                                       |

| 61      | 73      | TCON3    | 0                | TCON Output 3                                                       |

| 62      | 74      | TCON4    | 0                | TCON Output 4                                                       |

| 63      | 75      | TCON5    | 0                | TCON Output 5                                                       |

| 64      | 76      | TCON6    | 0                | TCON Output 6                                                       |

| 65      | 77      | TCON7    | 0                | TCON Output 7                                                       |

Table 5: System Controls (Sheet 1 of 2)

| LQFP100 | LQFP128 | Name     | Input/<br>Output | Description               |

|---------|---------|----------|------------------|---------------------------|

| 47      | 59      | XTAL_OUT | 0                | Crystal Oscillator output |

| 48      | 60      | XTAL_IN  | I                | Crystal Oscillator input  |

ADE3800 Pin Descriptions

Table 5: System Controls (Sheet 2 of 2)

| LQFP100 | LQFP128 | Name                   | Input/<br>Output | Description                                                                                                                             |

|---------|---------|------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 23      | 32      | XCLK                   | I/O              | Crystal clock buffered output. Controlled by XCLK_EN pin                                                                                |

| 28      | 37      | XCLK_EN                | I                | Crystal clock output enable.  When connected to 3.3 V, the XCLK output is active  When connected to Ground, the XCLK output is disabled |

| 25      | 34      | RESETN2                | ı                | Reset 2 input <sup>a</sup> . Active Low                                                                                                 |

| 53      | 65      | RESETN                 | I                | Reset input <sup>1</sup> . Active Low                                                                                                   |

| 54      | 66      | SDA                    | I/O              | I2C Data <sup>b</sup> . Open drain                                                                                                      |

| 56      | 68      | SCL/CSYNC              | I                | I2C Clock <sup>c</sup> or Composite Sync Input Signal                                                                                   |

| 26      | 35      | SDA2                   | I/O              | I2C 2 Data <sup>2</sup> . Open drain                                                                                                    |

| 27      | 36      | SCL2/EXT_SOG/<br>CSYNC | I                | I2C 2 Clock <sup>3</sup> or Composite Sync Input Signal                                                                                 |

| 24      | 33      | TST_SCAN               | I                | Reserved for test. Should be connected to Digital Ground                                                                                |

- a. RESETN and RESETN2 pins are ORed together internally. The pin which is not used must be connected to ground.

- b. The SDA and SDA2 pins share the same internal bi-directional control. The pin that is not used reverts as output and must be left floating or connected to a pull-up resistor.

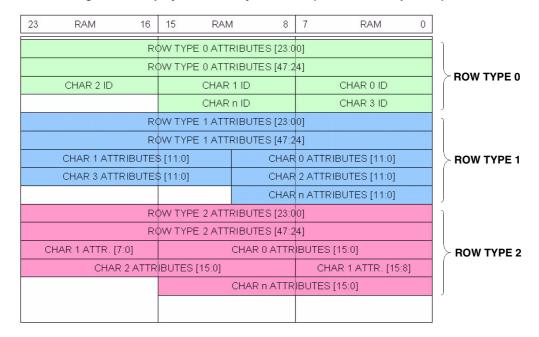

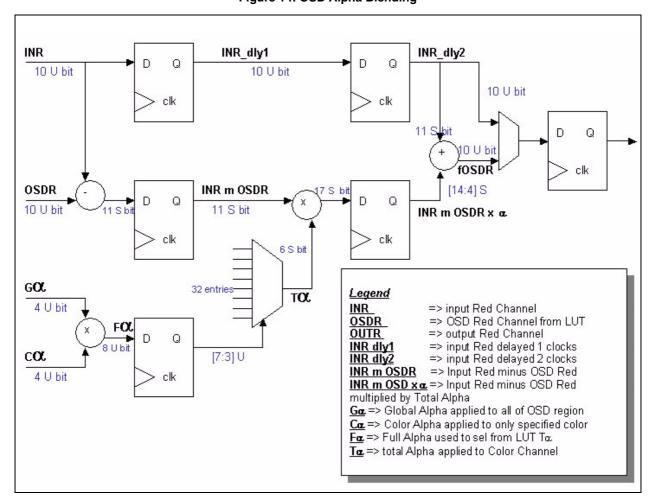

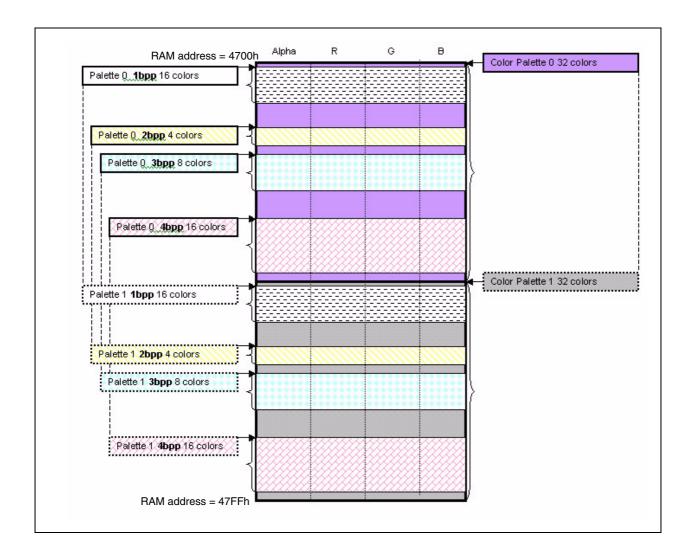

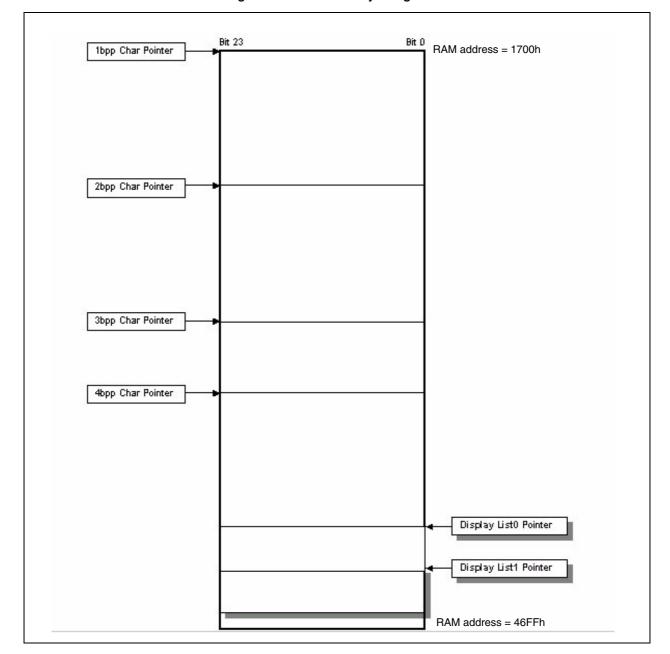

- c. This device has two RESET/I2C ports (RESETN/SCL/SDA or RESETN2/EXT\_SOG/SDA2) to facilitate PCB layout. The state of the two RESET pins determines which RESET/I2C port is active. The RESET pin that is held in the low state disables that RESET/I2C port for normal RESET/I2C operations. However, the disabled ports SCL input (either SCL or EXT\_SOG) can be used as a CSYNC input from an external CSYNC extractor. If this CSYNC input is not required, then the unused SCL pin should be connected to ground