# **EPCQ-A Serial Configuration Device** Datasheet

CF52014 | 2019.10.01 Latest document on the web: PDF | HTML

Send Feedback

# Contents

| 1. EPCQ-A Serial Configuration Device Datasheet                | 4        |

|----------------------------------------------------------------|----------|

| 1.1. Supported Devices                                         | 4        |

| 1.2. Features                                                  |          |

| 1.3. Operating Conditions                                      | 5        |

| 1.3.1. Absolute Maximum Ratings                                |          |

| 1.3.2. Recommended Operating Conditions                        |          |

| 1.3.3. DC Operating Conditions                                 |          |

| 1.3.4. AC Measurement Conditions                               |          |

| 1.3.5. ICC Supply Current.                                     |          |

| 1.3.6. Capacitance                                             |          |

| 1.4. Pin Information                                           |          |

| 1.4.1. Pin-Out Diagram for EPCQ4A, EPCQ16A and EPCQ32A Devices |          |

| 1.4.2. Pin-Out Diagram for EPCQ64A and EPCQ128A Devices        |          |

| 1.4.3. EPCQ-A Device Pin Description                           |          |

| 1.5. Device Package and Ordering Code                          |          |

| 1.5.1. Package                                                 |          |

| 1.5.2. Ordering Code                                           |          |

| 1.6. Memory Array Organization                                 |          |

| 1.6.1. Address Range for EPCQ4A                                |          |

| 1.6.2. Address Range for EPCQ16A                               |          |

| 1.6.3. Address Range for EPCQ32A                               |          |

| 1.6.4. Address Range for EPCQ64A                               |          |

| 1.6.5. Address Range for EPCQ128A                              |          |

| 1.7. Memory Operations                                         |          |

| 1.7.1. Timing Requirements                                     |          |

| 1.8. Status Register.                                          |          |

| 1.8.1. Read Status Operation                                   |          |

| 1.8.2. Write Status Operation                                  |          |

| 1.9. Summary of Operation Codes                                |          |

| 1.9.1. Read Bytes Operation (03h)                              |          |

| 1.9.2. Fast Read Operation (0Bh)                               |          |

| 1.9.3. Extended Dual Input Fast Read Operation (BBh)           |          |

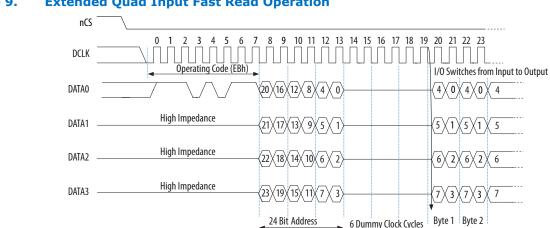

| 1.9.4. Extended Quad Input Fast Read Operation (EBh)           |          |

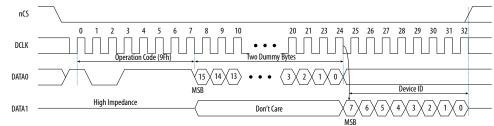

| 1.9.5. Read Device Identification Operation (9Fh)              |          |

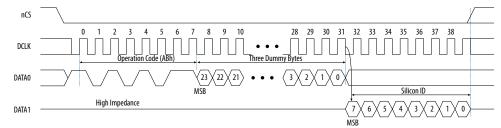

| 1.9.6. Read Silicon Identification Operation (ABh)             |          |

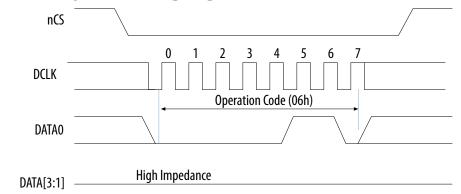

| 1.9.7. Write Enable Operation (06h)                            |          |

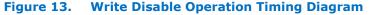

| 1.9.8. Write Disable Operation (04h)                           |          |

| 1.9.9. Write Bytes Operation (02h)                             |          |

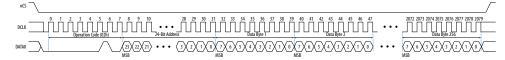

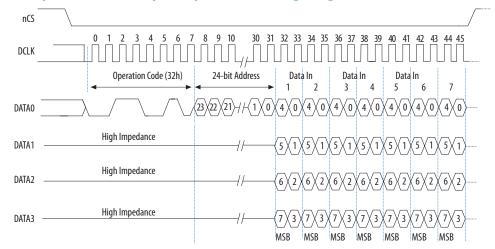

| 1.9.10. Quad Input Fast Write Bytes Operation (32h)            | Z/<br>28 |

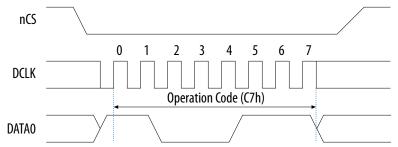

| 1.9.11. Erase Bulk Operation (C7h)                             |          |

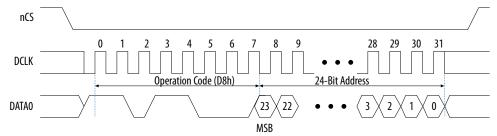

| 1.9.12. Erase Sector Operation (D8h)                           |          |

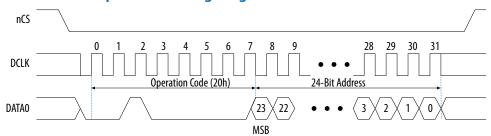

| 1.9.13. Erase Subsector Operation (20h)                        |          |

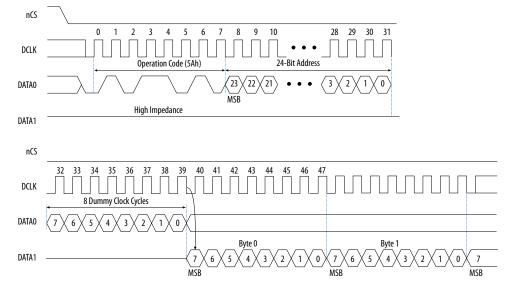

| 1.9.14. Read SFDP Register Operation (56h)                     |          |

| 1.9.14. Read SFDP Register Operation (SAIT)                    |          |

| 1.10. Power Mode                                               |          |

| 1.11. 1. Write Operation Timing                                |          |

| 1.11.2. Read Operation Timing                                  |          |

|                                                                |          |

| 1.12. Programming and Configuration File Support                                     | 34 |

|--------------------------------------------------------------------------------------|----|

| 1.13. Appendix: SFDP Register Definitions                                            | 34 |

| 1.14. Document Revision History for the EPCQ-A Serial Configuration Device Datasheet | 37 |

# **1. EPCQ-A Serial Configuration Device Datasheet**

#### **Related Information**

AN822: Intel<sup>®</sup> Configuration Device Migration Guideline

# **1.1. Supported Devices**

#### Table 1. Supported Intel EPCQ-A Devices

| Device   | Memory Size<br>(bits) | On-Chip<br>Decompression<br>Support | ISP<br>Support | Cascading<br>Support | Reprogrammable | Recommended<br>Operating Voltage<br>(V) |

|----------|-----------------------|-------------------------------------|----------------|----------------------|----------------|-----------------------------------------|

| EPCQ4A   | 4,194,304             | No                                  | Yes            | No                   | Yes            | 3.3                                     |

| EPCQ16A  | 16,777,216            | No                                  | Yes            | No                   | Yes            | 3.3                                     |

| EPCQ32A  | 33,554,432            | No                                  | Yes            | No                   | Yes            | 3.3                                     |

| EPCQ64A  | 67,108,864            | No                                  | Yes            | No                   | Yes            | 3.3                                     |

| EPCQ128A | 134,217,728           | No                                  | Yes            | No                   | Yes            | 3.3                                     |

# **1.2. Features**

EPCQ-A devices offer the following features:

- Serial or quad-serial FPGA configuration in devices that support active serial (AS) x1 or AS  $x4^{(1)}$  configuration schemes

- Low cost, low pin count, and non-volatile memory

- 2.7-V to 3.6-V operation

- Available in 8-pin small-outline integrated circuit (SOIC) package for EPCQ4A, EPCQ16A, and EPCQ32A devices

- Available in 16-pin SOIC package for EPCQ64A and EPCQ128A devices

- Reprogrammable memory more than 100,000 program-erase cycles

- Write protection support for memory sectors using status register bits

- Fast read, extended dual input fast read, and extended quad input fast read of the entire memory using a single operation code

- Reprogrammable with an external microprocessor using the SRunner software driver

- In-system programming (ISP) support with the SRunner software driver

<sup>&</sup>lt;sup>(1)</sup> AS x4 is not applicable for EPCQ4A.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

- ISP support with Intel $^{\ensuremath{\mathbb{R}}}$  FPGA Download Cable II, Intel FPGA Download Cable, or Intel FPGA Ethernet Cable

- By default, the memory array is erased and the bits are set to  $\ensuremath{\mathtt{1}}$

- More than 20-year data retention

- Supports JEDEC standard Serial Flash Discoverable Parameter (SFDP)

# **1.3. Operating Conditions**

# **1.3.1. Absolute Maximum Ratings**

#### Table 2. Absolute Maximum Ratings for EPCQ-A Devices

| Symbol           | Parameter                         | Condition                        | Min  | Max                  | Unit |

|------------------|-----------------------------------|----------------------------------|------|----------------------|------|

| V <sub>CC</sub>  | Supply voltage                    | With respect to GND              | -0.6 | 4.6                  | V    |

| V <sub>IO</sub>  | Input or output voltage           | With respect to GND              | -0.6 | V <sub>CC</sub> +0.4 | V    |

| T <sub>STG</sub> | Storage temperature               | No bias                          | -65  | 150                  | °C   |

| V <sub>IT</sub>  | Transient voltage on any pin      | < 20ns transient relative to GND | -2.0 | V <sub>CC</sub> +2.0 | V    |

| P <sub>D</sub>   | Power dissipation                 | EPCQ4A                           | _    | 18                   | mW   |

|                  |                                   | EPCQ16A, EPCQ32A, and EPCQ64A    | _    | 54                   | mW   |

|                  |                                   | EPCQ128A                         | _    | 72                   | mW   |

| I <sub>MAX</sub> | DC V <sub>CC</sub> or GND current | EPCQ4A                           | _    | 5                    | mA   |

|                  |                                   | EPCQ16A, EPCQ32A, and EPCQ64A    | _    | 15                   | mA   |

|                  |                                   | EPCQ128A                         | _    | 20                   | mA   |

# **1.3.2. Recommended Operating Conditions**

#### Table 3. Recommended Operating Conditions for EPCQ-A Devices

|        | Symbol          | Parameter                      | Condition          | Min | Мах | Unit |

|--------|-----------------|--------------------------------|--------------------|-----|-----|------|

| \<br>\ | V <sub>CC</sub> | Supply voltage                 | (2)                | 2.7 | 3.6 | V    |

|        | T <sub>A</sub>  | Ambient temperature, Operating | For industrial use | -40 | 85  | °C   |

*Note:* For the junction temperature (T<sub>J</sub>), follow the T<sub>A</sub> specification.

$<sup>^{(2)}</sup>$  V<sub>CC</sub> voltage during a Read operation can operate across the min and max range but should not exceed  $\pm 10\%$  of the programming (erase/write) voltage.

# 1.3.3. DC Operating Conditions

#### Table 4. DC Operating Conditions for EPCQ-A Devices

| Symbol          | Parameter                                                               | Condition                              | Min                   | Max                   | Unit |

|-----------------|-------------------------------------------------------------------------|----------------------------------------|-----------------------|-----------------------|------|

| V <sub>IH</sub> | High-level input voltage                                                | -                                      | 0.7 x V <sub>CC</sub> | $V_{CC} + 0.4$        | V    |

| V <sub>IL</sub> | Low-level input voltage                                                 | -                                      | -0.5                  | 0.3 x V <sub>CC</sub> | V    |

| V <sub>OH</sub> | High-level output voltage                                               | I <sub>OH</sub> = -100 μA              | V <sub>CC</sub> - 0.2 | _                     | V    |

| V <sub>OL</sub> | Low-level output voltage for EPCQ4A                                     | I <sub>OL</sub> = 100 μA               | _                     | 0.4                   | V    |

|                 | Low-level output voltage for EPCQ16A,<br>EPCQ32A, EPCQ64A, and EPCQ128A |                                        | _                     | 0.2                   | V    |

| II              | Input leakage current                                                   | V <sub>I</sub> =V <sub>CC</sub> or GND | -2                    | 2                     | μA   |

| I <sub>OZ</sub> | Tri-state output off-state current                                      | $V_0 = V_{CC}$ or GND                  | -2                    | 2                     | μA   |

| I <sub>LR</sub> | Input leakage                                                           | 0≤/Reset <v<sub>CC</v<sub>             | _                     | 12                    | μA   |

|                 |                                                                         | /Reset = V <sub>CC</sub>               | _                     | 1                     | μA   |

| R <sub>PR</sub> | Pull-up resistance                                                      | _                                      | 300                   | 1000                  | kΩ   |

# **1.3.4. AC Measurement Conditions**

#### Table 5. AC Measurement Conditions for EPCQ-A Devices

| Symbol                          | Parameter                                                                  | Min                   | Max                   | Unit |

|---------------------------------|----------------------------------------------------------------------------|-----------------------|-----------------------|------|

| CL                              | Load Capacitance                                                           | —                     | 30                    | pF   |

| T <sub>R</sub> , T <sub>F</sub> | Input Rise and Fall Times                                                  | _                     | 5                     | ns   |

| V <sub>IN</sub>                 | Input Pulse Voltages                                                       | 0.1 V <sub>CC</sub> t | V                     |      |

| IN                              | Input Timing Reference Voltages 0.3 V <sub>CC</sub> to 0.7 V <sub>CC</sub> |                       |                       |      |

| Out                             | Output Timing Reference Voltages                                           | 0.5 V <sub>CC</sub> t | o 0.5 V <sub>CC</sub> | V    |

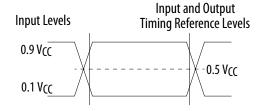

#### Figure 1. AC Measurement I/O Waveform

# 1.3.5. ICC Supply Current

#### Table 6. I<sub>CC</sub> Supply Current AC Measurement

| Symbol           | Parameter                                                                | Condition | Min | Max | Unit    |

|------------------|--------------------------------------------------------------------------|-----------|-----|-----|---------|

| I <sub>CC0</sub> | V <sub>CC</sub> supply current for EPCQ4A, EPCQ16A, EPCQ32A, and EPCQ64A | Standby   | 10  | 50  | μA      |

|                  | V <sub>CC</sub> supply current for EPCQ128A                              |           | 10  | 60  |         |

|                  |                                                                          |           |     | сог | ntinued |

1. EPCQ-A Serial Configuration Device Datasheet CF52014 | 2019.10.01

| Symbol           | Parameter                                                        | Condition                | Min | Max | Unit |

|------------------|------------------------------------------------------------------|--------------------------|-----|-----|------|

| I <sub>CC1</sub> | V <sub>CC</sub> supply current for EPCQ4A                        | During active power mode | 1   | 5   | mA   |

|                  | V <sub>CC</sub> supply current for EPCQ16A, EPCQ32A, and EPCQ64A |                          | 1   | 15  |      |

|                  | V <sub>CC</sub> supply current for EPCQ128A                      |                          | 1   | 20  |      |

## 1.3.6. Capacitance

#### Table 7.Capacitance for EPCQ-A Devices

Capacitance is sample-tested only at  $T_A$  = 25 °C and at  $V_{CC}$  = 3.0 V.

| Symbol           | Parameter              | Condition             | Min | Max | Unit |

|------------------|------------------------|-----------------------|-----|-----|------|

| C <sub>IN</sub>  | Input pin capacitance  | V <sub>IN</sub> =0 V  | _   | 6   | pF   |

| C <sub>OUT</sub> | Output pin capacitance | V <sub>OUT</sub> =0 V | _   | 8   | pF   |

# **1.4. Pin Information**

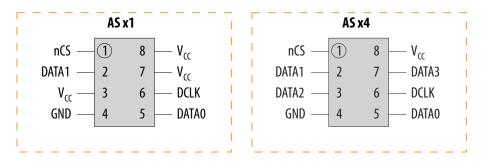

### 1.4.1. Pin-Out Diagram for EPCQ4A, EPCQ16A and EPCQ32A Devices

# Figure 2. AS x1 and AS x4 Pin-Out Diagrams for EPCQ4A, EPCQ16A, and EPCQ32A Devices

Note: EPCQ4A supports AS x1 only.

(intel)

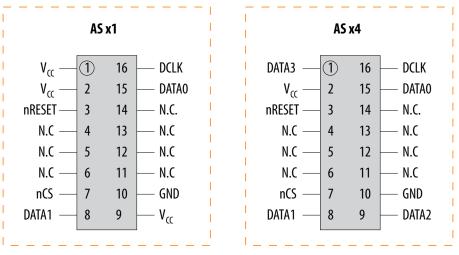

## 1.4.2. Pin-Out Diagram for EPCQ64A and EPCQ128A Devices

#### Figure 3. AS x1 and AS x4 Pin-Out Diagrams for EPCQ64A and EPCQ128A Devices

Notes:

N.C pins must be left unconnected.

There is an internal pull-up resistor for the dedicated nRESET pin. If the reset function is not needed, connect this pin to Vcc or leave it unconnected.

# 1.4.3. EPCQ-A Device Pin Description

#### Table 8. EPCQ-A Device Pin Description

| Pin<br>Number<br>in 8-Pin<br>SOIC<br>PackagePin<br>Number<br>in 8-Pin<br>SOIC<br>PackagePin<br>Number<br>in 16-Pin<br>SOIC<br>PackageDATA0515515I/ODATA0515515I/ODATA0515515For AS x1 mode, use this pin at<br>pin to write or program the EP<br>During write or program opera<br>latched at rising edges of the I<br>pin is equivalent to the ASDI p<br>pro AS x4 mode, use this pin at<br>During write or program opera<br>as an input pin that serially tra<br>the EPCQ-A device. The data at<br>edges of the DCLK signal. Duri<br>configuration operations, this p<br>output signal pin that serially to<br>the EPCQ-A device to the FF<br>shifted out at falling edges of the DCLK signal put fast read<br>output fast read operations. this pin acts as an input pin that<br>serially to<br>the EPCQ-A device. The data at<br>edges of the DCLK signal put fast read<br>output signal pin that serially to<br>the SDCA device. The data at<br>edges of the DCLK signal point that serially to<br>the EPCQ-A device. The data at<br>edges of the DCLK signal pin that serially to<br>this pin acts as an input pin that serially to<br>the SDCA device. The data at<br>edges of the DCLK signal pin that serially to<br>the SDCA device. The shifted out at falling edges of the<br>During the quadinput fast read operations. This pin acts as an input pin the<br>the SDCA device. The shifted out at falling edges of the DCLK signal pin that serially to<br>the SDCA device. The shifted out at falling edges of the DCLK signal pin that serially to<br>the SDCA device. The shifted out fast read operations. This pin acts as an input pin the shifted out fast read operations. This pin acts as an input pin that serial pin the SDCA device. The shifted out fast read operations. This pin acts as an input pin the shifted out fast | n                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pin Type | AS x1 Pin-Out AS x4 Pin-Out Diagram Diagram |                            | Pin Name                    |                            |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------|----------------------------|-----------------------------|----------------------------|--------|

| pin to write or program the EP<br>During write or program opera<br>latched at rising edges of the I<br>pin is equivalent to the ASDI p<br>For AS x4 mode, use this pin a<br>During write or program opera<br>as an input pin that serially tra<br>the EPCQ-A device. The data a<br>edges of the DCLK signal. Duri<br>configuration operations, this p<br>output signal pin that serially to<br>of the EPCQ-A device to the FF<br>shifted out at falling edges of t<br>During the quad input fast writ<br>this pin acts as an input pin th<br>data into the EPCQ-A device. T<br>at rising edges of the DCLK sig<br>extended dual input fast read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | Number<br>in 16-Pin<br>SOIC                 | Number<br>in 8-Pin<br>SOIC | Number<br>in 16-Pin<br>SOIC | Number<br>in 8-Pin<br>SOIC |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PCQ-A device.<br>ations, data are<br>DCLK signal. This<br>pin in EPCS devices<br>as an I/O signal pin<br>rations, this pin acts<br>ransfers data into<br>are latched at rising<br>ring read or<br>pin acts as an<br>transfers data out<br>FPGA. The data is<br>the DCLK signal.<br>rite bytes operation,<br>hat serially transfers<br>The data is latched<br>ignal. During<br>I or extended quad | pin to write or program the EP<br>During write or program opera<br>latched at rising edges of the I<br>pin is equivalent to the ASDI p<br>For AS x4 mode, use this pin a<br>During write or program opera<br>as an input pin that serially tra<br>the EPCQ-A device. The data a<br>edges of the DCLK signal. Duri<br>configuration operations, this p<br>output signal pin that serially fo<br>the EPCQ-A device to the FF<br>shifted out at falling edges of<br>During the quad input fast wri<br>this pin acts as an input pin th<br>data into the EPCQ-A device. The<br>at rising edges of the DCLK signal | I/O      | 15                                          | 5                          | 15                          | 5                          | DATA 0 |

1. EPCQ-A Serial Configuration Device Datasheet CF52014 | 2019.10.01

| DataData1000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pin Name | e AS x1 Pin-Out AS x4 Pin-Out Diagram Diagram |                             | Pin Type                   | Description                 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------|-----------------------------|----------------------------|-----------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA1Z8Z8I/OFor AS X1 and x4 modes, use this pin as an output signal pin that serially transfers data out of the EPC2.A device to the PCA. Hourd at a falling edges of the DCLX signal.DATA1Z8Z8I/OFor AS X1 and x4 modes, use this pin as an output signal pin that serially transfers data out of the EPC2.A device to the PFCA during read or configuration operations. The transition of the signal is at falling edges of the DCLX signal.DATA2SSI/OFor AS X1 and x4 modes, use this pin as an output signal pin that serially transfers data into the EPC2.A device. The data is fulling edges of the DCLX signal.DATA2SSPFor AS X1 mode, this pin as an output signal pin that serially transfer data out of the EPC2.A device to the EPCA device to the EP |          | Number<br>in 8-Pin<br>SOIC                    | Number<br>in 16-Pin<br>SOIC | Number<br>in 8-Pin<br>SOIC | Number<br>in 16-Pin<br>SOIC |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Market<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>Barket<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                               |                             |                            |                             |       | of the EPCQ-A device to the FPGA. The data is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| For AS x4 mode, use this pin as an output signal<br>that serially transfers data out of the EPCQ-A<br>device to the FPGA during read or configuration<br>operation, this pin acts as an output signal pin<br>that serially transfers data out of the EPCQ-A<br>device to the FPGA during read or configuration<br>operation, this pin acts as an output signal pin<br>that serially transfers data out of the EPCQ-A<br>device to the FPGA. The data is shifted out at<br>falling edges of the DCLK signal.DATA371I/OFor AS x1 mode, this pin must connect to Vcc.<br>For AS x4 mode, use this pin as an output signal<br>that serially transfers data out of the EPCQ-A<br>device to the FPGA. The data is shifted out at<br>falling edges of the DCLK signal.DATA371I/OFor AS x1 mode, this pin must connect to Vcc.<br>For AS x4 mode, use this pin as an output signal<br>that serially transfers data out of the EPCQ-A<br>device to the FPGA during read or configuration<br>operations. The transition of the signal is at<br>falling edges of the DCLK signal.nCS1717InputnCS1717InputDCLK6166InputThe experiment of the signal is in signal<br>signal is in high, the device is eabled and its in active<br>mode. After power up, the EPCQ-A device<br>requires a falling edge on the nCS signal before<br>you begin any operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DATA1    | 2                                             | 8                           | 2                          | 8                           | I/O   | output signal pin that serially transfers data out<br>of the EPCQ-A device to the FPGA during read or<br>configuration operations. The transition of the<br>signal is at falling edges of the DCLK signal. This<br>pin is equivalent to the DATA pin in EPCS devices.<br>During the quad input fast write bytes operation,<br>this pin acts as an input signal pin that serially<br>transfers data into the EPCQ-A device. The data is<br>latched at rising edges of the DCLK signal.<br>During extended quad input fast read operations,<br>this pin acts as an output signal pin that serially<br>transfer data out of the EPCQ-A device to the<br>FPGA. The data is shifted out at falling edges of<br>the DCLK signal. During read, configuration, or<br>program operations, you can enable the EPCQ-A |

| For AS x4 mode, use this pin as an output signal<br>that serially transfers data out of the EPCQ-A<br>device to the FPGA during read or configuration<br>operations. The transition of the signal is at<br>falling edges of the DCLK signal.<br>During the extended quad input fast read<br>operation, this pin acts as an output signal pin<br>that serially transfers data out of the EPCQ-A<br>device to the FPGA. The data is shifted out at<br>falling edges of the DCLK signal.nCS1717InputnCS1717InputDCLK616616InputThe active low nCS input signal toggles at the<br>beginning and end of a valid operation. When this<br>signal is high, the device is deselected and the<br>DATA[3:0] pins are tri-stated. When this signal<br>is low, the device is enabled and is in active<br>mode. After power up, the EPCQ-A device<br>requires a falling edge on the nCS signal before<br>you begin any operation.DCLK616616Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DATA2    | _                                             | _                           | 3                          | 9                           | I/O   | For AS x4 mode, use this pin as an output signal<br>that serially transfers data out of the EPCQ-A<br>device to the FPGA during read or configuration<br>operations. The transition of the signal is at<br>falling edges of the DCLK signal.<br>During the extended quad input fast read<br>operation, this pin acts as an output signal pin<br>that serially transfers data out of the EPCQ-A<br>device to the FPGA. The data is shifted out at                                                                                                                                                                                                                                                                                                                                                           |

| DCLK616616InputThe FPGA provides the DCLK signal. This signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DATA3    | _                                             | _                           | 7                          | 1                           | I/O   | For AS x4 mode, use this pin as an output signal that serially transfers data out of the EPCQ-A device to the FPGA during read or configuration operations. The transition of the signal is at falling edges of the DCLK signal.<br>During the extended quad input fast read operation, this pin acts as an output signal pin that serially transfers data out of the EPCQ-A device to the FPGA. The data is shifted out at                                                                                                                                                                                                                                                                                                                                                                                |

| provides the timing for the serial interface. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nCS      | 1                                             | 7                           | 1                          | 7                           | Input | beginning and end of a valid operation. When this<br>signal is high, the device is deselected and the<br>DATA[3:0] pins are tri-stated. When this signal<br>is low, the device is enabled and is in active<br>mode. After power up, the EPCQ-A device<br>requires a falling edge on the nCS signal before                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DCLK     | 6                                             | 16                          | 6                          | 16                          | Input | provides the timing for the serial interface. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin Name        |                                              | AS x1 Pin-Out<br>Diagram                      |                                              | AS x4 Pin-Out<br>Diagram                      |        | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|----------------------------------------------|-----------------------------------------------|----------------------------------------------|-----------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Pin<br>Number<br>in 8-Pin<br>SOIC<br>Package | Pin<br>Number<br>in 16-Pin<br>SOIC<br>Package | Pin<br>Number<br>in 8-Pin<br>SOIC<br>Package | Pin<br>Number<br>in 16-Pin<br>SOIC<br>Package |        |                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 |                                              |                                               |                                              |                                               |        | latched to the EPCQ-A device at rising edges of<br>the DCLK signal. The data on the DATA[3:0]<br>pins change after the falling edge of the DCLK<br>signal and are latched in to the FPGA on the next<br>falling edge of the DCLK signal.                                                                                                                                                                          |

| nRESET          | _                                            | 3                                             | _                                            | 3                                             | Input  | Dedicated hardware reset pin. When it's driven<br>low for a minimum period of ~1 $\mu$ S, the EPCQ-A<br>device will terminate any external or internal<br>operations and return to its power-on state.<br>There is an internal pull-up resistor for the<br>dedicated nRESET pin on the SOIC-16 package. If<br>the reset function is not needed, you can connect<br>it to V <sub>CC</sub> or leave it unconnected. |

| V <sub>CC</sub> | 8                                            | 2                                             | 8                                            | 2                                             | Power  | Connect the power pins to a 3.3-V power supply.                                                                                                                                                                                                                                                                                                                                                                   |

| GND             | 4                                            | 10                                            | 4                                            | 10                                            | Ground | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                       |

# **1.5. Device Package and Ordering Code**

# 1.5.1. Package

The EPCQ4A, EPCQ16A, and EPCQ32A devices are available in 8-pin SOIC packages. The EPCQ64A and EPCQ128A devices are available in 16-pin SOIC packages.

# **1.5.2. Ordering Code**

#### Table 9. EPCQ-A Device Ordering Codes

| Device   | Ordering Code <sup>(3)</sup> |

|----------|------------------------------|

| EPCQ4A   | EPCQ4ASI8N                   |

| EPCQ16A  | EPCQ16ASI8N                  |

| EPCQ32A  | EPCQ32ASI8N                  |

| EPCQ64A  | EPCQ64ASI16N                 |

| EPCQ128A | EPCQ128ASI16N                |

$<sup>^{(3)}\,</sup>$  N indicates that the device is lead free.

# **1.6. Memory Array Organization**

#### Table 10. Supported Memory Array Organization in EPCQ-A Devices

| Details                                    | EPCQ4A                                | EPCQ16A                    | EPCQ32A                    | EPCQ64A                    | EPCQ128A                     |  |

|--------------------------------------------|---------------------------------------|----------------------------|----------------------------|----------------------------|------------------------------|--|

| Bytes                                      | 524,288 bytes<br>[4 megabits<br>(Mb)] | 2,097,152<br>bytes [16 Mb] | 4,194,304<br>bytes (32 Mb) | 8,388,608<br>bytes (64 Mb) | 16,777,216<br>bytes (128 Mb) |  |

| Number of sectors                          | 8                                     | 32                         | 64                         | 128                        | 256                          |  |

| Bytes per sector                           | 65,536 bytes [512 kilobits (Kb)]      |                            |                            |                            |                              |  |

| Total numbers of subsectors <sup>(4)</sup> | 128                                   | 512                        | 1,024                      | 2,048                      | 4,096                        |  |

| Bytes per subsector                        |                                       | 4                          | ,096 bytes (32 Kb          | )                          | •                            |  |

| Pages per sector                           |                                       |                            | 256                        |                            |                              |  |

| Total number of pages                      | 2,048                                 | 8,192                      | 16,384                     | 32,768                     | 65,536                       |  |

| Bytes per page                             | 256 bytes                             |                            |                            |                            |                              |  |

# 1.6.1. Address Range for EPCQ4A

#### Table 11. Address Range for Sectors 7..0 and Subsectors 127..0 in EPCQ4A Devices

| Sector | Subsector | Address Range (Byte | Addresses in HEX) |

|--------|-----------|---------------------|-------------------|

|        |           | Start               | End               |

| 7      | 127       | 7F000               | 7FFFF             |

|        | 126       | 7E000               | 7EFFF             |

|        |           |                     |                   |

|        | 114       | 72000               | 72FFF             |

|        | 113       | 71000               | 71FFF             |

|        | 112       | 70000               | 70FFF             |

| 6      | 111       | 6F000               | 6FFFF             |

|        | 110       | 6E000               | 6EFFF             |

|        |           |                     |                   |

|        | 98        | 62000               | 62FFF             |

|        | 97        | 61000               | 61FFF             |

|        | 96        | 60000               | 60FFF             |

| 1      | 31        | 1F000               | 1FFFF             |

|        | 30        | 1E000               | 1EFFF             |

|        |           |                     |                   |

|        |           |                     | continued         |

<sup>&</sup>lt;sup>(4)</sup> Every sector is further divided into 16 subsectors with 4 KB of memory. Therefore, there are 128 (8 x 16) subsectors for the EPCQ4A device, 512 (32 x 16) subsectors for the EPCQ16A device, 1,024 (64 x 16) subsectors for the EPCQ32A device, 2,048 (128 x 16) subsectors for the EPCQ64A device, and 4,096 (256 x 16) subsectors for the EPCQ128A device.

| Sector | Subsector | Address Range (Byte Addresses in HEX) |           |  |

|--------|-----------|---------------------------------------|-----------|--|

|        |           | Start                                 | End       |  |

|        | 18        | 12000                                 | 12FFF     |  |

|        | 17        | 11000                                 | 11FFF     |  |

|        | 16        | 10000                                 | 10FFF     |  |

| 0      | 15        | F000                                  | FFFF      |  |

|        | 14        | E000                                  | EFFF      |  |

|        |           |                                       |           |  |

|        | 2         | 2000                                  | 2FFF      |  |

|        | 1         | 1000                                  | 1FFF      |  |

|        | 0         | H'000000                              | H'0000FFF |  |

# 1.6.2. Address Range for EPCQ16A

#### Table 12. Address Range for Sectors 31..0 and Subsectors 511..0 in EPCQ16A Devices

| Sector | Subsector | Address Range (Byte | e Addresses in HEX) |

|--------|-----------|---------------------|---------------------|

|        |           | Start               | End                 |

| 31     | 511       | 1FF000              | 1FFFFF              |

|        | 510       | 1FE000              | 1FEFFF              |

|        |           |                     |                     |

|        | 498       | 1F2000              | 1F2FFF              |

|        | 497       | 1F1000              | 1F1FFF              |

|        | 496       | 1F0000              | 1F0FFF              |

| 30     | 495       | 1EF000              | 1EFFFF              |

|        | 494       | 1EE000              | 1EEFFF              |

|        |           |                     |                     |

|        | 482       | 1E2000              | 1E2FFF              |

|        | 481       | 1E1000              | 1E1FFF              |

|        | 480       | 1E0000              | 1E0FFF              |

| 1      | 31        | 1F000               | 1FFFF               |

|        | 30        | 1E000               | 1EFFF               |

|        |           |                     |                     |

|        | 18        | 12000               | 12FFF               |

|        | 17        | 11000               | 11FFF               |

|        | 16        | 10000               | 10FFF               |

| 0      | 15        | F000                | FFFF                |

|        | 14        | E000                | EFFF                |

|        |           |                     |                     |

|        |           |                     | continued           |

| Sector | Subsector | Address Range (Byte Addresses in HEX) |           |

|--------|-----------|---------------------------------------|-----------|

|        |           | Start                                 | End       |

|        | 2         | 2000                                  | 2FFF      |

|        | 1         | 1000                                  | 1FFF      |

|        | 0         | H'000000                              | H'0000FFF |

# 1.6.3. Address Range for EPCQ32A

## Table 13. Address Range for Sectors 63..0 and Subsectors 1023..0 in EPCQ32A Devices

| Sector | Subsector | Address Range (Byte | e Addresses in HEX) |

|--------|-----------|---------------------|---------------------|

|        |           | Start               | End                 |

| 63     | 1023      | 3FF000              | 3FFFFF              |

|        | 1022      | 3FE000              | 3FEFFF              |

|        |           |                     |                     |

|        | 1010      | 3F2000              | 3F2FFF              |

|        | 1009      | 3F1000              | 3F1FFF              |

|        | 1008      | 3F0000              | 3F0FFF              |

| 62     | 1007      | 3EF000              | 3EFFFF              |

|        | 1006      | 3EE000              | 3EEFFF              |

|        |           |                     |                     |

|        | 994       | 3E2000              | 3E2FFF              |

|        | 993       | 3E1000              | 3E1FFF              |

|        | 992       | 3E0000              | 3E0FFF              |

| 1      | 31        | 1F000               | 1FFFF               |

|        | 30        | 1E000               | 1EFFF               |

|        |           |                     |                     |

|        | 18        | 12000               | 12FFF               |

|        | 17        | 11000               | 11FFF               |

|        | 16        | 10000               | 10FFF               |

| 0      | 15        | F000                | FFFF                |

|        | 14        | E000                | EFFF                |

|        |           |                     |                     |

|        | 2         | 2000                | 2FFF                |

|        | 1         | 1000                | 1FFF                |

|        | 0         | H'0000000           | H'0000FFF           |

# 1.6.4. Address Range for EPCQ64A

# Table 14.Address Range for Sectors 127..0 and Subsectors 2047..0 in EPCQ64A<br/>Devices

| Sector | Subsector | Address Range (Byt | e Addresses in HEX) |

|--------|-----------|--------------------|---------------------|

|        |           | Start              | End                 |

| 127    | 2047      | 7FF000             | 7fffff              |

|        | 2046      | 7fe000             | 7fefff              |

|        |           |                    |                     |

|        | 2034      | 7F2000             | 7F2FFF              |

|        | 2033      | 7F1000             | 7F1FFF              |

|        | 2032      | 7F0000             | 7F0FFF              |

| 64     | 1039      | 40F000             | 40FFFF              |

|        | 1038      | 40E000             | 40EFFF              |

|        |           |                    |                     |

|        | 1026      | 402000             | 402FFF              |

|        | 1025      | 401000             | 401FFF              |

|        | 1024      | 400000             | 400FFF              |

| 63     | 1023      | 3FF000             | 3fffff              |

|        | 1022      | 3FE000             | 3fefff              |

|        |           |                    |                     |

|        | 1010      | 3F2000             | 3F2FFF              |

|        | 1009      | 3F1000             | 3F1FFF              |

|        | 1008      | 3F0000             | 3F0FFF              |

| 62     | 1007      | 3EF000             | 3effff              |

|        | 1006      | 3EE000             | 3eefff              |

|        |           |                    |                     |

|        | 994       | 3E2000             | 3E2FFF              |

|        | 993       | 3E1000             | 3E1FFF              |

|        | 992       | 3E0000             | 3E0FFF              |

| 1      | 31        | 1F000              | 1FFFF               |

|        | 30        | 1E000              | 1efff               |

|        |           |                    |                     |

|        | 18        | 12000              | 12FFF               |

|        | 17        | 11000              | 11FFF               |

|        | 16        | 10000              | 10FFF               |

| 0      | 15        | F000               | FFFF                |

|        | L         |                    | continued           |

| Sector | Subsector | Address Range (Byte Addresses in HEX) |           |  |

|--------|-----------|---------------------------------------|-----------|--|

|        |           | Start                                 | End       |  |

|        | 14        | E000                                  | EFFF      |  |

|        |           |                                       |           |  |

|        | 2         | 2000                                  | 2FFF      |  |

|        | 1         | 1000                                  | lfff      |  |

|        | 0         | Н'000000                              | H'0000FFF |  |

# 1.6.5. Address Range for EPCQ128A

# Table 15.Address Range for Sectors 255..0 and Subsectors 4095..0 in EPCQ128A<br/>Devices

| Sector | Subsector | Address Range (Byt | Address Range (Byte Addresses in HEX) |  |  |

|--------|-----------|--------------------|---------------------------------------|--|--|

|        |           | Start              | End                                   |  |  |

| 255    | 4095      | FFF000             | FFFFFF                                |  |  |

|        | 4094      | FFE000             | FFEFFF                                |  |  |

|        |           |                    |                                       |  |  |

|        | 4082      | FF2000             | FF2FFF                                |  |  |

|        | 4081      | FF1000             | FF1FFF                                |  |  |

|        | 4080      | FF0000             | FFOFFF                                |  |  |

| 254    | 4079      | FEF000             | FEFFFF                                |  |  |

|        | 4078      | FEE000             | FEEFFF                                |  |  |

|        |           |                    |                                       |  |  |

|        | 4066      | FE2000             | FE2FFF                                |  |  |

|        | 4065      | FE1000             | FE1FFF                                |  |  |

|        | 4064      | FE0000             | FEOFFF                                |  |  |

| 129    | 2079      | 81F000             | 81FFFF                                |  |  |

|        | 2078      | 81E000             | 81EFFF                                |  |  |

|        |           |                    |                                       |  |  |

|        | 2066      | 812000             | 812FFF                                |  |  |

|        | 2065      | 811000             | 811FFF                                |  |  |

|        | 2064      | 810000             | 810FFF                                |  |  |

| 128    | 2063      | 80F000             | 80FFFF                                |  |  |

|        | 2062      | 80E000             | 80EFFF                                |  |  |

|        |           |                    |                                       |  |  |

|        | 2050      | 802000             | 802FFF                                |  |  |

|        | 2049      | 801000             | 801FFF                                |  |  |

| Sector | Subsector | Address Range (Byte Addresses in HEX) |        |  |

|--------|-----------|---------------------------------------|--------|--|

|        |           | Start                                 | End    |  |

|        | 2048      | 800000                                | 800FFF |  |

| 127    | 2047      | 7 <b>FF</b> 000                       | 7FFFFF |  |

|        | 2046      | 7fe000                                | 7feff  |  |

|        |           |                                       |        |  |

|        | 2034      | 7F2000                                | 7F2FFF |  |

|        | 2033      | 7F1000                                | 7F1FFF |  |

|        | 2032      | 7F0000                                | 7F0FFF |  |

| 64     | 1039      | 40F000                                | 40FFFF |  |

|        | 1038      | 40E000                                | 40EFFF |  |

|        |           |                                       |        |  |

|        | 1026      | 402000                                | 402FFF |  |

|        | 1025      | 401000                                | 401FFF |  |

|        | 1024      | 400000                                | 400FFF |  |

| 63     | 1023      | 3FF000                                | 3fffff |  |

|        | 1022      | 3FE000                                | 3FEFFF |  |

|        |           |                                       |        |  |

|        | 1010      | 3F2000                                | 3F2FFF |  |

|        | 1009      | 3F1000                                | 3F1FFF |  |

|        | 1008      | 3F0000                                | 3F0FFF |  |

| 62     | 1007      | 3EF000                                | 3effff |  |

|        | 1006      | 3EE000                                | 3eefff |  |

|        |           |                                       |        |  |

|        | 994       | 3E2000                                | 3E2FFF |  |

|        | 993       | 3E1000                                | 3E1FFF |  |

|        | 992       | 3E0000                                | 3E0FFF |  |

| 1      | 31        | 1F000                                 | 1FFFF  |  |

|        | 30        | 1E000                                 | lefff  |  |

|        |           |                                       |        |  |

|        | 18        | 12000                                 | 12FFF  |  |

|        | 17        | 11000                                 | 11FFF  |  |

|        | 16        | 10000                                 | 10FFF  |  |

| 0      | 15        | F000                                  | FFFF   |  |

|        | 14        | E000                                  | EFFF   |  |

|        |           | •                                     |        |  |

| Sector | Subsector | Address Range (Byte Addresses in HEX) |           |  |

|--------|-----------|---------------------------------------|-----------|--|

|        |           | Start                                 | End       |  |

|        | 2         | 2000                                  | 2FFF      |  |

|        | 1         | 1000                                  | lfff      |  |

|        | 0         | н'000000                              | H'0000FFF |  |

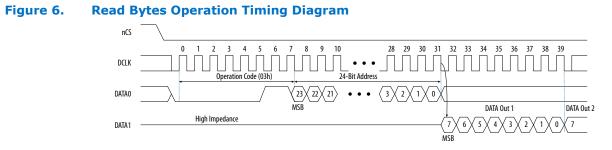

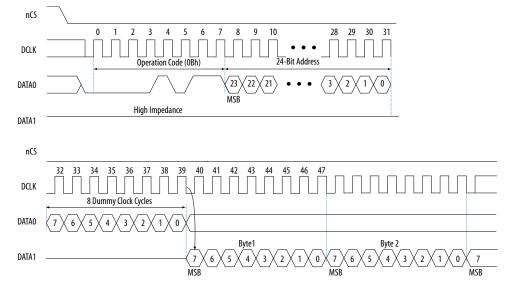

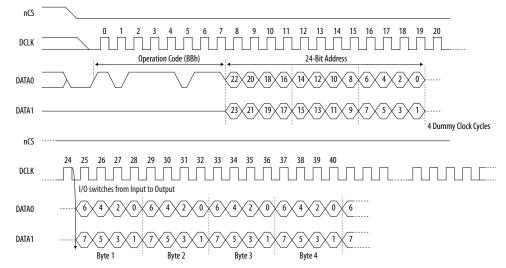

# **1.7. Memory Operations**

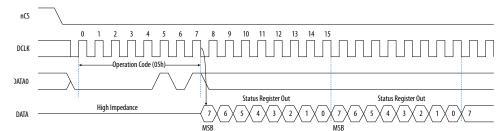

This section describes the operations that you can use to access the memory in EPCQ-A devices. When performing the operation, addresses and data are shifted in and out of the device serially, with the MSB first.

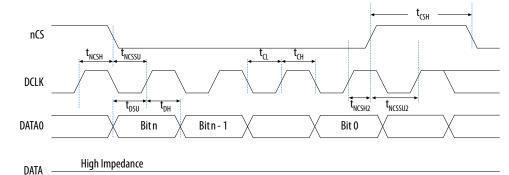

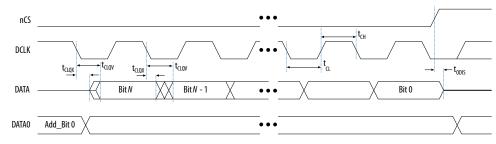

## **1.7.1. Timing Requirements**

When the active low chip select (nCS) signal is driven low, shift in the operation code into the EPCQ-A device using theDATA0 pin. Each operation code bit is latched into the EPCQ-A device at rising edges of the DCLK signal.

While executing an operation, shift in the desired operation code, followed by the address or data bytes. See related information for more information about the address and data bytes. The device must drive the nCS pin high after the last bit of the operation sequence is shifted in.

For read operations, the data read is shifted out on the DATA[3:0] pins. You can drive the nCS pin high when any bit of the data is shifted out.

For write and erase operations, drive the nCS pin high at a byte boundary, that is in a multiple of eight clock pulses. Otherwise, the operation is rejected and not executed.

All attempts to access the memory contents while a write or erase cycle is in progress are rejected, and the write or erase cycle continues unaffected.

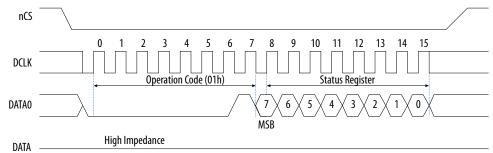

# **1.8. Status Register**

| Table 16. | Status | Register | Bits |

|-----------|--------|----------|------|

|-----------|--------|----------|------|

| Bit | R/W       | Default<br>Value | Name                   | Value                                                                                                                                               | Description                                                                                      |  |  |  |

|-----|-----------|------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| 7   | R/W       | 0 <sup>(5)</sup> |                        | Reserved                                                                                                                                            |                                                                                                  |  |  |  |

| 6   | R/W       | 0 <sup>(5)</sup> | Reserved               |                                                                                                                                                     |                                                                                                  |  |  |  |

| 5   | R/W       | 0                | TB (Top/Bottom<br>Bit) | <ul> <li>1=Protected area starts from the bottom of the memory array.</li> <li>0=Protected area starts from the top of the memory array.</li> </ul> | Determine that the<br>protected area starts<br>from the top or<br>bottom of the memory<br>array. |  |  |  |