# CMOS Low Voltage, 2 $\Omega$ SPST Switches

### **Data Sheet**

# ADG701L/ADG702L

### **FEATURES**

1.8 V to 5.5 V single supply 2 Ω (typical) on resistance Low on resistance flatness Guaranteed leakage specifications up to 85°C -3 dB bandwidth > 200 MHz Rail-to-rail operation Fast switching times tor 18 ns tor 12 ns Typical power consumption < 0.01 μW Transistor/Transistor Logic (TTL)/CMOS-compatible

#### **APPLICATIONS**

Battery-powered systems Communication systems Sample-and-hold systems Audio signal routing Video switching Mechanical reed relay replacement

#### **GENERAL DESCRIPTION**

The ADG701L/ADG702L are monolithic CMOS SPST switches. These switches are designed using an advanced submicron process that provides low power dissipation yet also offers high switching speed, low on resistance, and low leakage currents. In addition, –3 dB bandwidths greater than 200 MHz can be achieved.

The ADG701L/ADG702L can operate from a single 1.8 V to 5.5 V supply, making it ideal for use in battery-powered instruments and with the new generation of DACs and ADCs from Analog Devices, Inc.

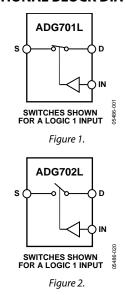

Figure 1 and Figure 2 show that with a logic input of 1, the switch of the ADG701L is closed while the switch of the ADG702L is open. Each switch conducts equally well in both directions when on.

The ADG701L/ADG702L are packaged as 5-lead SOT-23, 6-lead SOT-23, and 8-lead MSOP.

### FUNCTIONAL BLOCK DIAGRAMS

### **PRODUCT HIGHLIGHTS**

- 1.8 V to 5.5 V Single-Supply Operation. The ADG701L/ ADG702L offer high performance, including low on resistance and fast switching times. The ADG701L/ ADG702L are fully specified and guaranteed with 3 V and 5 V supply rails.

- $\begin{array}{ll} \mbox{2.} & \mbox{Very Low $R_{ON}$} (3 \ \Omega \ Maximum \ at 5 \ V, 5 \ \Omega \ Maximum \ at 3 \ V). \\ & \mbox{At 1.8 V operation, on resistance ($R_{ON}$) is typically 40 $\Omega$ \\ & \mbox{over the temperature range.} \end{array}$

- 3. On Resistance Flatness,  $R_{FLAT(ON)}$  (1  $\Omega$  Maximum).

- 4. -3 dB Bandwidth > 200 MHz.

- 5. Low Power Dissipation. CMOS construction ensures low power dissipation.

- 6. Fast ton/toff.

#### Rev. A

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### **TABLE OF CONTENTS**

| Features1                                    |

|----------------------------------------------|

| Applications                                 |

| General Description                          |

| Functional Block Diagrams1                   |

| Product Highlights 1                         |

| Revision History 2                           |

| Specifications                               |

| Absolute Maximum Ratings 5                   |

| ESD Caution                                  |

| Pin Configurations and Function Descriptions |

### **REVISION HISTORY**

| 1/2020—Rev. 0 to Rev. A           |    |

|-----------------------------------|----|

| Changes to Table 1                |    |

| Reformatted Test Circuits Section |    |

| Changes to Bandwidth Section      | 10 |

| Updated Outline Dimensions        | 11 |

| Changes to Ordering Guide         | 12 |

11/2006—Revision 0: Initial Version

| Typical Performance Characteristics | 7  |

|-------------------------------------|----|

| Test Circuits                       | 8  |

| Terminology                         | 9  |

| Applications Information            | 10 |

| Supply Voltages                     | 10 |

| Bandwidth                           | 10 |

| Off Isolation                       | 10 |

| Outline Dimensions                  | 11 |

| Ordering Guide                      | 12 |

### **SPECIFICATIONS**

$V_{DD}$  = 5 V ± 10% and GND = 0 V. Temperature range for the B version is -40°C to +85°C, unless otherwise noted.

#### Table 1.

|                                                          | B Version |                        |         |                                                                                                            |

|----------------------------------------------------------|-----------|------------------------|---------|------------------------------------------------------------------------------------------------------------|

| Parameter                                                | +25°C     | –40°C to +85°C         | Unit    | Test Conditions/Comments                                                                                   |

| ANALOG SWITCH                                            |           |                        |         |                                                                                                            |

| Analog Signal Range                                      |           | 0 V to V <sub>DD</sub> | V       |                                                                                                            |

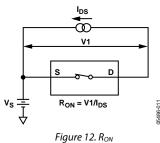

| R <sub>on</sub>                                          | 2         |                        | Ωtyp    | Source Voltage (V <sub>s</sub> ) = 0 V to $V_{DD}$ and source off leakage = -10 mA, see Figure 12          |

|                                                          | 3         | 4                      | Ωmax    |                                                                                                            |

| R <sub>FLAT</sub> (ON)                                   | 0.5       |                        | Ωtyp    | $V_s = 0 V$ to $V_{DD}$ and source current ( $I_s$ ) = -10 mA                                              |

|                                                          |           | 1.0                    | Ωmax    |                                                                                                            |

| LEAKAGE CURRENTS                                         |           |                        |         | $V_{DD} = 5.5 V$                                                                                           |

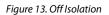

| Source Off Leakage, $I_S$ (Off)                          | ±0.01     |                        | nA typ  | $V_{\text{S}}$ = 4.5 V/1 V and drain voltage (V_D) = 1 V/4.5 V, see Figure 14                              |

|                                                          | ±0.25     | ±0.35                  | nA max  |                                                                                                            |

| Drain Off Leakage, I <sub>D</sub> (Off)                  | ±0.01     |                        | nA typ  | $V_s = 4.5 \text{ V/1 V}$ and $V_D = 1 \text{ V/4.5 V}$ , see Figure 14                                    |

|                                                          | ±0.25     | ±0.35                  | nA max  |                                                                                                            |

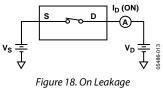

| Channel On Leakage, I <sub>D</sub> , I <sub>S</sub> (On) | ±0.01     |                        | nA typ  | $V_s = V_D = 1 V \text{ or } 4.5 V$ , see Figure 18                                                        |

|                                                          | ±0.25     | ±0.35                  | nA max  |                                                                                                            |

| DIGITAL INPUTS                                           |           |                        |         |                                                                                                            |

| Input High Voltage, V <sub>INH</sub>                     |           | 2.4                    | V min   |                                                                                                            |

| Input Low Voltage, VINL                                  |           | 0.8                    | V max   |                                                                                                            |

| Input Current                                            |           |                        |         |                                                                                                            |

| IINL OR INH                                              | 0.005     |                        | μA typ  | Digital input voltage $(V_{IN}) = V_{INL}$ or $V_{INH}$                                                    |

|                                                          |           | ±0.1                   | µA max  |                                                                                                            |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                     |           |                        |         |                                                                                                            |

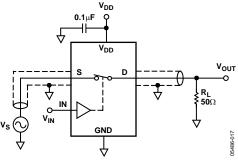

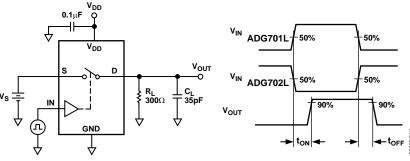

| t <sub>on</sub>                                          | 12        |                        | ns typ  | Load resistance (R <sub>L</sub> ) = 300 $\Omega$ and load capacitance (C <sub>LOAD</sub> ) = 35 pF         |

|                                                          |           | 18                     | ns max  | $V_s = 3 V$ , see Figure 16                                                                                |

| t <sub>OFF</sub>                                         | 8         |                        | ns typ  | $R_L = 300 \Omega$ and $C_L = 35 pF$                                                                       |

|                                                          |           | 12                     | ns max  | $V_s = 3 V$ , see Figure 16                                                                                |

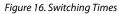

| Charge Injection                                         | 5         |                        | pC typ  | $V_{\text{S}}$ = 2 V and source resistance (R_{\text{S}}) = 0 \ \Omega, C_{\text{L}} = 1 nF, see Figure 17 |

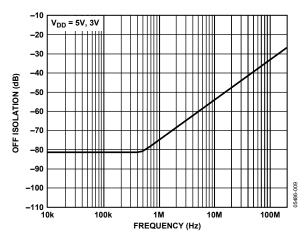

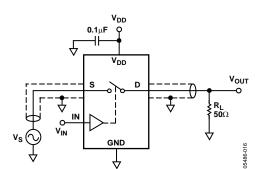

| Off Isolation                                            | -55       |                        | dB typ  | $R_{\text{L}}$ = 50 $\Omega,$ $C_{\text{L}}$ = 5 pF, and f = 10 MHz                                        |

|                                                          | -75       |                        | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , and $f = 1 MHz$ , see Figure 13                                         |

| Bandwidth –3 dB                                          | 200       |                        | MHz typ | $R_L=50~\Omega$ and $C_L=5~pF,$ see Figure 15                                                              |

| Source Capacitance (C <sub>s</sub> ) (Off)               | 17        |                        | pF typ  |                                                                                                            |

| Drain Capacitance (C <sub>D</sub> ) (Off)                | 17        |                        | pF typ  |                                                                                                            |

| C <sub>D</sub> , C <sub>s</sub> (On)                     | 38        |                        | pF typ  |                                                                                                            |

| POWER REQUIREMENTS                                       |           |                        |         | $V_{DD} = 5.5 V$                                                                                           |

| Supply Current (IDD)                                     | 0.001     |                        | μA typ  | Digital inputs = 0 V or 5 V                                                                                |

|                                                          |           | 1.0                    | μA max  |                                                                                                            |

<sup>1</sup> Guaranteed by design, not subject to production test.

$V_{DD}$  = 3 V ± 10% and the GND pin = 0 V. Temperature range for the B version is -40°C to +85°C, unless otherwise noted.

#### Table 2.

|                                                         |       | B Version              |         |                                                                                    |  |

|---------------------------------------------------------|-------|------------------------|---------|------------------------------------------------------------------------------------|--|

| Parameter                                               | +25°C | –40°C to +85°C         | Unit    | Test Conditions/Comments                                                           |  |

| ANALOG SWITCH                                           |       |                        |         |                                                                                    |  |

| Analog Signal Range                                     |       | 0 V to V <sub>DD</sub> | V       |                                                                                    |  |

| Ron                                                     | 3.5   |                        | Ωtyp    | $V_{\text{S}} = 0$ V to $V_{\text{DD}}$ and $I_{\text{S}} = -10$ mA, see Figure 12 |  |

|                                                         | 5     | 6                      | Ωmax    |                                                                                    |  |

| R <sub>FLAT(ON)</sub>                                   | 1.5   |                        | Ωtyp    | $V_s = 0$ V to $V_{DD}$ and $I_s = -10$ mA                                         |  |

| LEAKAGE CURRENTS                                        |       |                        |         | V <sub>DD</sub> = 3.3 V                                                            |  |

| Source Off Leakage Is (Off)                             | ±0.01 |                        | nA typ  | $V_S = 3 V/1 V$ and $V_D = 1 V/3 V$ , see Figure 14                                |  |

|                                                         | ±0.25 | ±0.35                  | nA max  |                                                                                    |  |

| Drain Off Leakage I <sub>D</sub> (Off)                  | ±0.01 |                        | nA typ  | $V_S = 3 V/1 V$ and $V_D = 1 V/3 V$ , see Figure 14                                |  |

|                                                         | ±0.25 | ±0.35                  | nA max  |                                                                                    |  |

| Channel On Leakage I <sub>D</sub> , I <sub>S</sub> (On) | ±0.01 |                        | nA typ  | $V_S = V_D = 1 V \text{ or } 3 V$ , see Figure 18                                  |  |

|                                                         | ±0.25 | ±0.35                  | nA max  |                                                                                    |  |

| DIGITAL INPUTS                                          | İ     |                        |         |                                                                                    |  |

| Input High Voltage, V <sub>INH</sub>                    |       | 2.0                    | V min   |                                                                                    |  |

| Input Low Voltage, V <sub>INL</sub>                     |       | 0.4                    | V max   |                                                                                    |  |

| Input Current                                           |       |                        |         |                                                                                    |  |

| I <sub>INL</sub> or I <sub>INH</sub>                    | 0.005 |                        | μA typ  | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                             |  |

|                                                         |       | ±0.1                   | μA max  |                                                                                    |  |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                    |       |                        |         |                                                                                    |  |

| t <sub>on</sub>                                         | 14    |                        | ns typ  | $R_L = 300 \Omega$ and $C_L = 35 pF$                                               |  |

|                                                         |       | 20                     | ns max  | $V_s = 2 V$ , see Figure 16                                                        |  |

| t <sub>OFF</sub>                                        | 8     |                        | ns typ  | $R_L = 300 \Omega$ and $C_L = 35 pF$                                               |  |

|                                                         |       | 13                     | ns max  | $V_s = 2 V$ , see Figure 16                                                        |  |

| Charge Injection                                        | 4     |                        | pC typ  | $V_s = 1.5 V$ , $R_s = 0 \Omega$ and $C_L = 1 nF$ , see Figure 17                  |  |

| Off Isolation                                           | -55   |                        | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , and $f = 10 MHz$                                |  |

|                                                         | -75   |                        | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , and $f = 1 MHz$ , see Figure 13                 |  |

| Bandwidth –3 dB                                         | 200   |                        | MHz typ | $R_L = 50 \Omega$ and $C_L = 5 pF$ , see Figure 15                                 |  |

| Cs (Off)                                                | 17    |                        | pF typ  |                                                                                    |  |

| C <sub>D</sub> (Off)                                    | 17    |                        | pF typ  |                                                                                    |  |

| C <sub>D</sub> , C <sub>s</sub> (On)                    | 38    |                        | pF typ  |                                                                                    |  |

| POWER REQUIREMENTS                                      | İ     |                        |         | V <sub>DD</sub> = 3.3 V                                                            |  |

| I <sub>DD</sub>                                         | 0.001 |                        | μA typ  | Digital inputs = 0 V or 3 V                                                        |  |

|                                                         |       | 1.0                    | µA max  |                                                                                    |  |

<sup>1</sup> Guaranteed by design, not subject to production test.

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                            | Rating                                                             |

|--------------------------------------|--------------------------------------------------------------------|

| V <sub>DD</sub> to GND Pin           | –0.3 V to +7 V                                                     |

| Analog, Digital Inputs <sup>1</sup>  | -0.3 V to V <sub>DD</sub> + 0.3 V or 30 mA, whichever occurs first |

| Continuous Current, S or D           | 30 mA                                                              |

| Peak Current, S or D                 | 100 mA, pulsed at 1 ms,<br>10% duty cycle maximum                  |

| Operating Temperature Range          |                                                                    |

| Industrial (B Version)               | -40°C to +85°C                                                     |

| Storage Temperature Range            | –65°C to +150°C                                                    |

| Junction Temperature                 | 150°C                                                              |

| MSOP Package, Power<br>Dissipation   | 315 mW                                                             |

| $\theta_{JA}$ Thermal Impedance      | 206°C/W                                                            |

| $\theta_{JC}$ Thermal Impedance      | 44°C/W                                                             |

| SOT-23 Package, Power<br>Dissipation | 282 mW                                                             |

| $\theta_{JA}$ Thermal Impedance      | 229.6°C/W                                                          |

| $\theta_{JC}$ Thermal Impedance      | 91.99°C/W                                                          |

| Lead Temperature, Soldering          |                                                                    |

| Vapor Phase (60 sec)                 | 215°C                                                              |

| Infrared (15 sec)                    | 220°C                                                              |

| Lead-free Reflow Soldering           |                                                                    |

| Peak Temperature                     | 260 (+0/–5)°C                                                      |

| Time at Peak Temperature             | 10 sec to 40 sec                                                   |

| ESD                                  | 2 kV                                                               |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>1</sup> Overvoltages at IN, S, or D are clamped by internal diodes. Current should be limited to the maximum ratings given.

### **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

Figure 3. 8-Lead MSOP Pin Configuration

Figure 4. 6-Lead SOT-23 Pin Configuration

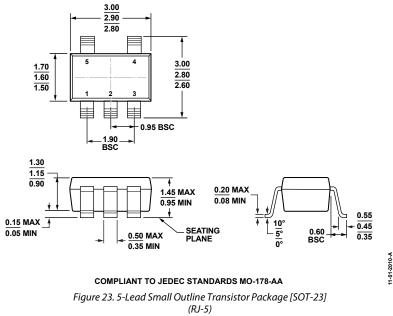

Figure 5. 5-Lead SOT-23 Pin Configuration

| Table 4. Pin Function Descriptions |               |                |                 |                                             |  |

|------------------------------------|---------------|----------------|-----------------|---------------------------------------------|--|

|                                    | Pin Number    | Pin Number     |                 |                                             |  |

| 8-Lead MSOP                        | 6-lead SOT-23 | 5-lead SOT-23  | Mnemonic        | Description                                 |  |

| 1                                  | 1             | 1              | D               | Drain Terminal. Can be an input or output.  |  |

| 2, 3, 5                            | 5             | Not applicable | NC              | No Connect.                                 |  |

| 4                                  | 6             | 5              | V <sub>DD</sub> | Most Positive Power Supply Potential.       |  |

| 6                                  | 4             | 4              | IN              | Logic Control Input.                        |  |

| 7                                  | 3             | 3              | GND             | Ground (0 V) Reference.                     |  |

| 8                                  | 2             | 2              | S               | Source Terminal. May be an input or output. |  |

Table 5. Truth Table

| ADG701L In | ADG702L In | Switch Condition |  |  |  |

|------------|------------|------------------|--|--|--|

| 0          | 1          | Off              |  |  |  |

| _1         | 0          | On               |  |  |  |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

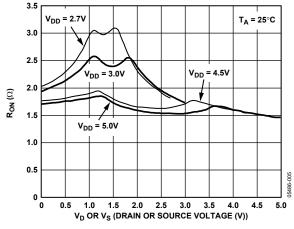

Figure 6.  $R_{ON}$  as a Function of  $V_D$  ( $V_S$ ) Single Supplies

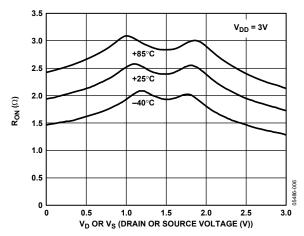

Figure 7.  $R_{ON}$  as a Function of  $V_D$  (V<sub>s</sub>) for Different Temperatures  $V_{DD} = 3 V$

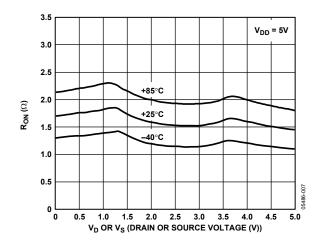

Figure 8.  $R_{ON}$  as a Function of  $V_D$  (V<sub>s</sub>) for Different Temperatures  $V_{DD} = 5 V$

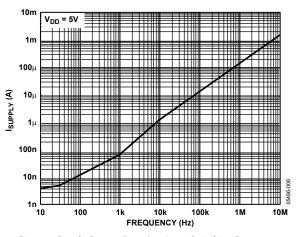

Figure 9. Supply Current (ISUPPLY) vs. Input Switching Frequency

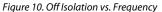

Figure 11. Bandwidth

### **TEST CIRCUITS**

Figure 14. Off Leakage

### TERMINOLOGY

Ron

Ohmic resistance between D and S.

#### R<sub>FLAT(ON)</sub>

Flatness is defined as the difference between the maximum and minimum value of on resistance as measured over the specified analog signal range.

Is (OFF) Source leakage current with the switch off.

I<sub>D</sub> (OFF) Drain leakage current with the switch off.

I<sub>D</sub>, I<sub>s</sub> (ON) Channel leakage current with the switch on.

$\mathbf{V}_{D}$  ( $\mathbf{V}_{S}$ ) Analog voltage on Terminal D and Terminal S.

Cs (OFF) Off switch source capacitance.

C<sub>D</sub> (OFF) Off switch drain capacitance.

C<sub>D</sub>, C<sub>s</sub> (ON) On switch capacitance.

## ADG701L/ADG702L

#### ton

Delay between applying the digital control input and the output switching on. See Figure 16.

toff

Delay between applying the digital control input and the output switching off.

**Off Isolation** A measure of unwanted signal coupling through an off switch.

#### **Charge Injection**

A measure of the glitch impulse transferred from the digital input to the analog output during switching.

**Bandwidth** The frequency at which the output is attenuated by -3 dB.

**On Response** The frequency response of the on switch.

#### On Loss

The voltage drop across the on switch, seen in Figure 11 as the number of decibels the signal is away from 0 dB at very low frequencies.

### **APPLICATIONS INFORMATION**

The ADG701L/ADG702L belong to the Analog Devices new family of CMOS switches. This series of general-purpose switches have improved switching times, lower  $R_{ON}$ , higher bandwidth, low power consumption, and low leakage currents.

#### SUPPLY VOLTAGES

Functionality of the ADG701L/ADG702L extends from 1.8 V to 5.5 V single supply, making the parts ideal for battery-powered instruments where power, efficiency, and performance are important design parameters.

It is important to note that the supply voltage affects the input signal range, the on resistance, and the switching times of the part. The effects of the power supplies can be clearly seen in the Typical Performance Characteristics section and the Specifications section.

For  $V_{\text{DD}}$  = 1.8 V operation,  $R_{\text{ON}}$  is typically 40  $\Omega$  over the temperature range.

### BANDWIDTH

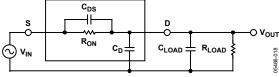

Figure 19 illustrates the parasitic components that affect the ac performance of CMOS switches (a box surrounds the switch). Additional external capacitances further degrade some performance. These capacitances affect feedthrough, crosstalk, and system bandwidth.

Figure 19. Switch Represented by Equivalent Parasitic Components

The transfer function that describes the equivalent diagram of the switch (see Figure 19) is of the form A(s), as shown in the following equation:

$$A(s) = R_T \left( \frac{s(R_{ON}C_{DS}) + 1}{s(R_{ON}C_TR_T) + 1} \right)$$

and calculate the total capacitance,  $C_T$ , with the following equation:

$C_T = C_{LOAD} + C_D + C_{DS}$

where C<sub>DS</sub> is the drain/source capacitance.

The signal transfer characteristic is dependent on the switch channel capacitance,  $C_{DS}$ . This capacitance creates a frequency zero in the numerator of the transfer function, A(s). Because the switch on resistance is small, this zero usually occurs at high frequencies. The bandwidth is a function of the switch output capacitance combined with  $C_{DS}$  and the load capacitance. The frequency pole corresponding to these capacitances appears in the denominator of A(s).

The dominant effect of the output capacitance,  $C_D$ , causes the pole breakpoint frequency to occur first. In order to maximize bandwidth, a switch must have a low input and output capacitance and low on resistance. The on response versus frequency for the ADG701L/ADG702L is shown in Figure 11.

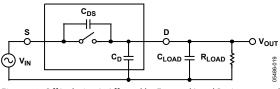

#### **OFF ISOLATION**

Off isolation is a measure of the input signal coupled through an off switch to the switch output. The capacitance,  $C_{DS}$ , couples the input signal to the output load when the switch is off (see Figure 20).

Figure 20. Off Isolation Is Affected by External Load Resistance and Capacitance

The larger the value of  $C_{DS}$ , the larger the values of feedthrough produced. Figure 10 illustrates the drop in off isolation as a function of frequency. From dc to roughly 1 MHz, the switch shows better than -75 dB isolation. Up to frequencies of 10 MHz, the off isolation remains better than -55 dB. As the frequency increases, more and more of the input signal is coupled through to the output. Off isolation can be maximized by choosing a switch with the smallest  $C_{DS}$  possible. The values of load resistance and capacitance also affect off isolation, as they contribute to the coefficients of the poles and zeros in the transfer function of the switch when open.

$$A(s) = R_T \left( \frac{s(R_{LOAD}C_{DS}) + 1}{s(R_{LOAD})(C_T) + 1} \right)$$

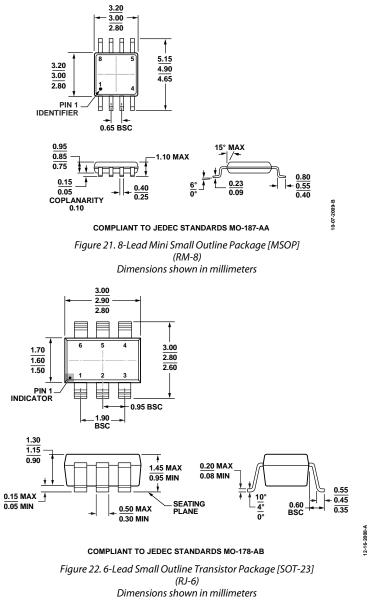

### **OUTLINE DIMENSIONS**

Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package Option | Marking Code <sup>2</sup> |

|--------------------|-------------------|--------------------------------------------------|----------------|---------------------------|

| ADG701LBRJZ-500RL7 | -40°C to +85°C    | 5-Lead Small Outline Transistor Package [SOT-23] | RJ-5           | S10                       |

| ADG701LBRJZ-REEL7  | -40°C to +85°C    | 5-Lead Small Outline Transistor Package [SOT-23] | RJ-5           | S10                       |

| ADG701LBRMZ        | -40°C to +85°C    | 8-Lead Mini Small Outline Package [MSOP]         | RM-8           | S10                       |

| ADG701LBRMZ-REEL7  | -40°C to +85°C    | 8-Lead Mini Small Outline Package [MSOP]         | RM-8           | S10                       |

| ADG701LBRTZ-REEL7  | -40°C to +85°C    | 6-Lead Small Outline Transistor Package [SOT-23] | RJ-6           | S10                       |

| ADG702LBRMZ        | -40°C to +85°C    | 8-Lead Mini Small Outline Package [MSOP]         | RM-8           | S11                       |

| ADG702LBRTZ-REEL7  | -40°C to +85°C    | 6-Lead Small Outline Transistor Package [SOT-23] | RJ-6           | S11                       |

<sup>1</sup> Z = RoHS Compliant Part.

<sup>2</sup> Due to package size limitations, these three characters represent the part number.

©2006–2020 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D05486-1/20(A)

www.analog.com