| Parameter                                 | Rating | Units |

|-------------------------------------------|--------|-------|

| Drain-to-Source Voltage - V <sub>DS</sub> | 350    | V     |

| Max On-Resistance - R <sub>DS(on)</sub>   | 14     | Ω     |

| Max Power                                 | 2.5    | W     |

#### **Features**

- 350V Drain-to-Source Voltage

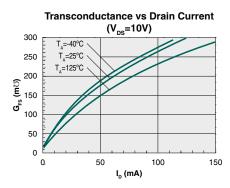

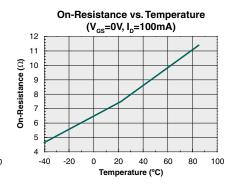

- Depletion Mode Device Offers Low R<sub>DS(on)</sub> at Cold Temperatures

- Low On-resistance: 8Ω (Typical) @ 25°C

- Low V<sub>GS(off)</sub> Voltage: -2.0V to -3.6V

- High Input Impedance

- · Low Input and Output Leakage

- Small Package Size SOT-223

- PC Card (PCMCIA) Compatible

- PCB Space and Cost Savings

### **Applications**

- Support Component for LITELINK™

Data Access Arrangement (DAA)

- Telecommunications

- Normally On Switches

- · Ignition Modules

- Converters

- Security

- Power Supplies

### **Description**

The CPC5602 is an N-channel depletion mode Field Effect Transistor (FET) that utilizes IXYS Integrated Circuits Division's proprietary third generation vertical DMOS process. The third generation process realizes world class, high voltage MOSFET performance in an economical silicon gate process. The vertical DMOS process yields a highly reliable device, particularly in difficult application environments such as telecommunications, security, and power supplies.

One of the primary applications for the CPC5602 is as a linear regulator/hook switch for the LITELINK family of Data Access Arrangements (DAA) Devices CPC5620A, CPC5621A, and CPC5622A.

The CPC5602 has a typical on-resistance of  $8\Omega$ , a drain-to-source voltage of 350V, and is available in an SOT-223 package. As with all MOS devices, the FET structure prevents thermal runaway and thermal-induced secondary breakdown.

### **Ordering Information**

| Part #                                                                                          | Description                                                                                                                    |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| CPC5602C                                                                                        | N-Channel Depletion Mode FET, SOT-223 Pkg.<br>Cut-Tape, Available in Quantities of 200, 400,<br>600, and 800 Only (see Note 1) |  |  |

| CPC5602CTR                                                                                      | N-Channel Depletion Mode FET, SOT-223 Pkg.<br>Tape and Reel (1000/Reel)                                                        |  |  |

| Note 1: Orders for 1000 or greater must be for the "CTR" part option and in increments of 1000. |                                                                                                                                |  |  |

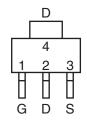

# **Package Pinout**

| Pin Number | Name   |

|------------|--------|

| 1          | GATE   |

| 2          | DRAIN  |

| 3          | SOURCE |

| 4          | DRAIN  |

## Absolute Maximum Ratings @ 25°C

| Parameter                                  | Ratings     | Units |

|--------------------------------------------|-------------|-------|

| Drain-to-Source Voltage (V <sub>DS</sub> ) | 350         | V     |

| Gate-to-Source Voltage (V <sub>GS</sub> )  | ±20         | V     |

| Total Package Dissipation                  | 2.5         | W     |

| Operational Temperature                    | -40 to +85  | °C    |

| Storage Temperature                        | -40 to +125 | °C    |

Absolute Maximum Ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at conditions beyond those indicated in the operational sections of this data sheet is not implied.

# **Electrical Characteristics @25°C (Unless Otherwise Specified)**

| Parameter                       | Symbol               | Conditions                                    | Min  | Тур   | Max | Units |

|---------------------------------|----------------------|-----------------------------------------------|------|-------|-----|-------|

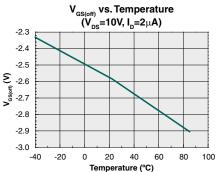

| Gate-to-Source Off Voltage      | V <sub>GS(off)</sub> | $I_D = 2\mu A, V_{DS} = 10V, V_{DS} = 100V$   | -3.6 | -2.62 | -2  | V     |

| Drain-to-Source Leakage Current | ı                    | $V_{GS} = -5V, V_{DS} = 190V$                 | -    | -     | 20  | nA    |

| Brain to Gource Leakage Garrent | <sup>I</sup> DS(off) | $V_{GS} = -5V, V_{DS} = 350V$                 | -    | -     | 1   | μΑ    |

| Drain Current                   | 1                    | $V_{GS}$ = -2.7V, $V_{DS}$ =5V, $V_{DS}$ =50V | -    | -     | 5   | mA    |

|                                 | 'D                   | V <sub>GS</sub> = -0.57V, V <sub>DS</sub> =5V | 130  | -     | -   | mA    |

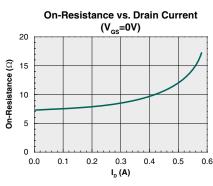

| On-Resistance                   | R <sub>DS(on)</sub>  | $V_{GS}$ = -0.35V, $I_{DS}$ =50mA             | -    | 8     | 14  | Ω     |

| Gate Leakage Current            | I <sub>GSS</sub>     | V <sub>GS</sub> =10V, V <sub>GS</sub> =-10V   | -    | -     | 0.1 | μΑ    |

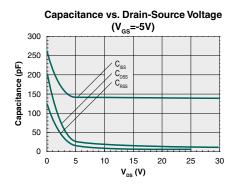

| Gate Capacitance                | C <sub>ISS</sub>     | $V_{DS} = V_{GS} = 0V$                        | -    | -     | 300 | pF    |

### **Thermal Characteristics**

| Parameter          | Symbol          | Conditions | Min | Тур | Max | Units |

|--------------------|-----------------|------------|-----|-----|-----|-------|

| Thermal Resistance | $R_{\theta JC}$ | -          |     | -   | 14  | °C/W  |

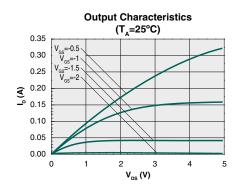

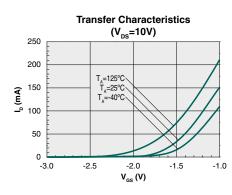

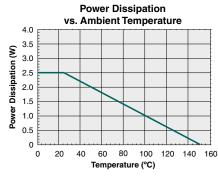

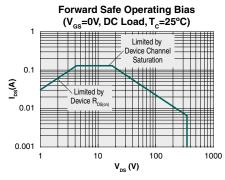

#### **PERFORMANCE DATA\***

<sup>\*</sup>The Performance data shown in the graphs above is typical of device performance. For guaranteed parameters not indicated in the written specifications, please contact our application department.

### **Manufacturing Information**

### **Moisture Sensitivity**

All plastic encapsulated semiconductor packages are susceptible to moisture ingression. IXYS Integrated Circuits Division classified all of its plastic encapsulated devices for moisture sensitivity according to the latest version of the joint industry standard, IPC/JEDEC J-STD-020, in force at the time of product evaluation. We test all of our products to the maximum conditions set forth in the standard, and guarantee proper operation of our devices when handled according to the limitations and information in that standard as well as to any limitations set forth in the information or standards referenced below.

Failure to adhere to the warnings or limitations as established by the listed specifications could result in reduced product performance, reduction of operable life, and/or reduction of overall reliability.

This product carries a **Moisture Sensitivity Level (MSL) rating** as shown below, and should be handled according to the requirements of the latest version of the joint industry standard **IPC/JEDEC J-STD-033**.

| Device   | Moisture Sensitivity Level (MSL) Rating |

|----------|-----------------------------------------|

| CPC5602C | MSL 1                                   |

#### **ESD Sensitivity**

This product is ESD Sensitive, and should be handled according to the industry standard JESD-625.

#### **Reflow Profile**

This product has a maximum body temperature and time rating as shown below. All other guidelines of **J-STD-020** must be observed.

| Device   | Maximum Temperature x Time |

|----------|----------------------------|

| CPC5602C | 260°C for 30 seconds       |

#### **Board Wash**

IXYS Integrated Circuits Division recommends the use of no-clean flux formulations. However, board washing to remove flux residue is acceptable, and the use of a short drying bake may be necessary. Chlorine-based or Fluorine-based solvents or fluxes should not be used. Cleaning methods that employ ultrasonic energy should not be used.

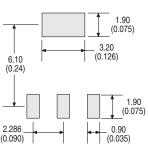

#### **MECHANICAL DIMENSIONS**

#### **CPC5602C** 2.90 / 3.10 0.229 / 0.330 (0.114 / 0.122) (0.009 / 0.013) 3.30 / 3.71 6.705 / 7.290 (0.264 / 0.287) 1.499 / 1.981 (0.130 / 0.146) (0.059 / 0.078)Pin 1 0.610 / 0.787 0.914 MIN (0.024 / 0.031)(0.036 MIN) 6.30 / 6.71 (0.248 / 0.264) 0.020 / 0.102 1.549 / 1.803 (0.061 / 0.071) (0.0008 / 0.004) 2 286 1(0.090) 0.864 / 1.067

(0.181)

### PCB Land Pattern

Dimensions mm MIN / mm MAX (inches MIN / inches MAX)

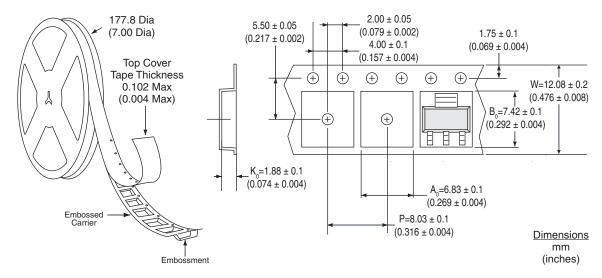

### **CPC5602CTR Tape & Reel**

(0.034 / 0.042)

#### For additional information please visit our website at: www.ixysic.com

IXYS Integrated Circuits Division makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. Neither circuit patent licenses nor indemnity are expressed or implied. Except as set forth in IXYS Integrated Circuits Division's Standard Terms and Conditions of Sale, IXYS Integrated Circuits Division assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

The products described in this document are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or where malfunction of IXYS Integrated Circuits Division's product may result in direct physical harm, injury, or death to a person or severe property or environmental damage. IXYS Integrated Circuits Division reserves the right to discontinue or make changes to its products at any time without notice.