# Single/Dual/Quad Comparators with Accurate Reference Output

**Data Sheet**

## ADCMP394/ADCMP395/ADCMP396

### **FEATURES**

High accuracy reference output voltage: 1 V  $\pm$  0.9% Single-supply voltage operation: 2.3 V to 5.5 V Rail-to-rail common-mode input voltage range Low input offset voltage across V<sub>CMR</sub>: 1 mV typical

Guarantees comparator output logic low from  $V_{\text{cc}}$  = 0.9 V to

undervoltage lockout (UVLO)

Operating temperature range: -40°C to +125°C

Package types:

8-lead, narrow body SOIC (ADCMP394)

10-lead MSOP (ADCMP395)

16-lead, narrow body SOIC (ADCMP396)

#### **APPLICATIONS**

Battery management/monitoring Power supply detection Window comparators Threshold detectors/discriminators Microprocessor systems

#### **GENERAL DESCRIPTION**

The ADCMP394/ADCMP395/ADCMP396 are single/dual/quad rail-to-rail input, low power comparator ideal for use in general-purpose applications. These comparators operate from a supply voltage of 2.3 V to 5.5 V and draw a minimal amount of current. The single ADCMP394 consumes only 33.9  $\mu A$  of supply current. The dual ADCMP395 and quad ADCMP396 consumes 37.2  $\mu A$  and 41.6  $\mu A$  of supply current respectively. The low voltage and low current operation of these devices makes it ideal for battery-powered systems.

The comparators features a common-mode input voltage range of 200 mV beyond rails, an offset voltage of 1 mV typical across the full common-mode range, and a UVLO monitor. In addition, the design of the comparator allows a defined output state upon power-up. The comparator generates a logic low output if the supply voltage is less than the UVLO threshold.

The ADCMP394/ADCMP395/ADCMP396 incorporates a 1 V  $\pm$  0.9% buffered reference voltage. The reference voltage output can directly connect to the comparator input to serve as the trip value for precise monitoring and detection of positive voltage. It can also act as an offset when monitoring the negative voltage.

The ADCMP394 and ADCMP396 are available in 8-pin and 16-lead, narrow body SOIC package, respectively. The ADCMP395 is available in a 10-lead MSOP package. The comparators are specified to operate over the  $-40^{\circ}$ C to  $+125^{\circ}$ C extended temperature range.

## Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

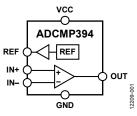

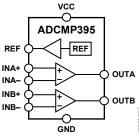

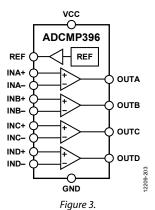

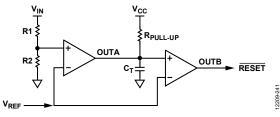

#### **FUNCTIONAL BLOCK DIAGRAMS**

Figure 1.

Figure 2.

## **Data Sheet**

## **TABLE OF CONTENT**

11/14—Revision 0: Initial Version

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| General Description                          | 1  |

| Functional Block Diagrams                    | 1  |

| Revision History                             | 2  |

| Specifications                               | 3  |

| Absolute Maximum Ratings                     | 4  |

| Thermal Resistance                           | 4  |

| ESD Caution                                  | 4  |

| Pin Configurations and Function Descriptions | 5  |

| Typical Performance Characteristics          | 7  |

| Theory of Operation                          | 11 |

| Basic Comparator                             | 11 |

| Rail-to-Rail Input (RRI)                     | 11 |

| REVISION HISTORY                             |    |

| 5/16—Rev. A to Rev. B                        |    |

| Changes to Equation 4                        | 12 |

| Changes to Figure 39                         | 14 |

| 3/15—Rev. 0 to Rev. A                        |    |

| Added ADCMP395/ADCMP396 (Throughout)         | 1  |

|   | Open-Drain Output                                        | 11 |

|---|----------------------------------------------------------|----|

|   | Power-Up Behavior                                        | 11 |

|   | Crossover Bias Point                                     | 11 |

|   | Comparator Hysteresis                                    | 11 |

| Γ | ypical Applications                                      | 12 |

|   | Adding Hysteresis                                        | 12 |

|   | Window Comparator for Positive Voltage Monitoring        | 12 |

|   | $Window\ Comparator\ for\ Negative\ Voltage\ Monitoring$ | 13 |

|   | Programmable Sequencing Control Circuit                  | 13 |

|   | Mirrored Voltage Sequencer Example                       | 15 |

|   | Threshold and Timeout Programmable Voltage Supervisor    | 16 |

| C | utline Dimensions                                        | 17 |

|   | Ordering Guide                                           | 18 |

## **SPECIFICATIONS**

$V_{\text{CC}} = 2.3 \text{ V to } 5.5 \text{ V}, T_{\text{A}} = -40 ^{\circ}\text{C to } + 125 ^{\circ}\text{C}, V_{\text{CMR}} = -200 \text{ mV to } V_{\text{CC}} + 200 \text{ mV}, unless otherwise noted.}$  Typical values are at  $T_{\text{A}} = 25 ^{\circ}\text{C}$ .

Table 1.

| Parameter                         | Symbol               | Min   | Тур        | Max                         | Unit | Test Conditions/Comments <sup>1</sup>                                                                                                              |

|-----------------------------------|----------------------|-------|------------|-----------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY                      |                      |       |            |                             |      |                                                                                                                                                    |

| Supply Voltage Range              | V <sub>CC</sub>      | 2.3   |            | 5.5                         | V    |                                                                                                                                                    |

|                                   |                      | 0.9   |            | <b>UVLO</b> <sub>RISE</sub> | V    | Guarantees comparator output low                                                                                                                   |

| V <sub>CC</sub> Quiescent Current | lcc                  |       |            |                             |      |                                                                                                                                                    |

| ADCMP394                          |                      |       | 33.9       | 47.9                        | μΑ   | All outputs in high-Z state, $V_{OD} = 0.1 \text{ V}$                                                                                              |

|                                   |                      |       | 32.6       | 45.8                        | μA   | All outputs low, $V_{OD} = 0.1 \text{ V}$                                                                                                          |

| ADCMP395                          |                      |       | 37.2       | 51.9                        | μΑ   | All outputs in high-Z state, $V_{OD} = 0.1 \text{ V}$                                                                                              |

|                                   |                      |       | 35.9       | 49.2                        | μΑ   | All outputs low, $V_{OD} = 0.1 \text{ V}$                                                                                                          |

| ADCMP396                          |                      |       | 41.6       | 59.4                        | μΑ   | All outputs in high-Z state, $V_{OD} = 0.1 \text{ V}$                                                                                              |

|                                   |                      |       | 41.3       | 56.4                        | μA   | All outputs low, $V_{OD} = 0.1 \text{ V}$                                                                                                          |

| UNDERVOLTAGE LOCKOUT              |                      |       |            |                             |      |                                                                                                                                                    |

| V <sub>CC</sub> Rising            | UVLO <sub>RISE</sub> | 2.062 | 2.162      | 2.262                       | V    |                                                                                                                                                    |

| Hysteresis                        | UVLO <sub>HYS</sub>  | 5     | 25         | 50                          | mV   |                                                                                                                                                    |

| REFERENCE OUTPUT                  | -                    |       |            |                             |      |                                                                                                                                                    |

| Reference Output Voltage          | V <sub>REF</sub>     | 0.991 | 1          | 1.008                       | V    | $I_{REF} = \pm 1 \text{ mA}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                    |

| , ,                               |                      | 0.991 | 1          | 1.008                       | V    | I <sub>REF</sub> = ±1 mA                                                                                                                           |

| COMPARATOR INPUT                  |                      |       |            |                             | 1    |                                                                                                                                                    |

| Common-Mode Input Range           | V <sub>CMR</sub>     | -200  |            | $V_{CC} + 200$              | mV   |                                                                                                                                                    |

| Input Offset Voltage              | Vos                  |       | 0.5        | 2.5                         | mV   | IN+ = IN- = 1 V                                                                                                                                    |

|                                   | 103                  |       | 0.5        | 2.5                         | mV   | $IN+=IN-=1 \text{ V, } T_A=-40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                            |

|                                   |                      |       | 1          | 5                           | mV   |                                                                                                                                                    |

|                                   |                      |       | 1          | 5                           | mV   | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                                                |

| Input Offset Current              | los                  |       | •          | 10                          | nA   | $V_{CMR} = -50 \text{ mV} \text{ to } V_{CC} + 50 \text{ mV}$                                                                                      |

| Input Bias Current                | I <sub>BIAS</sub>    |       |            | ±30                         | nA   |                                                                                                                                                    |

| pat s.as can ent                  | ·biA3                |       |            | ±80                         | nA   | $V_{CMR} = -50 \text{ mV} \text{ to } V_{CC} + 50 \text{ mV}$                                                                                      |

|                                   |                      |       |            | ±10                         | nA   | $V_{CMR} = -50 \text{ mV to } V_{CC} + 50 \text{ mV}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                           |

| Input Hysteresis                  | V <sub>HYST</sub>    |       | 3          | 4                           | mV   | V <sub>CM</sub> = 1 V                                                                                                                              |

| input hysteresis                  | VIII                 |       | 6          | 8                           | mV   | V CW - I V                                                                                                                                         |

| COMPARATOR OUTPUT                 |                      |       |            |                             |      |                                                                                                                                                    |

| Output Low Voltage                | V <sub>OL</sub>      |       | 0.1        | 0.3                         | V    | $V_{CC} = 2.3 \text{ V}, I_{SINK} = 2.5 \text{ mA}$                                                                                                |

| output Low Voltage                | VOL                  |       | 0.01       | 0.15                        | v    | $V_{CC} = 0.9 \text{ V, } I_{SINK} = 100  \mu\text{A}$                                                                                             |

| Output Leakage Current            | I <sub>LEAK</sub>    |       | 0.01       | 150                         | nA   | $V_{OUT} = 0 \text{ V to } 5.5 \text{ V}$                                                                                                          |

| COMPARATOR CHARACTERISTICS        | ILEAN                |       |            | 150                         | 11/1 | V001 = 0 V to 5.5 V                                                                                                                                |

| Power Supply Rejection Ratio      | PSRR                 | 60    | 80         |                             | dB   |                                                                                                                                                    |

| Common-Mode Rejection Ratio       | CMRR                 | 50    | 74         |                             | dB   |                                                                                                                                                    |

| Voltage Gain                      | Av                   | 30    | 132        |                             | dB   |                                                                                                                                                    |

| Rise Time <sup>2</sup>            | t <sub>R</sub>       |       | 1.1        |                             | μs   | $V_{OUT} = 10\%$ to 90% of $V_{CC}$                                                                                                                |

| Fall Time <sup>2</sup>            | t <sub>F</sub>       |       | 0.15       |                             | μs   | $V_{OUT} = 90\%$ to 10% of $V_{CC}$                                                                                                                |

| Propagation Delay                 | LF.                  |       | 0.13       |                             | μs   | V001 = 90% to 10% of VCC                                                                                                                           |

| · •                               |                      |       | 4.7        |                             |      | $V_{CM} = 1 \text{ V, } V_{CC} = 2.3 \text{ V, } V_{OD} = 10 \text{ mV}$                                                                           |

| Input Rising <sup>2</sup>         | t <sub>PROP_R</sub>  |       | 4.7<br>4.9 |                             | μs   | $V_{CM} = 1 \text{ V, } V_{CC} = 2.5 \text{ V, } V_{OD} = 10 \text{ mV}$<br>$V_{CM} = 1 \text{ V, } V_{CC} = 5 \text{ V, } V_{OD} = 10 \text{ mV}$ |

|                                   |                      |       | 4.9        | 2.0                         | μs   |                                                                                                                                                    |

|                                   |                      |       |            | 2.8                         | μs   | $V_{CM} = 1 \text{ V, } V_{CC} = 2.3 \text{ V, } 100 \text{ mV overdrive}$                                                                         |

| ADCMD20F Channel P                |                      |       | 4.0        | 3.2                         | μs   | $V_{CM} = 1 \text{ V}, V_{CC} = 5 \text{ V}, 100 \text{ mV overdrive}$                                                                             |

| ADCMP395 Channel B                |                      |       | 4.9        |                             | μs   | $V_{CM} = 1 \text{ V}, V_{CC} = 2.3 \text{ V}, V_{OD} = 10 \text{ mV}$                                                                             |

| Innut Falling?                    |                      |       | 9.7        |                             | μs   | $V_{CM} = 1 \text{ V}, V_{CC} = 5 \text{ V}, V_{OD} = 10 \text{ mV}$                                                                               |

| Input Falling <sup>2</sup>        | t <sub>PROP_F</sub>  |       | 4.5        |                             | μs   | $V_{CM} = 1 \text{ V}, V_{CC} = 2.3 \text{ V}, V_{OD} = 10 \text{ mV}$                                                                             |

|                                   |                      |       | 9.5        | 2                           | μs   | $V_{CM} = 1 \text{ V}, V_{CC} = 5 \text{ V}, V_{OD} = 10 \text{ mV}$                                                                               |

|                                   |                      |       |            | 2                           | μs   | $V_{CM} = 1 \text{ V}, V_{CC} = 2.3 \text{ V}, 100 \text{ mV overdrive}$                                                                           |

| ADCHARGE CL. LD                   |                      |       | 4 -        | 4.2                         | μs   | $V_{CM} = 1 \text{ V}, V_{CC} = 5 \text{ V}, 100 \text{ mV overdrive}$                                                                             |

| ADCMP395 Channel B                |                      |       | 4.7        |                             | μs   | $V_{CM} = 1 \text{ V}, V_{CC} = 2.3 \text{ V}, V_{OD} = 10 \text{ mV}$                                                                             |

|                                   |                      |       | 5          |                             | μs   | $V_{CM} = 1 \text{ V}, V_{CC} = 5 \text{ V}, V_{OD} = 10 \text{ mV}$                                                                               |

$<sup>^1\,</sup>V_{OD}$  is overdrive voltage.  $^2\,R_{PULL\cdot UP}=10~k\Omega,$  and  $C_L=50~pF.$

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                     | Rating          |

|-------------------------------|-----------------|

| VCC Pin                       | −0.3 V to +6 V  |

| All INx+ and INx- Pins        | −0.3 V to +6 V  |

| All OUTx Pins                 | −0.3 V to +6 V  |

| Reference Load Current, IREF  | ±1 mA           |

| OUTx Pins Sink Current, ISINK | 10 mA           |

| Storage Temperature Range     | −65°C to +150°C |

| Operating Temperature Range   | -40°C to +125°C |

| Lead Temperature (10 sec)     | 300°C           |

| Junction Temperature          | 150°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

**Table 3. Thermal Resistance**

| Package Type             | θιΑ | Unit |

|--------------------------|-----|------|

| 8-Lead Narrow-Body SOIC  | 121 | °C/W |

| 10-Lead MSOP             | 130 | °C/W |

| 16-Lead Narrow-Body SOIC | 80  | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

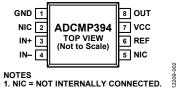

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 4. ADCMP394 Pin Configuration

Table 4. ADCMP394 Pin Function Descriptions

| Pin No. | Mnemonic | Description                                                               |

|---------|----------|---------------------------------------------------------------------------|

| 1       | GND      | Device Ground.                                                            |

| 2, 5    | NIC      | Not Internally Connected.                                                 |

| 3       | IN+      | Comparator Noninverting Input.                                            |

| 4       | IN-      | Comparator Inverting Input.                                               |

| 6       | REF      | Reference Output. This pin can be used to setup the comparator threshold. |

| 7       | VCC      | Device Supply Input.                                                      |

| 8       | OUT      | Comparator Output, Open-Drain.                                            |

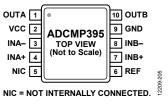

Figure 5. ADCMP395 Pin Configuration

Table 5. ADCMP395 Pin Function Descriptions

| Pin No. | Mnemonic | Description                                                            |

|---------|----------|------------------------------------------------------------------------|

| 1       | OUTA     | Comparator A Output, Open Drain.                                       |

| 2       | VCC      | Device Supply Input.                                                   |

| 3       | INA-     | Comparator A Inverting Input.                                          |

| 4       | INA+     | Comparator A Noninverting Input.                                       |

| 5       | NIC      | Not Internally Connected.                                              |

| 6       | REF      | Reference Output. This pin can be used to set up comparator threshold. |

| 7       | INB+     | Comparator B Noninverting Input.                                       |

| 8       | INB-     | Comparator B Inverting Input.                                          |

| 9       | GND      | Device Ground.                                                         |

| 10      | OUTB     | Comparator B Output, Open Drain.                                       |

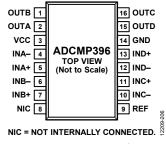

Figure 6. ADCMP396 Pin Configuration

Table 6. ADCMP396 Pin Function Descriptions

| Pin No. | Mnemonic | Description                                                                |

|---------|----------|----------------------------------------------------------------------------|

| 1       | OUTB     | Comparator B Output, Open Drain.                                           |

| 2       | OUTA     | Comparator A Output, Open Drain.                                           |

| 3       | VCC      | Device Supply Input.                                                       |

| 4       | INA-     | Comparator A Inverting Input.                                              |

| 5       | INA+     | Comparator A Noninverting Input.                                           |

| 6       | INB-     | Comparator B Inverting Input.                                              |

| 7       | INB+     | Comparator B Noninverting Input.                                           |

| 8       | NIC      | Not Internally Connected.                                                  |

| 9       | REF      | Reference Output. This pin can be used to set up the comparator threshold. |

| 10      | INC-     | Comparator C Inverting Input.                                              |

| 11      | INC+     | Comparator C Noninverting Input.                                           |

| 12      | IND-     | Comparator D Inverting Input.                                              |

| 13      | IND+     | Comparator D Noninverting Input.                                           |

| 14      | GND      | Device Ground.                                                             |

| 15      | OUTD     | Comparator D Output, Open Drain.                                           |

| 16      | OUTC     | Comparator C Output, Open Drain.                                           |

### TYPICAL PERFORMANCE CHARACTERISTICS

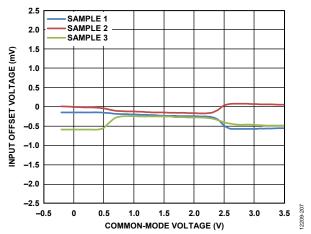

Figure 7. Input Offset Voltage ( $V_{CS}$ ) vs. Common-Mode Voltage ( $V_{CM}$ ),  $V_{CC} = 3.3 \text{ V}$

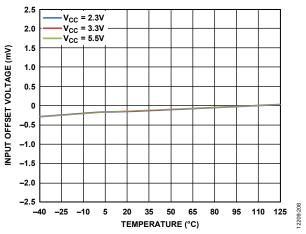

Figure 8. Input Offset Voltage ( $V_{OS}$ ) vs. Temperature for Various Supply Voltages,  $V_{CM} = 1 \text{ V}$

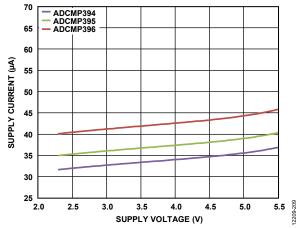

Figure 9. Supply Current ( $I_{CC}$ ) vs. Supply Voltage ( $V_{CC}$ ) at Output Low Voltage

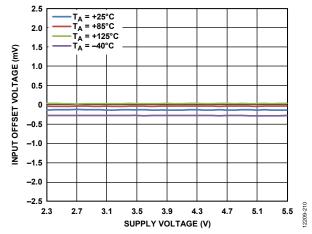

Figure 10. Input Offset Voltage ( $V_{CS}$ ) vs. Supply Voltage ( $V_{CC}$ ),  $V_{CM} = 1 V$  for Various Temperatures

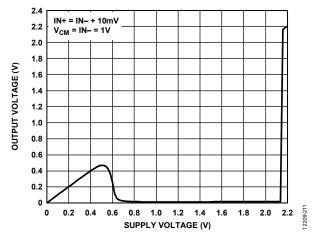

Figure 11. Output Voltage ( $V_{OUT}$ ) vs. Supply Voltage ( $V_{CC}$ ),  $R_{PULLUP} = 10 \text{ k}\Omega$

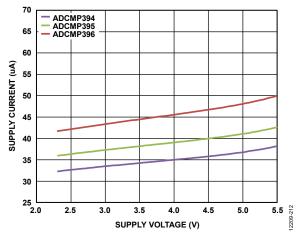

Figure 12. Supply Current ( $I_{CC}$ ) vs. Supply Voltage ( $V_{CC}$ ) at Output High Voltage

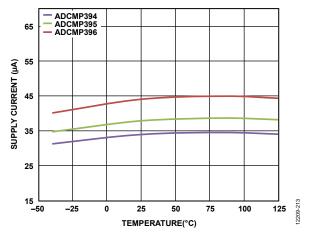

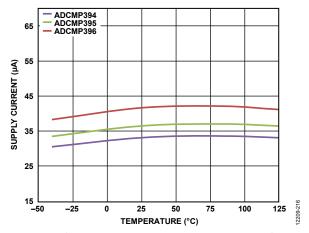

Figure 13. Supply Current (Icc) vs. Temperature at Output High Voltage (VoH)

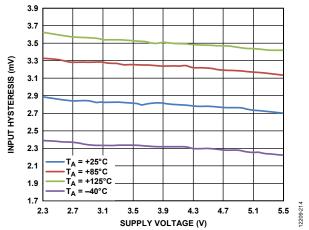

Figure 14. Input Hysteresis vs. Supply Voltage ( $V_{CC}$ ),  $V_{CM} = 1 V$  for Various Temperatures

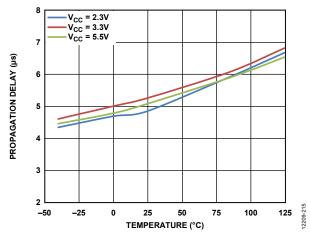

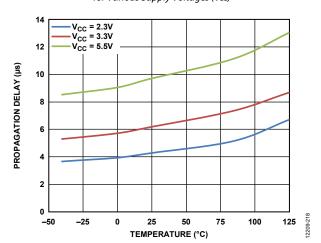

Figure 15. Propagation Delay vs. Temperature, Low to High,  $V_{\text{OD}} = 10 \text{ mV}$

Figure 16. Supply Current (Icc) vs. Temperature at Output Low Voltage (Vol.)

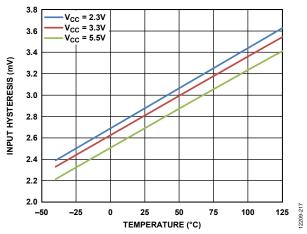

Figure 17. Input Hysteresis vs. Temperature,  $V_{CM} = 1 V$  for Various Supply Voltages ( $V_{CC}$ )

Figure 18. Propagation Delay vs. Temperature, High to Low,  $V_{\text{OD}} = 10 \text{ mV}$

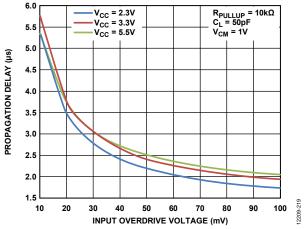

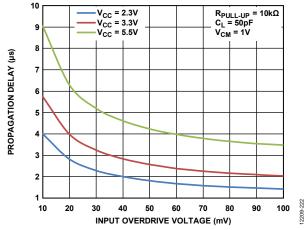

Figure 19. Propagation Delay vs. Input Overdrive Voltage, Low to High

Figure 20. Propagation Delay vs. Input Overdrive Voltage, Low to High, Channel B

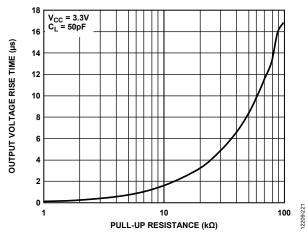

Figure 21. Output Voltage Rise Time (t<sub>R</sub>) vs. Pull-Up Resistance (R<sub>PULLUP</sub>)

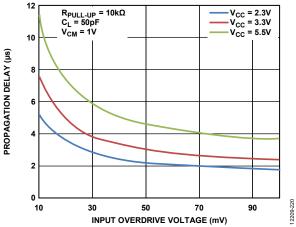

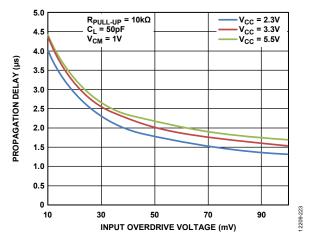

Figure 22. Propagation Delay vs. Input Overdrive Voltage, High to Low

Figure 23. Propagation Delay vs. Input Overdrive Voltage, High to Low, Channel B

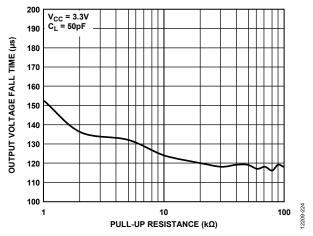

Figure 24. Output Voltage Fall Time ( $t_F$ ) vs. Pull-Up Resistance ( $R_{PULLUP}$ )

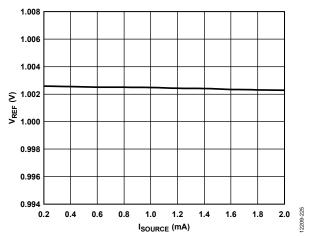

Figure 25. Reference Voltage ( $V_{REF}$ ) vs. Source Current ( $I_{SOURCE}$ ) of the REF Pin,  $V_{CC} = 3.3~V$

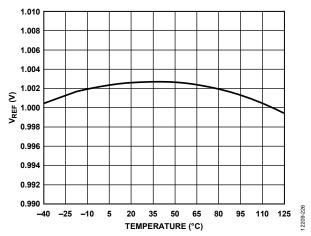

Figure 26. Reference Voltage ( $V_{REF}$ ) vs. Temperature,  $V_{CC} = 3.3 \text{ V}$

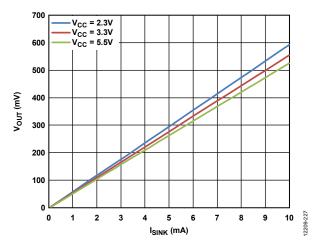

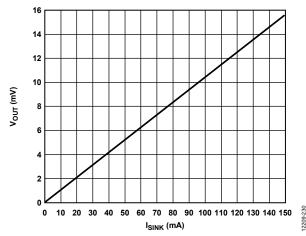

Figure 27. Output Voltage (V<sub>OUT</sub>) Low vs. Sink Current (I<sub>SINK</sub>) for Various Supply Voltages

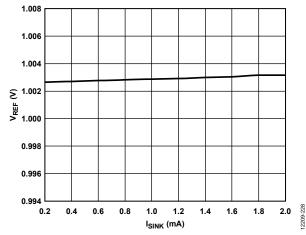

Figure 28. Reference Voltage (V\_REF) vs. Sink Current (I\_SINK) of the REF Pin,  $V_{CC}=3.3~V$

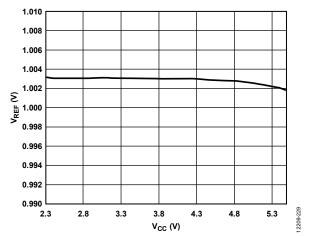

Figure 29. Reference Voltage ( $V_{REF}$ ) vs. Supply Voltage ( $V_{CC}$ )

Figure 30. Output Voltage ( $V_{OUT}$ ) Low vs. Sink Current ( $I_{SINK}$ ),  $V_{CC} = 0.9 \text{ V}$

## THEORY OF OPERATION BASIC COMPARATOR

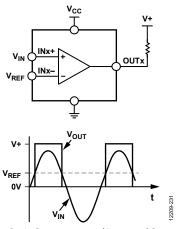

In its most basic configuration, a comparator can be used to convert an analog input signal to a digital output signal (see Figure 31). The analog signal on INx+ is compared to the voltage on INx-, and the voltage at OUTx is either high or low, depending on whether INx+ is at a higher or lower potential than INx-, respectively.

Figure 31. Basic Comparator and Input and Output Signals

### **RAIL-TO-RAIL INPUT (RRI)**

Using a CMOS nonRRI stage (that is, a single differential pair) limits the input voltage to approximately one gate-to-source voltage ( $V_{\rm GS}$ ) away from one of the supply lines. Because  $V_{\rm GS}$  for normal operation is commonly more than 1 V, a single differential pair input stage comparator greatly restricts the allowable input voltage. This restriction can be quite limiting with low voltage supplies. To resolve this issue, RRI stages allow the input signal range to extend up to the supply voltage range. In the case of the ADCMP394/ADCMP395/ADCMP396, the inputs continue to operate 200 mV beyond the supply rails.

### **OPEN-DRAIN OUTPUT**

The ADCMP394/ADCMP395/ADCMP396 have an open-drain output stage that requires an external resistor to pull up to the logic high voltage level when the output transistor is switched off. The pull-up resistor must be large enough to avoid excessive power dissipation, but small enough to switch logic levels reasonably quickly when the comparator output is connected to other digital circuitry. The rise time of the open-drain output depends on the pull-up resistor (RPULLUP) and load capacitor (CL) used.

The rise time can be calculated by

$$t_R = 2.2 R_{PULLUP} C_L \tag{1}$$

### **POWER-UP BEHAVIOR**

On power-up, when  $V_{\rm CC}$  reaches 0.9 V, the ADCMP394/ ADCMP395/ADCMP396 is guaranteed to assert an output low logic. When the voltage on the  $V_{\rm CC}$  pin exceeds UVLO, the comparator inputs take control.

#### **CROSSOVER BIAS POINT**

Rail-to-rail inputs of this type of architecture in both op amps and comparators, have a dual front-end design. PMOS devices are inactive near the  $V_{\rm CC}$  rail, and NMOS devices are inactive near GND. At some predetermined point in the common-mode range, a crossover occurs. At this point, normally 0.8 V and  $V_{\rm CC}$  – 0.8 V, the measured offset voltages change.

#### **COMPARATOR HYSTERESIS**

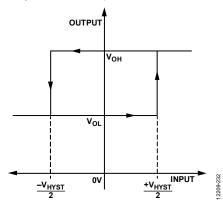

In noisy environments, or when the differential input amplitudes are relatively small or slow moving, adding hysteresis ( $V_{\rm HYST}$ ) to the comparator is often desirable. The transfer function for a comparator with hysteresis is shown in Figure 32. As the input voltage approaches the threshold (0 V in Figure 32) from below the threshold region in a positive direction, the comparator switches from low to high when the input crosses  $+V_{\rm HYST}/2$ . The new switch threshold becomes  $-V_{\rm HYST}/2$ . The comparator remains in the high state until the  $-V_{\rm HYST}/2$  threshold is crossed from below the threshold region in a negative direction. In this manner, noise or feedback output signals centered on the 0 V input cannot cause the comparator to switch states unless it exceeds the region bounded by  $\pm V_{\rm HYST}/2$ .

Figure 32. Comparator Hysteresis Transfer Function

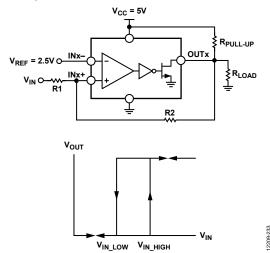

## TYPICAL APPLICATIONS ADDING HYSTERESIS

To add hysteresis, see Figure 33; two resistors are used to create different switching thresholds, depending on whether the input signal is increasing or decreasing in magnitude. When the input voltage increases, the threshold is above  $V_{\text{REF}}$ , and when the input voltage decreases, the threshold is below  $V_{\text{REF}}$ .

Figure 33. Noninverting Comparator Configuration with Hysteresis

The upper input threshold level is given by

$$V_{IN\_HI} = \frac{V_{REF}(RI + R2)}{R2} \tag{2}$$

Assuming  $R_{LOAD} >> R2$ ,  $R_{PULLUP}$ .

The lower input threshold level is given by

$$V_{IN\_LO} = \frac{V_{REF} (R1 + R2 + R_{PULLUP}) - V_{CC}R1}{R2 + R_{PULLUP}}$$

(3)

The hysteresis is the difference between these voltages levels.

$$V_{HYS} = \frac{V_{REF} \times (R1 \times R_{PULL-UP}) + V_{CC} \times (R1 \times R2)}{R2(R2 + R_{PULL-UP})} \tag{4}$$

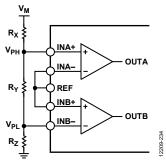

## WINDOW COMPARATOR FOR POSITIVE VOLTAGE MONITORING

When monitoring a positive supply, the desired nominal operating voltage for monitoring is denoted by  $V_M$ ,  $I_M$  is the nominal current through the resistor divider,  $V_{\rm OV}$  is the overvoltage trip point, and  $V_{\rm UV}$  is the undervoltage trip point.

Figure 34. Positive Undervoltage/Overvoltage Monitoring Configuration

Figure 34 illustrates the positive voltage monitoring input connection. Three external resistors,  $R_X$ ,  $R_Y$ , and  $R_Z$ , divide the positive voltage for monitoring,  $V_M$ , into the high-side voltage,  $V_{PH}$ , and the low-side voltage,  $V_{PL}$ . The high-side voltage is connected to the INA+ pin and the low-side voltage is connected to the INB- pin.

To trigger an overvoltage condition, the low-side voltage (in this case,  $V_{\text{PL}}$ ) must exceed the  $V_{\text{REF}}$  threshold on the INB+ pin. Calculate the low-side voltage,  $V_{\text{PL}}$ , by the following:

$$V_{PL} = V_{REF} = V_{OV} \left( \frac{R_Z}{R_X + R_Y + R_Z} \right) \tag{5}$$

In addition,

$$R_X + R_Y + R_Z = V_M / I_M \tag{6}$$

Therefore,  $R_Z$ , which sets the desired trip point for the overvoltage monitor, is calculated as

$$R_Z = \frac{\left(V_{REF}\right)\left(V_M\right)}{\left(V_{OV}\right)\left(I_M\right)} \tag{7}$$

To trigger the undervoltage condition, the high-side voltage,  $V_{\text{PH}}$ , must be less than the  $V_{\text{REF}}$  threshold on the INA– pin. The high-side voltage,  $V_{\text{PH}}$ , is calculated by

$$V_{PH} = V_{REF} = V_{UV} \left( \frac{R_Y + R_Z}{R_X + R_Y + R_Z} \right)$$

(8)

Because Rz is already known, Ry can be expressed as

$$R_{Y} = \frac{\left(V_{REF}\right)\left(V_{M}\right)}{\left(V_{UV}\right)\left(I_{M}\right)} - R_{Z} \tag{9}$$

When R<sub>Y</sub> and R<sub>Z</sub> are known, R<sub>X</sub> can be calculated by

$$R_X = (V_M/I_M) - R_Y - R_Z \tag{10}$$

If V<sub>M</sub>, I<sub>M</sub>, V<sub>OV</sub>, or V<sub>UV</sub> changes, each step must be recalculated.

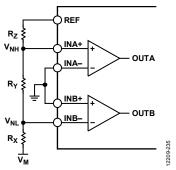

## WINDOW COMPARATOR FOR NEGATIVE VOLTAGE MONITORING

Figure 35 shows the circuit configuration for negative supply voltage monitoring. To monitor a negative voltage, a reference voltage is required to connect to the end node of the voltage divider circuit, in this case, REF.

Figure 35. Negative Undervoltage/Overvoltage Monitoring Configuration

Equation 7, Equation 9, and Equation 10 need some minor modifications. The reference voltage,  $V_{\text{REF}}$ , is added to the overall voltage drop; therefore, it must be subtracted from  $V_{\text{M}}$ ,  $V_{\text{UV}}$ , and  $V_{\text{OV}}$  before using each of them in Equation 7, Equation 9, and Equation 10.

To monitor a negative voltage level, the resistor divider circuit divides the voltage differential level between  $V_{REF}$  and the negative supply voltage into the high-side voltage,  $V_{NH}$ , and the low-side voltage,  $V_{NL}$ . The high-side voltage,  $V_{NH}$ , is connected to INA+, and the low-side voltage,  $V_{NL}$ , is connected to INB-.

To trigger an overvoltage condition, the monitored voltage must exceed the nominal voltage in terms of magnitude, and the high-side voltage (in this case,  $V_{\rm NH}$ ) on the INA+ pin must be more negative than ground. Calculate the high-side voltage,  $V_{\rm NH}$ , by using the following formula:

$$V_{NH} = GND = \left[ \left( V_{REF} - V_{OV} \left( \frac{R_X + R_Y}{R_X + R_Y + R_Z} \right) \right] + V_{OV} \right]$$

(11)

In addition,

$$R_X + R_Y + R_Z = \frac{\left(V_M - V_{REF}\right)}{I_M} \tag{12}$$

Therefore, R<sub>z</sub>, which sets the desired trip point for the overvoltage monitor, is calculated by

$$R_{Z} = \frac{V_{REF}(V_{M} - V_{REF})}{I_{M}(V_{REF} - V_{OV})}$$

(13)

To trigger an undervoltage condition, the monitored voltage must be less than the nominal voltage in terms of magnitude, and the low-side voltage (in this case,  $V_{\rm NL}$ ) on the INB– pin must be more positive than ground. Calculate the low-side voltage,  $V_{\rm NL}$ , by the following:

$$V_{NL} = GND = \left[ \left( V_{REF} - V_{UV} \left( \frac{R_X}{R_X + R_Y + R_Z} \right) \right] + V_{UV}$$

(14)

Because Rz is already known, Ry can be expressed as follows:

$$R_{Y} = \frac{V_{REF}(V_{M} - V_{REF})}{I_{M}(V_{REF} - V_{UV})} - R_{Z}$$

(15)

When R<sub>Y</sub> and R<sub>Z</sub> are known, R<sub>X</sub> is then calculated by

$$R_X = \frac{\left(V_M - V_{REF}\right)}{I_M} - R_Y - R_Z \tag{16}$$

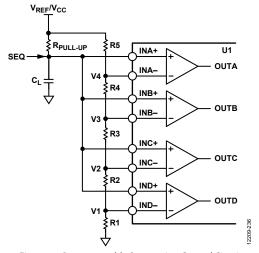

### PROGRAMMABLE SEQUENCING CONTROL CIRCUIT

The circuit shown in Figure 36 is used to control power supply sequencing. The delay is set by the combination of the pull-up resistor (Rpullup), the load capacitor (CL), and the resistor divider network.

Figure 36. Programmable Sequencing Control Circuit

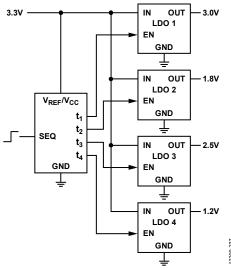

Figure 37 shows a simple block diagram for a programmable sequencing control circuit. The application delays the enable signal, EN, of the external regulators (LDO x) in a linear order when the open-drain signal (SEQ) changes from low to high impedance.

The ADCMP394/ADCMP395/ADCMP396 have a defined output state during startup, which prevents any regulator from turning on if  $V_{\rm CC}$  is still below the UVLO threshold.

Figure 37. Simplified Block Diagram of a Programmable Sequencing Control Circuit

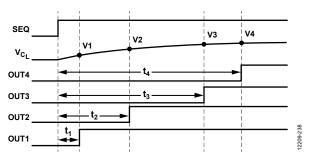

Figure 38. Programmable Sequencing Control Circuit Timing Diagram

When the SEQ signal changes from low to high impedance, the load capacitor,  $C_L$ , starts to charge. The time it takes to charge the load capacitor to the pull-up voltage (in this case,  $V_{\text{REF}}$  or  $V_{\text{CC}}$ ) is the maximum delay programmable in the circuit. It is recommended to have the threshold within 10% to 90% of the pull-up voltage. Calculate the maximum allowable delay by

$$t_{MAX} = 2.2R_{PULLUP}C_{LOAD} \tag{17}$$

The delay of each output is changed by changing the threshold voltage, V1 to V4, when the comparator changes its output state.

To calculate the voltage thresholds for the comparator, use the following formulas:

$$V1 = V_{REF} \left( 1 - e^{\frac{-t_1}{R_{PULLUP}C_L}} \right)$$

(18)

$$V2 = V_{REF} \left( 1 - e^{\frac{-t_2}{R_{PULLUP}C_L}} \right)$$

(19)

$$V3 = V_{REF} \left( 1 - e^{\frac{-t_3}{R_{PULLUP}C_L}} \right) \tag{20}$$

$$V4 = V_{REF} \left( 1 - e^{\frac{-t_4}{R_{PULLUF}C_L}} \right) \tag{21}$$

The threshold voltages can come from a voltage reference or a voltage divider circuit, as shown in Figure 36.

First, determine the allowable current,  $I_{DIV}$ , flowing through the resistor divider. After the value for  $I_{DIV}$  is determined, calculate R1, R2, R3, R4, and R5 using the following formulas:

$$R_{DIV} = \frac{V_{REF}}{I_{DIV}} = R1 + R2 + R3 + R4 + R5 \tag{22}$$

$$RI = \frac{V1R_{DIV}}{V_{RFF}} \tag{23}$$

$$R2 = \frac{V2R_{DIV}}{V_{REF}} - R1 \tag{24}$$

$$R3 = \frac{V3R_{DIV}}{V_{REF}} - R1 - R2 \tag{25}$$

$$R4 = \frac{V4R_{DIV}}{V_{REF}} - R1 - R2 - R3 \tag{26}$$

$$R5 = R_{DIV} - R1 - R2 - R3 - R4 \tag{27}$$

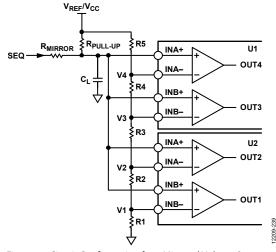

To create a mirrored voltage sequence, add a resistor ( $R_{\text{MIRROR}}$ ) between the pull-up resistor ( $R_{\text{PULLUP}}$ ) and the load capacitor ( $C_L$ ) as shown in Figure 39.

${\it Figure\,39. Circuit\,Configuration\,for\,a\,Mirrored\,Voltage\,Sequencer}$

Figure 39 shows the circuit configuration for a mirrored voltage sequencer. When SEQ changes from low to high impedance, the response is similar to Figure 38. When SEQ changes from high to low impedance, the load capacitor ( $C_L$ ) starts to discharge at a rate set by  $R_{\text{MIRROR}}$ . The delay of each comparator is dependent on the threshold voltage previously set for  $t_1$  to  $t_4$ . The result is a mirrored power-down sequence.

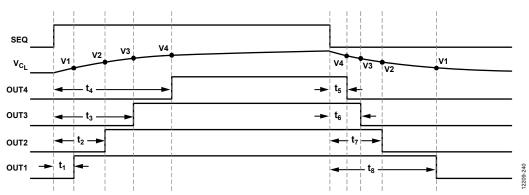

Figure 40. Mirrored Voltage Sequencer Timing Diagram

The timing diagram for the mirrored voltage sequencer is shown in Figure 40.

Equation 18 through Equation 21 must account for the additional resistance,  $R_{\rm MIRROR}$ , in the calculations of the voltage thresholds. To calculate these new thresholds, see Equation 28 through Equation 31.

$$V1 = V_{REF} \left( 1 - e^{\frac{-t_1}{(R_{PULLUP} + R_{MIRROR})C_L}} \right)$$

(28)

$$V2 = V_{REF} \left( 1 - e^{\frac{-t_2}{\left( R_{PULLUP} + R_{MIRROR} \right) C_L}} \right)$$

(29)

$$V3 = V_{REF} \left( 1 - e^{\frac{-t_3}{\left(R_{PULLUP} + R_{MIRROR}\right)C_L}} \right)$$

(30)

$$V4 = V_{REF} \left( 1 - e^{\frac{-t_4}{\left( R_{PULLUP} + R_{MIRROR} \right) C_L}} \right)$$

(31)

R<sub>MIRROR</sub> provides the mirrored delay by prolonging the discharge time of the capacitor. The mirrored voltage sequencer uses the same threshold in Equation 28 to Equation 31 in a decreasing order. To calculate the exact value of the mirrored delay time, see Equation 32 through Equation 35.

$$t_{5} = -R_{MIRROR}C_{L}\ln\left(\frac{V4}{V_{RFF}}\right) \tag{32}$$

$$t_6 = -R_{MIRROR}C_L \ln \left(\frac{V3}{V_{REF}}\right) \tag{33}$$

$$t_7 = -R_{MIRROR}C_L \ln \left( \frac{V2}{V_{REF}} \right) \tag{34}$$

$$t_{8} = -R_{MIRROR}C_{L}\ln\left(\frac{VI}{V_{REF}}\right) \tag{35}$$

### MIRRORED VOLTAGE SEQUENCER EXAMPLE

To illustrate how the mirrored voltage sequencer works, see Figure 37 and then consider a system that uses a  $V_{\rm REF}$  of 1 V and requires a delay of 50 ms when SEQ changes from low to high impedance, and between each regulator when turning on. These considerations require a rise time of at least 200 ms for the pull-up resistor (Rpullup) and the load capacitor (Cl). The sum of the resistance of Rmirror and Rpullup must be large enough to charge the capacitor longer than the minimum required delay. For a symmetrical mirrored power-down sequence, the value of Rmirror must be much larger than Rpullup. A 10 k $\Omega$  Rpullup value limits the pull-down current to 100  $\mu$ A while giving a reasonable value for Rmirror. A typical 1  $\mu$ F capacitor together with a 150 k $\Omega$  Rmirror value gives a value of

$$t_{MAX} = 2.2((160 \times 10^3) \times (1 \times 10^{-6})) = 351 \text{ ms}$$

(36)

The threshold voltage required by each comparator is set by Equation 28 to Equation 31. For example,

$$V1 = V_{REF} \left( 1 - e^{\frac{-50 \times 10^{-3}}{160 \times 10^{3} \times 1 \times 10^{-6}}} \right)$$

where V1 = 268.38 mV.

Therefore, V2 = 464.74 mV, V3 = 608.39 mV, and V4 = 713.5 mV.

Next, consider 10  $\mu$ A as the maximum current ( $I_{DIV}$ ) flowing through the resistor divider network. This current gives the total resistance of the divider network ( $R_{DIV}$ ) and the individual resistor values using Equation 22 to Equation 27, resulting in the following:

- $R_{DIV} = 100 \text{ k}\Omega$

- $R1 = 26.84 \text{ k}\Omega \approx 26.7 \text{ k}\Omega$

- $R2 = 19.64 \text{ k}\Omega \approx 19.6 \text{ k}\Omega$

- $R3 = 14.37 \text{ k}\Omega \approx 14.3 \text{ k}\Omega$

- $R4 = 10.51 \text{ k}\Omega \approx 10.5 \text{ k}\Omega$

- $R5 = 28.65 \text{ k}\Omega \approx 28.7 \text{ k}\Omega$

Resistor values from the calculation are nonindustry standard, using industry standard resistor values resulted in a new  $R_{\rm DIV}$  value of 99.8 k $\Omega$ . Due to the discrepancy of the calculated resistor value to the industry standard value, the threshold of each comparator also changed. Calculate the new threshold values by using a simple voltage divider formula:

$$VI = V_{REF}R1/R_{DIV}$$

(37)

where V1 =  $\frac{1V(26.7 \text{ k}\Omega)}{99.8 \text{ k}\Omega} = 267.54 \text{ mV}.$

Therefore, V2 = 463.93 mV, V3 = 607.21 mV, and V4 = 712.42 mV.

Because the threshold of each comparator has changed, the time when each comparator changes its output has also changed. Calculate the new delay values for each comparator by using the following equation:

$$t_{I} = -C_{L} \left( R_{PULLUP} + R_{MIRROR} \right) \ln \left( 1 - \frac{VI}{V_{REF}} \right)$$

(38)

where

$$t_I = -1 \,\mu\text{F}(10 \,\text{k}\Omega + 150 \,\text{k}\Omega) \ln\left(1 - \frac{267.54 \,\text{mV}}{1}\right) = 49.81 \,\text{ms}.$$

Therefore,  $t_2 = 99.78$  ms,  $t_3 = 149.52$  ms, and  $t_4 = 199.4$  ms.

To calculate t<sub>5</sub> through t<sub>8</sub>, use Equation 32 to Equation 35:

$$t_5 = -R_{MIRROR}C_L \ln \left( \frac{V4}{V_{REF}} \right)$$

where

$$t_5 = -150~k\Omega \times 1~\mu F \times ln \bigg(\frac{712.42~mV}{1}\bigg) = 50.86~ms.$$

Therefore,  $t_6 = 74.83$  ms,  $t_7 = 115.2$  ms, and  $t_8 = 197.78$  ms.

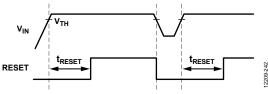

## THRESHOLD AND TIMEOUT PROGRAMMABLE VOLTAGE SUPERVISOR

Figure 41 shows a circuit configuration for a programmable threshold and timeout circuit. The timeout,  $t_{RESET}$ , defines the duration that the input voltage  $(V_{IN})$  must be kept above the threshold voltage to toggle the  $\overline{RESET}$  signal, preventing the device from operating when  $V_{IN}$  is not stable. If  $V_{IN}$  falls below the threshold voltage, the  $\overline{RESET}$  signal toggles quickly.

Figure 41. Programmable Threshold and Timeout Circuit

Figure 42. Threshold and Timeout Programmable Voltage Supervisor Timing Diagram

During startup, the ADCMP394/ADCMP395/ADCMP396 guarantee a low output state when  $V_{\rm CC}$  is still below the UVLO threshold, preventing the voltage supervisor from toggling.

When  $V_{\rm IN}$  reaches the threshold set by the resistor divider (R1 and R2) and  $V_{\rm REF}$ , OUT1 changes from low to high and starts to charge the timeout capacitor ( $C_T$ ). If  $V_{\rm IN}$  is kept above the threshold voltage and the voltage in  $C_T$  reaches  $V_{\rm REF}$ , OUT2 toggles. If  $V_{\rm IN}$  falls below the threshold voltage while  $C_T$  is charging, the timeout capacitor quickly discharges, preventing OUT2 from toggling while  $V_{\rm IN}$  is not stable.

In the condition that  $V_{\rm IN}$  is tied to  $V_{\rm CC}$ , the circuit operates when  $V_{\rm CC}$  is more than the minimum operating voltage.

The threshold voltage ( $V_{\text{TH}}$ ) is configured by changing the resistor divider or  $V_{\text{REF}}$ . Calculate the threshold voltage by

$$V_{TH} = V_{REF} \left( 1 + \frac{RI}{R2} \right) \tag{39}$$

Timeout is adjusted by changing the values of the pull-up resistor or the timeout capacitor. To set the timeout value, determine the allowable current flowing through Rpullup, Ipullup. When Ipullup is known, calculate Rpullup and C<sub>T</sub> by the following formulas:

$$R_{PULLUP} = V_{CC}/I_{PULLUP} \tag{40}$$

$$C_{T} = \frac{-t_{RESET}}{R_{PULLUP} ln \left(1 - \frac{V_{REF}}{V_{CC}}\right)}$$

(41)

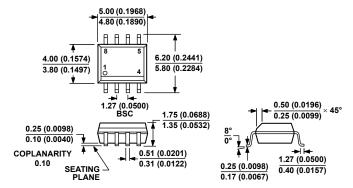

### **OUTLINE DIMENSIONS**

### COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 43. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

Figure 44. 10-Lead Mini Small Outline Package [MSOP] (RM-10) Dimensions shown in millimeters

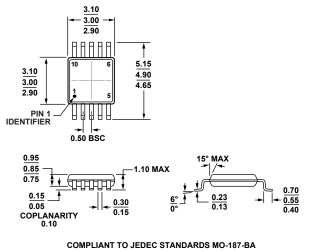

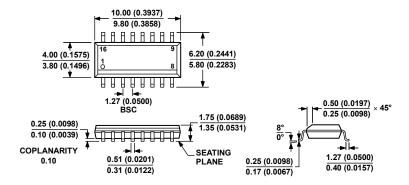

#### COMPLIANT TO JEDEC STANDARDS MS-012-AC

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 45. 16-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-16)

Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                             | Package Option | Branding |

|--------------------|-------------------|-------------------------------------------------|----------------|----------|

| ADCMP394ARZ        | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]  | R-8            |          |

| ADCMP394ARZ-RL7    | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]  | R-8            |          |

| ADCMP395ARMZ       | −40°C to +125°C   | 10-Lead Mini Small Outline Package [MSOP]       | RM-10          | LQ4      |

| ADCMP395ARMZ-RL7   | −40°C to +125°C   | 10-Lead Mini Small Outline Package [MSOP]       | RM-10          | LQ4      |

| ADCMP396ARZ        | -40°C to +125°C   | 16-Lead Standard Small Outline Package [SOIC_N] | R-16           |          |

| ADCMP396ARZ-RL7    | -40°C to +125°C   | 16-Lead Standard Small Outline Package [SOIC_N] | R-16           |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.