# Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

### **General Description**

DARWIN is a new breed of low-power microcontrollers built to thrive in the rapidly evolving Internet of Things (IoT). They are smart, with the biggest memories in their class and a massively scalable memory architecture. They run forever, thanks to wearable-grade power technology. They are durable enough to withstand the most advanced cyberattacks. DARWIN microcontrollers are designed to run any application imaginable—in places where you would not dream of sending other microcontrollers.

Generation UB microcontrollers are designed to handle the increasingly complex applications demanded by today's advanced battery-powered devices and wirelessly connected devices, while providing robust hardware security and Bluetooth<sup>®</sup> 5 Low Energy (BLE) radio connectivity.

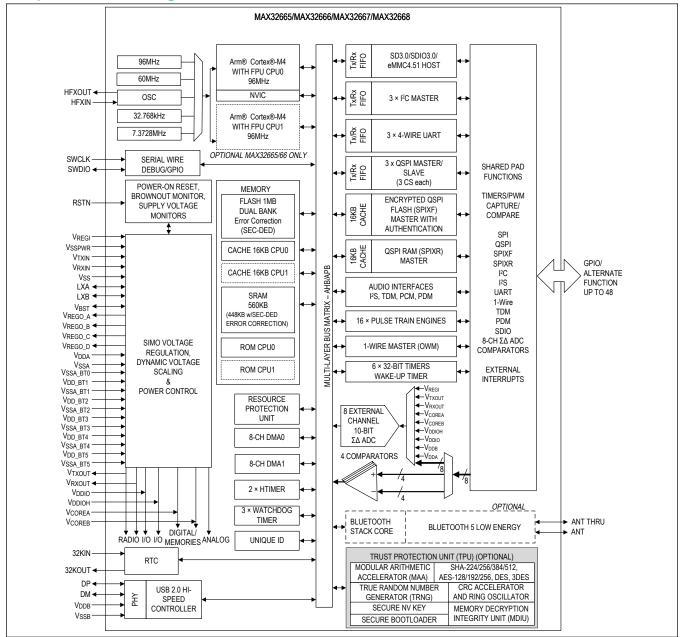

The MAX32665-MAX32668 UB class microcontrollers are advanced systems-on-chips featuring an Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU CPU for efficient computation of complex functions and algorithms with integrated power management. It also includes the newest generation Bluetooth 5 Low Energy radio with support for long range (4x) and high throughput (2Mbps) and Maxim's best-in-class hardware security suite trust protection unit (TPU). The devices offer large on-board memory with 1MB flash and up to 560KB SRAM that can be configured as 448KB SRAM with error correction coding (ECC). Split flash banks of 512KB each support seamless over the air upgrades, adding an additional degree of reliability. Memory scalability of data (SRAM) and code (Flash) space is supported by two SPI execute-in-place (SPIX) interfaces.

Multiple high-speed interfaces are supported including HS-USB, secure digital interface (SD, SDIO, MMC, SD-HC, and microSD<sup>™</sup>), SPI, UART, and I<sup>2</sup>C serial interfaces, and an audio subsystem supporting PDM, PCM, I<sup>2</sup>S, and TDM interfaces. An 8-input, 10-bit ADC is available to monitor analog inputs from external sensors and meters. The devices are available in 109-bump WLP (0.35mm pitch) and 121-bump CTBGA (0.65mm pitch).

## **Applications**

- Connected Home

- Industrial Sensors

- Payment/Fitness/Medical Wearables

- Telemedicine

- Gaming Devices

- Hearables

#### **Benefits and Features**

- High-Efficiency Microcontroller and Audio DSP for Wearable and Hearable Devices

- · Arm Cortex-M4 with FPU Up to 96MHz

- Optional Second Arm Cortex-M4 with FPU Optimized for Data Processing

- Low-Power 7.3728MHz System Clock Option

- 1MB Flash, Organized into Dual Banks 2 x 512KB

- 560KB (448KB ECC) SRAM; 3 x 16KB Cache

- Optional Error Correction Code (ECC-SEC-DED) for Cache, SRAM, and Internal Flash

- Bluetooth 5 Low Energy Radio

- 1Mbps and 2Mbps Data Throughput

- Long Range (125kbps and 500kbps)

- · Advertising Extension

- Rx Sensitivity: -95dbm; Tx Power Up to +4.5dbm

- On-Chip Matching with Single-Ended Antenna Port

- Power Management Maximizes Operating Time for Battery Applications

- Integrated SIMO SMPS for Coin-Cell Operation

- Dynamic Voltage Scaling Minimizes Active Core Power Consumption

- 27.3µA/MHz at 3.3V Executing from Cache

- Selectable SRAM Retention in Low Power Modes

with RTC Enabled

- Multiple Peripherals for System Control

- Three QSPI Master/Slave with Three Chip Selects Each, Three 4-Wire UARTs, Three I<sup>2</sup>C Master/ Slave, up to 50 GPIO

- QSPI (SPIXF) with Real-Time Flash Decryption

- QSPI (SPIXR) RAM Interface Provides SRAM Expansion

- 8-Input, 10-Bit Delta-Sigma ADC 7.8ksps

- USB 2.0 HS Engine with Internal Transceiver

- PDM Interface Supports Two Digital Microphones

- I<sup>2</sup>S with TDM, Six 32-Bit Timers, Two High-Speed Timers, 1-Wire Master, Sixteen Pulse Trains (PWM)

- Secure Digital Interface Supports SD3.0/SDIO3.0/ eMMC4.51

- Secure Valuable IP/Data with Hardware Security

- Trust Protection Unit (TPU) with MAA Supports Fast ECDSA and Modular Arithmetic

- AES128/192/256, DES, 3DES, Hardware Accelerator

- TRNG Seed Generator, SHA-2 Accelerator

- · Secure Bootloader

Ordering Information appears at end of data sheet.

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

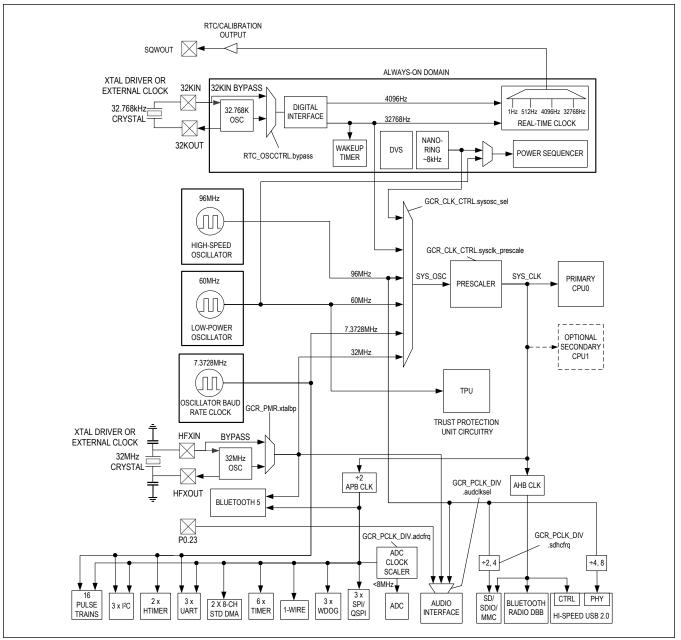

## Simplified Block Diagram

Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **TABLE OF CONTENTS**

| General Description                                                  | 1  |

|----------------------------------------------------------------------|----|

| Applications                                                         | 1  |

| Benefits and Features                                                | 1  |

| Simplified Block Diagram                                             | 2  |

| Absolute Maximum Ratings                                             | 7  |

| Package Information                                                  | 7  |

| 109 WLP                                                              | 7  |

| 121 CTBGA                                                            | 7  |

| Electrical Characteristics                                           | 8  |

| Electrical Characteristics—SPI                                       | 17 |

| Electrical Characteristics—I <sup>2</sup> C                          | 18 |

| Electrical Characteristics—SD/SDIO/SDHC/MMC                          | 20 |

| Electrical Characteristics—One Wire Master                           | 21 |

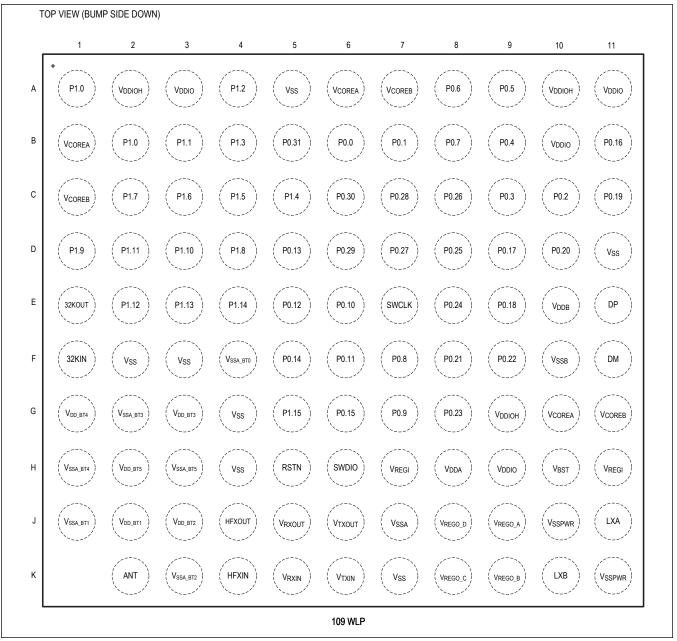

| Pin Configurations                                                   | 25 |

| 109 WLP                                                              | 25 |

| 121 CTBGA                                                            | 26 |

| Pin Description                                                      | 26 |

| Detailed Description                                                 | 31 |

| MAX32665–MAX32668                                                    | 31 |

| Arm Cortex-M4 with FPU Processor                                     | 31 |

| Memory                                                               | 31 |

| Internal Flash Memory                                                | 31 |

| Internal SRAM                                                        | 31 |

| Secure Digital Interface                                             | 32 |

| Bluetooth 5                                                          | 32 |

| Bluetooth 5 Low Energy Radio                                         | 32 |

| Bluetooth 5 Software Stack                                           | 32 |

| Comparators                                                          | 33 |

| Dynamic Voltage Scaling Controller                                   | 33 |

| Clocking Scheme                                                      | 33 |

| General-Purpose I/O and Special Function Pins                        | 34 |

| Analog-to-Digital Converter                                          | 35 |

| Single-Inductor Multiple-Output Switch-Mode Power Supply (SIMO SMPS) | 35 |

| Power Management                                                     | 35 |

| Power Management Unit                                                | 35 |

| Active Mode.                                                         | 36 |

| Sleep Mode                                                           | 36 |

| DeepSleep Mode.                                                      | 36 |

Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **TABLE OF CONTENTS (CONTINUED)**

| Backup Mode                               | 6  |

|-------------------------------------------|----|

| Wake-up Sources                           | 6  |

| Real-Time Clock                           | 7  |

| CRC Module                                | 7  |

| Programmable Timers                       | 7  |

| 32-Bit Timer/Counter/PWM (TMR) 3          | 7  |

| Watchdog Timer (WDT)                      | 8  |

| Pulse Train Engine (PT)                   | 8  |

| HTIMER                                    | 9  |

| Serial Peripherals                        | 9  |

| USB Controller                            | 9  |

| Audio Interface                           | 9  |

| I <sup>2</sup> C Interface                | 9  |

| Serial Peripheral Interface               | 0  |

| SPI Execute in Place (SPIX) Master 4      | 0  |

| UART                                      | 0  |

| 1-Wire Master (OWM)                       | 1  |

| Standard DMA Controller                   | 1  |

| Trusted Protection Unit (TPU)             | 1  |

| True Random Number Generator (TRNG) 4     | 2  |

| MAA                                       | 2  |

| AES                                       | 2  |

| SHA-2                                     | 2  |

| Memory Decryption Integrity Unit (MDIU) 4 | 2  |

| Secure Bootloader                         | 2  |

| Applications Information 4                | .3 |

| Bypass Capacitors                         | .3 |

| Transmitted Spurious Emissions            | .3 |

| GPIO and Alternate Function Matrix 4      | .3 |

| Ordering Information                      | 5  |

| Revision History 4                        | 6  |

Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **LIST OF FIGURES**

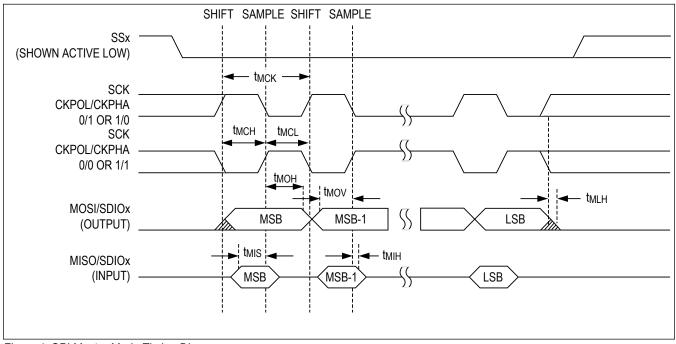

| Figure 1. SPI Master Mode Timing Diagram       | 22 |

|------------------------------------------------|----|

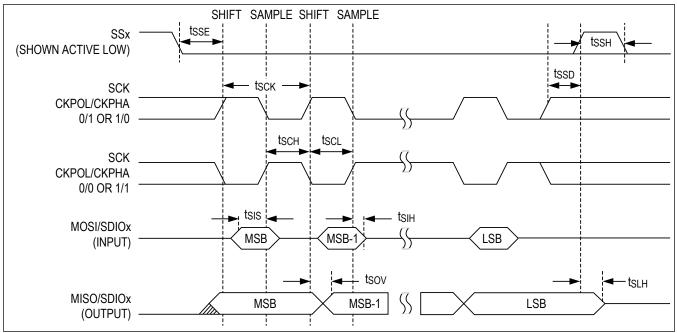

| Figure 2. SPI Slave Mode Timing Diagram        | 22 |

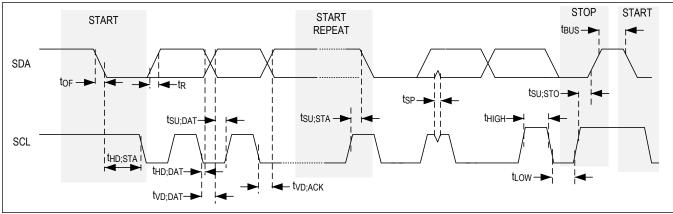

| Figure 3. I <sup>2</sup> C Timing Diagram      | 23 |

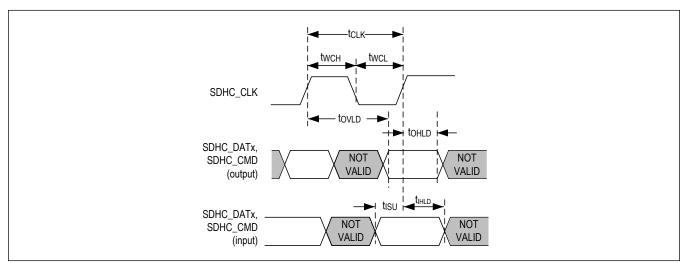

| Figure 4. SD/SDIO/SDHC/MMC Timing Diagram      | 23 |

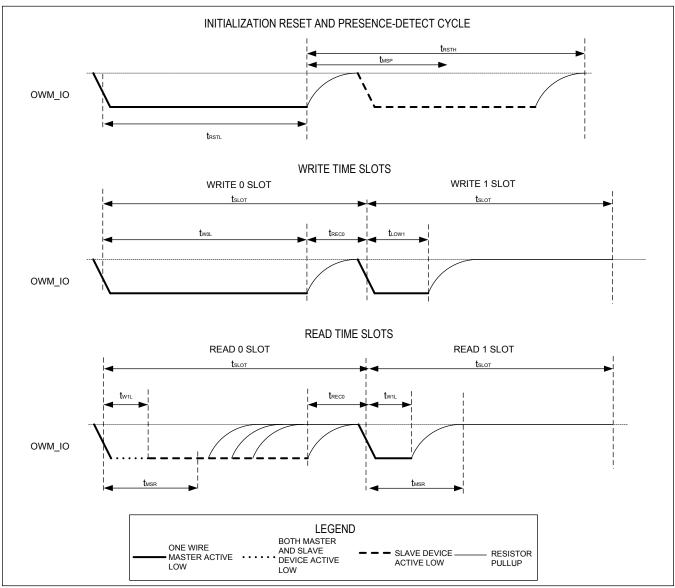

| Figure 5. One-Wire Master Data Timing Diagram. | 24 |

| Figure 6. Clocking Scheme Diagram.             | 34 |

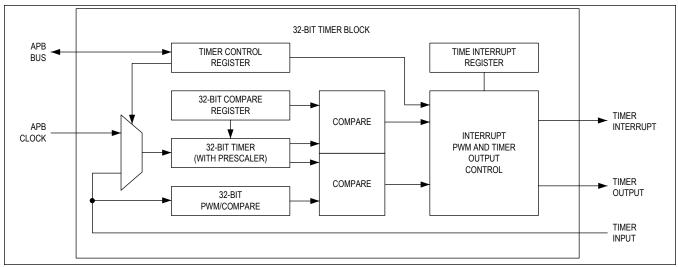

| Figure 7. 32-Bit Timer                         | 38 |

Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## LIST OF TABLES

| Table 1. Wake-up Sources                    | 36 |

|---------------------------------------------|----|

| Table 2. SPI Configuration Options          | 40 |

| Table 3. UART Configuration Options         | 41 |

| Table 4. GPIO and Alternate Function Matrix | 43 |

# Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Absolute Maximum Ratings**

| V <sub>COREA</sub>                                   |                                   |

|------------------------------------------------------|-----------------------------------|

| V <sub>COREB</sub>                                   |                                   |

| V <sub>DDA</sub>                                     |                                   |

| V <sub>DDIO</sub>                                    |                                   |

| V <sub>DDIOH</sub>                                   | 0.3V to +3.6V                     |

| V <sub>REGI</sub>                                    | 0.3V to +3.6V                     |

| V <sub>TXIN</sub>                                    |                                   |

| V <sub>RXIN</sub>                                    | 0.3V to +1.9V                     |

| V <sub>DDA BT[1:5]</sub>                             |                                   |

| RSTN, GPIO (V <sub>DDIO</sub> )                      | 0.3V to V <sub>DDIO</sub> + 0.5V  |

| GPIO (V <sub>DDIOH</sub> )                           | 0.3V to V <sub>DDIOH</sub> + 0.5V |

| 32KIN, 32KOUT                                        | 0.3V to V <sub>DDA</sub> + 0.2V   |

| HFXIN, HFXOUT                                        | 0.3V to V <sub>DDA</sub> + 0.2V   |

| AIN[7:0]                                             | 0.3V to +3.6V                     |

| V <sub>DDB</sub> (with respect to V <sub>SSB</sub> ) |                                   |

| DM, DP (with respect to V <sub>SSB</sub> )            |                   |

|-------------------------------------------------------|-------------------|

| V <sub>DDIO</sub> Combined Pins (sink)                | 100mA             |

| V <sub>DDIOH</sub> Combined Pins (sink)               | 100mA             |

| V <sub>SSA</sub>                                      |                   |

| V <sub>SS</sub>                                       |                   |

| V <sub>SSPWR</sub>                                    | 100mA             |

| V <sub>SSA BT[1:5]</sub>                              | 100mA             |

| Output Current (sink) by Any GPIO Pin                 |                   |

| Output Current (source) by Any GPIO Pin               | 25mA              |

| Continuous Package Power Dissipation                  | CTBGA (multilayer |

| board) T <sub>A</sub> = +70°C (derate 31.0mW/°C above | e +70°C)1692mW    |

| Operating Temperature Range                           | 40°C to +105°C    |

| Storage Temperature Range                             |                   |

| Soldering Temperature                                 | +260°C            |

|                                                       |                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 109 WLP

| Package Code                                               | W1093A4+1        |  |  |

|------------------------------------------------------------|------------------|--|--|

| Outline Number                                             | <u>21-100301</u> |  |  |

| Land Pattern Number         Refer to Application Note 1891 |                  |  |  |

| Thermal Resistance, Four-Layer Board:                      |                  |  |  |

| Junction to Ambient (0 <sub>JA</sub> )                     | 38.05°C/W        |  |  |

| Junction to Case ( $\theta_{JC}$ )                         | N/A              |  |  |

## 121 CTBGA

| Package Code                           | X12188+6C      |  |  |

|----------------------------------------|----------------|--|--|

| Outline Number                         | <u>21-0680</u> |  |  |

| Land Pattern Number                    | <u>90-0451</u> |  |  |

| Thermal Resistance, Four-Layer Board:  |                |  |  |

| Junction to Ambient (0 <sub>JA</sub> ) | 32.5°C/W       |  |  |

| Junction to Case $(\theta_{JC})$       | 8.8°C/W        |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics**

| PARAMETER                                 | SYMBOL                | CONDITIONS                                                                                                                                                                                                                                                                                                                     | MIN                                    | TYP   | MAX  | UNITS  |  |

|-------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------|------|--------|--|

| POWER SUPPLIES                            |                       |                                                                                                                                                                                                                                                                                                                                |                                        |       |      |        |  |

| Core Input Supply<br>Voltage A            | V <sub>COREA</sub>    |                                                                                                                                                                                                                                                                                                                                | V <sub>COREA</sub><br>V <sub>RST</sub> | 1.1   | 1.21 | V      |  |

| Core Input Supply<br>Voltage B            | V <sub>COREB</sub>    |                                                                                                                                                                                                                                                                                                                                | V <sub>COREB</sub><br>V <sub>RST</sub> | 1.1   | 1.21 | V      |  |

| Input Supply Voltage,<br>Analog           | V <sub>DDA</sub>      |                                                                                                                                                                                                                                                                                                                                | 1.71                                   | 1.8   | 1.89 | V      |  |

| Input Supply Voltage,<br>TXIN             | V <sub>TXIN</sub>     | Bluetooth Transmitter Supply                                                                                                                                                                                                                                                                                                   | 1.1                                    | 1.3   | 1.9  | V      |  |

| Input Supply Voltage,<br>RXIN             | V <sub>RXIN</sub>     | Bluetooth Receiver Supply                                                                                                                                                                                                                                                                                                      | 1.1                                    | 1.3   | 1.9  | V      |  |

| Input Supply Voltage,                     | V <sub>REGI</sub>     |                                                                                                                                                                                                                                                                                                                                | 2.0                                    | 2.7   | 3.6  | - v    |  |

| Battery                                   | V <sub>REGI_POR</sub> |                                                                                                                                                                                                                                                                                                                                | 2.4                                    |       |      | v      |  |

| Input Supply Voltage,<br>GPIO             | V <sub>DDIO</sub>     |                                                                                                                                                                                                                                                                                                                                | 1.71                                   | 1.8   | 1.89 | V      |  |

| Input Supply Voltage,<br>GPIO (High)      | V <sub>DDIOH</sub>    |                                                                                                                                                                                                                                                                                                                                | 1.71                                   | 1.8   | 3.6  | V      |  |

|                                           |                       | Monitors V <sub>COREA</sub>                                                                                                                                                                                                                                                                                                    | 0.72                                   | 0.77  |      |        |  |

|                                           |                       | Monitors V <sub>COREB</sub>                                                                                                                                                                                                                                                                                                    | 0.72                                   | 0.77  |      | _      |  |

|                                           |                       | Monitors V <sub>DDA</sub>                                                                                                                                                                                                                                                                                                      | 1.60                                   | 1.65  | 1.69 |        |  |

|                                           |                       | Monitors V <sub>DDB</sub>                                                                                                                                                                                                                                                                                                      | 2.81                                   | 2.91  |      |        |  |

| Power-Fail Reset<br>Voltage               | V <sub>RST</sub>      | Monitors V <sub>DDIO</sub>                                                                                                                                                                                                                                                                                                     | 1.60                                   | 1.65  | 1.69 | V      |  |

|                                           |                       | Monitors V <sub>DDIOH</sub>                                                                                                                                                                                                                                                                                                    | 1.60                                   | 1.65  | 1.69 |        |  |

|                                           |                       | Monitors V <sub>REGI</sub>                                                                                                                                                                                                                                                                                                     | 1.94                                   |       | 2.08 |        |  |

|                                           |                       | Monitors V <sub>TXOUT</sub>                                                                                                                                                                                                                                                                                                    |                                        | 0.773 |      | 1      |  |

|                                           |                       | Monitors V <sub>RXOUT</sub>                                                                                                                                                                                                                                                                                                    |                                        | 0.773 |      |        |  |

| Power-On Reset<br>Voltage                 | V <sub>POR</sub>      | Monitors V <sub>COREA</sub>                                                                                                                                                                                                                                                                                                    |                                        | 0.63  |      | V      |  |

| -                                         | IREGI_ACT             | Total current into $V_{REGI}$ pins, $f_{SYS}_{CLK}$ = 96MHz, $V_{REGI}$ = 3.3V, CPU0 in Active mode, executing While(1) from cache, inputs tied to $V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ , outputs source/sink 0mA                                                                                                            |                                        | 3.3   |      | mA     |  |

| V <sub>REGI</sub> Current, Active<br>Mode | IREGI_SLOPE           | This parameter is the slope of a line<br>which includes the point $I_{REGI\_ACT}$ and a<br>non-zero y-intercept. $V_{REGI} = 3.3V$ ,<br>$f_{SYS\_CLK}$ is changed only. DVS off.<br>CPU0 in Active mode, executing While(1)<br>from cache, inputs tied to $V_{SS}$ , $V_{DDIO}$ , or<br>$V_{DDIOH}$ , outputs source/sink 0mA. |                                        | 27.3  |      | µA/MHz |  |

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics (continued)**

| PARAMETER                                          | SYMBOL                           | COND                                                                                                                            | ITIONS                                        | MIN                                           | TYP                | MAX    | UNITS |  |

|----------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------|--------|-------|--|

| V <sub>REGI</sub> Current, Sleep<br>Mode           | IREGI_SLP                        | Total current into V <sub>R</sub><br>96MHz, V <sub>REGI</sub> = 3.3<br>mode, inputs tied to<br>V <sub>DDIOH</sub> , outputs sou | V <sub>SS</sub> , V <sub>DDIO</sub> , or      | 2.1                                           |                    |        | mA    |  |

|                                                    |                                  |                                                                                                                                 | RTC enabled, full memory retention            |                                               | 8.6                |        |       |  |

|                                                    |                                  |                                                                                                                                 | RTC enabled, no memory retention              |                                               | 1.6                |        |       |  |

|                                                    |                                  | Total current into<br>V <sub>REGI</sub> pins, V <sub>REGI</sub>                                                                 | RTC disabled, no memory retention             |                                               | 1.2                |        |       |  |

| V <sub>REGI</sub> Current, Backup<br>Mode          | I <sub>REGI_BK</sub>             | = 3.3V, inputs tied<br>to V <sub>SS</sub> , V <sub>DDIO</sub> , or                                                              | RTC disabled, full memory retention           |                                               | 8.4                |        | μA    |  |

|                                                    |                                  | V <sub>DDIOH</sub> , outputs<br>source/sink 0mA                                                                                 | RTC disabled,<br>32KB ECC memory<br>retention |                                               | 6.3                |        |       |  |

|                                                    |                                  |                                                                                                                                 |                                               | RTC disabled,<br>64KB ECC memory<br>retention |                    | 6.3    |       |  |

| V <sub>REGI</sub> Fixed Current,<br>DeepSleep Mode | IREGI_FDSL                       | Standby state with full retention                                                                                               |                                               |                                               | 10.0               |        | μA    |  |

| V <sub>REGO_X</sub> Output<br>Current              | V <sub>REGO_X_IOU</sub><br>T     | Output current for each of the V <sub>REGO_X</sub> outputs                                                                      |                                               |                                               | 5                  | 50     | mA    |  |

| V <sub>REGO_X</sub> Output<br>Current Combined     | V <sub>REGO_X_IOU</sub><br>T_TOT | All four V <sub>REGO_X</sub> outputs combined                                                                                   |                                               |                                               | 15                 | 100    | mA    |  |

| V <sub>REGO_X</sub> Output<br>Voltage Range        | V <sub>REGO_X_RA</sub><br>NGE    | V <sub>REGI</sub> ≥V <sub>REGO_X</sub> +                                                                                        | · 200mV                                       | 0.5                                           | 1.0                | 1.85   | V     |  |

| V <sub>REGO_X</sub> Efficiency                     | V <sub>REGO_X_EFF</sub>          | V <sub>REGI</sub> = 2.7V, V <sub>REG</sub><br>30mA                                                                              | <sub>;O_X</sub> = 1.1 V, load =               |                                               | 90                 |        | %     |  |

| CLOCKS                                             |                                  |                                                                                                                                 |                                               |                                               |                    |        |       |  |

| System Clock<br>Frequency                          | fsys_clk                         |                                                                                                                                 |                                               | 8                                             |                    | 96,000 | kHz   |  |

| System Clock Period                                | <sup>t</sup> sys_clk             |                                                                                                                                 |                                               |                                               | 1/<br>fsys_cl<br>K |        | ns    |  |

| High-Speed Oscillator<br>Frequency                 | fhsclk                           | Factory default, user adjustable<br>50MHz–96MHz                                                                                 |                                               | 92.5                                          | 96                 | 99.6   | MHz   |  |

| Low-Power Oscillator<br>Frequency                  | flpclk                           |                                                                                                                                 |                                               |                                               | 60                 |        | MHz   |  |

| RF Oscillator Frequency                            | frfclk                           | 32MHz crystal, $C_L = C_0 \le 7pF$ , temperatu initial tolerance ±20p                                                           | re stability ±20ppm,                          |                                               | 32                 |        | MHz   |  |

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics (continued)**

| PARAMETER                          | SYMBOL               | CONDITIONS                                                                  | MIN                         | TYP                         | MAX                         | UNITS |  |

|------------------------------------|----------------------|-----------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-------|--|

| HFXIN, HFXOUT Input<br>Capacitance | C <sub>HFX_PIN</sub> |                                                                             |                             | 6                           |                             | pF    |  |

| 7MHz Oscillator<br>Frequency       | <sup>f</sup> 7MCLK   |                                                                             |                             | 7.3728                      |                             | MHz   |  |

| RTC Input Frequency                | f <sub>32KIN</sub>   | 32kHz watch crystal, C <sub>L</sub> = 6pF, ESR < 90kΩ, C <sub>0</sub> ≤ 2pF |                             | 32.768                      |                             | kHz   |  |

| RTC Operating Current              | IRTC_BDSLP           | Backup or DeepSleep mode                                                    |                             | 0.39                        |                             | μA    |  |

| RTC Power-Up Time                  | <sup>t</sup> RTC_ON  |                                                                             |                             | 250                         |                             | ms    |  |

| Nano-ring Oscillator<br>Frequency  | f <sub>NANO</sub>    |                                                                             |                             | 8                           |                             | kHz   |  |

| GENERAL-PURPOSE I/C                | )                    |                                                                             | •                           |                             |                             |       |  |

| Input Low Voltage for All          | VIL_VDDIO            | V <sub>DDIO</sub> selected as I/O supply                                    |                             |                             | 0.3 ×<br>V <sub>DDIO</sub>  |       |  |

| GPIO                               | VIL_VDDIOH           | V <sub>DDIOH</sub> selected as I/O supply                                   |                             |                             | 0.3 ×<br>V <sub>DDIOH</sub> | V     |  |

| Input Low Voltage for RSTN         | V <sub>IL_RSTN</sub> |                                                                             |                             | 0.5 x<br>V <sub>COREA</sub> |                             | V     |  |

| Input High Voltage for             | VIH_VDDIO            | V <sub>DDIO</sub> selected as I/O supply                                    | 0.7 ×<br>V <sub>DDIO</sub>  |                             |                             |       |  |

| Ali GPIO                           | VIH_VDDIOH           | V <sub>DDIOH</sub> selected as I/O supply                                   | 0.7 ×<br>V <sub>DDIOH</sub> |                             |                             | V     |  |

| Input High Voltage for<br>RSTN     | VIH_RSTN             |                                                                             |                             | 0.5 x<br>V <sub>COREA</sub> |                             | V     |  |

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics (continued)**

| PARAMETER                           | SYMBOL                                                                       | CONDITIONS                                                                                                                 | MIN | TYP | MAX | UNITS |

|-------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

|                                     |                                                                              | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, GPIOn_DS_SEL[1:0] = 00, I <sub>OL</sub> = 1mA                       |     | 0.2 | 0.4 |       |

|                                     | Manager                                                                      | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, GPIOn_DS_SEL[1:0] = 01, I <sub>OL</sub> = 2mA                       |     | 0.2 | 0.4 |       |

|                                     | VOL_VDDIO                                                                    | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, GPIOn_DS_SEL[1:0] = 10, I <sub>OL</sub> = 4mA                       |     | 0.2 | 0.4 |       |

| Output Low Voltage for<br>All GPIO  |                                                                              | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, GPIOn_DS_SEL[1:0] = 11, I <sub>OL</sub> = 8mA                       |     | 0.2 | 0.4 | v     |

|                                     |                                                                              | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 00, I <sub>OL</sub><br>= 1mA |     | 0.2 | 0.4 | V     |

|                                     |                                                                              | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 01, I <sub>OL</sub><br>= 2mA |     | 0.2 | 0.4 |       |

|                                     | = 1.71V, GPIOn_DS_SEL[1:<br>= 4mA<br>V <sub>DDIOH</sub> selected as I/O supp | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 10, I <sub>OL</sub><br>= 4mA |     | 0.2 | 0.4 |       |

|                                     |                                                                              | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 11, I <sub>OL</sub><br>= 8mA |     | 0.2 | 0.4 |       |

| Combined I <sub>OL</sub> , All GPIO | IOL_TOTAL                                                                    |                                                                                                                            |     |     | 48  | mA    |

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics (continued)**

| PARAMETER                           | SYMBOL            | CONDITIONS                                                                                                                    | MIN                         | TYP | MAX  | UNITS |

|-------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|------|-------|

|                                     |                   | V <sub>DDIO</sub> selected as I/O supply, V <sub>DDIO</sub> = 1.71V, GPIOn_DS_SEL[1:0] = 00, I <sub>OL</sub> = -1mA           | V <sub>DDIO</sub> -<br>0.4  |     |      |       |

|                                     |                   | V <sub>DDIO</sub> selected as I/O supply, V <sub>DDIO</sub> = 1.71V, GPIOn_DS_SEL[1:0] = 01, I <sub>OL</sub> = -2mA           | V <sub>DDIO</sub> -<br>0.4  |     |      |       |

|                                     | Voh_vddio         | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, GPIOn_DS_SEL[1:0] = 10, I <sub>OL</sub> = -4mA                         | V <sub>DDIO</sub> -<br>0.4  |     |      |       |

| Output High Voltage for             |                   | V <sub>DDIO</sub> selected as I/O supply, V <sub>DDIO</sub> = 1.71V, GPIOn_DS_SEL[1:0] = 11, I <sub>OL</sub> = -8mA           | V <sub>DDIO</sub> -<br>0.4  |     |      | v     |

| All GPIO                            | Voh_vddioh -      | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 00, I <sub>OL</sub><br>= -1mA   | V <sub>DDIOH</sub><br>- 0.4 |     |      | V     |

|                                     |                   | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 01, I <sub>OL</sub><br>= -2mA   | V <sub>DDIOH</sub><br>- 0.4 |     |      |       |

|                                     |                   | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 10, I <sub>OL</sub><br>= -8mA   | V <sub>DDIOH</sub><br>- 0.4 |     |      |       |

|                                     |                   | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 11, I <sub>OL</sub><br>= -8mA   | V <sub>DDIOH</sub><br>- 0.4 |     |      |       |

| Combined I <sub>OH</sub> , All GPIO | IOH_TOTAL         |                                                                                                                               |                             |     | -48  | mA    |

| Input Hysteresis<br>(Schmitt)       | V <sub>IHYS</sub> |                                                                                                                               |                             | 300 |      | mV    |

| Input Leakage Current<br>Low        | IIL               | $V_{DDIO}$ = 1.89V, $V_{DDIOH}$ = 3.6V, $V_{DDIOH}$<br>selected as I/O supply, $V_{IN}$ = 0V, internal<br>pullup disabled     | -100                        |     | +100 | nA    |

|                                     | Ιн                | $V_{DDIO}$ = 1.89V, $V_{DDIOH}$ = 3.6V, $V_{DDIOH}$<br>selected as I/O supply, $V_{IN}$ = 3.6V,<br>internal pulldown disabled | -100                        |     | +100 | nA    |

| Input Leakage Current<br>High       | IOFF              | $V_{DDIO} = 0V, V_{DDIOH} = 0V, V_{DDIO}$<br>selected as I/O supply, $V_{IN} < 1.89V$                                         | -1                          |     | +1   |       |

|                                     | I <sub>IH3V</sub> | $V_{DDIO} = V_{DDIOH} = 1.71V, V_{DDIO}$<br>selected as I/O supply, $V_{IN} = 3.6V$                                           | -2                          |     | +2   | μA    |

| Input Pullup Resistor               | <b>D</b>          | P1M = 1                                                                                                                       |                             | 1   |      | MΩ    |

| RSTN                                | R <sub>PU_R</sub> | P1M = 0                                                                                                                       |                             | 25  |      | kΩ    |

| Input Pullup/Pulldown               | R <sub>PU1</sub>  | Normal resistance                                                                                                             |                             | 25  |      | kΩ    |

| Resistor for All GPIO               | R <sub>PU2</sub>  | Highest resistance                                                                                                            |                             | 1   |      | MΩ    |

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics (continued)**

| PARAMETER                                                     | SYMBOL                  | CONDITIONS                                                                                                  | MIN                                   | TYP                       | MAX                                    | UNITS           |  |

|---------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------|----------------------------------------|-----------------|--|

| BLUETOOTH RADIO / P                                           | OWER                    |                                                                                                             |                                       |                           |                                        |                 |  |

| Bluetooth Supply<br>Voltage LNA/Mixer                         | V <sub>DDA_BT1</sub>    | Internal LDO disabled.                                                                                      | 0.855                                 | 0.9                       | 0.945                                  | V               |  |

| Bluetooth Supply<br>Voltage Power Amplifier                   | V <sub>DDA_BT2</sub>    | Internal LDO disabled.                                                                                      | 0.9                                   |                           | 1.2                                    | V               |  |

| Bluetooth Supply<br>Voltage FRAC_N<br>Divider                 | V <sub>DDA_BT3</sub>    | Internal LDO disabled.                                                                                      | 0.855                                 | 0.9                       | 0.945                                  | v               |  |

| Bluetooth Supply<br>Voltage Receiver<br>Baseband              | V <sub>DDA_BT4</sub>    | Internal LDO disabled.                                                                                      | 0.855                                 | 0.9                       | 0.945                                  | v               |  |

| Bluetooth Supply<br>Voltage Voltage-<br>Controlled Oscillator | V <sub>DDA_BT5</sub>    | Internal LDO disabled.                                                                                      | 0.855                                 | 0.9                       | 0.945                                  | v               |  |

| BLUETOOTH RADIO / F                                           | REQUENCY                |                                                                                                             |                                       |                           |                                        |                 |  |

| Operating Frequency                                           |                         | 1MHz channel spacing                                                                                        | 2360                                  |                           | 2500                                   | MHz             |  |

| PLL Programming<br>Resolution                                 | PLL <sub>RES</sub>      |                                                                                                             |                                       | 1                         |                                        | MHz             |  |

| Frequency Deviation at<br>1MBPS                               | $\Delta f_{1MHz}$       |                                                                                                             |                                       | ±170                      |                                        | kHz             |  |

| Frequency Deviation at BLE 1MBPS                              | Δf <sub>BLE1MHz</sub>   |                                                                                                             |                                       | ±250                      |                                        | kHz             |  |

| Frequency Deviation at 2MBPS                                  | Δf <sub>2MHz</sub>      |                                                                                                             |                                       | ±320                      |                                        | kHz             |  |

| Frequency Deviation at BLE 2MBPS                              | Δf <sub>BLE2MHz</sub>   |                                                                                                             |                                       | ±500                      |                                        | kHz             |  |

| BLUETOOTH RADIO / C<br>60MHz, BLE stack runni<br>Sleep mode.) | URRENT CONSI            | UMPTION (SIMO enabled, V <sub>REGI</sub> = 3.3V. Lo<br>I hardware. Measured at the V <sub>REGI</sub> device | ow power o<br>pin, V <sub>REG</sub> ( | scillator e<br>D_B = 0.9V | nabled, f <sub>SY</sub><br>. CPU0 in D | S_CLK =<br>leep |  |

|                                                               | I <sub>TX_+4.5DBM</sub> | P <sub>RF</sub> = +4.5dBm                                                                                   |                                       | 6.00                      |                                        |                 |  |

|                                                               | ITX_0DBM                | P <sub>RF</sub> = 0dBm                                                                                      |                                       | 4.30                      |                                        |                 |  |

| Tx Run Current                                                | ITX10DBM                | P <sub>RF</sub> = -10dBm                                                                                    |                                       | 3.22                      |                                        | mA              |  |

|                                                               | I <sub>TX12DBM</sub>    | P <sub>RF</sub> = -12dBm                                                                                    |                                       | 3.05                      |                                        |                 |  |

|                                                               | ITX16DBM                | P <sub>RF</sub> = -16dBm                                                                                    |                                       | 2.85                      |                                        | ]               |  |

|                                                               | ITX20DBM                | P <sub>RF</sub> = -20dBm                                                                                    |                                       | 2.80                      |                                        |                 |  |

| Tx Startup Current                                            | ISTART_TX               |                                                                                                             |                                       | 1.40                      |                                        | mA              |  |

| Rx Run Current                                                | I <sub>RX_1M</sub>      | f <sub>RX</sub> = 1Mbps                                                                                     |                                       | 3.20                      |                                        |                 |  |

|                                                               | I <sub>RX_2M</sub>      | f <sub>RX</sub> = 2Mbps                                                                                     | 3.30                                  |                           |                                        | - mA            |  |

| Rx Startup Current                                            | I <sub>START_RX</sub>   |                                                                                                             |                                       | 1.40                      |                                        | mA              |  |

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics (continued)**

| PARAMETER                                                                    | SYMBOL               | CONDITIONS              | MIN TYP M | AX UNITS |

|------------------------------------------------------------------------------|----------------------|-------------------------|-----------|----------|

| BLUETOOTH RADIO / TI                                                         | RANSMITTER           |                         |           |          |

| Maximum Output Power                                                         | P <sub>RF</sub>      |                         | +4.5      | dBm      |

| RF Power Accuracy                                                            | P <sub>RF_ACC</sub>  |                         | ±1        | dB       |

| First Adjacent Channel<br>Transmit Power ±2MHz                               | P <sub>RF1_1</sub>   | 2Mbps BLE               | -31.7     | dBc      |

| Second Adjacent<br>Channel Transmit<br>Power ±4MHz                           | P <sub>RF2_1</sub>   | 2Mbps BLE               | -49.1     | dBc      |

| BLUETOOTH RADIO / R                                                          | ECEIVER              | •                       |           |          |

| Maximum Received<br>Signal Strength at <<br>0.1% PER                         | P <sub>RX_MAX</sub>  |                         | 0         | dBm      |

| Receiver Sensitivity,                                                        | D                    | 1Mbps BLE               | -95       | dDaa     |

| Ideal Transmitter                                                            | P <sub>SENS_IT</sub> | 2Mbps BLE               | -92       | dBm      |

| Receiver Sensitivity,                                                        | P                    | 1Mbps BLE               | -94       | dDm      |

| Dirty Transmitter                                                            | P <sub>SENS_DT</sub> | 2Mbps BLE               | -91       | dBm      |

| Receiver Sensitivity,                                                        | D                    | 125kbps BLE             | -103      | dDm      |

| Long Range Coded                                                             | P <sub>SENS_LR</sub> | 500kbps BLE             | -101      | dBm      |

| C/I Cochannel                                                                | C/I <sub>1MHz</sub>  | 1Mbps BLE               | 8         | dB       |

| Chicochannei                                                                 | C/I <sub>2Mhz</sub>  | 2Mbps BLE               | 8         | uв       |

|                                                                              | C/I <sub>+1_1</sub>  | +1MHz offset, 1Mbps BLE | -1        | dBm      |

|                                                                              | C/I <sub>-1_1</sub>  | -1MHz offset, 1Mbps BLE | -2        | UDIII    |

|                                                                              | C/I <sub>+2_1</sub>  | +2MHz offset, 1Mbps BLE | -30.7     |          |

| A diagont Interference                                                       | C/I <sub>-2_1</sub>  | -2MHz offset, 1Mbps BLE | -32.3     |          |

| Adjacent Interference                                                        | C/I <sub>+2_2</sub>  | +2MHz offset, 2Mbps BLE | -1.7      | dB       |

|                                                                              | C/I_2_2              | -2MHz offset, 2Mbps BLE | -3        | UB       |

|                                                                              | C/I <sub>+4_2</sub>  | +4MHz offset, 2Mbps BLE | -25.3     |          |

|                                                                              | C/I_4_2              | -4MHz offset, 2Mbps BLE | -26.3     |          |

| Adjacent Interference,<br>(3+n) MHz Offset [n = 0,<br>1, 2,]                 | C/I <sub>3+MHZ</sub> | 1Mbps BLE               | -34.8     | dB       |

| Adjacent Interference,<br>(6+2n) MHz Offset [n =<br>0, 1, 2,]                | C/I <sub>6+MHZ</sub> | 2Mbps BLE               | -34.8     | dB       |

| Intermodulation<br>Performance, 1Mbps<br>BLE with 3MHz, 4MHz,<br>5MHz Offset | PIMD_1MBPS           | 1Mbps BLE               | -37.1     | dBm      |

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics (continued)**

| PARAMETER                                                                     | SYMBOL                | COND                                                        | ITIONS                                                                                 | MIN                        | TYP                 | MAX                 | UNITS |

|-------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------|---------------------|---------------------|-------|

| Intermodulation<br>Performance, 2Mbps<br>BLE with 6MHz, 8MHz,<br>10MHz Offset | PIMD_2MBPS            | 2Mbps BLE                                                   |                                                                                        |                            | -36.4               |                     | dBm   |

| Received Signal<br>Strength Indicator<br>Accuracy                             | RSSI <sub>ACC</sub>   |                                                             |                                                                                        |                            | +/- 3               |                     | dB    |

| Received Signal<br>Strength Indicator<br>Range                                | RSSI <sub>RANGE</sub> |                                                             |                                                                                        |                            | -95 to<br>-50       |                     | dB    |

| ADC (DELTA-SIGMA)                                                             |                       |                                                             |                                                                                        |                            |                     |                     |       |

| Resolution                                                                    |                       |                                                             |                                                                                        |                            | 10                  |                     | Bits  |

| ADC Clock Rate                                                                | <b>f</b> ACLK         |                                                             |                                                                                        | 0.1                        |                     | 8                   | MHz   |

| ADC Clock Period                                                              | t <sub>ACLK</sub>     |                                                             |                                                                                        |                            | 1/f <sub>ACLK</sub> |                     | μs    |

|                                                                               |                       | AIN[7:0],<br>ADC_DIVSEL =<br>[00],<br>ADC_CH_SEL =<br>[7:0] | REF_SEL = 0,<br>INPUT_SCALE = 0                                                        | V <sub>SSA</sub> +<br>0.05 |                     | V <sub>BG</sub>     |       |

|                                                                               |                       | AIN[7:0],<br>ADC_DIVSEL =<br>[01],<br>ADC_CH_SEL =<br>[7:0] | REF_SCALE = 0,<br>INPUT_SCALE = 0                                                      | V <sub>SSA</sub> +<br>0.05 |                     | 2 x V <sub>BG</sub> | V     |

| Input Voltage Range                                                           | Vain                  | AIN[7:0],<br>ADC_DIVSEL =<br>[10],<br>ADC_CH_SEL =<br>[7:0] | REF_SCALE = 0,<br>INPUT_SCALE =<br>0, V <sub>DDIOH</sub> selected<br>as the I/O supply | V <sub>SSA</sub> +<br>0.05 |                     | V <sub>DDIOH</sub>  | v     |

|                                                                               |                       | AIN[7:0],<br>ADC_DIVSEL =<br>[11],<br>ADC_CH_SEL =<br>[7:0] | REF_SEL = 0,<br>INPUT_SCALE =<br>0, V <sub>DDIOH</sub> selected<br>as the I/O supply   | V <sub>SSA</sub> +<br>0.05 |                     | V <sub>DDIOH</sub>  |       |

| Input Impedance                                                               | R <sub>AIN</sub>      |                                                             |                                                                                        |                            | 30                  |                     | kΩ    |

| Analog Input                                                                  | Cana                  | Fixed capacitance to                                        | V <sub>SSA</sub>                                                                       |                            | 1                   |                     | pF    |

| Capacitance                                                                   | C <sub>AIN</sub>      | Dynamically switche                                         | d capacitance                                                                          |                            | 250                 |                     | fF    |

| Integral Nonlinearity                                                         | INL                   | Measured at 25°C, I temperature drift due                   |                                                                                        |                            |                     | ±2                  | LSb   |

| Differential Nonlinearity                                                     | DNL                   | Measured at 25°C, I temperature drift due                   |                                                                                        |                            |                     | ±1                  | LSb   |

| Offset Error                                                                  | V <sub>OS</sub>       |                                                             |                                                                                        |                            | ±1                  |                     | LSb   |

## Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics (continued)**

| PARAMETER                                  | SYMBOL               | CONDITIONS                                                         | MIN | TYP     | MAX              | UNITS             |

|--------------------------------------------|----------------------|--------------------------------------------------------------------|-----|---------|------------------|-------------------|

| ADC Active Current                         | I <sub>ADC</sub>     | ADC active, reference buffer enabled, input buffer disabled        |     | 210     |                  | μA                |

| ADC Setup Time                             | <sup>t</sup> ADC_SU  | Any power-up of ADC clock or ADC bias<br>to CpuAdcStart            |     |         | 10               | μs                |

| ADC Output Latency                         | t <sub>ADC</sub>     |                                                                    |     | 1067    |                  | t <sub>ACLK</sub> |

| ADC Sample Rate                            | f <sub>ADC</sub>     |                                                                    |     |         | 7.8              | ksps              |

| ADC Input Leakage                          | IADC_LEAK            | ADC inactive or channel not selected                               |     | 0.16    |                  | nA                |

| Full-Scale Voltage                         | V <sub>FS</sub>      | ADC code = 0x3FF                                                   |     | 1.2     |                  | V                 |

| Bandgap Temperature<br>Coefficient         | V <sub>TEMPCO</sub>  | Box method                                                         |     | 30      |                  | ppm               |

| COMPARATORS                                |                      | · · · · ·                                                          |     |         |                  | •                 |

| Input Offset Voltage                       | VOFFSET              |                                                                    |     | +/-1    |                  | mV                |

|                                            |                      | AINCOMPHYST[1:0] = 00                                              |     | ±23     |                  |                   |

|                                            | .,                   | AINCOMPHYST[1:0] = 01                                              |     | ±50     |                  | - mV              |

| Input Hysteresis                           | V <sub>HYST</sub>    | AINCOMPHYST[1:0] = 10                                              |     | ±2      |                  |                   |

|                                            |                      | AINCOMPHYST[1:0] = 11                                              |     | ±7      |                  |                   |

| Input Voltage Range                        | VIN_CMP              | Common-mode range                                                  | 0.6 |         | 1.35             | V                 |

| FLASH MEMORY                               |                      |                                                                    |     |         |                  | 1                 |

|                                            | t <sub>M_ERASE</sub> | Mass erase                                                         |     | 20      |                  |                   |

| Flash Erase Time                           | tp_erase             | Page erase                                                         |     | 20      |                  | ms                |

| Flash Programming<br>Time per Word         | t <sub>PROG</sub>    | 32-bit programming mode, f <sub>FLC_CLK</sub> = 1MHz               |     | 42      |                  | μs                |

| Flash Endurance                            |                      |                                                                    | 10  |         |                  | kcycles           |

| Data Retention                             | t <sub>RET</sub>     | T <sub>A</sub> = +85°C                                             | 10  |         |                  | years             |

| USB                                        |                      | · · · · ·                                                          |     |         |                  | •                 |

| USB Transceiver Supply Voltage             | V <sub>DDB</sub>     |                                                                    | 3.0 | 3.3     | 3.6              | v                 |

| Pin Capacitance (DP,<br>DM)                | C <sub>IN_USB</sub>  | Pin to $V_{SSB}$                                                   |     | 8       |                  | pF                |

| Driver Output<br>Resistance                | R <sub>DRV</sub>     | Steady state drive                                                 |     | 44 ±10% |                  | Ω                 |

| USB / FULL SPEED                           |                      | · · · · · ·                                                        |     |         |                  | •                 |

| Single-Ended Input High Voltage (DP, DM)   | VIH_USB              |                                                                    | 2.1 |         |                  | V                 |

| Single-Ended Input Low<br>Voltage (DP, DM) | V <sub>IL_USB</sub>  |                                                                    |     |         | 0.5              | V                 |

| Output High Voltage<br>(DP, DM)            | V <sub>OH_USB</sub>  | $R_L$ = 1.5k $\Omega$ from DP and DM to $V_{SSB},$ $I_{OH}$ = -4mA | 2.8 |         | V <sub>DDB</sub> | v                 |

# Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +105^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. GPIO are only tested at  $T_A = +105^{\circ}$ C.)

| PARAMETER                                               | SYMBOL              | CONDITIONS                                                        | MIN             | ТҮР          | MAX  | UNITS |

|---------------------------------------------------------|---------------------|-------------------------------------------------------------------|-----------------|--------------|------|-------|

| Output Low Voltage<br>(DP, DM)                          | V <sub>OL_USB</sub> | $R_L$ = 1.5kΩ from DP to V <sub>DDB</sub> , I <sub>OL</sub> = 4mA | V <sub>SS</sub> |              | 0.3  | V     |

| Differential Input<br>Sensitivity                       | V <sub>DI</sub>     | DP to DM ; system requirement, not tested                         | 0.2             |              |      | V     |

| Common-Mode Voltage<br>Range                            | V <sub>CM</sub>     | Includes V <sub>DI</sub> range; system requirement, not tested    | 0.8             |              | 2.5  | V     |

| Transition Time (Rise/<br>Fall) DP, DM                  | t <sub>RF</sub>     | C <sub>L</sub> = 50pF                                             | 4               |              | 20   | ns    |

| Pullup Resistor on<br>Upstream Ports                    | R <sub>PU</sub>     |                                                                   | 1.05            | 1.5          | 1.95 | kΩ    |

| USB / HI-SPEED                                          |                     |                                                                   |                 |              |      |       |

| Hi-Speed Data Signaling<br>Common-Mode Voltage<br>Range | V <sub>HSCM</sub>   |                                                                   | -50             |              | +500 | mV    |

| Hi-Speed Squelch                                        |                     | Squelch detected                                                  |                 | 100          |      |       |

| Detection Threshold                                     | V <sub>HSSQ</sub>   | No squelch detected                                               | 200             |              |      | mV    |

| Hi-Speed Idle Level<br>Output Voltage                   | V <sub>HSOI</sub>   |                                                                   | -10             |              | +10  | mV    |

| Hi-Speed Low-Level<br>Output Voltage                    | V <sub>HSOL</sub>   |                                                                   | -10             |              | +10  | mV    |

| Hi-Speed High-Level<br>Output Voltage                   | V <sub>HSOH</sub>   |                                                                   |                 | 400 ±40      |      | mV    |

| Chirp-J Output Voltage<br>(Differential)                | V <sub>CHIRPJ</sub> |                                                                   |                 | 900<br>±200  |      | mV    |

| Chirp-K Output Voltage<br>(Differential)                | V <sub>CHIRPK</sub> |                                                                   |                 | -700<br>±200 |      | mV    |

## **Electrical Characteristics—SPI**

| PARAMETER                                      | SYMBOL                              | CONDITIONS                                                                       | MIN                 | TYP                | MAX | UNITS |

|------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------|---------------------|--------------------|-----|-------|

| MASTER MODE                                    |                                     |                                                                                  |                     |                    |     |       |

| SPI Master Operating<br>Frequency              | fмск                                | f <sub>SYS_CLK</sub> = 96MHz, f <sub>MCK(MAX)</sub> =<br>f <sub>SYS_CLK</sub> /2 |                     |                    | 48  | MHz   |

| SPI Master SCK Period                          | t <sub>MCK</sub>                    |                                                                                  |                     | 1/f <sub>MCK</sub> |     | ns    |

| SCK Output Pulse-<br>Width High/Low            | t <sub>MCH</sub> , t <sub>MCL</sub> |                                                                                  | t <sub>MCK</sub> /2 |                    |     | ns    |

| MOSI Output Hold Time<br>After SCK Sample Edge | <sup>t</sup> мон                    |                                                                                  | t <sub>MCK</sub> /2 |                    |     | ns    |

| MOSI Output Valid to<br>Sample Edge            | t <sub>MOV</sub>                    |                                                                                  | t <sub>MCK</sub> /2 |                    |     | ns    |

# Low-Power Arm Cortex-M4 with FPU-Based Microcontroller with Bluetooth 5 for Wearables

## **Electrical Characteristics—SPI (continued)**

(TIming specifications are guaranteed by design and not production tested.)

| PARAMETER                                                | SYMBOL                              | CONDITIONS | MIN | TYP                 | MAX | UNITS |

|----------------------------------------------------------|-------------------------------------|------------|-----|---------------------|-----|-------|

| MOSI Output Hold Time<br>After SCK Low Idle              | t <sub>MLH</sub>                    |            |     | t <sub>MCK</sub> /2 |     | ns    |

| MISO Input Valid to<br>SCK Sample Edge<br>Setup          | t <sub>MIS</sub>                    |            |     | 5                   |     | ns    |