# Eight channel valve driver

#### Datasheet - production data

#### **Features**

- Eight protected low-side drivers with diagnostics

- Four 0.16  $\Omega$  (typ) low side outputs (Q1 Q4)

- Four 0.2  $\Omega$  (typ) PWM controlled outputs (Q5 Q8)

- All outputs with 35 V (min) zener clamp

- · Programmable output timer

- Clock monitor

- Integrated recirculation diodes (Q5-Q8 only)

- 16 bit serial peripheral interface (SPI), up to 5 MHz with diagnostics

- · Battery compatible supply voltage

- Detailed load diagnostics

- Over load protection

- Open load (off-state)

- Under current

- Under voltage

- Temperature warning and shutdown

- Power or signal GND loss

- Recirculation diode loss

- Silent valve driver test

## **Description**

The L9375TRLF is a SPI controlled octal channel low side driver with integrated recirculation diodes.

The output duty cycle (Q5 - Q8) can be programmed individually. It is possible to program two consecutive output duty cycles per channel as well as an individual duration time for each channel actuation (all channels).

Table 1. Device summary

| Order code | Package                | Packing |

|------------|------------------------|---------|

| L9375TRLF  | PowerSO-36 (slug down) | Tube    |

Contents L9375TRLF

# **Contents**

| 1 | Bloc | k diagra  | am                                                   | 8  |

|---|------|-----------|------------------------------------------------------|----|

| 2 | Pins | descrip   | otion                                                | 9  |

| 3 | Elec | trical sp | ecifications                                         | 11 |

|   | 3.1  | Absolu    | te maximum ratings                                   | 11 |

|   | 3.2  | ESD su    | usceptibility                                        | 12 |

|   |      | 3.2.1     | HBM                                                  | 12 |

|   |      | 3.2.2     | MM                                                   | 12 |

|   | 3.3  | Electric  | cal characteristics                                  | 12 |

|   |      | 3.3.1     | Supply current                                       | 12 |

|   |      | 3.3.2     | Output power stages                                  | 12 |

|   |      | 3.3.3     | Recirculation diode                                  |    |

|   |      | 3.3.4     | Output timing characteristics                        | 14 |

|   |      | 3.3.5     | Output configuration Q1 - Q4                         | 16 |

|   |      | 3.3.6     | Output configuration Q5 - Q8                         | 16 |

|   |      | 3.3.7     | Logic inputs / outputs                               | 17 |

|   |      | 3.3.8     | Logic outputs (MISO)                                 | 17 |

|   |      | 3.3.9     | Output stage diagnostic functions                    | 18 |

|   |      | 3.3.10    | General diagnostic functions                         | 18 |

|   |      | 3.3.11    | Filtering times                                      | 19 |

|   |      | 3.3.12    | Internal oscillator                                  | 19 |

|   |      | 3.3.13    | SPI timing characteristics SPICLK, MISO, MOSI, SPICS | 20 |

| 4 | Circ | uit desc  | ription                                              | 21 |

|   | 4.1  | SPI sei   | rial peripheral interface                            | 21 |

|   |      | 4.1.1     | General protocol                                     | 22 |

|   |      | 4.1.2     | SPI failure detection                                | 23 |

|   |      | 4.1.3     | Data transfer                                        | 23 |

|   |      | 4.1.4     | Address decoder                                      | 24 |

|   |      | 4.1.5     | Parity generator                                     | 24 |

|   |      | 4.1.6     | Initial MISO information                             | 24 |

|   |      | 4.1.7     | Register map                                         | 24 |

|   | 4.2  | Clock     |                                                      | 25 |

L9375TRLF Contents

|   |      | 4.2.1          | Clock multiplier                                           | 26 |

|---|------|----------------|------------------------------------------------------------|----|

|   |      | 4.2.2          | Internal oscillator                                        | 26 |

|   |      | 4.2.3          | CLKIN signal monitoring                                    | 26 |

|   | 4.3  | Synchr         | ronization controller                                      | 26 |

|   |      | 4.3.1          | Output synchronization                                     | 26 |

|   |      | 4.3.2          | Time shift between output actuation (Q5-Q8 only)           | 30 |

|   | 4.4  | Set-po         | int controller                                             | 31 |

|   | 4.5  | PWM g          | generator(Q5-Q8 only)                                      | 34 |

|   | 4.6  | Output         | driver                                                     | 34 |

|   |      | 4.6.1          | Output driver controls                                     | 35 |

|   |      | 4.6.2          | Diagnostics                                                | 35 |

|   | 4.7  | Diagno         | ostics                                                     | 37 |

|   |      | 4.7.1          | Undercurrent / openload                                    | 37 |

|   |      | 4.7.2          | Openload                                                   | 38 |

|   |      | 4.7.3          | Over current                                               | 38 |

|   |      | 4.7.4          | Thermal warning and thermal shutdown                       | 39 |

|   |      | 4.7.5          | Power ground loss (PGND-loss)                              | 40 |

|   |      | 4.7.6          | Signal ground loss (SGND-loss)                             | 40 |

|   |      | 4.7.7          | Recirculation diode loss detection (Dx-loss)(Q5 - Q8 only) | 40 |

|   |      | 4.7.8          | SPI-failure                                                | 40 |

|   |      | 4.7.9          | CLKIN-failure                                              | 41 |

|   |      | 4.7.10         | Sync-failure                                               |    |

|   |      | 4.7.11         | Silent valve driver test (SVDT)                            | 43 |

| 5 | Prog | ırammaı        | rs guide                                                   | 50 |

| 3 |      |                |                                                            |    |

|   | 5.1  |                | and registers                                              |    |

|   |      | 5.1.1<br>5.1.2 | Sync + Sync-trigger register (address 0)                   |    |

|   |      | 5.1.2          | Sync tolerance window (STW) register (address 1)           |    |

|   |      | 5.1.4          | Fast switch-on (FSON) register (address 3)                 |    |

|   |      | 5.1.5          | Duration registers (address 4, 5, 14, and 15)              |    |

|   |      | 5.1.6          | Duty cycle register (address 6 to 13)                      |    |

|   | 5.2  |                | registers                                                  |    |

|   | ٥.۷  | 5.2.1          | General status (address 0)                                 |    |

|   |      | 5.2.1          | Output status Q1 to Q8 (address 1 to 8)                    |    |

|   |      | 5.2.3          | Reserved (addresses 9 - 15)                                |    |

|   |      | 5.2.0          | 1.000.100 (4441.0000 0 10)                                 |    |

Contents L9375TRLF

| 6 | Regi | Register block functional overview 6                 |  |  |  |

|---|------|------------------------------------------------------|--|--|--|

|   | 6.1  | Input command register block overview (MOSI data) 60 |  |  |  |

|   |      | 6.1.1 Status register block overview (MISO data)     |  |  |  |

| 7 | Pack | kage information                                     |  |  |  |

| 8 | Revi | sion history                                         |  |  |  |

L9375TRLF List of tables

# List of tables

| Table 1.  | Device summary                                                      | . 1 |

|-----------|---------------------------------------------------------------------|-----|

| Table 2.  | Pins description                                                    | . 9 |

| Table 3.  | Absolute maximum ratings                                            | 11  |

| Table 4.  | HBM                                                                 | 12  |

| Table 5.  | MM                                                                  | 12  |

| Table 6.  | Supply current                                                      | 12  |

| Table 7.  | Output power stages                                                 | 13  |

| Table 8.  | Recirculation diode electrical characteristics (Q5-Q8)              | 14  |

| Table 9.  | Timing for outputs Q1 - Q4 (no edge shaping)                        | 14  |

| Table 10. | Output timing electrical characteristics (Q5-Q8)                    | 15  |

| Table 11. | Symmetric switching of DMOS electrical characteristics              |     |

| Table 12. | Q3 / Q4 (current controller) electrical characteristics             |     |

| Table 13. | PWM output behavior characteristics (Q5 - Q8)                       |     |

| Table 14. | Logic inputs electrical characteristics                             |     |

| Table 15. | Logic outputs (MISO) electrical characteristics                     |     |

| Table 16. | Diagnostic functions at output stage electrical characteristics     |     |

| Table 17. | General diagnostic functions electrical characteristics             |     |

| Table 18. | CLKIN-monitoring characteristics                                    |     |

| Table 19. | Failure filtering times characteristics                             | 19  |

| Table 20. | SVDT test timing (refer to 4.7.11: Silent valve driver test (SVDT)) |     |

| Table 21. | Internal oscillator electrical characteristics                      | 19  |

| Table 22. | SPI timing characteristics                                          |     |

| Table 23. | Command buffer (data_in)                                            |     |

| Table 24. | Status buffer (data_out)                                            |     |

| Table 25. | Clock validation                                                    |     |

| Table 26. | Sync. tolerance window interval length                              |     |

| Table 27. | Example of PWM duration timing, t(n)                                |     |

| Table 28. | Timer t(n) resolution versus RESET_VALUE MSB                        |     |

| Table 29. | Qx_ON and Qx_OFF provide gate voltage status history information    |     |

| Table 30. | Output driver possible input configuration                          |     |

| Table 31. | SPI failure Response data                                           |     |

| Table 32. | Fault diagnostic summary                                            |     |

| Table 33. | Status monitored during SVDT                                        |     |

| Table 34. | SVDT command                                                        |     |

| Table 35. | SVDT status                                                         |     |

| Table 36. | Sync + sync-trigger register                                        |     |

| Table 37. | STW value                                                           |     |

| Table 38. | Configuration register 1                                            |     |

| Table 39. | Silent valve driver test (SVDT)                                     |     |

| Table 40. | CLKIN_S                                                             |     |

| Table 41. | Fast switch off                                                     |     |

| Table 42. | Edge shaping                                                        |     |

| Table 43. | Fast switch-on.                                                     |     |

| Table 44. | Register duration value                                             |     |

| Table 45. | Duration bit resolution                                             |     |

| Table 46. | Duty cycle register (address 6 to 9)                                |     |

| Table 47. | Status registers                                                    |     |

| Table 48. | CLKIN_S command                                                     | 5/  |

| ist of tables | L9375TRLF |

|---------------|-----------|

| IST OF TABLES | L93/51RLF |

| Table 49. | Output status Q1 to Q8         | 58 |

|-----------|--------------------------------|----|

|           | Overview input register block  |    |

|           | Overview answer register block |    |

| Table 52. | Document revision history      | 64 |

L9375TRLF List of figures

# **List of figures**

| igure 1.  | Block diagram                                                    | 8  |

|-----------|------------------------------------------------------------------|----|

| igure 2.  | Pins connection (top view)                                       | 9  |

| igure 3.  | Output power stages Q1-Q4                                        |    |

| igure 4.  | Output power stages Q5-Q8                                        | 13 |

| igure 5.  | Output timing (Q1 - Q4)                                          |    |

| igure 6.  | Output timing characteristics diagram with edge shaping (Q5-Q8)I | 15 |

| igure 7.  | Symmetric switching of DMOS diagram                              |    |

| igure 8.  | Logic inputs                                                     | 17 |

| igure 9.  | Logic outputs (MISO) circuit                                     | 17 |

| igure 10. | SPI timing characteristics SPICLK, MISO, MOSI, SPICS             | 20 |

| igure 11. | SPI block diagram                                                | 21 |

| igure 12. | SPI error handling                                               |    |

| igure 13. | Clock block diagram                                              |    |

| igure 14. | Synchronization controller block diagram                         |    |

| igure 15. | Normal mode                                                      |    |

| igure 16. | Sync-failure + re-synchronization                                |    |

| igure 17. | Behavior of the output when the synchronization is done          |    |

| igure 18. | Channels time shift                                              |    |

| igure 19. | Set-point controller block diagram                               |    |

| igure 20. | Set-point control example                                        |    |

| igure 21. | Set point controller for Q1-Q4                                   |    |

| igure 22. | PWM control block diagram (Q5 - Q8 only)                         |    |

| igure 23. | Gate drive block diagram with power (Q5-Q8)                      |    |

| igure 24. | Gate drive block diagram with power (Q1-Q4)                      |    |

| igure 25. | Diagnosis block diagram                                          |    |

| igure 26. | Diagram under current                                            |    |

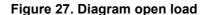

| igure 27. | Diagram open load                                                |    |

| igure 28. | Thermal detection / protection behavior                          |    |

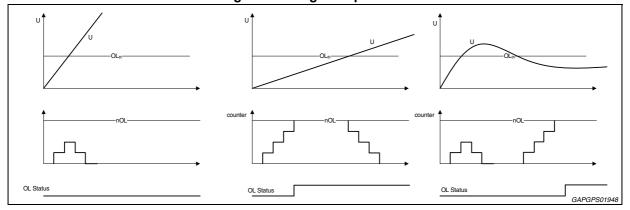

| igure 29. | Timing between each output tests                                 |    |

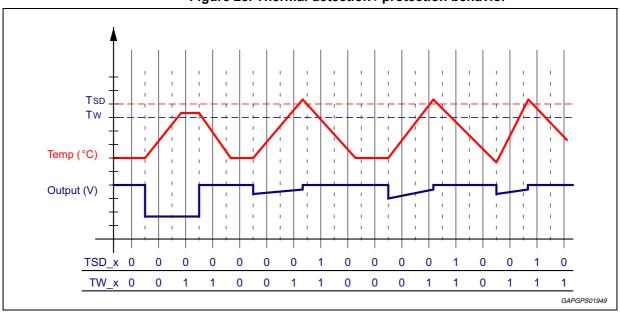

| igure 30. | SVDT-Timing with SPI-transfer                                    |    |

| igure 31. | Passing test diagram                                             |    |

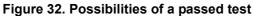

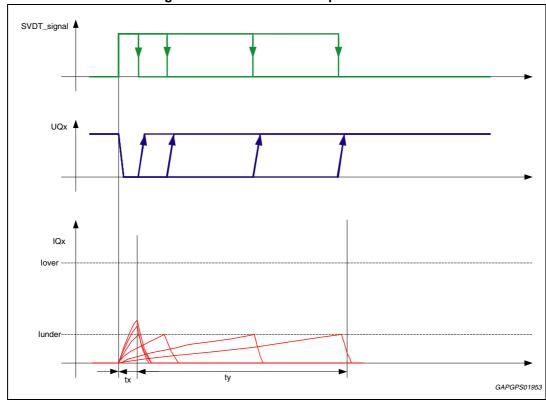

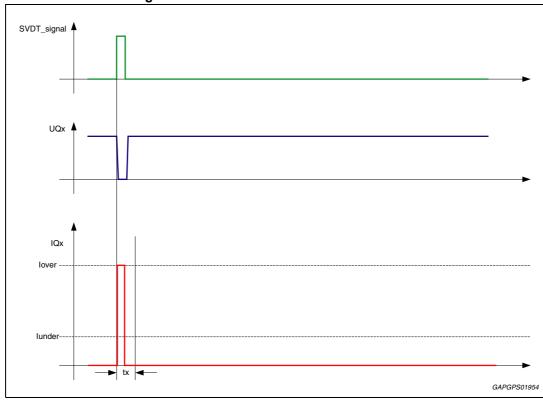

| igure 32. | Possibilities of a passed test                                   |    |

| igure 33. | Test failed: short circuit / overload                            |    |

| igure 34. | Test failed: high resistive load / undercurrent                  |    |

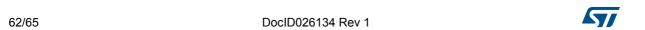

| igure 35. | PowerSO-36 (slug down) mechanical data and package dimensions    | 33 |

Block diagram L9375TRLF

# 1 Block diagram

Supply voltage P.O.R. Vs ⊠-**-**⊠ Q4 Thermal sense **-**⊠ Q3 Open load L\_Vs Over-current Under-current **-**⊠ Q2 Gate monitor -⊠ Q1 Gate driver SPICLK 🖾 SPI MOSI ⊠ 16 registers Synchronization controller MISO ⊠ 16-bit each **⊠** D7 Thermal sense SPICS ⊠ **-**⊠ Q7 Open load Dx loss Set-point controller **-**⊠ D5 Over-current Under-current **-**⊠ Q5 Gate monitor Gate Drive PWM ENABLE EN 🖾 Channel 8 Channel 6 controller Thermal sense CLKIN 🖾 -⊠ Q8 Open load Dx loss Set-point controller \_**→** 250kHz -⊠ D6/D8 Over-current Under-current **-**⊠ Q6 Gate monitor SGND / PGND SGND ⊠-PWM control -⊠ PGND -⊠ PGND GAPGPS01921

Figure 1. Block diagram

L9375TRLF Pins description

# 2 Pins description

0 NC [ 36 □ PGND 2 Q5 Q1 [ 35 3 34 Q5 Q1 D5 Q2 33 Q2 [ 5 32 D5 Q6 [ 6 31 SGND Q6 [ 7 30 ΕN NC E SPICS 8 29 D6/D8 [ MISO 28 D6/D8 [ 10 27 MOSI NC [ 11 26 **SPICLK** CLKIN Q8 [ 12 25 Q8 [ 13 24 ٧S 23 Q4 [ 14 D7 Q4 [ 22 D7 15 Q3 [ 16 21 Q7 Q3 [ 17 20 Q7 18 19 ☐ PGND NC [ GAPGPS01922

Figure 2. Pins connection (top view)

Table 2. Pins description

| Pin# | Name  | Description                        |  |

|------|-------|------------------------------------|--|

| 1    | N.C.  | Not connected                      |  |

| 2    | Q1    | Low side driver output 1           |  |

| 3    | Q1    | Low side driver output 1           |  |

| 4    | Q2    | Low side driver output 2           |  |

| 5    | Q2    | Low side driver output 2           |  |

| 6    | Q6    | Low side driver output 6           |  |

| 7    | Q6    | ow side driver output 6            |  |

| 8    | N.C.  | lot connected                      |  |

| 9    | D6/D8 | Output 6 and 8 recirculation diode |  |

| 10   | D6/D8 | Output 6 and 8 recirculation diode |  |

| 11   | N.C.  | Not connected                      |  |

| 12   | Q8    | Low side driver output 8           |  |

| 13   | Q8    | Low side driver output 8           |  |

| 14   | Q4    | Low side driver output 4           |  |

| 15   | Q4    | Low side driver output 4           |  |

| 16   | Q3    | Low side driver output 3           |  |

Pins description L9375TRLF

Table 2. Pins description (continued)

| Pin# | Name   | Description                               |  |

|------|--------|-------------------------------------------|--|

| 17   | Q3     | Low side driver output 3                  |  |

| 18   | N.C.   | Not connected                             |  |

| 19   | PGND   | Power ground                              |  |

| 20   | Q7     | Low side driver output 7                  |  |

| 21   | Q7     | Low side driver output 7                  |  |

| 22   | D7     | Output 7 recirculation diode              |  |

| 23   | D7     | Output 7 recirculation diode              |  |

| 24   | VS     | IC supply                                 |  |

| 25   | CLKIN  | recision clock input                      |  |

| 26   | SPICLK | PI communication clocK                    |  |

| 27   | MOSI   | Master out slave in for SPI communication |  |

| 28   | MISO   | Master in slave out for SPI communication |  |

| 29   | SPICS  | SPI chip select                           |  |

| 30   | EN     | Device Enable                             |  |

| 31   | SGND   | Signal ground                             |  |

| 32   | D5     | Output 5 recirculation diode              |  |

| 33   | D5     | Output 5 recirculation diode              |  |

| 34   | Q5     | Low side driver output 5                  |  |

| 35   | Q5     | Low side driver output 5                  |  |

| 36   | PGND   | Power ground                              |  |

# 3 Electrical specifications

# 3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol                                                                                                        | Parameter                                                                                                          | Min          | Max                   | Unit   |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|--------|

| V <sub>s</sub>                                                                                                | Supply voltage                                                                                                     | -0.3         | 38                    | V      |

| V <sub>Dx</sub>                                                                                               | Recirculation diode voltage  Continuous t<2 ms                                                                     | -0.3<br>-0.3 | 35<br>38              | V<br>V |

| V <sub>Qx</sub>                                                                                               | Output Voltage                                                                                                     | -0.3         | Internally<br>Clamped | V      |

| V <sub>EN</sub> V <sub>SPICLK</sub> V <sub>SPICS</sub> V <sub>MOSI</sub> V <sub>MISO</sub> V <sub>CLKIN</sub> | Enable voltage SPI clock voltage SPI chip select voltage SPI MOSI voltage SPI MISO voltage SPI clock input voltage | -0.3         | 6                     | V      |

| IQ                                                                                                            | Output current at reversal voltage                                                                                 |              | -2                    | Α      |

| I <sub>EN_CL</sub> I <sub>SPICLK_CL</sub> I <sub>SPICS_CL</sub> I <sub>MOSI_CL</sub> I <sub>CLKIN_CL</sub>    | Input clamping currents (static) Input clamping currents (dynamic)                                                 | - 3<br>-10   | + 3<br>+10            | mA     |

| T <sub>amb</sub>                                                                                              | Ambient operating temperature                                                                                      | -40          | +125                  | °C     |

Definition: Current flowing into the L9375TRLF are considered positive -> " + " Current flowing out of the L9375TRLF are considered negative -> " - "

Warning: Transients beyond this limit will cause currents into ESD structures which must be limited externally to  $\pm 10$  mA

(maximum energy to be dissipated: 2 mJ).

5/

# 3.2 ESD susceptibility

#### 3.2.1 HBM

ESD susceptibility HBM according to EIA/JESD 22-A 114B:

Table 4. HBM

| Pin                                           | Condition                                      | Min | Max | Unit |

|-----------------------------------------------|------------------------------------------------|-----|-----|------|

| All pins                                      | -                                              | ± 2 | -   | kV   |

| Output pins D <sub>X</sub> ; Q <sub>X</sub> ; | All PGND and SGND pins are connected together. | ± 4 | -   | kV   |

#### 3.2.2 MM

ESD susceptibility according to EIA/JESD 22-A 115A:

Table 5. MM

| Parameter          | Condition | Min   | Max | Unit |

|--------------------|-----------|-------|-----|------|

| Machine model (MM) | All pins  | ± 250 | -   | V    |

## 3.3 Electrical characteristics

$V_{S}$  = 5.2 to 20 V; -40 °C  $\leq$   $T_{j}1$   $\leq$  175 °C, unless other-wise specified.

Function is guaranteed until thermal shutdown threshold, T<sub>SD</sub>;

### 3.3.1 Supply current

Table 6. Supply current

| Symbol          | Parameter                      | Condition                                                 | Min           | Тур           | Max          | Unit     |

|-----------------|--------------------------------|-----------------------------------------------------------|---------------|---------------|--------------|----------|

| l <sub>VS</sub> | Supply current                 | V <sub>s</sub> = 13.5 V<br>@+175 °C<br>@+25 °C<br>@-40 °C | 4.0<br>-<br>- | -<br>7.5<br>- | -<br>-<br>10 | mA       |

| V <sub>s</sub>  | Supply voltage operating range | -                                                         | 5.2           | -             | 20           | <b>V</b> |

## 3.3.2 Output power stages

All output power stages consist of a MOSFET with accompanying protection/diagnostic circuitry. Outputs Q5 - Q8 have a recirculation diode as well for PWMming inductive loads.

Off-State Open Load

RPD

A to 1

NUX

From Other Outputs

Internal Signals

PGND

GAPGPS01924

Figure 3. Output power stages Q1-Q4

Table 7. Output power stages

| Symbol                                            | Parameter                                                                        | Condition                                                                                   | Min | Тур | Max      | Unit     |

|---------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|----------|----------|

| R <sub>ON</sub> (Q <sub>1</sub> -Q <sub>4</sub> ) | Static drain-source on-resistance Q <sub>1</sub> - Q4                            | I <sub>Q</sub> = 1 A<br>(TC: 0.58 %/K; Typ @ RT)                                            | 60  | 160 | 390      | mΩ       |

| R <sub>ON</sub> (Q <sub>5</sub> -Q <sub>8</sub> ) | Static drain-source on-resistance Q <sub>5</sub> - Q <sub>8</sub>                | I <sub>Q</sub> = 1 A<br>(TC: 0.58 %/K; Typ @ RT)                                            | 100 | 200 | 520      | mΩ       |

| V <sub>Z</sub>                                    | Z-diode clamping voltage                                                         | I <sub>Q</sub> = current limitation                                                         | 35  | -   | 40       | V        |

| R <sub>PD</sub>                                   | Output pull down resistor (multiplexed to 4 outputs sequentially) <sup>(1)</sup> | EN = 1                                                                                      | 20  | 40  | 100      | kΩ       |

| I <sub>LEAK</sub>                                 | Output leakage current                                                           | $V_Q = 20 \text{ V}; \text{ EN} = 0 \text{ V}$ $T_j = 140 \text{ °C}$ $T_j = 25 \text{ °C}$ | -   | 1   | 3<br>1.5 | μΑ<br>μΑ |

R<sub>PD</sub> is sequentially connected to each output for 2 μs (8 μs period) for the purpose of detecting off-state open load. There

are two R<sub>PDs</sub> and two 4:1 multiplexers, one for outputs Q1 -Q4 and another for outputs Q5 - Q8.

Off-State Open Load

RPD

A to 1

NUX

Outputs

Outputs

Outputs

Outputs

Outputs

Outputs

OAPGPS01925

Figure 4. Output power stages Q5-Q8

577

### 3.3.3 Recirculation diode

Table 8. Recirculation diode electrical characteristics (Q5-Q8)

| Symbol                 | Parameter                                    | Condition                                                    | Min | Тур  | Max  | Unit |

|------------------------|----------------------------------------------|--------------------------------------------------------------|-----|------|------|------|

| V <sub>FD(5-8)</sub>   | Recirculation diode forward voltage          | I <sub>FD</sub> < -3 A                                       | 0.5 | 0.75 | 1.75 | V    |

| R <sub>D5-8</sub>      | Resistor D <sub>X</sub> -Pin to ground       | V <sub>Q</sub> < V <sub>D</sub> < 18 V<br>(Typ @ Tj = 25 °C) | 100 | 240  | 650  | kΩ   |

| I <sub>leak_Dx_0</sub> | Leakage current into Dx-Pin<br>D5, D7, D6/D8 | -                                                            | 6   | 90   | 170  | μΑ   |

| I <sub>sub</sub>       | Dx substrate current                         | % of Recirculation current                                   | -   | -    | 2    | %    |

## 3.3.4 Output timing characteristics

The DMOS outputs have controlled slopes to minimize EME. The Edge Shaping option is programmed via SPI (See : *Edge shaping (EDGE\_SH):*). Edge shaping is optional for outputs Q5-Q8 only.

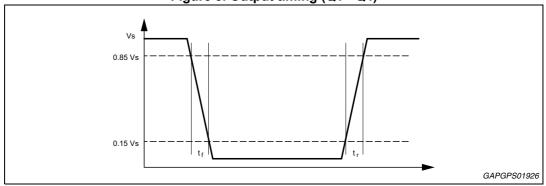

Figure 5. Output timing (Q1 - Q4)

Table 9. Timing for outputs Q1 - Q4 (no edge shaping)

| Symbol         | Parameter                                | Condition          | Min | Тур | Max | Unit |

|----------------|------------------------------------------|--------------------|-----|-----|-----|------|

| t <sub>r</sub> | Output slope rising edge (15 % to 85 %)  | 0.5 A < IQ < 1.5 A | 4   | 8   | 12  | V/µs |

| t <sub>f</sub> | Output slope falling edge (85 % to 15 %) | 0.5 A < IQ < 1.5 A | 4   | 8   | 12  | V/µs |

VQ/V

VD

SS

Vedge

Vedge

1/µs

GAPGPS01927

Figure 6. Output timing characteristics diagram with edge shaping (Q5-Q8)I

#### Where:

- V<sub>D</sub>: Valve supply voltage

- V<sub>FD</sub>: Forward voltage drop across the recirculation diode

- V<sub>EDGE</sub>: Voltage Sf to Ss slope transition

- Ss: Slow slope

- Sf: Fast slope

Table 10. Output timing electrical characteristics (Q5-Q8)

| Symbol                            | Parameter                                                  | Condition                                                                                           | Min  | Тур | Max | Unit |

|-----------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|-----|------|

| V <sub>edge</sub>                 | Edge shaping threshold                                     | $0.5 \text{ A} < I_Q < 1.5 \text{ A}$<br>8 V< V <sub>D</sub> < 20 V<br>measured from V <sub>D</sub> | -2.2 |     | -1  | V    |

| Sf_Q <sub>1</sub> -Q <sub>4</sub> | Sf output on/off slope fast Q <sub>1</sub> -Q <sub>4</sub> | 8 V< V <sub>D</sub> < 20 V                                                                          | 3    | 10  | 17  | V/µs |

| Ss_Q <sub>1</sub> -Q <sub>4</sub> | Ss output on/off slope slow Q <sub>1</sub> -Q <sub>4</sub> | 0.5 A < I <sub>load</sub> < 1.5 A                                                                   | 2    | 4   | 6   | V/µs |

| Sf_Q <sub>5</sub> -Q <sub>8</sub> | Sf output on/off slope fast Q <sub>5</sub> -Q <sub>8</sub> | resistive load                                                                                      | 6    | 13  | 20  | V/µs |

| Ss_Q <sub>5</sub> -Q <sub>8</sub> | Ss output on/off slope slow Q <sub>5</sub> -Q <sub>8</sub> | 15 % to 85 %                                                                                        | 2.5  | 5   | 7.5 | V/µs |

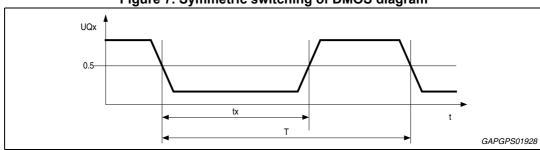

## Symmetric switching of DMOS

Figure 7. Symmetric switching of DMOS diagram

A Symmetric switching is present to assure a reliable PWM at the output.

Table 11. Symmetric switching of DMOS electrical characteristics

| Symbol            | Parameter                       | Condition                                                           | Min | Тур | Max | Unit |

|-------------------|---------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>sym1</sub> | Symmetry 1 with edge shaping    | tx. dc x T  < 1.5 μs<br>dc = {01}<br>0.5 A < I <sub>Q</sub> < 1.5 A | 0   | -   | 1.5 | μs   |

| t <sub>sym2</sub> | Symmetry 2 without edge shaping | tx. dc x T  < 2.7 μs<br>dc = {01}<br>0.5 A < I <sub>Q</sub> < 1.5 A | 0   | -   | 2.7 | μs   |

# 3.3.5 Output configuration Q1 - Q4

Table 12. Q3 / Q4 (current controller) electrical characteristics

| Symbol              | Parameter                                                               | Condition                                                      | Min | Тур        | Max          | Unit |

|---------------------|-------------------------------------------------------------------------|----------------------------------------------------------------|-----|------------|--------------|------|

| t <sub>D(min)</sub> | Minimum duration                                                        |                                                                | 250 | -          | -            | μs   |

| t <sub>D(res)</sub> | Duration resolution (per bit)  Address 0 bit 9 = 0  Address 0 bit 9 = 1 |                                                                | 1   | 250<br>500 | -            | μs   |

| n                   | Number of bits                                                          |                                                                | -   | 5          | -            | -    |

| t <sub>D(max)</sub> | Maximum duration  Address 0 bit 9 = 0  Address 0 bit 9 = 1              | (2 <sup>5</sup> - 1) x 250 μs<br>(2 <sup>5</sup> - 1) x 250 μs | -   | -          | 7.75<br>15.5 | ms   |

# 3.3.6 Output configuration Q5 - Q8

(refer to Section 4.4: Set-point controller for details)

Table 13. PWM output behavior characteristics (Q5 - Q8)

| Symbol              | Parameter                                                    | Condition                                                    | Min  | Тур        | Max          | Unit     |

|---------------------|--------------------------------------------------------------|--------------------------------------------------------------|------|------------|--------------|----------|

| f_Q <sub>x</sub>    | Output frequency                                             | -                                                            | -2 % | 4          | +2 %         | kHz      |

| DC                  | Duty range                                                   | -                                                            | 0    | -          | 100          | %        |

| DC <sub>RES</sub>   | Duty resolution of f_A                                       | -                                                            | -    | 0.2        | -            | %        |

| N <sub>RES</sub>    | Number of bits for duty resolution                           | -                                                            | -    | 9          | -            | -        |

| t(n) <sub>RES</sub> | Resolution of duration  Add. 0 bit D9 = 0  Add. 0 bit D9 = 1 | 1/f_A                                                        | -    | 250<br>500 | -            | µs<br>µs |

| N <sub>Bit</sub>    | Number of bits for duration                                  | -                                                            | -    | 5          | -            | -        |

| t(n) <sub>MAX</sub> | Max. duration  Add. 0 bit D9 = 0  Add. 0 bit D9 = 1          | (2 <sup>5</sup> -1) x 250 μs<br>(2 <sup>5</sup> -1) x 500 μs | -    | -          | 7.75<br>15.5 | ms<br>ms |

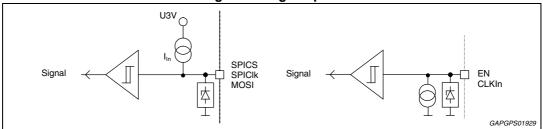

# 3.3.7 Logic inputs / outputs

Figure 8. Logic inputs

Table 14. Logic inputs electrical characteristics

| Symbol               | Parameter                                               | Condition                        | Min  | Тур | Max | Unit |

|----------------------|---------------------------------------------------------|----------------------------------|------|-----|-----|------|

| V <sub>In_low</sub>  | Input threshold                                         | -                                | -0.3 | -   | 1.0 | V    |

| V <sub>In_high</sub> | Input threshold                                         | -                                | 2.0  | -   | 3.5 | V    |

| V <sub>In-hys</sub>  | Input threshold hysteresis                              | -                                | 50   | 100 | 350 | mV   |

| I <sub>P-U</sub>     | Internal pull-up current source for SPICS, SPICLK, MOSI | 0V ≤ V <sub>In-xy</sub> ≤ 2 V    | -12  | -30 | -60 | μΑ   |

| I <sub>P-D</sub>     | Internal pull-down current source for EN, CLKIN         | 1V ≤ V <sub>In-xy</sub> ≤ 3.45 V | +12  | +30 | +60 | μΑ   |

| C <sub>in</sub>      | Input capacitance                                       | designed but not tested          | 3.5  | -   | 7.5 | pF   |

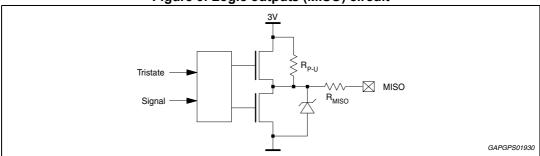

# 3.3.8 Logic outputs (MISO)

Figure 9. Logic outputs (MISO) circuit

Table 15. Logic outputs (MISO) electrical characteristics

| Symbol               | Parameter             | Condition                                | Min | Тур | Max  | Unit |

|----------------------|-----------------------|------------------------------------------|-----|-----|------|------|

| V <sub>MISO_L</sub>  | MISO low voltage      | $I_{Out-xy} \le 25 \mu A; C_L \le 30 pF$ | 0   | -   | 0.4  | V    |

| V <sub>MISO_H</sub>  | MISO high voltage     | I <sub>Out-xy</sub> ≤ -25 μA;            | 2.5 | 3.3 | 3.45 | V    |

| R <sub>MISO-ON</sub> | MISO ON resistance    | R <sub>ON</sub> +R <sub>MISO</sub>       | 40  | 100 | 400  | Ω    |

| R <sub>P-U</sub>     | MISO pull up resistor | SPICS = high → MISO in tristate mode     | 50  | 120 | 300  | kΩ   |

| C <sub>in</sub>      | Input capacitance     | designed but not tested                  | 3.5 | -   | 7.5  | pF   |

## 3.3.9 Output stage diagnostic functions

(refer to Section 4.7: Diagnostics for details)

Table 16. Diagnostic functions at output stage electrical characteristics

| Symbol              | Parameter                                            | Condition                                                    | Min | Тур  | Max  | Unit |

|---------------------|------------------------------------------------------|--------------------------------------------------------------|-----|------|------|------|

| V <sub>OL</sub>     | Open load threshold                                  | output off                                                   | 0.3 | 0.33 | 0.39 | x VS |

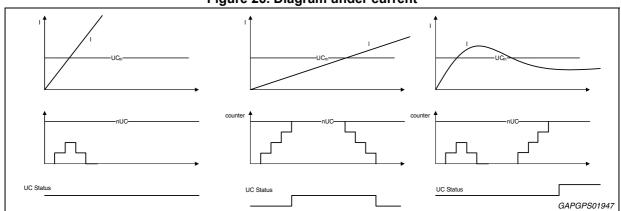

| l <sub>uc</sub>     | Undercurrent threshold                               | output on                                                    | 50  | 100  | 140  | mA   |

| T <sub>SD</sub>     | Temperature shut down threshold <sup>(1)</sup>       | -                                                            | 180 | 200  | 225  | °C   |

| T <sub>W</sub>      | Temperature warning                                  | -                                                            | 160 | 180  | 200  | °C   |

| $\Delta T_{SD}$     | T <sub>SD</sub> Hysteresis                           | T <sub>SD</sub>                                              | 5   | -    | 35   | °C   |

| D <sub>x loss</sub> | D <sub>x</sub> supply loss threshold and zener clamp | Output is clamping                                           | 32  | -    | 39   | ٧    |

| I <sub>OC</sub>     | Overcurrent threshold                                | Qx switched off after t <sub>OC</sub>                        | 3   | 5    | 8    | Α    |

| V <sub>G_ON</sub>   | Gate monitoring threshold                            | Internal node, not tested                                    | 5   | -    | -    | V    |

| V <sub>G_OFF</sub>  | Gate monitoring threshold                            | Max allowable I <sub>DS</sub><br>See: <i>Gate monitoring</i> | -   | -    | 15   | mA   |

<sup>1.</sup> Monitoring is only active if the output is on.

# 3.3.10 General diagnostic functions

(refer to Section 4.7: Diagnostics for details)

Table 17. General diagnostic functions electrical characteristics

| Symbol             | Parameter                 | Condition | Min | Тур  | Max | Unit |

|--------------------|---------------------------|-----------|-----|------|-----|------|

| V <sub>UV</sub>    | Under voltage threshold   | (VS-pin)  | 3.0 | -    | 5.2 | V    |

| V <sub>SG_L</sub>  | Signal GND loss threshold | -         | 0.2 | 0.4  | 0.6 | V    |

| V <sub>PG_L</sub>  | Power GND loss threshold  | -         | 0.7 | 1.45 | 2.2 | V    |

| V <sub>PG_Lh</sub> | Power GND loss hysteresis | -         | -   | 1.0  | -   | V    |

Table 18. CLKIN-monitoring characteristics

| Symbol                  | Parameter                                   | Conditions         | Min  | Тур      | Max  | Unit       |

|-------------------------|---------------------------------------------|--------------------|------|----------|------|------------|

| f <sub>CLKIN_H250</sub> | CLKIN monitoring @ 250 kHz-mode set SPI bit | frequency too high | 290  | -        | 760  | kHz        |

| f <sub>CLKIN_L250</sub> | CLKIN monitoring @ 250 kHz-mode set SPI bit | frequency too low  | 90   | -        | 190  | kHz        |

| f <sub>CLKIN_H1M</sub>  | CLKIN monitoring @ 1 MHz-mode set SPI bit   | frequency too high | 1.16 | -        | 3.04 | MHz        |

| f <sub>CLKIN_L1M</sub>  | CLKIN monitoring @ 1 MHz-mode set SPI bit   | frequency too low  | 0.36 | -        | 0.76 | MHz        |

| f <sub>CLKIN_OK</sub>   | CLKIN monitoring clear SPI bit              | CLKIN frequency ok | -    | 250<br>1 | -    | kHz<br>MHz |

18/65 DocID026134 Rev 1

# 3.3.11 Filtering times

Table 19. Failure filtering times characteristics

| Symbol              | Parameter <sup>(1)</sup>           | Condition   | Min | Тур | Max | Unit |

|---------------------|------------------------------------|-------------|-----|-----|-----|------|

| t <sub>OL</sub>     | Open load filtering time           | outputs off | 20  | 44  | 70  | μs   |

| t <sub>UC</sub>     | Under current filtering time       | -           | 10  | 20  | 40  | μs   |

| t <sub>oc</sub>     | Over current switch-off delay time | -           | 10  | 20  | 40  | μs   |

| t <sub>SD</sub>     | Thermal shutdown delay time        | -           | 10  | 40  | 80  | μs   |

| t <sub>TW</sub>     | Thermal Warning filtering time     | -           | 10  | 20  | 40  | μs   |

| t <sub>DX_L</sub>   | Dx loss filtering time             | -           | 1   | 2   | 5   | μs   |

| t <sub>PGND_L</sub> | Power GND loss filtering time      | -           | 10  | 20  | 40  | μs   |

| t <sub>SGND_L</sub> | Signal GND loss filtering time     | -           | 10  | 20  | 40  | μs   |

| t_EN_F              | EN filtering time <sup>(2)</sup>   | -           | 1.5 | 2   | 3   | μs   |

| t <sub>CLK_F</sub>  | CLKIN-failure detection time       | -           | 140 | 200 | 310 | μs   |

<sup>1.</sup> All parameters based on valid CLKIN (250 kHz/1 MHz) signal.

Table 20. SVDT test timing (refer to 4.7.11: Silent valve driver test (SVDT))

| Symbol         | Parameter                                       | Condition                              | Min | Тур  | Max  | Unit |

|----------------|-------------------------------------------------|----------------------------------------|-----|------|------|------|

| t <sub>x</sub> | Minimum passing test time                       | SVDT Enabled<br>I_Qx < I <sub>UC</sub> | 90  | 100  | 110  | μs   |

| t <sub>y</sub> | Maximum failing test time, Outputs Q1 - Q7 only | SVDT Enabled<br>I_Qx < I <sub>UC</sub> | 900 | 1000 | 1100 | μs   |

| t <sub>y</sub> | Maximum failing test time Output Q8 Only        | SVDT Enabled<br>I_Q8 < I <sub>UC</sub> | 675 | 750  | 825  | μs   |

### 3.3.12 Internal oscillator

Table 21. Internal oscillator electrical characteristics

| Symbol           | Parameter            | Condition | min | typ | max | Unit |

|------------------|----------------------|-----------|-----|-----|-----|------|

| f <sub>osc</sub> | Oscillator frequency | -         | 1.4 | 2.0 | 2.6 | MHz  |

<sup>2.</sup> Digital filter only for falling edges and analog filter for both edges.

GAPGPS01931

# 3.3.13 SPI timing characteristics SPICLK, MISO, MOSI, SPICS

SPICS

SPICIA

O.8 V<sub>high</sub>

O.2 V<sub>high</sub>

MISO

MISO

Tespicia-high

Figure 10. SPI timing characteristics SPICLK, MISO, MOSI, SPICS

Table 22. SPI timing characteristics

| No.                                                | Parameter                                 | Conditions                                                                               | Min               | Тур         | Max            | Unit           |

|----------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------|-------------------|-------------|----------------|----------------|

| f <sub>SPICLK</sub>                                | SPICLK frequency                          | C <sub>load</sub> ≤ 30 pF                                                                | 0                 | -           | 5              | MHz            |

| t <sub>SPICLK-high,</sub> t <sub>SPICLK-low</sub>  | SPICLK high time / low time               | -                                                                                        | 68                | -           | -              | ns             |

| t <sub>lead</sub>                                  | SPICS -> SPICLK delay                     | -                                                                                        | 50                | -           | -              | ns             |

| t <sub>lag</sub>                                   | SPICLK -> SPICS delay                     | -                                                                                        | 60                | -           | -              | ns             |

| t <sub>MOSI-stable</sub>                           | MOSI stable                               | -                                                                                        | 68                | -           | -              | ns             |

| t <sub>rise</sub> /t <sub>fall</sub>               | SPICLK, MOSI<br>rise time / fall time     | $C_{load} \le 50 \text{ pF}$ $C_{load} \le 100 \text{ pF}$ $C_{load} \le 150 \text{ pF}$ | 0<br>0<br>0       | -           | 14<br>23<br>32 | ns             |

| t <sub>MISO-delay</sub>                            | SPICLK -> MISO delay                      | C <sub>load</sub> ≤ 150 pF                                                               | -                 | -           | 65             | ns             |

| t <sub>MISO-rise</sub> ,<br>t <sub>MISO-fall</sub> | MISO rise time / fall time <sup>(1)</sup> | $C_{load} \le 15 \text{ pF}$ $C_{load} \le 50 \text{ pF}$ $C_{load} \le 65 \text{ pF}$   | 0.8<br>2.5<br>3.5 | 2<br>7<br>9 | 7<br>21<br>28  | ns<br>ns<br>ns |

| t <sub>SPICS-high</sub>                            | SPICS high time / low time                | C <sub>load</sub> ≤ 150 pF                                                               | 150               | -           | -              | ns             |

| t <sub>MISO_tri</sub>                              | MISO tri-state                            | C <sub>load</sub> ≤ 150 pF                                                               | -                 | -           | 100            | ns             |

<sup>1.</sup> guaranteed by design

20/65

Note: The MISO pin is tri-stated with a weak pull-up when SPICS is high.

DocID026134 Rev 1

# 4 Circuit description

The L9375TRLF is an eight channel low side driver intended for ABS applications. The device communicates entirely by individual SPI commands. All of the outputs can be switched on or off for defined periods with four of the outputs having PWM capability. It is possible to program two consecutive on-time durations or PWM duty cycles at one time.

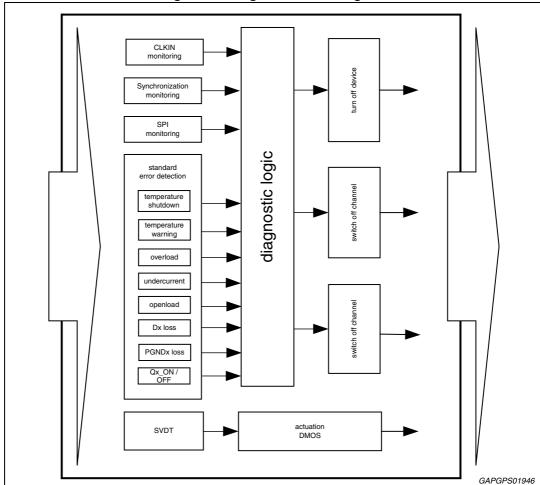

All outputs have high level diagnostic capabilities. These include off state open load, under current, shorted load, gate monitoring, thermal warning, and thermal shutdown flags. Higher level diagnostics include a Silent-Valve-Detection-Test (SVDT) to verify load and driver integrity as well as detection and reporting of a missing recirculation diode (Q5-Q8), Ground loss, Clock failure, and SPI synchronization failure.

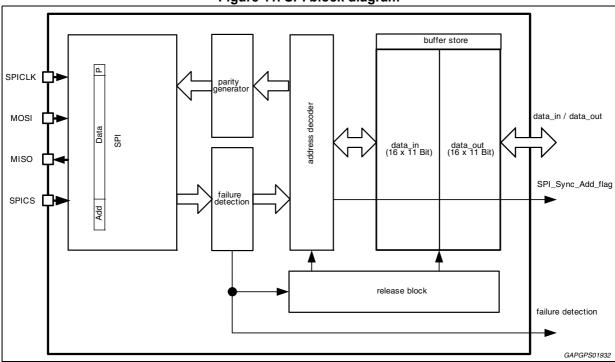

## 4.1 SPI serial peripheral interface

The L9375TRLF SPI is a fully bidirectional serial interface configured as a SLAVE for communication between a  $\mu$ C (the MASTER) and the L9375TRLF. All of the data management is handled in 16 sets of SPI registers of 16 bits each. There are 16 input or command registers and 8 status registers. All output control including on-time and PWM / switching timing is realized internally. The control parameters (Duty Cycle and Duration) are programmed via serial communication. The 16 status registers (only 8 are used) provide a high level of diagnostic capability from output status to internal control parameter confirmation.

Figure 11. SPI block diagram

Messages from the master ( $\mu$ C) to the L9375TRLF are sent over the MOSI (Master out Slave In) pin. Messages from the L9375TRLF to the master will be sent over the MISO (Master in Slave Out) pin.

The master starts the communication with a '1'  $\rightarrow$  '0' transition on the SPICS pin. After  $t_{LEAD}$ , (*Table 22*) the master sends a clock signal to the SPICLK and data to the MOSI pin. The SPICLK pin must be low at the falling edge of SPICS and remain low for  $t_{LEAD}$  for correct communication to occur. The SPICS pin must rise after every 16 bits sent.

The MISO pin is tri-stated with a high ohmic pull-up resistor when the SPI chip select (SPICS) pin is held high.

The SPI has the following features:

- 4 wire SPI (SPICS, SPICLK, MOSI, MISO)

- Word length of 16-Bits (0..15)

- 4 address and 11 data bits and one parity bit

- 16 receive-buffers (11 bit wide)

- 8 send-buffers (11 bit wide)

### 4.1.1 General protocol

The protocol has the following structure:

- A parity-bit at the LSB and eleven data bits (bits 1 to 11).

- The four address bits are at the highest position at the transfer (bits 12 15).

- SPI communication begins with the MSB.

- High level = '1'

- Low level = '0'

#### **General SPI protocol**

| /_ | MSB |    |    |    |     |    |    |    |    |    |    |    |    |    |    | LSB |

|----|-----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|-----|

| 7  | А3  | A2 | A1 | A0 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Р   |

Ax: address bits

Dx: data bits

P: parity bit

A message from the L9375TRLF to the master  $\mu$ C (MISO) contains 4 address bits. These bits are not a copy of the received address from the previous transmission, but are addresses that were decoded from the address decoder. This is done so that the master ( $\mu$ C) has the ability to discern the integrity of the L9375TRLF address decoder.

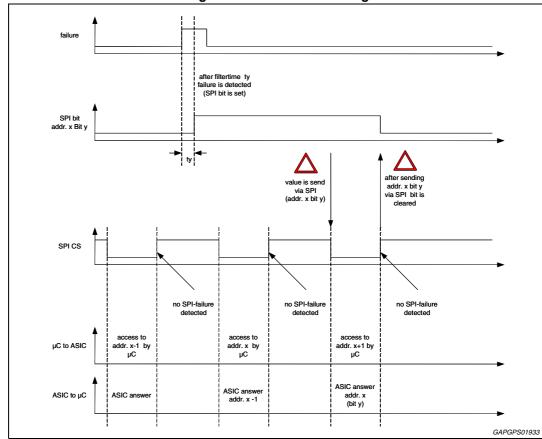

Every time an error bit in one of the SPI registers is set by the L9375TRLF it will remain set until the corresponding register has been read out via SPI. Once a status register has been read the corresponding register will be reset upon the rising edge of SPICS.

Every SPI communication writes data into a register (read only not possible). Every SPI response is associated with the address of the message sent one communication before.

#### 4.1.2 SPI failure detection

SPI communications sent to the L9375TRLF that contain errors are ignored. This inaction includes both the commands given and the data retrieved. That is, commands are ignored and the initial state of the output is not changed. Also data registers referenced by the erroneous SPI communication will not be reset.

Figure 12. SPI error handling

Three functions are monitored to discern a correct SPI communication from the master:

- Correct number of Clock pulses in SPICLK per transfer.

During each SPICS-low-phase the L9375TRLF counts the number of positive edges of SPICLK. If this number is unequal to 16 a SPICLK-error is detected.

- 2. Parity check (odd)

The L9375TRLF detects a parity error if the number of '1's within a transfer is even.

- 3. Data-failure monitoring:

This bit is set if the master writes inappropriate data to any of the config-registers (2/14/15).

#### 4.1.3 Data transfer

Upon the completion of each 16 bit SPI command (rising edge of SPICS), data is transferred from the SPI block to the appropriate internal registers. Some internal SPI registers are reset (such as fault bits) once they are accessed.

#### 4.1.4 Address decoder

The address decoder routes incoming data into the appropriate receive buffer and sets up the appropriate send buffer register to transmit information back to the master (MISO) for the subsequent SPI communication.

### 4.1.5 Parity generator

The parity generator completes the output messages with a parity bit. The number of '1's within an output-transfer has to be odd. Parity is verified prior to the SPICS going high.

#### 4.1.6 Initial MISO information

After initial power on, the first SPI-answer from the L9375TRLF reflects the Chip-ID information. Typically, the information will appear as follows:

| А3 | A2 | <b>A1</b> | Α0 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Р |

|----|----|-----------|----|-----|----|----|----|----|----|----|----|----|----|----|---|

| 1  | 0  | 1         | 0  | 0   | 0  | 1  | х  | х  | х  | х  | х  | х  | х  | х  | х |

This information is unique to this device and reflects specific device information relevant only to ST.

### 4.1.7 Register map

This is a brief reference to the register locations within the L9375TRLF (for more detailed information please see Section *5: Programmers guide*).

#### Command buffer (data in)

Table 23. Command buffer (data\_in)

| Address <sub>(HEX)</sub> | Content                              | Buffer name    |

|--------------------------|--------------------------------------|----------------|

| 0                        | Sync-trigger, Reset, and Sync values | SYNC_REG       |

| 1                        | STW min and max values               | STW_V          |

| 2                        | Configuration register               | CONFIG         |

| 3                        | Fast Switch ON gate commands         | FSON           |

| 4                        | Duration Registers for Q1 /Q2        | Duration Q1/Q2 |

| 5                        | Duration Registers for Q5 /Q6        | Duration Q5/Q6 |

| 6                        | Duty cycle 1 Q5                      | DUTY1_Q5       |

| 7                        | Duty cycle 2 Q5                      | DUTY2_Q5       |

| 8                        | Duty cycle 1 Q6                      | DUTY1_Q6       |

| 9                        | Duty cycle 2 Q6                      | DUTY2_Q6       |

| 10                       | Duty cycle 1 Q7                      | DUTY1_Q7       |

| 11                       | Duty cycle 2 Q7                      | DUTY2_Q7       |

| 12                       | Duty cycle 1 Q8                      | DUTY1_Q8       |

| 13                       | Duty cycle 2 Q8                      | DUTY2_Q8       |

| 14                       | Duration Registers for Q7 /Q8        | Duration Q7/Q8 |

| 15                       | Duration Registers for Q3 /Q4        | Duration Q3/Q4 |

## Status buffer (data out)

Table 24. Status buffer (data\_out)

| Address <sub>(HEX)</sub> | Content                                     | Buffer name |

|--------------------------|---------------------------------------------|-------------|

| 0                        | General status                              | G_STATUS    |

| 1                        | Q1 Output Status Register                   | STATUS_Q1   |

| 2                        | Q2 Output Status Register                   | STATUS_Q2   |

| 3                        | Q5 Output Status Register                   | STATUS_Q5   |

| 4                        | Q6 Output Status Register                   | STATUS_Q6   |

| 5                        | Q3 Output Status Register                   | STATUS_Q3   |

| 6                        | Q4 Output Status Register                   | STATUS_Q4   |

| 7                        | Q7 Output Status Register                   | STATUS_Q7   |

| 8                        | Q8 Output Status Register                   | STATUS_Q8   |

| 9                        | Reserved → data ,000 0000 0000'             | RESERVED    |

| 10                       | Reserved → data ,000 0000 0000'             | RESERVED    |

| 11                       | Reserved → data ,000 0000 0000'             | RESERVED    |

| 12                       | Reserved → data ,000 0000 0000'             | RESERVED    |

| 13                       | Reserved → data ,000 0000 0000 <sup>o</sup> | RESERVED    |

| 14                       | Reserved → data ,000 0000 0000 <sup>o</sup> | RESERVED    |

| 15                       | Reserved → data ,000 0000 0000'             | RESERVED    |

A more detailed explanation about the register settings can be found in *Section 5: Programmers guide*.

## 4.2 Clock

The clock controller contains a CLKIN-monitoring function to validate the CLKIN frequency, a clock multiplier to produce an internal 2 MHz clock, and an internal oscillator for monitoring purposes and backup.

Oscillator

CLKIN F

CLKIN\_state

250 kHz/1MHz

GAPGPS01934

Figure 13. Clock block diagram

### 4.2.1 Clock multiplier

The Clock Multiplier provides a steady 2 MHz signal ( $f_{CLK}$ ) for the internal logic based on the CLKIN signal. The multiplier factor is determined by setting the CLKIN\_S bits in the SPI Command register *Configuration register (address 2)*. It is possible to have the wrong CLKIN\_S bits set for a specific CLKIN frequency. When this occurs a CLKIN failure (CLKIN\_F) is registered.

#### 4.2.2 Internal oscillator

The 2 MHz internal oscillator (f<sub>osc,</sub> *Table 21*) provides a comparison signal used to validate the incoming CLKIN signal. If the CLKIN signal is determined to be out of range then the internal oscillator is used to provide clock signals internal to the L9375TRLF. The internal oscillator does not have the accuracy of a proper CLKIN signal. Therefore the diagnostic filter times will reflect the accuracy of this clock for that case.

#### 4.2.3 CLKIN signal monitoring

The CLKIN signal is an external 250 kHz or 1 MHz signal from the  $\mu$ C to the L9375TRLF. This signal is monitored to be within a specified range ( $f_{CLKIN\_L} < f_{CLKIN\_H}, Table 18$ ). If the value is out of range, then the CLKIN\_F (CLKIN failure) bit is set to '1'. If a CLKIN failure ( $f_{CLK}$  out of range) is detected, the outputs are disabled and the internal 2 MHz oscillator is used as the clock for the internal logic.

| CLKIN   | CLKIN_S 250 kHz / 1 MHz | f <sub>CLK</sub> | CLKIN_F        |

|---------|-------------------------|------------------|----------------|

| 250 kHz | 250 kHz                 | 2 MHz            | 0 (no failure) |

| 1 MHz   | 1 MHz                   | 2 MHz            | 0 (no failure) |

| 250 kHz | 1 MHz                   | 1 MHz            | 1 (failure)    |

| 1 MHz   | 250 kHz                 | 8 MHz            | 1 (failure)    |

**Table 25. Clock validation**

# 4.3 Synchronization controller

Due to natural SPI communication task time jitter, proper actuation of the outputs requires some level of synchronization. The Synchronization Controller provides for synchronized output actuation eliminating SPI task time jitter issues.

This function forces the outputs to change to their commanded state at a specified point in time outside of the SPI communication window. This also ensures a more stable SPI communication by minimizing ground fluctuation due to output switching during periods of SPI communications. This delay between the SPI commands and the output actuation is programmed by setting the RESET\_VALUE and SYNC\_VALUE parameters located in the Section 5.1.1: Sync + Sync-trigger register (address 0).

## 4.3.1 Output synchronization

The RESET\_VALUE time value is determined by using the typical time between SPI cycles. When programmed properly, the SPI communications occur at or around the RESET\_VALUE timing. The Sync Tolerance Window (STW) is an interval of time between RESET\_VALUE times where accessing the Sync (Section 5.1.1: Sync + Sync-trigger

26/65 DocID026134 Rev 1

*register (address 0)*) during this interval generates a sync failure (SYNC\_F). This window is defined by the parameters STW V MIN and STW V MAX.

The SYNC\_VALUE is a programmed delay after the RESET\_VALUE when the output transitions occur. This delay is typically set as half of the RESET\_VALUE. This sets the output transitions furthest from each SPI cycle and during the STW.

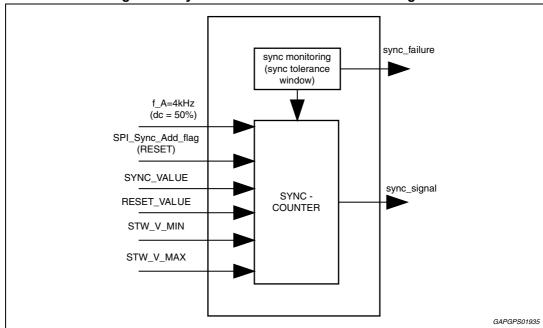

Figure 14. Synchronization controller block diagram

#### Inputs

The synchronization controller receives the following input signals:

- f A = 4 kHz for internal clocking.

- SYNC\_TRIG ="1" initiates the synchronization timing with that SPI event.

- SPI synchronization values (SYNC\_VALUE, RESET\_VALUE, STW\_V\_MIN;

STW V MAX) provide the parameters that allow for output synchronization.

#### **Outputs**

The synchronization controller provides the following output signals:

- The STW signal is used in conjunction with accessing address 0 to notify the master that the SPI cycles are within the programmed exclusionary window (SYNC F=1).

- The SYNC SIG initiates the actuation of the new output commands.

The synchronization counter increases its value with every period of f\_A. When the value of the counter equals the SYNC\_VALUE a synchronization signal (SYNC\_SIG) is generated (SYNC\_SIG='1').

The synchronization counter continually counts to the RESET\_VALUE and resets unless a SYNC\_TRIG command is sent. If a SYNC\_TRIG command is sent then the counter resets immediately. Upon resetting the SYNC\_TRIG and STW signals are reset (SYNC\_SIG = STW ='0').

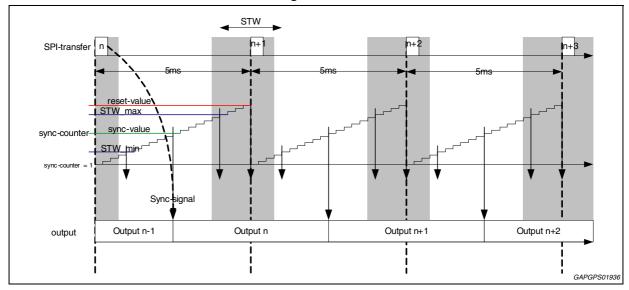

#### Normal sequence

When stepping through a normal sequence of events the following occurs:

- At a SYNC\_TRIG (SYNC\_TRIG='1') command the synchronization counter, STW and SYNC\_SIG flags are reset (STW='0', SYNC\_SIG='0')

- The counter counts up at a rate defined by f\_A (=4kHz).

- When the counter value reaches STW V MIN the STW flag is set (STW='1')

- When the counter value reaches SYNC\_VALUE the SYNC\_SIG flag is set (SYNC\_SIG='1') which activates the most recent output commands.

- When the counter value reaches the STW\_V\_MAX value the STW flag is reset (STW='0')

- When the counter value 4 MSBs are equal to the RESET\_VALUE the counter is reset and the output signal sync\_signal is reset (SYNC\_SIG='0')

#### Disallowed programming states

Erroneous programming results in the STW flag being set '1'

- If the STW\_V\_MIN value is higher than or equal to STW\_V\_MAX value the STW flag is set (STW = 1)

- If the STW\_V\_MAX value is higher or equal to the RESET\_VALUE value the STW flag is set (STW = 1)

#### Synchronization failure

Sync failure detects a timing error in the output command synchronization. The master  $\mu C$  programs a timing window (STW) where accessing to the Status Register address 0 is not allowed. If there is an access to the Status Register address 0 when the STW flag is set then a sync-failure is generated (SYNC\_F = 1). Also, a SYNC\_F will be detected if there is no SPI traffic at all between two SYNC\_SIG events. This status will be read out on the subsequent SPI transfer.

Without a SYNC\_SIG or at sync-failure there is no effect for the actuation and set points.

#### Synchronization controller programming

It is necessary to write into two registers (Command Register addresses 0 and 1, Section 5.1.1 and 5.1.2) to program the Synchronization Controller. The SYNC\_VALUE, the RESET\_VALUE and the SYNC\_TRIG values are programmed through address 0. The SYNC\_TRIG is written to once to initialize the counter. Once initialized the SYNC\_TRIG bit is reset by the controller. For subsequent SPI transfers the SYNC\_TRIG bit should not be set to avoid re-initializing the sync counter. There is no influence on the sync counter if the SYNC\_TRIG is not set. Occasionally, the sync counter may need re-initializing depending on the timing between the RESET\_VALUE and the  $\mu C$  loop time. The RESET\_VALUE is incremented by 1ms intervals. The SYNC\_VALUE is incremented by 250  $\mu s$  intervals.

The STW\_V\_MIN and STW\_V\_MAX values are programmed via register 1 (Section 5.1.2). Their interval length is dependant on the RESET\_VALUE MSB (address '0', bit D9):

Table 26. Sync. tolerance window interval length

| RESET_VALUE (add.0, bit D9) | RESET_VALUE duration | Sync tolerance window interval |

|-----------------------------|----------------------|--------------------------------|

| 0                           | <8ms                 | 250 µs/bit                     |

| 1                           | <u>&gt;</u> 8ms      | 500 μs/bit                     |

### **Example**

Example for a 5 ms cycle time, 2.5 ms SYNC\_VALUE-, STW of +1.75 ms/-1.25 ms:

- Cycle time:

- For programming the cycle time the master has to write the RESET\_VALUE (4 bit) via SPI. One bit has the resolution of 4/f\_A = 1 ms.

- RESET\_VALUE: 5 ms / 1 ms = 5  $\rightarrow$  0101<sub>(2)</sub>

- SYNC VALUE:

- For programming the sync-signal the master has to write the SYNC\_VALUE (6 bit). The LSB has the resolution of 250 μs.

- SYNC\_VALUE: 2.5 ms / 250 μs =  $10 \rightarrow 00 \ 1010_{(2)}$

- Sync tolerance window:

- For programming the STW the master must write min and max values (2 x 5 bit).

STW\_V\_MIN: 0.75 ms STW\_V\_MAX: 3.75 ms

STW\_V\_MIN: 0.75 ms / 250  $\mu$ s + 1 = 4  $\rightarrow$  0 0100<sub>(2)</sub> STW\_V\_MAX: 3.75 ms / 250  $\mu$ s + 1 = 16  $\rightarrow$  1 0000<sub>(2)</sub>

Figure 15. Normal mode

SPI transfer means transfer of all send and receive registers (0 through 15).

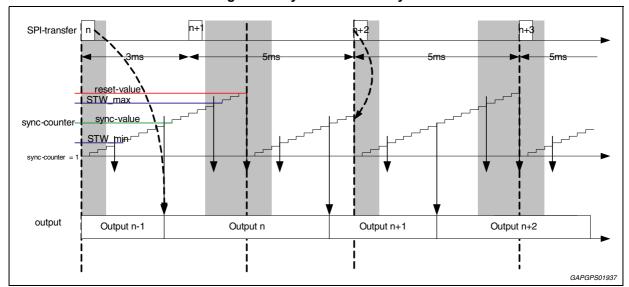

Figure 16. Sync-failure + re-synchronization

#### Re-synchronizing

The master sets the SYNC\_TRIG bit to '1' (Section 5.1.1) to re-initialize the sync counter. This re-synchronizes the L9375TRLF synchronization controller to the master. When this bit is set three counters are reset: the PWM counter (output frequency and duty cycle), the synchronization counter and the duration counter. The SYNC\_TRIG bit is reset (set to '0') by the L9375TRLF upon re-synchronization.

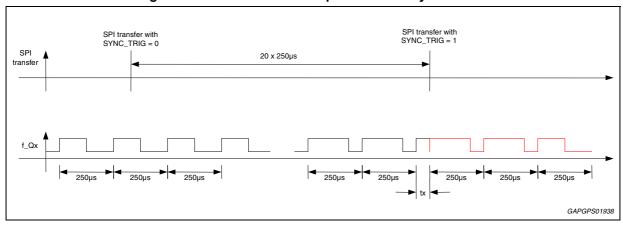

*Figure 17* shows the behavior of the output when the synchronization is done. The time tx is anything lower than 250  $\mu s$ .

Figure 17. Behavior of the output when the synchronization is done

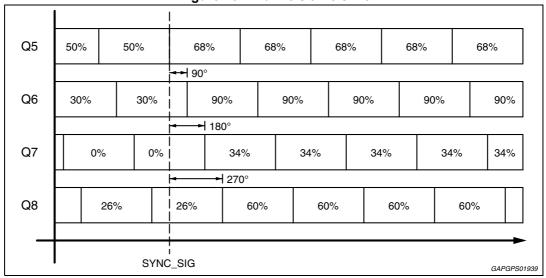

## 4.3.2 Time shift between output actuation (Q5-Q8 only)

The actuations of the outputs are time shifted by  $90^{\circ}$  (typ  $62.5~\mu s$ ) to offset their effect on the supply during switching. This balances the incremental switching current and reduces the EME generated by the switching of these channels. The new duty cycle or target current also becomes valid with this 90 degree time shift after the SYNC\_SIG.

30/65 DocID026134 Rev 1

Figure 18. Channels time shift

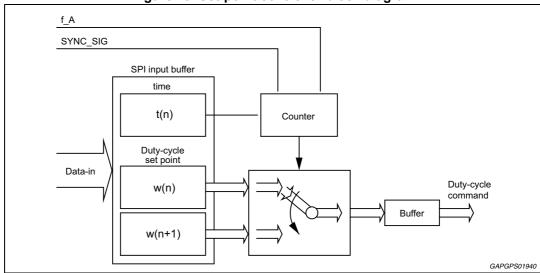

# 4.4 Set-point controller

The set point controller commands an on time duration (all outputs) and a PWM duty cycle (Q5-Q8 only) based on a duration command and duty cycle values from the SPI command registers for each output.

For outputs Q5 through Q8 this circuit is designed to generate two different PWM duty cycle values for each output per SPI cycle. This translates to a duty cycle [w(n)] for a duration [t(n)] and then a second duty cycle [w(n+1)] until otherwise commanded for each output per SPI cycle.

Figure 19. Set-point controller block diagram

The set point controller receives the following input information:

- Synchronization-signal (SYNC\_SIG)

- Frequency of the PWM-generator (f\_A; duty 50%)

- Set Point 1 (Duty cycle) = w(n) (9 bits)

- Set Point 2 (Duty cycle) = w(n+1) (9 bits)

- Duration (duration of Duty cycle = t(n) (5 bits)

The Duty cycle set point value is the only output signal.

The timer commands the change between w(n) and w(n+1) to the Duty cycle set point according to the programmed timing value t(n). If the value of the counter is lower than t(n) the Duty Cycle set point is set to w(n). If the value is equal or higher the Duty Cycle set point is set to w(n+1).

|                        | • • • • • • • • • • • • • • • • • • • • |              |  |

|------------------------|-----------------------------------------|--------------|--|

| Duration value (5 Bit) | Add. 0, bit D9                          | on-time (ms) |  |

| 00000 <sub>(2)</sub>   | X                                       | 0 ms (off)   |  |

| 11111 <sub>(2)</sub>   | 0                                       | 7.75 ms      |  |

| 01101 <sub>(2)</sub>   | 0                                       | 3.25 ms      |  |

| 11111 <sub>(2)</sub>   | 1                                       | 15.5 ms      |  |

| 01101 <sub>(2)</sub>   | 1                                       | 6.5 ms       |  |

Table 27. Example of PWM duration timing, t(n)

Note that the RESET\_VALUE MSB (bit 9 of address 0) affects the timer duration. With the MSB set the timer values double. This means if the SPI cycle time is equal or higher than 8 ms (>100 $_{(H)}$ ) the resolution of the duration t(n) is 500  $\mu$ s per LSB instead of 250  $\mu$ s.

| RESET_VALUE (add.0, bit D9) | RESET_VALUE duration | Resolution of timer duration |

|-----------------------------|----------------------|------------------------------|

| 0                           | <8 ms                | 250 µs                       |

| 1                           | <u>≥</u> 8 ms        | 500 μs                       |

All buffers and the timer counter are reset by:

- A CLKIN failure detection (CLKIN\_F = '1')

- A re-synchronization command (SYNC TRIG = '1')

The Q5 - Q8 PWM value range (externally programmed):

w(n): 9 Bit w(n+1): 9 Bit t(n): 5 Bit

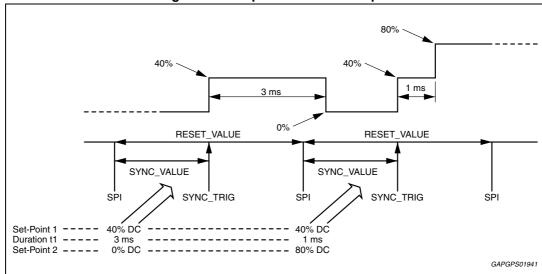

#### Example of set-point control (Q5 - Q8 only)

Below is an example of programming two sets of Set-Points sequentially for outputs Q5 through Q8. After programming the parameters that govern the synchronization (RESET\_VALUE, SYNC\_VALUE and the SWT values) the parameters Set-Point 1 (DUTY1), Set-Point 2 (DUTY2) and duration t1 (D\_Qx) are programmed (for programming instructions see Section 5.1.5: Duration registers (address 4, 5, 14, and 15)).

32/65 DocID026134 Rev 1

Generically, after the SYNC\_TRIG the Set-Point 1 is valid for t1 ms. After t1 ms the set-point controller switches to Set-Point 2 until the next SYNC\_TRIG event.

Figure 20. Set-point control example

In this example the RESET\_VALUE (and therefore the SPI transfer loop time) is set to 5ms and the SYNC\_VALUE is set to 2.5 ms. This sets the SYNC\_TRIG at 2.5ms after each SPI transfer. At SYNC\_TRIG, the new information received at the previous SPI transfer is incorporated into the Set-Point Controller.

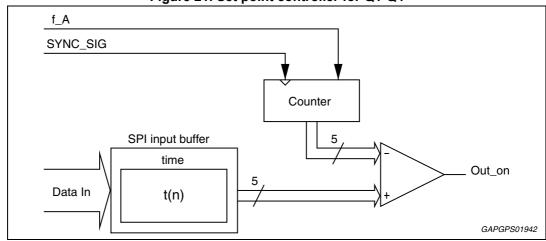

All that is required for outputs Q1 through Q4 is a commanded on-time based on data in the SPI input command registers (see *Section 5.1.5: Duration registers (address 4, 5, 14, and 15)*). Since there is no duty cycle information to decode there is no need to generate duty cycle commands or go through a PWM generator. The resulting circuit is shown in *Figure 21* below.

Figure 21. Set point controller for Q1-Q4

## 4.5 PWM generator(Q5-Q8 only)

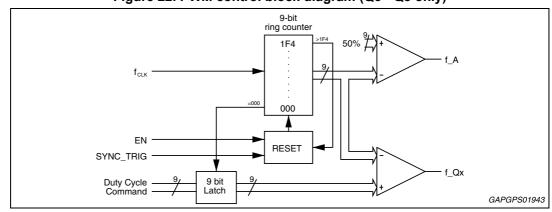

The PWM Generator converts the commanded Duty Cycle from the Set Point controller into a PWM signal for Output Driver Q5 - Q8. The PWM-generator provides a 4 kHz PWM duty cycle (f\_Qx) depending on the value of the 9 bit control variable. A 9-Bit ring counter counts with a frequency of  $f_{CLK}$  (2 MHz). The ring counter output is compared to the control variable. If the value of the counter is lower than the control variable the output, f\_Qx is high turning on the output Qx. If the value of the counter is equal or higher to the output, f\_Qx is low turning off the output Qx.

The counter can be reset by either a counter overflow at '1F4<sub>(Hex)</sub>' ( $\rightarrow$  500<sub>(10)</sub>), or by a SYNC\_TRIG command. The control variable value is changed only when the counter passes through zero.

Figure 22. PWM control block diagram (Q5 - Q8 only)

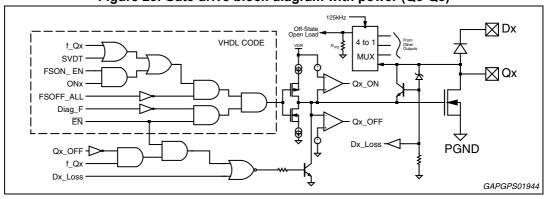

## 4.6 Output driver

The output driver controls the gate of the low side power DMOS as well as provides specific diagnostic information to the SPI diagnostic registers. There are several signals that control the actuation of the output power DMOS. In normal operation the typical input is the f\_Qx from the PWM generator (Q5-Q8) or Out\_on for the Set Point controller (Q1 -Q4). Other inputs that can turn on the output are the silent valve driver test (SVDT) and the Fast Switch on circuitry. Inputs that can disable the outputs are the fast switch off command, device enable, and certain failure detections that can potentially cause catastrophic damage if the output is left on.

Figure 23. Gate drive block diagram with power (Q5-Q8)

Figure 24. Gate drive block diagram with power (Q1-Q4)

### 4.6.1 Output driver controls

The output driver control circuit includes the logical combination of the following signals:

- PWM generator (Figure 22) (Q5-Q8):(f\_Qx)/ Set Point controller (Figure 21) (Q1-Q4): (Out on)

- Silent valve driver test signal (SVDT)

- Device enable (EN)

- Specific diagnostic failure indications such as PGND loss, overload, over temperature (Diag F).

- Fast switch off for all outputs: (FSOFF\_ALL)

- Fast switch on enable: (FSON EN)

- Direct SPI driven output switching through the fast switch on command (ON<sub>x</sub>)

In normal operation, the signals EN = '1', FSOFF\_ALL = '0', Diag\_F = '0', allow the gate to be driven by the PWM generator/set point controller signal (f\_Qx). The signal f\_Qx can override the SVDT input if actuation is commanded during an SVDT.

The signals Diag\_F='0', EN='0' and FSOFF\_ALL='1' by-pass all other inputs and turn off the output immediately. The Diag\_F flag is set to '1' at the detection of PGND loss, overload and over-temperature disabling the affected output. Hardware Enable (EN) is an external pin and is controlled by the  $\mu C$  directly. FSOFF\_ALL is a SPI command that provides a method to shut down all outputs in one SPI command.

#### 4.6.2 Diagnostics

Output stage diagnostics provide fault feedback information for the SPI status registers.

#### **Gate monitoring**

The Qx\_ON and Qx\_OFF SPI diagnostic bits provide Gate status history information. If the output DMOS Gate voltage is above the Qx\_ON threshold at any point between two SPI cycles the Qx\_ON output will latch on ('1') the SPI bit associated with that signal (bit 6 of status registers 1 - 8). If the output DMOS gate is below the Qx\_OFF threshold at any point between two SPI cycles the Qx\_OFF output will latch on ('1') the SPI bit associated with that signal (bit 7 of status of status registers 1 - 8). If an output is PWMmed both Qx\_ON and Qx\_OFF will return a '1' when read by the SPI. Upon reading status registers 1 through 8 the Qx\_ON and Qx\_OFF bits are reset to '0'.

This parameter cannot be tested directly as the Output MOSFET Gates are not exposed to measure their voltage. These parameters can only be tested by secondary means. and are guaranteed by design.

To verify that Qx\_ON is functional it is checked when the output is commanded on. At this point the output transistor is fully enhanced and the Rds(on) is within specification. The Qx\_on bit should be set.

To verify the Qx\_OFF condition the output is commanded off and a 15 mA current is forced into the Qx pin. This forces the output voltage to rise to the clamped voltage and raise the gate voltage so that the output MOSFET can sink the 15 mA. This will then reset the Qx\_OFF bit. This guarantees that the Qx\_OFF threshold is below the gate voltage value required for the output MOSFET to sink 15 mA.

Conversely if the Gate voltage remains above or below the thresholds mentioned the status bits Qx\_ON or Qx\_OFF will indicate only one state was present. At no time during normal operation will both bits not be set.

| Condition           | QX_ON | QX_OFF |  |  |

|---------------------|-------|--------|--|--|

| duty: 100%          | 1     | 0      |  |  |

| duty: 0%            | 0     | 1      |  |  |

| duty: 0% < dc <100% | 1     | 1      |  |  |

| Fault condition     | 0     | 0      |  |  |

Table 29. Qx\_ON and Qx\_OFF provide gate voltage status history information

## Recirculation diode loss detection (Q5-Q8)